# 10 MHz, 4-Quadrant Multiplier/Divider

**AD734**

#### **FEATURES**

High Accuracy

0.1% Typical Error

High Speed

10 MHz Full-Power Bandwidth

450 V/µs Slew Rate

200 ns Settling to 0.1% at Full Power

Low Distortion

-80 dBc from Any Input

Third-Order IMD Typically -75 dBc at 10 MHz

Low Noise 94 dB SNR, 10 Hz to 20 kHz 70 dB SNR, 10 Hz to 10 MHz

Direct Division Mode

2 MHz BW at Gain of 100

#### **APPLICATIONS**

High Performance Replacement for AD534

Multiply, Divide, Square, Square Root

Modulator, Demodulator

Wideband Gain Control, RMS-DC Conversion

Voltage-Controlled Amplifiers, Oscillators, and Filters

Demodulator with 40 MHz Input Bandwidth

#### PRODUCT DESCRIPTION

The AD734 is an accurate high speed, four-quadrant analog multiplier that is pin-compatible with the industry-standard AD534 and provides the transfer function W = XY/U. The AD734 provides a low-impedance voltage output with a full-power (20 V pk-pk) bandwidth of 10 MHz. Total static error (scaling, offsets, and nonlinearities combined) is 0.1% of full scale. Distortion is typically less than –80 dBc and guaranteed. The low capacitance X, Y and Z inputs are fully differential. In most applications, no external components are required to define the function.

The internal scaling (denominator) voltage U is 10 V, derived from a buried-Zener voltage reference. A new feature provides the option of substituting an external denominator voltage, allowing the use of the AD734 as a two-quadrant divider with a 1000:1 denominator range and a signal bandwidth that remains 10 MHz to a gain of 20 dB, 2 MHz at a gain of 40 dB and 200 kHz at a gain of 60 dB, for a gain-bandwidth product of 200 MHz.

The advanced performance of the AD734 is achieved by a combination of new circuit techniques, the use of a high speed complementary bipolar process and a novel approach to laser-trimming based on ac signals rather than the customary dc methods. The wide bandwidth (>40 MHz) of the AD734's input stages and the 200 MHz gain-bandwidth product of the multiplier core allow the AD734 to be used as a low distortion

#### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

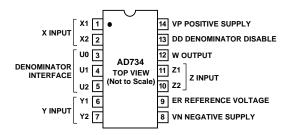

#### CONNECTION DIAGRAM

14-Lead DIP (Q Package and N Package)

demodulator with input frequencies as high as 40 MHz as long as the desired output frequency is less than 10 MHz.

The AD734AQ and AD734BQ are specified for the industrial temperature range of -40°C to +85°C and come in a 14-lead ceramic DIP. The AD734SQ/883B, available processed to MIL-STD-883B for the military range of -55°C to +125°C, is available in a 14-lead ceramic DIP.

#### PRODUCT HIGHLIGHTS

The AD734 embodies more than two decades of experience in the design and manufacture of analog multipliers, to provide:

- A new output amplifier design with more than twenty times the slew-rate of the AD534 (450 V/μs versus 20 V/μs) for a full power (20 V pk-pk) bandwidth of 10 MHz.

- 2. Very low distortion, even at full power, through the use of circuit and trimming techniques that virtually eliminate all of the spurious nonlinearities found in earlier designs.

- 3. Direct control of the denominator, resulting in higher multiplier accuracy and a gain-bandwidth product at small denominator values that is typically 200 times greater than that of the AD534 in divider modes.

- 4. Very clean transient response, achieved through the use of a novel input stage design and wide-band output amplifier, which also ensure that distortion remains low even at high frequencies.

- 5. Superior noise performance by careful choice of device geometries and operating conditions, which provide a guaranteed 88 dB of dynamic range in a 20 kHz bandwidth.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

# $\label{eq:total and the second of the sec$

#### TRANSFER FUNCTION

$$W = A_O \left\{ \frac{\left(X_1 - X_2\right)\left(Y_1 - Y_2\right)}{\left(U_1 - U_2\right)} - \left(Z_1 - Z_2\right) \right\}$$

| Parameter                                                                                                                                                                                                                                   | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Min            | A<br>Typ                            | Max                                                 | Min            | B<br>Typ                            | Max                                | Min            | S<br>Typ                            | Max                                   | Units                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------|-----------------------------------------------------|----------------|-------------------------------------|------------------------------------|----------------|-------------------------------------|---------------------------------------|-------------------------------------------|

| MULTIPLIER PERFORMANCE  Transfer Function Total Static Error¹ Over T <sub>MIN</sub> to T <sub>MAX</sub> vs. Temperature vs. Either Supply Peak Nonlinearity  THD²  Feedthrough Noise (RTO) Spectral Density                                 | Conditions $ -10 \text{ V} \le \text{ X}, \text{ Y} \le 10 \text{ V} $ $ T_{\text{MIN}} \text{ to } T_{\text{MAX}} $ $ \pm V_{\text{S}} = 14 \text{ V to } 16 \text{ V} $ $ -10 \text{ V} \le \text{X} \le +10 \text{ V}, \text{Y} = +10 \text{ V} $ $ -10 \text{ V} \le \text{Y} \le +10 \text{ V}, \text{X} = +10 \text{ V} $ $ X = 7 \text{ V rms}, \text{Y} = +10 \text{ V}, \text{f} \le 5 \text{ kHz} $ $ T_{\text{MIN}} \text{ to } T_{\text{MAX}} $ $ Y = 7 \text{ V rms}, \text{X} = +10 \text{ V}, \text{f} \le 5 \text{ kHz} $ $ T_{\text{MIN}} \text{ to } T_{\text{MAX}} $ $ X = 7 \text{ V rms}, \text{Y} = \text{nulled}, \text{f} \le 5 \text{ kHz} $ $ Y = 7 \text{ V rms}, \text{X} = \text{nulled}, \text{f} \le 5 \text{ kHz} $ $ X = Y = 0 $ $ 100 \text{ Hz to } 1 \text{ MHz} $ |                | = XY/<br>0.1<br>0.004               | 0.4<br>1<br>4<br>0.05                               |                | = XY<br>0.1<br>0.00                 | 0.25<br>0.6<br>3<br>0.05           |                | = XY/<br>0.1<br>0.004               | 110<br>0.4<br>1.25<br>4<br>0.05       | % % %/°C %//V % dBc dBc dBc dBc dBc dBc   |

| Total Output Noise                                                                                                                                                                                                                          | 100 Hz to 1 MHz<br>10 Hz to 20 kHz<br>$T_{MIN}$ to $T_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                | -94                                 | -88<br>-85                                          |                | -94                                 | -88<br>-85                         |                | -94                                 | -88<br>-85                            | dBc<br>dBc                                |

| DIVIDER PERFORMANCE (Y = 10 V) Transfer Function Gain Error X Input Clipping Level U Input Scaling Error <sup>3</sup>                                                                                                                       | $Y = 10 \text{ V}, U = 100 \text{ mV} \text{ to } 10 \text{ V}$ $Y \le 10 \text{ V}$ $T_{MIN} \text{ to } T_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | 1<br>1.25                           | XY/U<br>× U<br>0.3<br>0.8                           |                | 1<br>1.25                           | XY/U<br>× U<br>0.15<br>0.65        |                | 1<br>1.25                           | XY/U<br>× U<br>0.3<br>1               | %<br>V<br>%<br>%                          |

| (Output to 1%)                                                                                                                                                                                                                              | U = 1 V to 10 V Step, X = 1 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                | 100                                 |                                                     |                | 100                                 |                                    |                | 100                                 |                                       | ns                                        |

| INPUT INTERFACES (X, Y, & Z) 3 dB Bandwidth Operating Range X Input Offset Voltage Y Input Offset Voltage Z Input Offset Voltage Z Input PSRR (Either Supply)  CMRR Input Bias Current (X, Y, Z Inputs)  Input Resistance Input Capacitance | Differential or Common Mode $T_{\text{MIN}} \text{ to } T_{\text{MAX}}$ $T_{\text{MIN}} \text{ to } T_{\text{MAX}}$ $T_{\text{MIN}} \text{ to } T_{\text{MAX}}$ $f \leq 1 \text{ kHz}$ $T_{\text{MIN}} \text{ to } T_{\text{MAX}}$ $f = 5 \text{ kHz}$ $T_{\text{MIN}} \text{ to } T_{\text{MAX}}$ $Differential$ $Differential$                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54<br>50<br>70 | 40<br>±12.5<br>70<br>85<br>50<br>2  | 5<br>15<br>25<br>10<br>12<br>20<br>50<br>300<br>400 | 66<br>56<br>70 | 40<br>±12.<br>70<br>85<br>50<br>2   | 5<br>5<br>15<br>5<br>6<br>10<br>50 | 54<br>50<br>70 | 40<br>±12.<br>70<br>85<br>50<br>2   | 5<br>15<br>25<br>10<br>12<br>20<br>90 | MHz V mV mV mV mV mV dB dB dB nA nA kΩ pF |

| DENOMINATOR INTERFACES (U0<br>Operating Range<br>Denominator Range<br>Interface Resistor                                                                                                                                                    | , U1, & U2)<br> <br>  U1 to U2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VN             | V to VI<br>1000<br>28               |                                                     | VN             | to V<br>1000<br>28                  |                                    | VN             | V to VI<br>1000<br>28               |                                       | V<br>kΩ                                   |

| OUTPUT AMPLIFIER (W) Output Voltage Swing Open-Loop Voltage Gain Dynamic Response 3 dB Bandwidth Slew Rate Settling Time To 1% To 0.1% Short-Circuit Current                                                                                | $T_{MIN}$ to $T_{MAX}$<br>X = Y = 0, Input to $ZFrom X or Y Input, CL \le 20 pFW \le 7 V rms+20$ V or $-20$ V Output Step<br>$T_{MIN}$ to $T_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ±12<br>8       | 72<br>10<br>450<br>125<br>200<br>50 | 80                                                  | ±12<br>8       | 72<br>10<br>450<br>125<br>200<br>50 | 80                                 | ±12<br>8       | 72<br>10<br>450<br>125<br>200<br>50 | 80                                    | V<br>dB<br>MHz<br>V/µs<br>ns<br>ns<br>mA  |

| POWER SUPPLIES, ±V <sub>S</sub> Operating Supply Range Quiescent Current                                                                                                                                                                    | $T_{ m MIN}$ to $T_{ m MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ±8<br>6        | 9                                   | ±16.5<br>12                                         | ±8<br>6        | 9                                   | ±16.5<br>12                        | ±8<br>6        | 9                                   | ±16.5<br>12                           | V<br>mA                                   |

NOTES  $^1$ Figures given are percent of full scale (e.g., 0.01% = 1 mV).  $^2$ dBc refers to deciBels relative to the full-scale input (carrier) level of 7 V rms.  $^3$ See Figure 10 for test circuit. All min and max specifications are guaranteed. Specifications subject to change without notice.

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup> Internal Power Dissipation<sup>2</sup>

X, Y and Z Input Voltages . . . . . . VN to VP Output Short Circuit Duration ..... Indefinite Storage Temperature Range Q ..... -65°C to +150°C

| AD734A, B (Industrial)40°C to +85°C             |

|-------------------------------------------------|

| AD734S (Military)55°C to +125°C                 |

| Lead Temperature Range (soldering 60 sec)+300°C |

| Transistor Count                                |

| ESD Rating 500 V                                |

Operating Temperature Range

#### **ORDERING GUIDE**

| Model                                                                   | Temperature                                                                                                | Package                                                         | Package                              |  |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------|--|

|                                                                         | Range                                                                                                      | Description                                                     | Option                               |  |

| AD734AN<br>AD734BN<br>AD734AQ<br>AD734BQ<br>AD734SQ/883B<br>AD734SCHIPS | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-55°C to +125°C<br>-55°C to +125°C | Plastic DIP<br>Plastic DIP<br>Cerdip<br>Cerdip<br>Cerdip<br>Die | N-14<br>N-14<br>Q-14<br>Q-14<br>Q-14 |  |

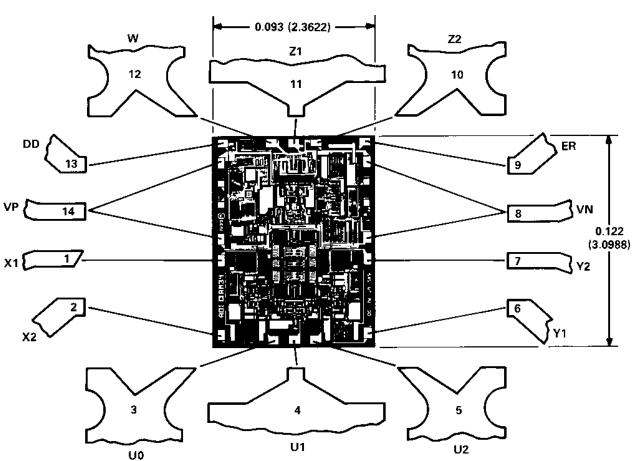

#### **CHIP DIMENSIONS & BONDING DIAGRAM**

Dimensions shown in inches and (mm). (Contact factory for latest dimensions.)

REV. C -3-

<sup>&</sup>lt;sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied.  $^2$ 14-Lead Ceramic DIP:  $\theta_{JA}$  = 110°C/W.

#### **AD734**

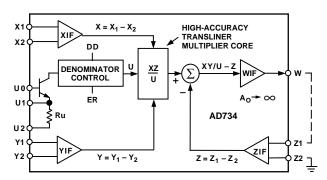

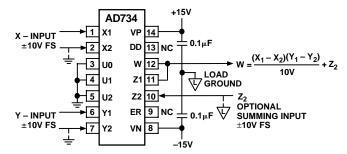

Figure 1. AD734 Block Diagram

#### **FUNCTIONAL DESCRIPTION**

Figure 1 is a simplified block diagram of the AD734. Operation is similar to that of the industry-standard AD534 and in many applications these parts are pin-compatible. The main functional difference is the provision for direct control of the denominator voltage, U, explained fully on the following page. Internal signals are actually in the form of currents, but the function of the AD734 can be understood using voltages throughout, as shown in this figure. Pins are named using upper-case characters (such as X1, Z2) while the *voltages* on these pins are denoted by subscripted variables (for example,  $X_1$ ,  $Z_2$ ).

The AD734's differential X, Y and Z inputs are handled by wideband interfaces that have low offset, low bias current and low distortion. The AD734 responds to the difference signals  $X = X_1 - X_2$ ,  $Y = Y_1 - Y_2$  and  $Z = Z_1 - Z_2$ , and rejects common-mode voltages on these inputs. The X, Y and Z interfaces provide a nominal full-scale (FS) voltage of  $\pm 10$  V, but, due to the special design of the input stages, the linear range of the differential input can be as large as  $\pm 17$  V. Also unlike previous designs, the response on these inputs is not clipped abruptly above  $\pm 15$  V, but drops to a slope of one half.

The bipolar input signals X and Y are multiplied in a translinear core of novel design to generate the product XY/U. The denominator voltage, U, is internally set to an accurate, temperature-stable value of 10 V, derived from a buried-Zener reference. An uncalibrated fraction of the denominator voltage U appears between the voltage reference pin (ER) and the negative supply pin (VN), for use in certain applications where a temperature-compensated voltage reference is desirable. The internal denom-inator, U, can be disabled, by connecting the denominator disable Pin 13 (DD) to the positive supply pin (VP); the denom-inator can then be replaced by a fixed or variable external volt-age ranging from 10 mV to more than 10 V.

The high-gain output op-amp nulls the difference between XY/U and an additional signal Z, to generate the final output W. The actual transfer function can take on several forms, depending on the connections used. The AD734 can perform all of the functions supported by the AD534, and new functions using the direct-division mode provided by the U-interface.

Each input pair (X1 and X2, Y1 and Y2, Z1 and Z2) has a differential input resistance of 50 k $\Omega$ ; this is formed by "real" resistors (not a small-signal approximation) and is subject to a tolerance of  $\pm 20\%$ . The common-mode input resistance is several megohms and the parasitic capacitance is about 2 pF.

The bias currents associated with these inputs are nulled by laser-trimming, such that when one input of a pair is optionally ac-coupled and the other is grounded, the residual offset voltage

is typically less than 5 mV, which corresponds to a bias current of only 100 nA. This low bias current ensures that mismatches in the sources resistances at a pair of inputs does not cause an offset error. These currents remain low over the full temperature range and supply voltages.

The common-mode range of the X, Y and Z inputs does not fully extend to the supply rails. Nevertheless, it is often possible to operate the AD734 with one terminal of an input pair connected to either the positive or negative supply, unlike previous multipliers. The common-mode resistance is several megohms.

The full-scale output of  $\pm 10~V$  can be delivered to a load resistance of 1 k\Omega (although the specifications apply to the standard multiplier load condition of 2 k\Omega). The output amplifier is stable driving capacitive loads of at least 100 pF, when a slight increase in bandwidth results from the peaking caused by this capacitance. The 450 V/µs slew rate of the AD734's output amplifier ensures that the bandwidth of 10 MHz can be maintained up to the full output of 20 V pk-pk. Operation at reduced supply voltages is possible, down to  $\pm 8~V$ , with reduced signal levels.

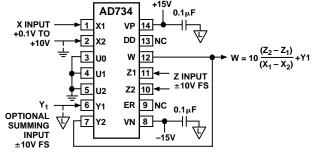

#### **Available Transfer Functions**

The uncommitted (open-loop) transfer function of the AD734 is

$$W = A_O \left\{ \frac{(X_1 - X_2)(Y_1 - Y_2)}{U} - (Z_1 - Z_2) \right\}, \tag{1}$$

where  $A_{\rm O}$  is the open-loop gain of the output op-amp, typically 72 dB. When a negative feedback path is provided, the circuit will force the quantity inside the brackets essentially to zero, resulting in the equation

$$(X_1 - X_2)(Y_1 - Y_2) = U(Z_1 - Z_2)$$

(2)

This is the most useful generalized transfer function for the AD734; it expresses a balance between the product XY and the product UZ. The absence of the output, W, in this equation only reflects the fact that we have not yet specified which of the inputs is to be connected to the op amp output.

Most of the functions of the AD734 (including division, unlike the AD534 in this respect) are realized with  $Z_1$  connected to W. So, substituting W in place of  $Z_1$  in the above equation results in an output.

$$W = \frac{(X_1 - X_2)(Y_1 - Y_2)}{U} + Z_2.$$

(3)

The free input Z2 can be used to sum another signal to the output; in the absence of a product signal, W simply follows the voltage at Z2 with the full 10 MHz bandwidth. When not needed for summation, Z2 should be connected to the ground associated with the load circuit. We can show the allowable polarities in the following shorthand form:

$$\left(\pm W\right) = \frac{\left(\pm X\right)\left(\pm Y\right)}{\left(+U\right)} + \pm Z. \tag{4}$$

In the recommended direct divider mode, the Y input is set to a fixed voltage (typically 10 V) and U is varied directly; it may have any value from 10 mV to 10 V. The magnitude of the ratio X/U cannot exceed 1.25; for example, the peak X-input for U = 1 V is  $\pm 1.25$  V. Above this level, clipping occurs at the positive and negative extremities of the X-input. Alternatively,

-4- REV. C

the AD734 can be operated using the standard (AD534) divider connections (Figure 8), when the negative feedback path is established via the  $Y_2$  input. Substituting W for  $Y_2$  in Equation (2), we get

$$W = U \frac{(Z_2 - Z_1)}{(X_1 - X_2)} + Y_1.$$

(5)

In this case, note that the variable X is now the denominator, and the above restriction ( $X/U \le 1.25$ ) on the magnitude of the X input does not apply. However, X must be positive in order for the feedback polarity to be correct.  $Y_1$  can be used for summing purposes or connected to the load ground if not needed. The shorthand form in this case is

$$\left(\pm W\right) = \left(+U\right) \frac{\left(\pm Z\right)}{\left(+X\right)} + \left(\pm Y\right). \tag{6}$$

In some cases, feedback may be connected to two of the available inputs. This is true for the square-rooting connections (Fig-ure 9), where W is connected to both  $X_1$  and  $Y_2$ . Setting  $X_1 = W$  and  $Y_2 = W$  in Equation (2), and anticipating the possibility of again providing a summing input, so setting  $X_2 = S$  and  $Y_1 = S$ , we find, in shorthand form

$$(\pm W) = \sqrt{(+U)(+Z)} + (\pm S). \tag{7}$$

This is seen more generally to be the geometric-mean function, since both U and Z can be variable; operation is restricted to one quadrant. Feedback may also be taken to the U-interface. Full details of the operation in these modes is provided in the appropriate section of this data sheet.

#### **Direct Denominator Control**

A valuable new feature of the AD734 is the provision to replace the internal denominator voltage, U, with any value from +10 mV to +10 V. This can be used (1) to simply alter the multiplier scaling, thus improve accuracy and achieve reduced noise levels when operating with small input signals; (2) to implement an accurate two-quadrant divider, with a 1000:1 gain range and an asymptotic gain-bandwidth product of 200 MHz; (3) to achieve certain other special functions, such as AGC or rms.

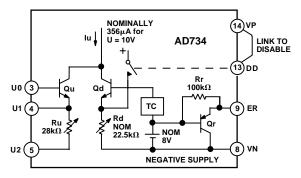

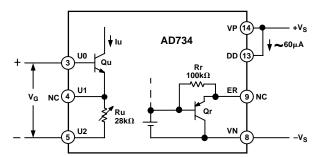

Figure 2 shows the internal circuitry associated with denominator control. Note first that the denominator is actually proportional to a current, Iu, having a nominal value of 356  $\mu A$  for U = 10 V, whereas the primary reference is a voltage, generated by a buried-Zener circuit and laser-trimmed to have a very low temperature coefficient. This voltage is nominally 8 V with a tolerance of  $\pm 10\%$ .

Figure 2. Denominator Control Circuitry

After temperature-correction (block TC), the reference voltage is applied to transistor Qd and trimmed resistor Rd, which generate the required reference current. Transistor Qu and resistor Ru are not involved in setting up the internal denominator, and their associated control pins U0, U1 and U2 will normally be grounded. The reference voltage is also made available, via the 100 k $\Omega$  resistor Rr, at Pin 9 (ER); the purpose of Qr is explained below.

When the control pin DD (denominator disable) is connected to VP, the internal source of Iu is shut off, and the collector current of Qu must provide the denominator current. The resistor Ru is laser-trimmed such that the multiplier denominator is exactly equal to the voltage across it (that is, across pins U1 and U2). Note that this trimming only sets up the correct internal ratio; the absolute value of Ru (nominally 28 k $\Omega$ ) has a tolerance of  $\pm 20\%$ . Also, the alpha of Qu, (typically 0.995) which might be seen as a source of scaling error, is canceled by the alpha of other transistors in the complete circuit.

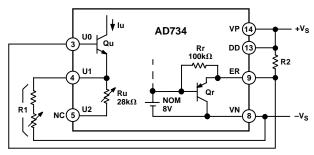

In the simplest scheme (Figure 3), an externally-provided control voltage,  $V_G$ , is applied directly to U0 and U2 and the resulting voltage across Ru is therefore reduced by one  $V_{BE}$ . For example, when  $V_G = 2$  V, the actual value of U will be about 1.3 V. This error will not be important in some closed-loop applications, such as automatic gain control (AGC), but clearly is not acceptable where the denominator value must be well-defined. When it is required to set up an accurate, fixed value of U, the on-chip reference may be used. The transistor Qr is provided to cancel the  $V_{BE}$  of Qu, and is biased by an external resistor, R2, as shown in Figure 4. R1 is chosen to set the desired value of U and consists of a fixed and adjustable resistor.

Figure 3. Low-Accuracy Denominator Control

Figure 4. Connections for a Fixed Denominator

Table I shows useful values of the external components for setting up nonstandard denominator values.

#### **AD734**

Table I. Component Values for Setting Up Nonstandard Denominator Values

| Denominator | R1 (Fixed) | R1 (Variable) | R2     |  |  |

|-------------|------------|---------------|--------|--|--|

| 5 V         | 34.8 kΩ    | 20 kΩ         | 120 kΩ |  |  |

| 3 V         | 64.9 kΩ    | 20 kΩ         | 220 kΩ |  |  |

| 2 V         | 86.6 kΩ    | 50 kΩ         | 300 kΩ |  |  |

| 1 V         | 174 kΩ     | 100 kΩ        | 620 kΩ |  |  |

The denominator can also be current controlled, by grounding Pin 3 (U0) and withdrawing a current of Iu from Pin 4 (U1). The nominal scaling relationship is  $U = 28 \times Iu$ , where u is expressed in volts and Iu is expressed in milliamps. Note, however, that while the linearity of this relationship is very good, it is subject to a scale tolerance of  $\pm 20\%$ . Note that the common mode range on Pins 3 through 5 actually extends from 4 V to 36 V below VP, so it is not necessary to restrict the connection of U0 to ground if it should be desirable to use some other voltage.

The output ER may also be buffered, re-scaled and used as a general-purpose reference voltage. It is generated with respect to the negative supply line Pin 8 (VN), but this is acceptable when driving one of the signal interfaces. An example is shown in Figure 12, where a fixed numerator of 10 V is generated for a divider application. There,  $Y_2$  is tied to VN but  $Y_1$  is 10 V above this; therefore the common-mode voltage at this interface is still 5 V above VN, which satisfies the internal biasing requirements (see Specifications table).

#### **OPERATION AS A MULTIPLIER**

All of the connection schemes used in this section are essentially identical to those used for the AD534, with which the AD734 is pin-compatible. The only precaution to be noted in this regard is that in the AD534, Pins 3, 5, 9, and 13 are not internally connected and Pin 4 has a slightly different purpose. In many cases, an AD734 can be directly substituted for an AD534 with immediate benefits in static accuracy, distortion, feedthrough, and speed. Where Pin 4 was used in an AD534 application to achieve a reduced denominator voltage, this function can now be much more precisely implemented with the AD734 using alternative connections (see Direct Denominator Control, page 5).

Operation from supplies down to  $\pm 8$  V is possible. The supply current is essentially independent of voltage. As is true of all high speed circuits, careful power-supply decoupling is important in maintaining stability under all conditions of use. The decoupling capacitors should always be connected to the load ground, since the load current circulates in these capacitors at high frequencies. Note the use of the special symbol (a triangle with the letter 'L' inside it) to denote the load ground.

#### **Standard Multiplier Connections**

Figure 5 shows the basic connections for multiplication. The X and Y inputs are shown as optionally having their negative nodes grounded, but they are fully differential, and in many applications the grounded inputs may be reversed (to facilitate interfacing with signals of a particular polarity, while achieving some desired output polarity) or both may be driven.

The AD734 has an input resistance of 50 k $\Omega$   $\pm$  20% at the X, Y, and Z interfaces, which allows ac-coupling to be achieved with moderately good control of the high-pass (HP) corner frequency; a capacitor of 0.1  $\mu$ F provides a HP corner frequency

Figure 5. Basic Multiplier Circuit

of 32 Hz. When a tighter control of this frequency is needed, or when the HP corner is above about 100 kHz, an external resistor should be added across the pair of input nodes.

At least one of the two inputs of any pair must be provided with a dc path (usually to ground). The careful selection of ground returns is important in realizing the full accuracy of the AD734. The Z2 pin will normally be connected to the load ground, which may be remote, in some cases. It may also be used as an optional summing input (see Equations (3) and (4), above) having a nominal FS input of  $\pm 10$  V and the full 10 MHz bandwidth.

In applications where high absolute accuracy is essential, the scaling error caused by the finite resistance of the signal source(s) may be troublesome; for example, a 50  $\Omega$  source resistance at just one input will introduce a gain error of -0.1%; if both the X- and Y-inputs are driven from 50  $\Omega$  sources, the scaling error in the product will be -0.2%. Provided the source resistance(s) are known, this gain error can be completely compensated by including the appropriate resistance (50  $\Omega$  or  $100 \Omega$ , respectively, in the above cases) between the output W (Pin 12) and the Z1 feedback input (Pin 11). If Rx is the total source resistance associated with the X1 and X2 inputs, and Ry is the total source resistance associated with the Y1 and Y2 inputs, and neither Rx nor Ry exceeds 1 k $\Omega$ , a resistance of Rx+Ry in series with pin Z1 will provide the required gain restoration.

Pins 9 (ER) and 13 (DD) should be left unconnected in this application. The U-inputs (Pins 3, 4 and 5) are shown connected to ground; they may alternatively be connected to VN, if desired. In applications where Pin 2 (X2) happens to be driven with a high-amplitude, high-frequency signal, the capacitive coupling to the denominator control circuitry via an ungrounded Pin 3 can cause high-frequency distortion. However, the AD734 can be operated without modification in an AD534 socket, and these three pins left unconnected, with the above caution noted.

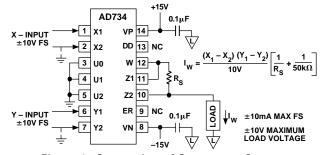

Figure 6. Conversion of Output to a Current

#### **Current Output**

It may occasionally be desirable to convert the output voltage to a current. In correlation applications, for example, multiplication is followed by integration; if the output is in the form of a current, a simple grounded capacitor can perform this function. Figure 6 shows how this can be achieved. The op amp forces the voltage across Z1 and Z2, and thus across the resistor  $R_{\rm S}$ , to be the product XY/U. Note that the input resistance of the Z interface is in shunt with  $R_{\rm S}$ , which must be calculated accordingly.

The smallest FS current is simply  $\pm 10~V/50~k\Omega$ , or  $\pm 200~\mu A$ , with a tolerance of about 20%. To guarantee a 1% conversion tolerance without adjustment,  $R_S$  must be less than 2.5 k $\Omega$ . The maximum full scale output current should be limited to about  $\pm 10~mA$  (thus,  $R_S = 1~k\Omega$ ). This concept can be applied to all connection modes, with the appropriate choice of terminals.

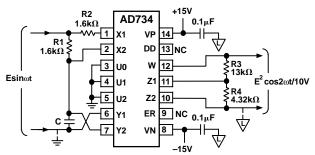

#### Squaring and Frequency-Doubling

Squaring of an input signal, E, is achieved simply by connecting the X and Y inputs in parallel; the phasing can be chosen to produce an output of  $E^2/U$  or  $-E^2/U$  as desired. The input may have either polarity, but the basic output will either always be positive or negative; as for multiplication, the Z2 input may be used to add a further signal to the output.

When the input is a sine wave, a squarer behaves as a frequency-doubler, since

$$(Esinwt)^2 = E^2 (1 - cos2wt)/2$$

(8)

Equation (8) shows a dc term at the output which will vary strongly with the amplitude of the input, E. This dc term can be avoided using the connection shown in Figure 7, where an RC-network is used to generate two signals whose product has no dc term. The output is

$$W = 4 \left\{ \frac{E}{\sqrt{2}} \sin\left(wt + \frac{\pi}{4}\right) \right\} \left\{ \frac{E}{\sqrt{2}} \sin\left(wt - \frac{\pi}{4}\right) \right\} \left( \frac{1}{10 \ V} \right) \tag{9}$$

for w = 1/CR1, which is just

$$W = E^2(\cos 2wt)/(10 \text{ V})$$

(10)

which has no dc component. To restore the output to  $\pm 10~V$  when E=10~V, a feedback attenuator with an approximate ratio of 4 is used between W and Z1; this technique can be used wherever it is desired to achieve a higher overall gain in the transfer function.

In fact, the values of R3 and R4 include additional compensation for the effects of the 50  $k\Omega$  input resistance of all three interfaces; R2 is included for a similar reason. These resistor values should not be altered without careful calculation of the consequences; with the values shown, the center frequency  $f_0$  is 100~kHz for C=1~nF. The amplitude of the output is only a weak function of frequency: the output amplitude will be 0.5% too low at  $f=0.9f_0$  and  $f=1.1f_0$ . The cross-connection is simply to produce the cosine output with the sign shown in Equation (10); however, the sign in this case will rarely be important.

Figure 7. Frequency Doubler

#### **OPERATION AS A DIVIDER**

The AD734 supports two methods for performing analog division. The first is based on the use of a multiplier in a feedback loop. This is the standard mode recommended for multipliers having a fixed scaling voltage, such as the AD534, and will be described in this Section. The second uses the AD734's unique capability for externally varying the scaling (denominator) voltage directly, and will be described in the next section.

#### **Feedback Divider Connections**

Figure 8 shows the connections for the standard (AD534) divider mode. Feedback from the output, W, is now taken to the Y2 (inverting) input, which, provided that the X-input is positive, establishes a negative feedback path. Y1 should normally be connected to the ground associated with the load circuit, but may optionally be used to sum a further signal to the output. If desired, the polarity of the Y-input connections can be reversed, with W connected to Y1 and Y2 used as the optional summation input. In this case, either the polarity of the X-input connections must be reversed, or the X-input voltage must be negative.

Figure 8. Standard (AD534) Divider Connection

The numerator input, which is differential and can have either polarity, is applied to pins Z1 and Z2. As with all dividers based on feedback, the bandwidth is directly proportional to the denominator, being 10 MHz for X = 10 V and reducing to 100 kHz for X = 100 mV. This reduction in bandwidth, and the increase in output noise (which is inversely proportional to the denominator voltage) preclude operation much below a denominator of 100 mV. Division using direct control of the denominator (Figure 10) does not have these shortcomings.

REV. C \_7\_

Figure 9. Connection for Square Rooting

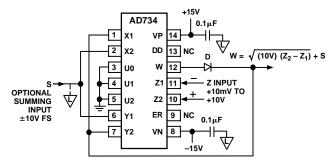

#### **Connections for Square-Rooting**

The AD734 may be used to generate an output proportional to the square-root of an input using the connections shown in Figure 9. Feedback is now via both the X and Y inputs, and is always negative because of the reversed-polarity between these two inputs. The Z input must have the polarity shown, but because it is applied to a differential port, either polarity of input can be accepted with reversal of Z1 and Z2, if necessary. The diode D, which can be any small-signal type (1N4148 being suitable) is included to prevent a latching condition which could occur if the input momentarily was of the incorrect polarity of the input, the output will be always negative.

Note that the loading on the output side of the diode will be provided by the 25 k $\Omega$  of input resistance at X1 and Y2, and by the user's load. In high speed applications it may be beneficial to include further loading at the output (to 1 k $\Omega$  minimum) to speed up response time. As in previous applications, a further signal, shown here as S, may be summed to the output; if this option is not used, this node should be connected to the load ground.

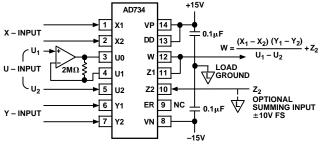

#### **DIVISION BY DIRECT DENOMINATOR CONTROL**

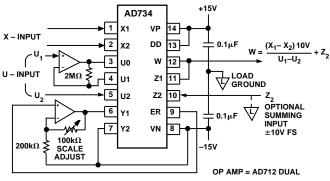

The AD734 may be used as an analog divider by directly varying the denominator voltage. In addition to providing much higher accuracy and bandwidth, this mode also provides greater flexibility, because all inputs remain available. Figure 10 shows the connections for the general case of a three-input multiplier divider, providing the function

$$W = \frac{(X_1 - X_2)(Y_1 - Y_2)}{(U_1 - U_2)} + Z_2, \tag{11}$$

where the X, Y, and Z signals may all be positive or negative, but the difference  $U = U_1 - U_2$  must be positive and in the range +10 mV to +10 V. If a negative denominator voltage must be used, simply ground the noninverting input of the op amp. As previously noted, the X input must have a magnitude of less than 1.25U.

Figure 10. Three-Variable Multiplier/Divider Using Direct Denominator Control

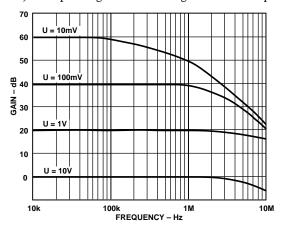

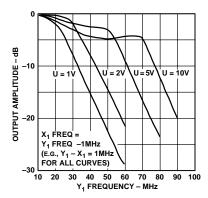

This connection scheme may also be viewed as a variable-gain element, whose output, in response to a signal at the X input, is controllable by both the Y input (for attenuation, using Y less than U) and the U input (for amplification, using U less than Y). The ac performance is shown in Figure 11; for these results, Y was maintained at a constant 10 V. At U = 10 V, the gain is unity and the circuit bandwidth is a full 10 MHz. At U = 1 V, the gain is 20 dB and the bandwidth is essentially unaltered. At U = 100 mV, the gain is 40 dB and the bandwidth is 2 MHz. Finally, at U = 10 mV, the gain is 60 dB and the bandwidth is 250 kHz, corresponding to a 250 MHz gain-bandwidth product.

Figure 11. Three-Variable Multiplier/Divider Performance

The 2  $M\Omega$  resistor is included to improve the accuracy of the gain for small denominator voltages. At high gains, the X input offset voltage can cause a significant output offset voltage. To eliminate this problem, a low-pass feedback path can be used from W to X2; see Figure 13 for details.

Where a numerator of 10 V is needed, to implement a two-quadrant divider with fixed scaling, the connections shown in Figure 12 may be used. The reference voltage output appearing between Pin 9 (ER) and Pin 8 (VN) is amplified and buffered by the second op amp, to impose 10 V across the Y1/Y2 input. Note that Y2 is connected to the negative supply in this application. This is permissible because the common-mode voltage is still high enough to meet the internal requirements. The transfer function is

$$W = 10 V \left( \frac{X_1 - X_2}{U_1 - U_2} \right) + Z_2. \tag{12}$$

The ac performance of this circuit remains as shown in Figure 11.

Figure 12. Two-Quadrant Divider with Fixed 10 V Scaling

–8– REV. C

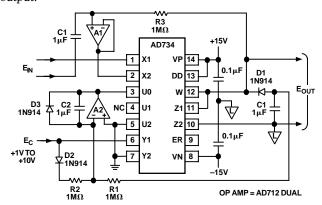

#### A PRECISION AGC LOOP

The variable denominator of the AD734 and its high gainbandwidth product make it an excellent choice for precise automatic gain control (AGC) applications. Figure 13 shows a suggested method. The input signal,  $E_{\text{IN}}$ , which may have a peak amplitude of from 10 mV to 10 V at any frequency from 100 Hz to 10 MHz, is applied to the X input, and a fixed positive voltage E<sub>C</sub> to the Y input. Op amp A2 and capacitor C2 form an integrator having a current summing node at its inverting input. (The AD712 dual op amp is a suitable choice for this application.) In the absence of an input, the current in D2 and R2 causes the integrator output to ramp negative, clamped by diode D3, which is included to reduce the time required for the loop to establish a stable, calibrated, output level once the circuit has received an input signal. With no input to the denominator (U0 and U2), the gain of the AD734 is very high (about 70 dB), and thus even a small input causes a substantial output.

Figure 13. Precision AGC Loop

Diode D1 and C1 form a peak detector, which rectifies the output and causes the integrator to ramp positive. When the current in R1 balances the current in R2, the integrator output holds the denominator output at a constant value. This occurs when there is sufficient gain to raise the amplitude of  $E_{\rm IN}$  to that required to establish an output amplitude of  $E_{\rm C}$  over the range of +1 V to +10 V. The X input of the AD734, which has finite offset voltage, could be troublesome at the output at high gains. The output offset is reduced to that of the X input (one or two millivolts) by the offset loop comprising R3, C3, and buffer A1. The low pass corner frequency of 0.16 Hz is transformed to a high-pass corner that is multiplied by the gain (for example,  $160~{\rm Hz}$  at a gain of 1000).

In applications not requiring operation down to low frequencies, amplifier A1 can he eliminated, but the AD734's input resistance of 50 k $\Omega$  between X1 and X2 will reduce the time constant and increase the input offset. Using a non-polar 20  $\mu F$  tantalum capacitor for C1 will result in the same unity-gain high-pass corner; in this case, the offset gain increases to 20, still very acceptable.

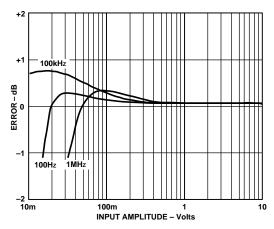

Figure 14 shows the error in the output for sinusoidal inputs at 100 Hz, 100 kHz, and 1 MHz, with  $E_{\rm C}$  set to +10 V. The output error for any frequency between 300 Hz and 300 kHz is similar to that for 100 kHz. At low signal frequencies and low input amplitudes, the dynamics of the control loop determine the gain error and distortion; at high frequencies, the 200 MHz gain-bandwidth product of the AD734 limit the available gain.

The output amplitude tracks  $E_{C}$  over the range +1 V to slightly more than +10 V.

Figure 14. AGC Amplifier Output Error vs. Input Voltage

## WIDEBAND RMS-DC CONVERTER USING U INTERFACE

The AD734 is well suited to such applications as implicit RMS-DC conversion, where the AD734 implements the function

$$V_{RMS} = \frac{avg\left[V_{IN}^{2}\right]}{V_{RMS}} \tag{13}$$

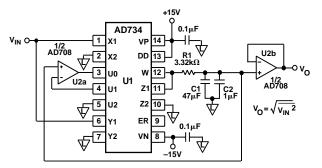

using its direct divide mode. Figure 15 shows the circuit.

Figure 15. A 2-Chip, Wideband RMS-DC Converter

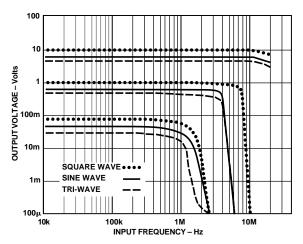

In this application, the AD734 and an AD708 dual op amp serve as a 2-chip RMS-DC converter with a 10 MHz bandwidth. Figure 16 shows the circuit's performance for square-, sine-, and triangle-wave inputs. The circuit accepts signals as high as 10 V p-p with a crest factor of 1 or 1 V p-p with a crest factor of 10. The circuit's response is flat to 10 MHz with an input of 10 V, flat to almost 5 MHz for an input of 1 V, and to almost 1 MHz for inputs of 100 mV. For accurate measurements of input levels below 100 mV, the AD734's output offset (Z interface) voltage, which contributes a dc error, must be trimmed out.

In Figure 15's circuit, the AD734 squares the input signal, and its output  $(V_{\rm IN}^2)$  is averaged by a low-pass filter that consists of R1 and C1 and has a corner frequency of 1 Hz. Because of the implicit feedback loop, this value is both the output value,  $V_{\rm RMS}$ , and the denominator in Equation (13). U2a and U2b, an AD708 dual dc precision op amp, serve as unity-gain buffers, supplying both the output voltage and driving the U interface.

REV. C \_9\_

## **AD734**

Figure 16. RMS-DC Converter Performance

#### LOW DISTORTION MIXER

The AD734's low noise and distortion make it especially suitable for use as a mixer, modulator, or demodulator. Although the AD734's –3 dB bandwidth is typically 10 MHz and is established by the output amplifier, the bandwidth of its X and Y interfaces and the multiplier core are typically in excess of 40 MHz. Thus, provided that the desired output signal is less than 10 MHz, as would typically be the case in demodulation, the AD734 can be used with both its X and Y input signals as high as 40 MHz. One test of mixer performance is to linearly combine two closely spaced, equal-amplitude sinusoidal signals and then mix them with a third signal to determine the mixer's 2-tone Third-Order Intermodulation Products.

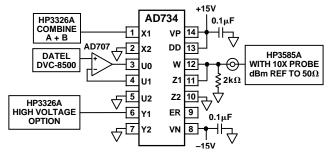

Figure 17. AD734 Mixer Test Circuit

Figure 17 shows a test circuit for measuring the AD734's performance in this regard. In this test, two signals, at 10.05 MHz and 9.95 MHz are summed and applied to the AD734's X interface. A second 9 MHz signal is applied to the AD734's Y interface. The voltage at the U interface is set to 2 V to use the full dynamic range of the AD734. That is, by connecting the W and Z1 pins together, grounding the Y2 and X2 pins, and setting U = 2 V, the overall transfer function is

$$W = \frac{X_1 Y_1}{2 V} \tag{14}$$

and W can be as high as 20 V p-p when X1 = 2 V p-p and Y1 = 10 V p-p. The 2 V p-p signal level corresponds to +10 dBm into a 50  $\Omega$  input termination resistor connected from X1 or Y1 to ground.

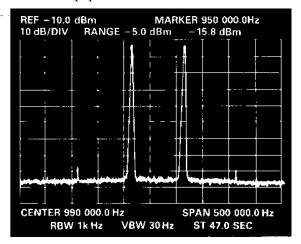

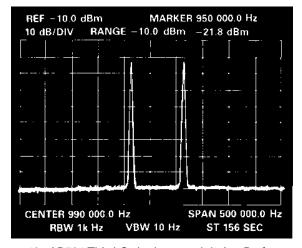

If the two X1 inputs are at frequencies  $f_1$  and  $f_2$  and the frequency at the Y1 input is  $f_0$ , then the two-tone third-order intermodulation products should appear at frequencies  $2f_1 - f_2 \pm f_0$  and  $2f_2 - f_1 \pm f_0$ . Figures 18 and 19 show the output spectra of the AD734 with  $f_1 = 9.95$  MHz,  $f_2 = 10.05$  MHz, and  $f_0 = 9.00$  MHz for a signal level of  $f_1$  &  $f_2$  of 6 dBm and  $f_0$  of +24 dBm in Figure 18 and  $f_1$  &  $f_2$  of 0 dBm and  $f_0$  of +24 dBm in Figure 19. This performance is *without* external trimming of the AD734's X and Y input-offset voltages.

The possible Two Tone Intermodulation Products are at  $2 \times 9.95$  MHz – 10.05 MHz ± 9.00 MHz and  $2 \times 10.05$  – 9.95 MHz ± 9.00 MHz; of these only the third-order products at 0.850 MHz and 1.150 MHz are within the 10 MHz bandwidth of the AD734; the desired output signals are at 0.950 MHz and 1.050 MHz. Note that the difference (Figure 18) between the desired outputs and third-order products is approximately 78 dB, which corresponds to a computed third-order intercept point of +46 dBm.

Figure 18. AD734 Third-Order Intermodulation Performance for  $f_1 = 9.95$  MHz,  $f_2 = 10.05$  MHz, and  $f_0 = 9.00$  MHz and for Signal Levels of  $f_1$  &  $f_2$  of 6 dBm and  $f_0$  of +24 dBm. All Displayed Signal Levels Are Attenuated 20 dB by the 10X Probe Used to Measure the Mixer's Output

Figure 19. AD734 Third-Order Intermodulation Performance for  $f_1 = 9.95$  MHz,  $f_2 = 10.05$  MHz, and  $f_0 = 9.00$  MHz and for Signal Levels of  $f_1 \& f_2$  of 0 dBm and  $f_0$  of +24 dBm. All Displayed Signal Levels Are Attenuated 20 dB by the 10X Probe Used to Measure the Mixer's Output

–10– REV. C

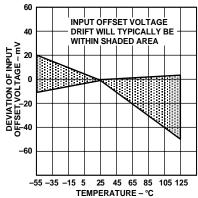

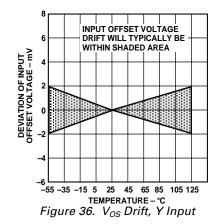

## Typical Characteristics—AD734

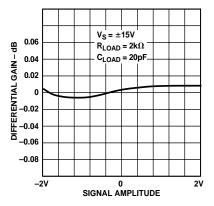

Figure 20. Differential Gain at 3.58 MHz and  $R_L = 2 \text{ k}\Omega$

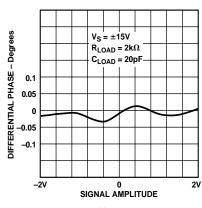

Figure 21. Differential Phase at 3.58 MHz and  $R_L = 2 k\Omega$

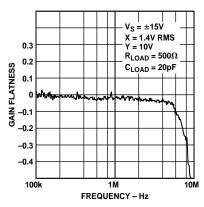

Figure 22. Gain Flatness, 300 kHz to 10 MHz,  $R_L = 500 \Omega$

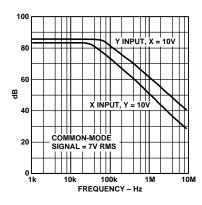

Figure 23. CMRR vs. Frequency

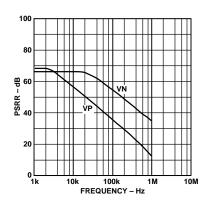

Figure 24. PSRR vs. Frequency

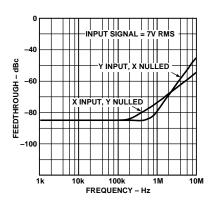

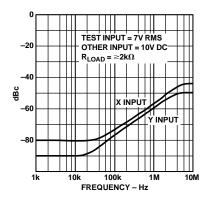

Figure 25. Feedthrough vs. Frequency

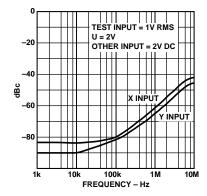

Figure 26. THD vs. Frequency, U = 2 V

Figure 27. THD vs. Frequency, U = 10 V

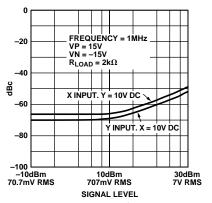

Figure 28. THD vs. Signal Level, f = 1 MHz

REV. C -11-

## **AD734-Typical Characteristics**

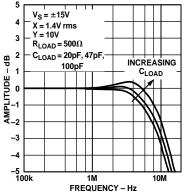

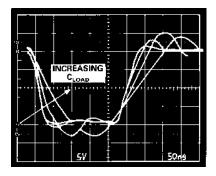

Figure 29. Gain vs. Frequency vs.  $C_{LOAD}$

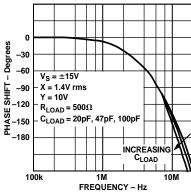

Figure 30. Phase vs. Frequency vs. C<sub>LOAD</sub>

Figure 31. Pulse Response vs.  $C_{LOAD}$ ,  $C_{LOAD} = 0$  pF, 47 pF, 100 pF, 200 pF

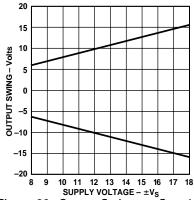

Figure 32. Output Swing vs. Supply Voltage

Figure 33. Output Amplitude vs. Input Frequency, When Used as Demodulator

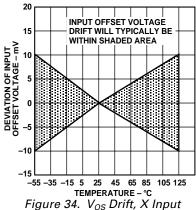

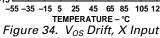

Figure 35. Vos Drift, Z Input

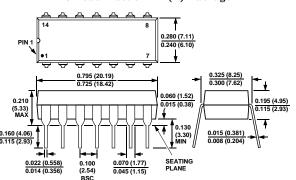

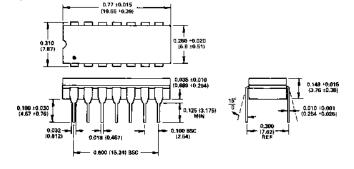

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 14-Lead Plastic DIP (N) Package

#### 14-Lead Ceramic DIP (Q) Package

REV. C -12-