# Quad 3000 V/µs, 35 mW Current Feedback Amplifier

AD8004

**FEATURES**

**High Speed**

250 MHz -3 dB Bandwidth (G = +1)

3000 V/μs Slew Rate

21 ns Settling Time to 0.1%

1.8 ns Rise Time for 2 V Step

**Low Power**

3.5 mA/Amp Power Supply Current (35 mW/Amp)

**Single Supply Operation**

Fully Specified for +5 V Supply

Good Video Specifications (R<sub>L</sub> = 150  $\Omega$ , G = +2)

Gain Flatness 0.1 dB to 30 MHz

0.04% Differential Gain Error

0.10° Differential Phase Error

**Low Distortion**

-78 dBc THD at 5 MHz

-61 dBc THD at 20 MHz

High Output Current of 50 mA

Available in a 14-Lead Plastic DIP and SOIC

**APPLICATIONS**

**Image Scanners**

**Active Filters**

Video Switchers

**Special Effects**

#### PRODUCT DESCRIPTION

The AD8004 is a quad, low power, high speed amplifier designed to operate on single or dual supplies. It utilizes a current feedback architecture and features high slew rate of  $3000 \text{ V/}\mu\text{s}$  making the AD8004 ideal for handling large amplitude pulses. Additionally, the AD8004 provides gain flatness of 0.1 dB to

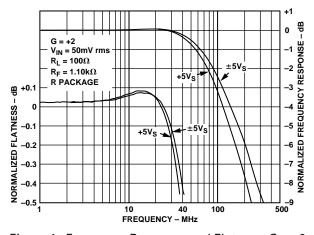

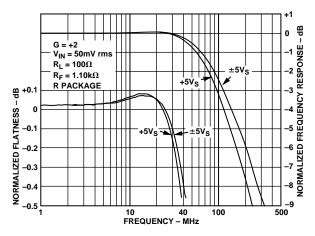

Figure 1. Frequency Response and Flatness, G = +2

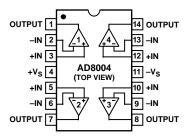

#### CONNECTION DIAGRAM

Plastic DIP (N) and SOIC (R) Packages

30 MHz while offering differential gain and phase error of 0.04% and 0.10°. This makes the AD8004 suitable for video electronics such as cameras and video switchers.

The AD8004 offers low power of 3.5 mA/amplifier and can run on a single +4 V to +12 V power supply, while being capable of delivering up to 50 mA of load current. All this is offered in a small 14-lead plastic DIP or 14-lead SOIC package. These features make this amplifier ideal for portable and battery powered applications where size and power are critical.

The outstanding bandwidth of 250 MHz along with 3000 V/ $\mu$ s of slew rate make the AD8004 useful in many general purpose, high speed applications where dual power supplies of up to  $\pm 6$  V and single supplies from 4 V to 12 V are needed. The AD8004 is available in the industrial temperature range of -40°C to +85°C.

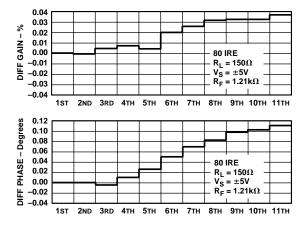

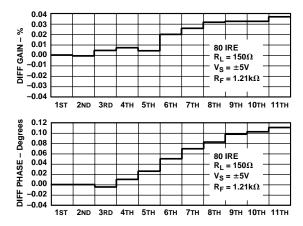

Figure 2. Differential Gain/Differential Phase

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

# $\label{eq:continuous} \textbf{AD8004-SPECIFICATIONS} \ (@\ \textbf{T}_A = +\ 25^{\circ}\textbf{C},\ \textbf{V}_S = \pm\ 5\ \textbf{V},\ \textbf{R}_L = 100\ \Omega,\ \text{unless otherwise noted})$

|                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AD8004A |                                                                      |                                     |                                                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------|--|

| Parameter                                                                                                                                                                                                                                                          | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Min     | Typ                                                                  | Max                                 | Units                                                             |  |

| DYNAMIC PERFORMANCE  -3 dB Bandwidth, N Package  Bandwidth for 0.1 dB Flatness Slew Rate  Settling Time to 0.1% Rise & Fall Time (10% to 90%)                                                                                                                      | $G = +2$ , $R_F = 698 \Omega$<br>$G = +1$ , $R_F = 806 \Omega$<br>G = +2<br>$G = +2$ , $V_O = 4 \text{ V Step}$<br>$G = -2$ , $V_O = 4 \text{ V Step}$<br>$G = +2$ , $V_O = 2 \text{ V Step}$<br>$G = +2$ , $V_O = 2 \text{ V Step}$                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | 185<br>250<br>30<br>3000<br>2000<br>21<br>1.8                        |                                     | MHz<br>MHz<br>MHz<br>V/µs<br>V/µs<br>ns                           |  |

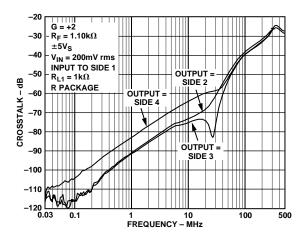

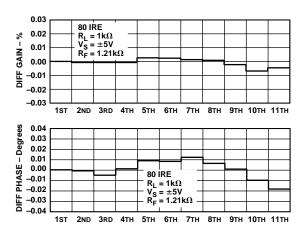

| NOISE/HARMONIC PERFORMANCE Total Harmonic Distortion Crosstalk, R Package, Worst Case Crosstalk, N Package, Worst Case Input Voltage Noise Input Current Noise  Differential Gain Error Differential Phase Error Differential Phase Error Differential Phase Error | $\begin{split} f_C &= 5 \text{ MHz},  V_O = 2 \text{ V p-p},  R_L = 1 \text{ k}\Omega \\ f &= 5 \text{ MHz},  G = +2,  R_L = 1 \text{ k}\Omega \\ f &= 5 \text{ MHz},  G = +2,  R_L = 1 \text{ k}\Omega \\ f &= 5 \text{ MHz},  G = +2,  R_L = 1 \text{ k}\Omega \\ f &= 10 \text{ kHz} \\ f &= 10 \text{ kHz},  +\text{In} \\ & -\text{In} \\ \text{NTSC},  G &= +2,  R_L = 150  \Omega,  R_F = 1.21 \text{ k}\Omega \\ \text{NTSC},  G &= +2,  R_L = 150  \Omega,  R_F = 1.21 \text{ k}\Omega \\ \text{NTSC},  G &= +2,  R_L = 1 \text{ k}\Omega,  R_F = 1.21 \text{ k}\Omega \\ \text{NTSC},  G &= +2,  R_L = 1 \text{ k}\Omega,  R_F = 1.21 \text{ k}\Omega \end{split}$ |         | -78<br>-69<br>-64<br>1.5<br>38<br>38<br>0.04<br>0.10<br>0.01<br>0.04 |                                     | dBc<br>dB<br>dB<br>nV/√Hz<br>pA/√Hz<br>pA/√Hz<br>%<br>Degree<br>% |  |

| DC PERFORMANCE Input Offset Voltage  Offset Drift -Input Bias Current  +Input Bias Current  Open-Loop Transresistance                                                                                                                                              | $T_{MIN}$ - $T_{MAX}$ $T_{MIN}$ - $T_{MAX}$ $T_{MIN}$ - $T_{MAX}$ $V_{O} = \pm 2.5 \text{ V}$ $T_{MIN}$ - $T_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 170     | 1.0<br>1.5<br>15<br>35<br>40<br>290<br>220                           | 3.5<br>5<br>90<br>110<br>110<br>120 | mV<br>mV<br>μV/°C<br>±μA<br>±μA<br>±μA<br>kΩ<br>kΩ                |  |

| INPUT CHARACTERISTICS Input Resistance Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio Offset Voltage —Input Current +Input Current                                                                                                  | +Input<br>-Input<br>+Input<br>$V_{CM} = \pm 2.5 \text{ V}$ $V_{CM} = \pm 2.5 \text{ V}, T_{MIN} - T_{MAX}$ $V_{CM} = \pm 2.5 \text{ V}, T_{MIN} - T_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52      | 2<br>50<br>1.5<br>3.2<br>58<br>1<br>12                               |                                     | MΩ<br>Ω<br>pF<br>±V<br>dB<br>μA/V<br>μA/V                         |  |

| OUTPUT CHARACTERISTICS Output Voltage Swing Output Current Short Circuit Current                                                                                                                                                                                   | $R_L = 150 \Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 100     | 3.9<br>50<br>180                                                     |                                     | ±V<br>mA<br>mA                                                    |  |

| POWER SUPPLY Operating Range Total Quiescent Current  Power Supply Rejection Ratio –Input Current +Input Current                                                                                                                                                   | $T_{MIN}-T_{MAX}$ $\Delta V_{S} = \pm 2 V$ $T_{MIN}-T_{MAX}$ $T_{MIN}-T_{MAX}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ±2.0    | 14<br>16<br>62<br>0.5<br>4                                           | ±6.0<br>17<br>20                    | V<br>mA<br>mA<br>dB<br>μA/V<br>μA/V                               |  |

Specifications subject to change without notice.

-2- REV. B

(@  $T_{A}=+$   $25^{\circ}C,\,V_{S}=+5$  V,  $R_{L}=100~\Omega,$  unless otherwise noted)

| Parameter                                              | Conditions                                                                | Min   | Typ Max         | Units          |

|--------------------------------------------------------|---------------------------------------------------------------------------|-------|-----------------|----------------|

| DYNAMIC PERFORMANCE  -3 dB Bandwidth, N Package        | $G = +2, R_F = 698 \Omega$<br>$G = +1, R_F = 806 \Omega$                  |       | 150<br>200      | MHz<br>MHz     |

| Bandwidth for 0.1 dB Flatness                          | G = +2                                                                    |       | 30              | MHz            |

| Slew Rate                                              | $G = +2, V_O = 2 \text{ V Step}$<br>$G = +2, V_O = 2 \text{ V Step}$      |       | 1100<br>24      | V/µs           |

| Settling Time to 0.1%<br>Rise & Fall Time (10% to 90%) | $G = +2$ , $V_O = 2$ V Step<br>$G = +2$ , $V_O = 2$ V Step                |       | 2.3             | ns<br>ns       |

| NOISE/HARMONIC PERFORMANCE                             |                                                                           |       |                 |                |

| Total Harmonic Distortion                              | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p}, R_L = 1 \text{ k}\Omega$     |       | -65             | dBc            |

| Crosstalk, R Package, Worst Case                       | $f = 5 \text{ MHz}, G = +2, R_L = 1 \text{ k}\Omega$                      |       | -69             | dB             |

| Crosstalk, N Package, Worst Case                       | $f = 5 \text{ MHz}, G = +2, R_L = 1 \text{ k}\Omega$                      |       | -64             | dB             |

| Input Voltage Noise                                    | f = 10  kHz                                                               |       | 1.5<br>38       | nV/√Hz         |

| Input Current Noise                                    | f = 10  kHz, +In                                                          |       | pA/√Hz          |                |

| D:00 - : 1 C : E                                       | -In                                                                       |       | 38              | $pA/\sqrt{Hz}$ |

| Differential Gain Error                                | NTSC, $G = +2$ , $R_L = 150 \Omega$ , $R_F = 1.21 k\Omega$                |       | 0.06            | %<br>D         |

| Differential Phase Error                               | NTSC, $G = +2$ , $R_L = 150 \Omega$ , $R_F = 1.21 k\Omega$                |       | 0.25            | Degree         |

| Differential Gain Error Differential Phase Error       | NTSC, $G = +2$ , $R_L = 1 \text{ k}\Omega$ , $R_F = 1.21 \text{ k}\Omega$ |       | 0.01            | %<br>Dograd    |

|                                                        | NTSC, G = +2, $R_L$ = 1 kΩ, $R_F$ = 1.21 kΩ                               |       | 0.08            | Degree         |

| DC PERFORMANCE                                         |                                                                           |       | 1.0 2.5         | X7             |

| Input Offset Voltage                                   | тт                                                                        |       | 1.0 2.5<br>1 3  | mV<br>mV       |

| Offset Drift                                           | $T_{MIN}$ - $T_{MAX}$                                                     |       | 1 3<br>15       | μV/°C          |

| -Input Bias Current                                    |                                                                           |       | 20 80           | ±μA            |

| -Input bias Current                                    | $T_{MIN}$ - $T_{MAX}$                                                     |       | 100             | $\pm \mu A$    |

| +Input Bias Current                                    | 1 MIN-1 MAX                                                               |       | 35 100          | $\pm \mu A$    |

| Imput Blus Guirent                                     | $T_{MIN}$ - $T_{MAX}$                                                     |       | 115             | ±μA            |

| Open Loop Transresistance                              | $V_0 = +1.5 \text{ V to } +3.5 \text{ V}$                                 | 140   | 230             | kΩ             |

|                                                        | $T_{MIN}$ - $T_{MAX}$                                                     |       | 170             | kΩ             |

| INPUT CHARACTERISTICS                                  |                                                                           |       |                 |                |

| Input Resistance                                       | +Input                                                                    |       | 2               | $M\Omega$      |

|                                                        | -Input                                                                    |       | 50              | Ω_             |

| Input Capacitance                                      | +Input                                                                    |       | 1.5             | pF             |

| Input Common-Mode Voltage Range                        |                                                                           |       | 3.2             | V              |

| Common-Mode Rejection Ratio                            | V = 11V + 12V                                                             | 50    |                 | ID.            |

| Offset Voltage                                         | $V_{CM} = +1 \text{ V to } +3 \text{ V}$                                  | 52    | 57              | dB             |

| -Input Current                                         | $V_{CM} = +1 \text{ V to } +3 \text{ V, } T_{MIN} - T_{MAX}$              |       | 2<br>15         | μA/V           |

| +Input Current                                         | $V_{CM}$ = +1 V to +3 V, $T_{MIN}$ - $T_{MAX}$                            |       | 15              | μA/V           |

| OUTPUT CHARACTERISTICS                                 | P = 150 O                                                                 |       | 0.0 +0.4.1      | V              |

| Output Voltage Swing Output Current                    | $R_{\rm L}$ = 150 $\Omega$                                                |       | 0.9 to 4.1      |                |

| Short Circuit Current                                  |                                                                           |       | 50<br>95        | mA<br>mA       |

|                                                        |                                                                           |       | ر <del>کا</del> | IIIA           |

| POWER SUPPLY                                           |                                                                           | 0 . 4 | .10             | 7.7            |

| Operating Range                                        |                                                                           | 0, +4 | +12             | V              |

| Total Quiescent Current                                |                                                                           |       | 13 14           | mA             |

| Darrage Complex Dallace's Darlace's                    | $T_{MIN}-T_{MAX}$                                                         | 5.0   | 14.5 15.5       | mA             |

| Power Supply Rejection Ratio                           | $\Delta V_{S} = +1 \text{ V}, V_{CM} = +2.5 \text{ V}$                    | 56    | 62              | dB             |

| -Input Current                                         | $T_{\text{MIN}}$ - $T_{\text{MAX}}$                                       |       | 1<br>6          | μΑ/V           |

| +Input Current                                         | $T_{MIN}-T_{MAX}$                                                         |       | U               | μA/V           |

Specifications subject to change without notice.

REV. B -3-

Supply Voltage

## ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply voltage                                    |

|---------------------------------------------------|

| Internal Power Dissipation <sup>2</sup>           |

| Plastic DIP Package (N) Observe Derating Curves   |

| Small Outline Package (R) Observe Derating Curves |

| Input Voltage (Common Mode) $\pm V_S$             |

| Differential Input Voltage ±2.5 V                 |

| Output Short Circuit Duration                     |

| Observe Power Derating Curves                     |

|                                                   |

..... Observe Power Derating Curves Storage Temperature Range (N, R) .....  $-65^{\circ}$ C to  $+125^{\circ}$ C Operating Temperature Range (A Grade) ...  $-40^{\circ}$ C to  $+85^{\circ}$ C Lead Temperature Range (Soldering 10 sec) .....  $+300^{\circ}$ C NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Specification is for device in free air:

14-Lead Plastic DIP Package:  $\theta_{JA}$  = 90°C/W 14-Lead SOIC Package:  $\theta_{JA}$  = 140°C/W

#### **ORDERING GUIDE**

| Model             | Temperature<br>Range | Package<br>Description | Package<br>Option |  |

|-------------------|----------------------|------------------------|-------------------|--|

| AD8004AN          | −40°C to +85°C       | 14-Lead Plastic DIP    | N-14              |  |

| AD8004AR-14       | -40°C to +85°C       | 14-Lead SOIC           | R-14              |  |

| AD8004AR-14-REEL  | -40°C to +85°C       | 13" Tape and Reel      | R-14              |  |

| AD8004AR-14-REEL7 | -40°C to +85°C       | 7" Tape and Reel       | R-14              |  |

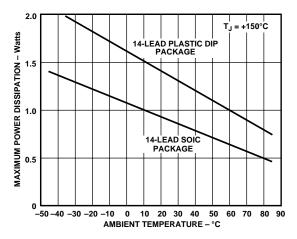

#### MAXIMUM POWER DISSIPATION

12 6 V

The maximum power that can be safely dissipated by the AD8004 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately +150°C. Exceeding this limit temporarily may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of +175°C for an extended period can result in device failure.

While the AD8004 is internally short circuit protected, this may not be sufficient to guarantee that the maximum junction temperature is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves (shown below in Figure 3).

Figure 3. Maximum Power Dissipation vs. Temperature

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8004 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

-4- REV. B

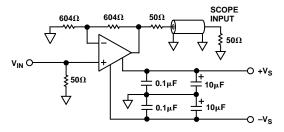

Figure 4. Test Circuit; Gain = +2

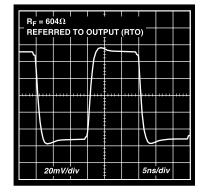

Figure 5.\* 100 mV Step Response; G = +2,  $V_S = \pm 2.5$  V or  $\pm 5$  V

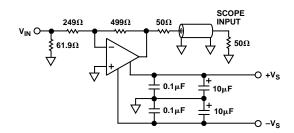

Figure 8. Test Circuit; Gain = −2

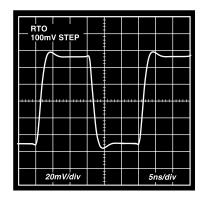

Figure 9.\* 100 mV Step Response; G = -2,  $V_S = \pm 2.5$  V or  $\pm 5$  V

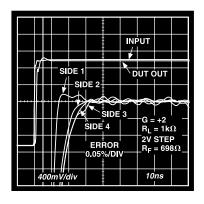

Figure 6.\* Step Response; G = +2,  $V_S = \pm 5 V$

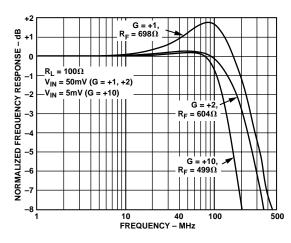

Figure 7. Frequency Response;  $G = +1, +2, +10, V_S = \pm 5 V$

Figure 10.\* Step Response; G = -2,  $V_S = \pm 5 V$

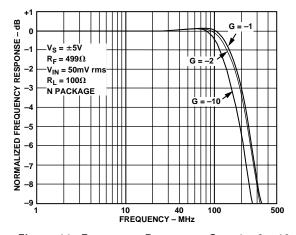

Figure 11. Frequency Response, G = -1, -2, -10

\*NOTE:  $V_S = \pm 2.5 \text{ V}$  operation is identical to  $V_S = +5 \text{ V}$  single supply operation.

-5-

REV. B

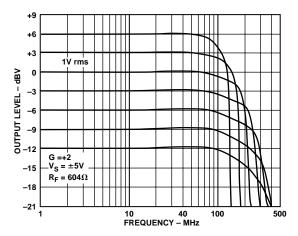

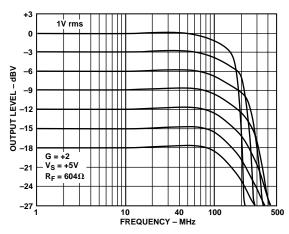

Figure 12. Large Signal Frequency Response;  $V_S=\pm 5.0$  V, G=+2,  $R_F=604$   $\Omega$

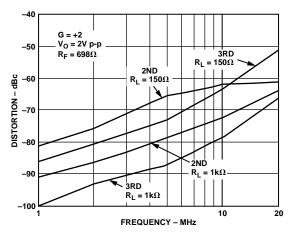

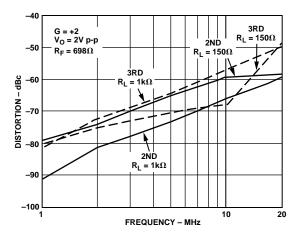

Figure 13. Distortion vs. Frequency;  $V_S = \pm 5 V$

Figure 14. Frequency Response and Flatness, G = +2

Figure 15. Large Signal Frequency Response;  $V_S$  = +5.0 V, G = +2,  $R_F$  = 604  $\Omega$

Figure 16. Distortion vs. Frequency;  $V_S = +5 \text{ V}$

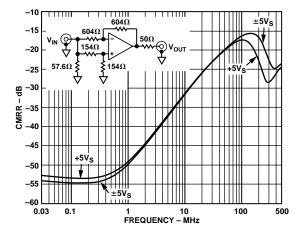

Figure 17. CMRR vs. Frequency;  $V_S = \pm 5 \ V$  or  $+5 \ V$ ,  $V_{IN} = 200 \ mV$  rms, Other Sides Are Equal, RTO

-6- REV. B

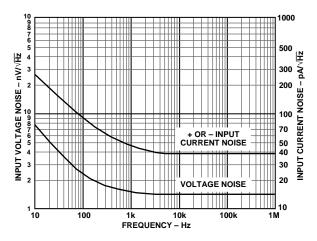

Figure 18. Noise vs. Frequency,  $V_S = +5 \text{ V or } \pm 5 \text{ V}_S$

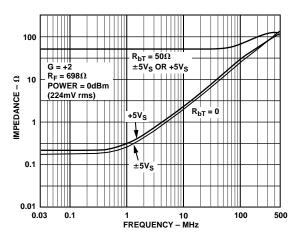

Figure 19. Output Impedance vs. Frequency

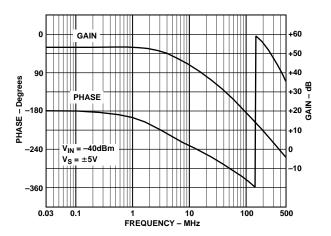

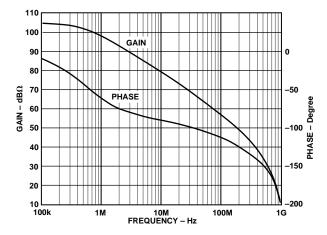

Figure 20. Open-Loop Voltage Gain and Phase

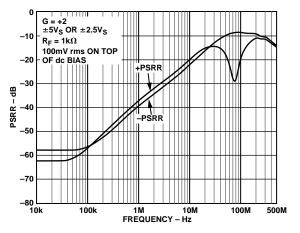

Figure 21. PSRR vs. Frequency

Figure 22. Crosstalk (Output to Output) vs. Frequency

Figure 23. Open-Loop Transimpedance Gain

REV. B -7-

Figure 24. Short-Term Settling Time

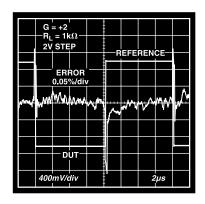

Figure 25. Long-Term Settling Time

Figure 26. Differential Gain/Differential Phase

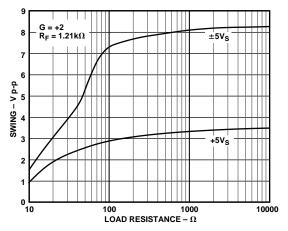

Figure 27. Output Voltage Swing vs. Load

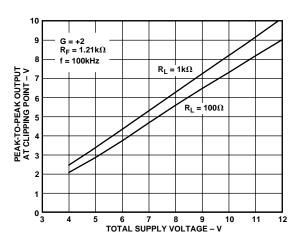

Figure 28. Output Swing vs. Supply

Figure 29. Differential Gain/Phase,  $R_L = 1 \text{ k}\Omega$

-8- REV. B

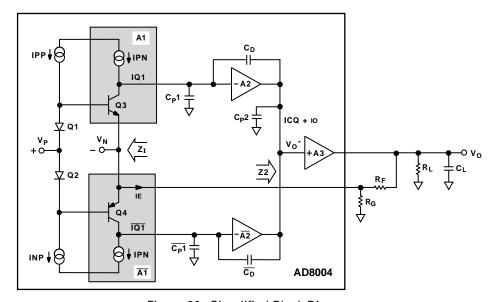

#### THEORY OF OPERATION

The AD8004 is a member of a new family of high speed current-feedback (CF) amplifiers offering new levels of bandwidth, distortion, and signal-swing capability vs. power. Its wide dynamic range capabilities are due to both a complementary high speed bipolar process and a new design architecture. The AD8004 is basically a two stage (Figure 30) rather than the conventional one stage design. Both stages feature the current-on-demand property associated with current feedback amplifiers. This gives an unprecedented ratio of quiescent current to dynamic performance. The important properties of slew rate, and full power bandwidth benefit from this performance. In addition the second gain stage buffers the effects of load impedance significantly reducing distortion.

A full discussion of this new amplifier architecture is available on the data sheet for the AD8011. This discussion only covers the basic principles of operation.

#### DC AND AC CHARACTERISTICS

As with traditional op amp circuits the dc closed-loop gain is defined as:

$$A_V = G = 1 + \frac{R_F}{R_N}$$

noninverting operation

$$A_V = G = -\frac{R_F}{R_N}$$

inverting operation

The more exact relationships that take into account open-loop gain errors are:

$$A_V = \frac{G}{1 + \frac{1 - G}{A_O(s)} + \frac{R_F}{T_O(s)}}$$

for inverting (G is negative)

$$A_V = \frac{G}{1 + \frac{G}{A_O(s)} + \frac{R_F}{T_O(s)}}$$

for noninverting (G is positive)

In these equations the open-loop voltage gain  $(A_O(s))$  is common to both voltage and current-feedback amplifiers and is the ratio of output voltage to differential input voltage. The open-loop transimpedance gain  $(T_O(s))$  is the ratio of output voltage to inverting input current and is applicable to current-feedback amplifiers. The open-loop voltage gain and open-loop transimpedance gain  $(T_O(s))$  of the AD8004 are plotted vs. frequency in Figures 20 and 23. These plots and the basic relationships can be used to predict the first order performance of the AD8004 over frequency. At low closed-loop gains the term  $(R_F/T_O(s))$  dominates the frequency response characteristics. This gives the result that bandwidth is constant with gain, a familiar property of current feedback amplifiers.

An  $R_{\rm F}$  of 1 k $\Omega$  has been chosen as the nominal value to give optimum frequency response with acceptable peaking at gains of +2/-1. As can be seen from the above relationships, at higher closed-loop gains reducing  $R_{\rm F}$  has the effect of increasing closed-loop bandwidth. Table I gives optimum values for  $R_{\rm F}$  and  $R_{\rm G}$  for a variety of gains.

Figure 30. Simplified Block Diagram

REV. B \_9\_

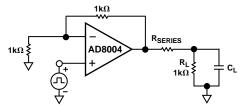

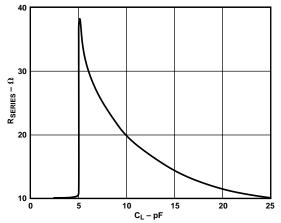

#### DRIVING CAPACITIVE LOADS

The AD8004 was designed primarily to drive nonreactive loads. If driving loads with a capacitive component is desired, best settling response is obtained by the addition of a small series resistance as shown in Figure 31. The accompanying graph shows the optimum value for  $R_{\rm SERIES}$  vs. capacitive load. It is worth noting that the frequency response of the circuit when driving large capacitive loads will be dominated by the passive roll-off of  $R_{\rm SERIES}$  and  $C_{\rm L}$ .

Figure 31. Driving Capacitive Load

Figure 32. Recommended  $R_{SERIES}$  vs. Capacitive Load for  $\leq$  30 ns Settling to 0.1%

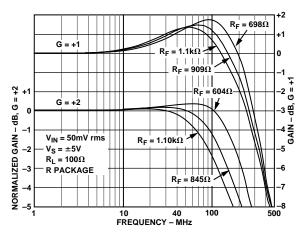

#### **OPTIMIZING FLATNESS**

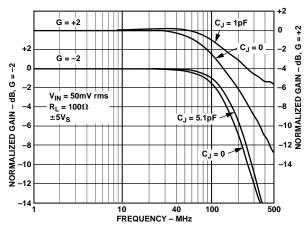

The fine scale gain flatness and -3~dB bandwidth is affected by  $R_{\rm FEEDBACK}$  selection as is normal of current feedback amplifiers. With exception of gain = +1, the AD8004 can be adjusted for either maximal flatness with modest closed-loop bandwidth or for mildly peaked-up frequency response with much more bandwidth. Figure 33 shows the effect of three evenly spaced  $R_{\rm F}$  changes upon gain = +1 and gain = +2. Table I shows the recommended component values for achieving maximally flat frequency response as well as a faster slightly peaked-up frequency response.

Printed circuit board parasitics and device lead frame parasitics also control fine scale gain flatness. The AD8004R package because of its small lead frame offers superior parasitics relative to the N package. In the printed circuit board environment, parasitics such as extra capacitance caused by two parallel and vertical flat conductors on opposite PC board sides in the

region of the summing junction will cause some bandwidth extension and/or increased peaking. In noninverting gains, the effect of extra capacitance on summing junctions is far more pronounced than versus inverting gains. Figure 34 shows an example of this. Note that only 1 pF of added junction capacitance causes about a 70% bandwidth extension and additional peaking on a gain = +2. For an inverting gain = -2, 5 pF of additional summing junction capacitance caused a small 10% bandwidth extension.

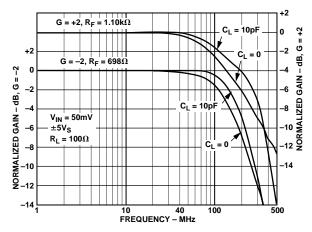

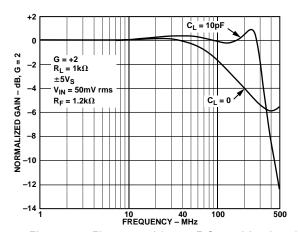

Extra output capacitive loading also causes bandwidth extensions and peaking. The effect is more pronounced with less resistive loading from the next stage. Figure 35 shows the effect of direct output capacitive loads for gains of +2 and –2. For both gains  $C_{LOAD}$  was set to 10 pF or 0 pF (no extra capacitive loading). For each of the four traces in Figure 35 the resistive loads were 100  $\Omega$ . Figure 36 also shows capacitive loading effects only with a lighter output resistive load. Note that even though bandwidth is extended 2×, the flatness dramatically suffers.

Figure 33.  $R_{FEEDBACK}$  vs. Frequency Response, G = +1/+2

Figure 34. Frequency Response vs. Added Summing Junction Capacitance

–10– REV. B

Figure 35. Frequency Response vs. Capacitive Loading,  $R_L = 100 \Omega$  Output

Figure 36. Flatness with 10 pF Capacitive Load

## **DRIVING A SINGLE-SUPPLY A/D CONVERTER**

New CMOS A/D converters are placing greater demands on the amplifiers that drive them. Higher resolutions, faster conversion rates and input switching irregularities require superior settling characteristics. In addition, these devices run off a single +5 V supply and consume little power, so good single-supply operation with low power consumption are very important. The AD8004 is well positioned for driving this new class of A/D converters.

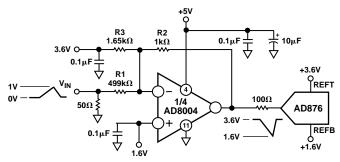

Figure 37 shows a circuit that uses an AD8004 to drive an AD876, a single supply, 10-bit, 20 MSPS A/D converter that requires only 140 mW. Using the AD8004 for level shifting and driving, the A/D exhibits no degradation in performance compared to when it is driven from a signal generator.

The analog input of the AD876 spans 2 V centered at about 2.6 V. The resistor network and bias voltages provide the level shifting and gain required to convert the 0 V to 1 V input signal to a 3.6 V to 1.6 V range that the AD876 wants to see.

Biasing the noninverting input of the AD8004 at 1.6 V dc forces the inverting input to be at 1.6 V dc for linear operation of the amplifier. When the input is at 0 V, there is 3.2 mA flowing out of the summing junction via R1 (1.6 V/499  $\Omega$ ). R3 has a current of 1.2 mA flowing into the summing junction (3.6 V–1.6 V)/ 1.65 k $\Omega$ . The difference of these two currents (2 mA) must flow

through R2. This current flows toward the summing junction and requires that the output be 2 V higher than the summing junction or at 3.6 V.

When the input is at 1 V, there is 1.2 mA flowing into the summing junction through R3 and 1.2 mA flowing out through R1. These currents balance and leave no current to flow through R2. Thus the output is at the same potential as the inverting input or 1.6 V.

The input of the AD876 has a series MOSFET switch that turns on and off at the sampling rate. This MOSFET is connected to a hold capacitor internal to the device. The on impedance of the MOSFET is about 50  $\Omega$ , while the hold capacitor is about 5 pF.

In a worst case condition, the input voltage to the AD876 will change by a full-scale value (2 V) in one sampling cycle. When the input MOSFET turns on, the output of the op amp will be connected to the charged hold capacitor through the series resistance of the MOSFET. Without any other series resistance, the instantaneous current that flows would be 40 mA. This would cause settling problems for the op amp.

The series 100  $\Omega$  resistor limits the current that flows instantaneously after the MOSFET turns on to about 13 mA. This resistor cannot be made too large or the high frequency performance will be affected.

The sampling MOSFET of the AD876 is closed for only half of each cycle or for 25 ns. Approximately seven time constants are required for settling to 10 bits. The series  $100~\Omega$  resistor along with the  $50~\Omega$  on resistance and the hold capacitor, create a 750 ps time constant. These values leave a comfortable margin for settling. Obtaining the same results with the op amp A/D combination as compared to driving with a signal generator indicates that the op amp is settling fast enough.

Overall the AD8004 provides adequate buffering for the AD876 A/D converter without introducing distortion greater than that of the A/D converter by itself.

Figure 37. AD8004 Driving the AD876

## LAYOUT CONSIDERATIONS

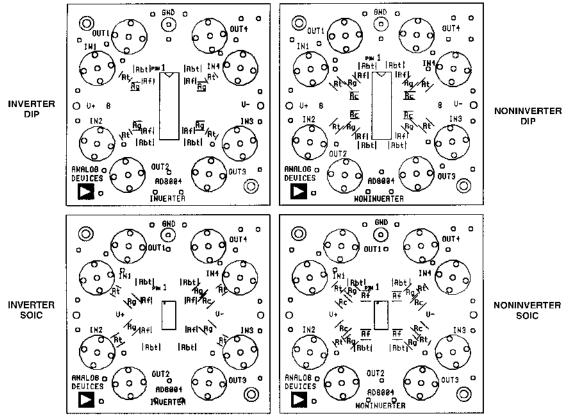

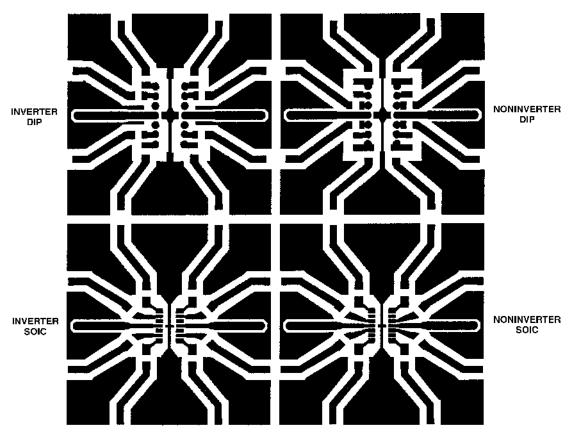

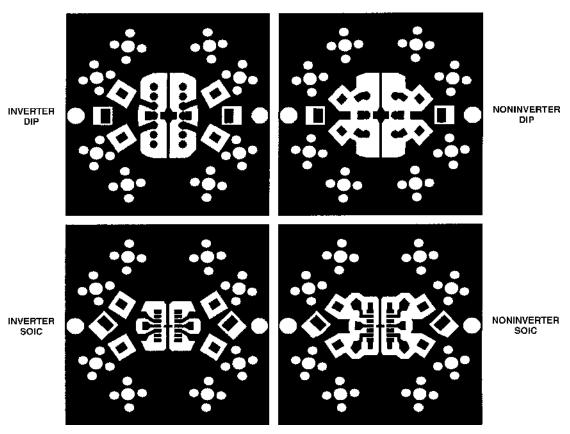

The specified high speed performance of the AD8004 requires careful attention to board layout and component selection. Table I shows the recommended component values for the AD8004 and Figures 39–41 show the layout for the AD8004 evaluation boards (14-lead DIP and SOIC). Proper  $R_F$  design techniques and low parasitic component selection are mandatory.

REV. B –11–

The PCB should have a ground plane covering all unused portions of the component side of the board to provide a low impedance ground path. The ground plane should be removed from the area near the input pins to reduce stray capacitance.

Chip capacitors should be used for supply bypassing (see Figure 38). One end should be connected to the ground plane and the other within 1/8 in. of each power pin. An additional  $(4.7 \ \mu\text{F}-10 \ \mu\text{F})$  tantalum electrolytic capacitor should be connected in parallel.

The feedback resistor should be located close to the inverting input pin in order to keep the stray capacitance at this node to a minimum. Capacitance greater than 1 pF at the inverting input will significantly affect high speed performance when operating at low noninverting gains. An example of extra inverting input capacitance can be seen on Figure 35 plot.

Stripline design techniques should be used for long signal traces (greater than about 1 in.). These should be designed with the proper system characteristic impedance and be properly terminated at each end.

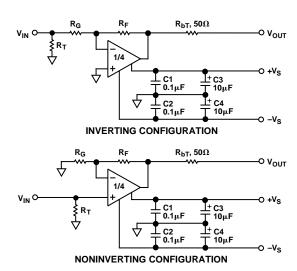

Figure 38. Inverting and Noninverting Configurations

Table I. Recommended Component Values and Typical Bandwidths

|                                                                                |                     |                    | Alternate          |                    | Alternate          |                   | Alternate      |                        | Alternate        |                   |

|--------------------------------------------------------------------------------|---------------------|--------------------|--------------------|--------------------|--------------------|-------------------|----------------|------------------------|------------------|-------------------|

| Gain                                                                           | -10                 | -2                 | -2                 | -1                 | <b>-1</b>          | +1                | +1             | +2                     | +2               | +10               |

| AD8004AN (DIP)<br>PACKAGE TYPE                                                 |                     |                    |                    |                    |                    |                   |                |                        |                  |                   |

| $R_{F}(\Omega)$ $R_{G}(\Omega)$ $R_{T}(\Omega)$                                | 499<br>49.9<br>None | 698<br>348<br>57.6 | 499<br>249<br>61.9 | 649<br>649<br>53.6 | 499<br>499<br>54.9 | 1.21 k<br>-<br>50 | 806<br>-<br>50 | 1.10 k<br>1.10 k<br>50 | 698<br>698<br>50 | 499<br>54.9<br>50 |

| Small Signal BW<br>@ ±5 V <sub>S</sub> (MHz)                                   | 155                 | 125                | 180                | 135                | 190                | 150               | 250            | 115                    | 185              | 135               |

| Peaking @ $\pm 5 \text{ V}_S$                                                  | < 0.3 dB            | None               | 0.3 dB             | None               | 0.3 dB             | 1.3 dB            | 1.7 dB         | < 0.14 dB              | 0.4 dB           | < 0.3 dB          |

| 0.1 dB Flatness<br>@ ±5 V <sub>S</sub> (MHz)                                   | _                   | 25                 | -                  | 30                 | _                  | _                 | _              | 35                     | _                | _                 |

| Small Signal BW  @ +5 V <sub>S</sub> (MHz)                                     | 135                 | 105                | 155                | 120                | 160                | 130               | 200            | 95                     | 150              | 120               |

| AD8004AR (SOIC)<br>PACKAGE TYPE                                                |                     |                    |                    |                    |                    |                   |                |                        |                  |                   |

| $egin{aligned} R_F & (\Omega) \ R_G & (\Omega) \ R_T & (\Omega) \end{aligned}$ | 499<br>49.9<br>None | 698<br>348<br>57.6 | 499<br>249<br>61.9 | 750<br>750<br>53.6 | 499<br>499<br>54.9 | 1.10 k<br>-<br>50 | 698<br>-<br>50 | 1.10 k<br>1.10 k<br>50 | 604<br>604<br>50 | 499<br>54.9<br>50 |

| Small Signal BW @ ±5 V <sub>S</sub> (MHz)                                      | 155                 | 130                | 190                | 125                | 195                | 150               | 225            | 110                    | 175              | 135               |

| Peaking @ ±5 V <sub>S</sub>                                                    | < 0.7 dB            | < 0.1 dB           | 0.5 dB             | None               | 0.4 dB             | 1.3 dB            | 1.8 dB         | < 0.1 dB               | 0.5 dB           | < 0.2 dB          |

| 0.1 dB Flatness<br>@ ±5 V <sub>S</sub> (MHz)                                   | _                   | 35                 | -                  | 25                 | _                  | _                 | _              | 30                     | _                | _                 |

| Small Signal BW  @ +5 V <sub>S</sub> (MHz)                                     | 135                 | 115                | 175                | 110                | 165                | 130               | 195            | 95                     | 155              | 120               |

NOTES

–12– REV. B

$<sup>^{1}</sup>R_{T}$  chosen for 50  $\Omega$  characteristic input impedance.

<sup>&</sup>lt;sup>2</sup>Resistor values listed are standard 1% tolerance.

NOTES:

- 1.  $H_{\rm T}$  (INPUT TERMINATION RESISTOR) IS MOUNTED ON BOARD BOTTOMS.

- 2. R<sub>C</sub> (IN SERIES WITH INPUT) IS A SHORT ON AD8004.

- 3. BYPASS CHIP CAPACITORS ARE MOUNTED ON BOARD BOTTOM WITH 0.1 #F BEING CLOSEST TO SUPPLY PINS.

- 4. ON BOTH INVERTER BOARDS  $\mathbf{R}_{G}$  ,  $\mathbf{R}_{F}$  AND  $\mathbf{R}_{BT}$  ARE MOUNTED ON BOARD TOP.

- 5. ON NONINVERTER DIP BOARDS,  $R_F$  AND  $R_{BT}$  ARE ON BOARD TOP WHILE  $R_G$  IS ON BOTTOM. ON NONINVERTER SOIC BOARD,  $R_{BT}$  IS ON TOP WHILE  $R_F$  AND  $R_G$  ARE ON BOARD BOTTOM.

Figure 39. Evaluation Board Silkscreen (Top)

REV. B -13-

Figure 40 Evaluation Board Layout (Top Side)

Figure 41. Evaluation Board Layout (Bottom Side, Looking Through the Board)

-14- REV. B

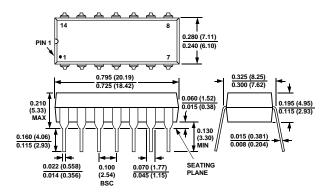

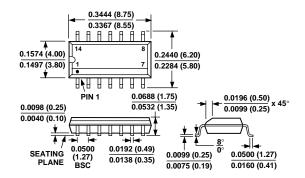

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

## 14-Lead Plastic DIP (N-14)

## 14-Lead Plastic SOIC (R-14)

REV. B -15-