# ANALOG Low-Power, Precision Analog Microcontroller, Dual $\Sigma$ - $\wedge$ Angs Flash/FF Arm7thmi Dual $\Sigma$ - $\triangle$ ADCs, Flash/EE, ARM7TDMI

### **Preliminary Technical Data**

### ADuC7060/ADuC7061/ADuC7062

#### **FEATURES**

Analog input/output

Dual (24-bit) ADCs

Single-ended and differential inputs

Programmable ADC output rate (4 Hz to 8 kHz)

**Programmable digital filters**

Low power operation mode

Primary (24-bit) ADC channel

Up to 5 input channels

PGA (1 to 512) input stage

Selectable input range, ±2.34 mV to ±1.2 V

30 nV rms noise

**Auxiliary (24-bit) ADC**

Up to 8 buffered input channels

On-chip precision reference (±10 ppm/°C)

Programmable sensor excitation current sources

200 µA to 2 mA current source range

Single 16-bit voltage output DAC

Microcontroller

ARM7TDMI core, 16-/32-bit RISC architecture

JTAG port supports code download and debug

Multiple clocking options

Memory

32 kB (16 kB × 16) Flash/EE memory

4 kB (1 kB × 32) SRAM

**Tools**

In-circuit download, JTAG based debug

Low cost, QuickStart development system

**Communications interfaces**

SPI interface(5 Mbps)

UART serial I/O and I2C (master/slave)

**On-chip peripherals**

4× general-purpose (capture/compare) timers

2× general-purpose (capture/compare) timers

**Wakeup timer**

Watchdog timer

Vectored interrupt controller for FIQ and IRQ

8 priority levels for each interrupt type

interrupt on edge or level external pin inputs

16-bit, 6-channel PWM

**General-purpose inputs/outputs**

Up to 14 GPIO pins that are fully 3.3 V compliant

AVDD/DVDD specified for 2.5 V (+5%)

All inputs/outputs fully 3.3 V compliant

Active mode: 2.6 mA (@1 MHz, both ADCs active)

10 mA (@10 MHz, both ADCs active)

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No ense is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

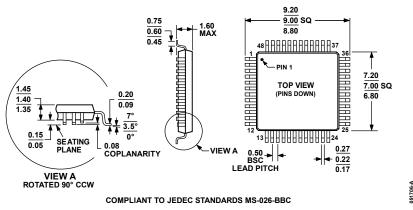

**Packages and Temperature range**

Fully specified for -40°C to +125°C operation

32-lead LFCSP (5 mm × 5 mm)

48-lead LFCSP

48-lead LQFP

Derivatives: 48-lead LQFP and 48-lead LFCSP, dual ADCs (ADuC7060); 32-lead LFCSP, dual ADCs (ADuC7061);

32-lead LFCSP, single ADC (ADuC7062)

#### **APPLICATIONS**

Industrial automation and process control Intelligent, precision sensing systems, 4 to 20 mA loopbased smart sensors

#### **GENERAL DESCRIPTION**

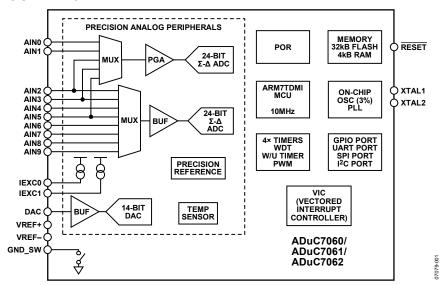

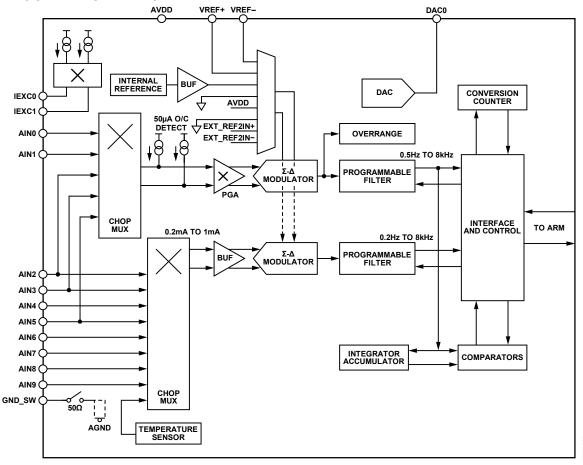

The ADuC706x are fully integrated, 8 kSPS, 24-bit data acquisition systems incorporating high performance multichannel sigma-delta ( $\Sigma$ - $\Delta$ ) analog-to-digital converters (ADCs), 16-bit/ 32-bit ARM7TDMI® MCU, and Flash/EE memory on a single chip.

The ADCs consists of a 5-channel primary ADC and up to an 8-channel auxiliary ADC. The ADCs operate in single-ended or differential input modes. A single channel buffered voltage output DAC is available on-chip. The DAC output range is programmable to one of two voltage ranges.

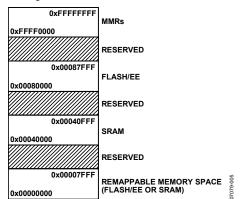

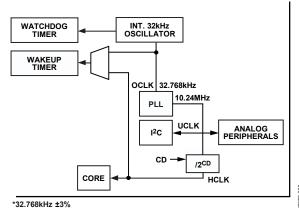

The devices operate from an on-chip oscillator and a PLL generating an internal high frequency clock up to 10.24 MHz. The microcontroller core is an ARM7TDMI, 16-bit/32-bit RISC machine offering up to 10 MIPS peak performance. 4 kB of SRAM and 32 kB of nonvolatile Flash/EE memory are provided on-chip. The ARM7TDMI core views all memory and registers as a single linear array.

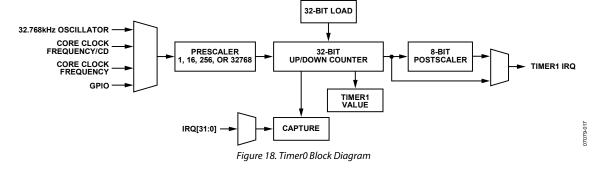

The ADuC7060 contains four timers. Timer 1 is wake-up timer with the ability to bring the part out of power saving mode. Timer 2 may be configured as a watchdog timer. A 16-bit PWM with six output channels is also provided.

The ADuC7060 contains an advanced interrupt controller. The vectored interrupt controller (VIC) allows every interrupt to be assigned a priority level. It also supports nested interrupts to a maximum level of eight per IRQ and FIQ. When IRQ and FIQ interrupt sources are combined, a total of 16 nested interrupt levels are supported. On-chip factory firmware supports incircuit serial download via the UART serial interface ports and nonintrusive emulation via the JTAG interface.

The parts operate from 2.375 V to 2.625 V over an industrial temperature range of -40°C to +125°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

## **Preliminary Technical Data**

### **TABLE OF CONTENTS**

| Features                                       | IRQ                                             | 51 |

|------------------------------------------------|-------------------------------------------------|----|

| Applications                                   | Fast Interrupt Request (FIQ)                    |    |

| General Description                            | Timers                                          |    |

| Revision History                               | Timer0                                          |    |

| Functional Block Diagram                       | Timer1 or Wake-Up Timer                         |    |

| Specifications                                 | Timer2 or Watchdog Timer                        |    |

| Electrical Specifications                      | Timer3                                          |    |

| Timing Specifications 8                        | Pulse-Width Modulator (PWM)                     |    |

| Absolute Maximum Ratings9                      | PWM General Overview                            |    |

| ESD Caution9                                   | UART Serial Interface                           |    |

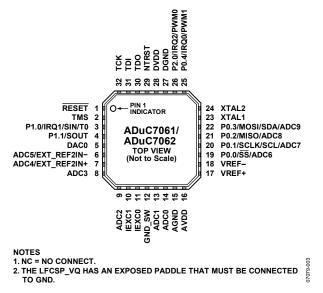

| Pin Configurations and Function Descriptions10 | Baud Rate Generation                            | 74 |

| Terminology14                                  | UART Register Definition                        |    |

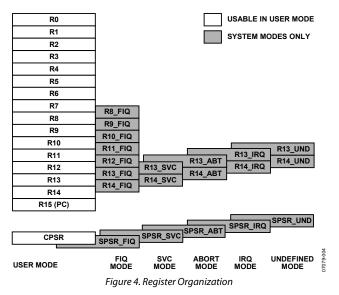

| Overview of the ARM7TDMI Core15                | I <sup>2</sup> C                                |    |

| Thumb Mode (T)15                               | Serial Clock Generation                         | 80 |

| Multiplier (M)15                               | I <sup>2</sup> C Bus Addresses                  | 80 |

| Embedded ICE (I)                               | I <sup>2</sup> C Registers                      | 80 |

| ARM Registers15                                | I <sup>2</sup> C Common Registers               | 8  |

| Interrupt Latency16                            | Serial Peripheral Interface                     | 89 |

| Memory Organization16                          | MISO (Master In, Slave Out) Pin                 | 89 |

| Flash/EE Control Interface17                   | MOSI (Master Out, Slave In) Pin                 | 89 |

| Memory Mapped Registers20                      | SCL (Serial Clock I/O) Pin                      | 89 |

| Complete MMR Listing21                         | Slave Select (SS Input) Pin                     | 89 |

| Reset                                          | Configuring External Pins for SPI Functionality | 8  |

| Oscillator, PLL and Power Control27            | SPI Registers                                   |    |

| ADC Circuit information30                      | General-Purpose I/O                             | 9  |

| Example Application Circuits49                 | GPxCON Registers                                | 9  |

| DAC Peripherals50                              | GPxDAT Registers                                | 9  |

| DAC50                                          | GPxSET Registers                                | 94 |

| MMR Interface50                                | GPxCLR Registers                                | 9  |

| Nonvolatile Flash/EE Memory52                  | GPxPAR Registers                                |    |

| Flash/EE Memory Reliability52                  | Hardware Design Considerations                  | 9  |

| Programming52                                  | Power Supplies                                  | 90 |

| Processor Reference Peripherals53              | Outline Dimensions                              | 9  |

| Interrupt System53                             | Ordering Guide                                  | 9  |

#### **REVISION HISTORY**

6/08—Revision PrA: Preliminary Version

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

### **SPECIFICATIONS**

#### **ELECTRICAL SPECIFICATIONS**

$V_{DD} = 2.5 \text{ V} \pm 5\%, V_{REF+} = 1.2 \text{ V}, V_{REF-} = GND \text{ internal reference, } f_{CORE} = 10.24 \text{ MHz driven from external } 32.768 \text{ kHz watch crystal or on-chip precision oscillator, all specifications } T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 1. ADuC706x Specifications

| Parameter                                          | Test Conditions/Comments                                                                                          | Min  | Тур          | Max   | Unit       |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|--------------|-------|------------|

| ADC SPECIFICATIONS                                 |                                                                                                                   |      |              |       |            |

| Conversion Rate <sup>1</sup>                       | Chop off, ADC normal operating mode                                                                               | 50   |              | 8000  | Hz         |

|                                                    | Chop on, ADC normal operating mode                                                                                | 4    |              | 2600  | Hz         |

|                                                    | Chop on, ADC low power mode                                                                                       | 1    |              | 650   | Hz         |

| Main Channel                                       |                                                                                                                   |      |              |       |            |

| No Missing Codes <sup>1</sup>                      | Chop off $(f_{ADC} \le 1 \text{ kHz})$                                                                            | 24   |              |       | Bits       |

|                                                    | Chop on $(f_{ADC} \le 666 \text{ Hz})$                                                                            | 24   |              |       | Bits       |

| Integral Nonlinearity <sup>2</sup>                 | Gain = 1                                                                                                          |      |              | ±14   | ppm of FSR |

|                                                    | Gain = 8                                                                                                          |      |              | ±25   | ppm of FSR |

|                                                    | Gain = 64                                                                                                         |      |              | ±66   | ppm of FSR |

| Offset Error <sup>3, 4</sup>                       | Chop off, offset error is in the order of the noise for the programmed gain and update rate following calibration | ±4   |              | μV    |            |

| Offset Error <sup>3, 4</sup>                       | Chop on                                                                                                           |      | ±0.5         |       | μV         |

| Offset Error Drift vs.<br>Temperature <sup>5</sup> | Chop off (with GAIN ≤ 64)                                                                                         |      | 650/PGA_GAIN |       | nV/°C      |

| Offset Error Drift vs.<br>Temperature <sup>5</sup> | Chop on (with GAIN ≤ 64)                                                                                          | 10   |              |       | nV/°C      |

| Full Scale Error <sup>1,6,7,8</sup>                | Normal mode                                                                                                       |      | ±0.5         |       | mV         |

| Full Scale Error <sup>1,6,7,8</sup>                | Low power mode                                                                                                    | ±1.0 |              |       | mV         |

| Gain Drift v Temperature <sup>9</sup>              |                                                                                                                   |      | 5            |       | ppm/°C     |

| PGA Gain Mismatch Error                            |                                                                                                                   |      | ±0.1         |       | %          |

| Output Noise <sup>1</sup>                          | See Table 29                                                                                                      |      |              |       |            |

| Power Supply Rejection                             | Chop on, ADC = 1 V, (gain = 1)                                                                                    |      | 80           |       | dB         |

|                                                    | Chop on, ADC = $7.8 \text{ mV}$ , (gain = $128$ )                                                                 |      | 113          |       | dB         |

|                                                    | Chop off, ADC = 1 V, (gain = 1)                                                                                   |      | 80           |       | dB         |

| Aux Channel                                        |                                                                                                                   |      |              |       |            |

| No Missing Codes <sup>1</sup>                      | Chop off ( $f_{ADC} \le 1 \text{ kHz}$ )                                                                          | 24   |              |       | Bits       |

|                                                    | Chop on $(f_{ADC} \le 666 \text{ Hz})$                                                                            | 24   |              |       | Bits       |

| Integral Nonlinearity                              |                                                                                                                   |      |              | ±20   | ppm of FSR |

| Offset Error <sup>4</sup>                          | Chop off                                                                                                          |      | ±15          |       | μV         |

| Offset Error <sup>4</sup>                          | Chop on                                                                                                           |      | ±0.5         |       | μV         |

| Offset Error Drift vs.<br>Temperature⁵             | Chop off                                                                                                          | 200  |              | nV/°C |            |

| Offset Error Drift vs.<br>Temperature⁵             | Chop on                                                                                                           |      | 10           |       | nV/°C      |

| Full-Scale Error <sup>1,6,7,8</sup>                | Normal mode                                                                                                       |      | ±0.5         |       | mV         |

| Full-Scale Error <sup>1,6,8</sup>                  | Low power mode                                                                                                    |      | ±1.0         |       | mV         |

| Gain Drift vs. Temperature9                        |                                                                                                                   |      | 3            |       | ppm/°C     |

| Output Noise                                       | See Table 27                                                                                                      |      |              |       |            |

| Power Supply Rejection                             | Chop on, ADC = 1 V                                                                                                |      | 80           |       | dB         |

|                                                    | Chop off, ADC = 1 V                                                                                               |      | 80           |       | dB         |

## ADuC7060/ADuC7061/ADuC7062

| Parameter                                                                        | Test Conditions/Comments                                                           | Min   | Тур            | Max          | Unit   |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|----------------|--------------|--------|

| ADC SPECIFICATIONS: ANALOG INPUT                                                 | Internal VREF = 1.2 V                                                              |       |                |              |        |

| Main Channel                                                                     |                                                                                    |       |                |              |        |

| Absolute Input Voltage<br>Range                                                  | Applies to both VIN+ and VIN-                                                      | 0.1   |                | $V_{DD}-0.7$ | V      |

| Input Voltage Range                                                              | Gain = 1 <sup>1</sup>                                                              |       | 1.2            |              | V      |

|                                                                                  | Gain = 2 <sup>10</sup>                                                             |       | 600            |              | mV     |

|                                                                                  | $Gain = 4^{10}$                                                                    |       | 300            |              | mV     |

|                                                                                  | Gain = 8                                                                           |       | 150            |              | mV     |

|                                                                                  | Gain = 16                                                                          |       | 75             |              | mV     |

|                                                                                  | Gain = 32                                                                          |       | 37.5           |              | mV     |

|                                                                                  | Gain = 64                                                                          |       | 18.75          |              | mV     |

|                                                                                  | Gain = 128                                                                         |       | 9.375          |              | mV     |

| Input Leakage Current <sup>1</sup>                                               | ADC0/ADC1                                                                          |       | 10             |              | nA     |

|                                                                                  | ADC2/ADC3/ADC4/ADC5                                                                |       | 15             |              | nA     |

|                                                                                  | ADC6/ADC7/ADC8/ADC9                                                                |       | 15             |              | nA     |

| Input Offset Current <sup>1,11</sup><br>Common-Mode Rejection<br>DC <sup>1</sup> |                                                                                    |       | 0.5            |              | nA     |

| On ADC                                                                           | ADC = 7.8 mV                                                                       | 95    |                |              | dB     |

| on no c                                                                          | $ADC = 1 V^{1}$                                                                    |       | 113            |              | dB     |

| Common-Mode Rejection 50/60 Hz <sup>1</sup>                                      | 50/60 Hz ± 1 Hz, 16.6 Hz and 50 Hz<br>update rate, chop on                         |       | 113            |              |        |

|                                                                                  | ADC = $7.8 \text{ mV}$ , range $\pm 20 \text{ mV}$                                 | 95    |                |              | dB     |

|                                                                                  | $ADC = 1 V$ , range $\pm 1.2 V$                                                    | 90    |                |              | dB     |

| Normal-Mode Rejection<br>50/60 Hz <sup>1</sup>                                   |                                                                                    |       |                |              |        |

| On ADC                                                                           | 50/60 Hz ± 1 Hz, 16.6Hz f <sub>ADC</sub> , chop on                                 | 75    |                |              | dB     |

|                                                                                  | $50/60 \text{ Hz} \pm 1 \text{ Hz}$ , $16.6 \text{Hz}$ f <sub>ADC</sub> , chop off | 67    |                |              | dB     |

| Aux Channel                                                                      |                                                                                    |       |                |              |        |

| Absolute Input Voltage<br>Range <sup>1</sup>                                     | Buffer enabled                                                                     | 0.1   |                | AVDD – 0.1   | V      |

|                                                                                  | Buffer disabled                                                                    | AGND  |                | AVDD         |        |

| Input Voltage Range                                                              | Range based reference source                                                       |       | 0 – 1.2        |              | V      |

| Input Current<br>Common-Mode Rejection<br>DC <sup>1</sup>                        |                                                                                    |       | 5.5            |              | μΑ     |

| On ADC                                                                           | ADC = 7.8 mV                                                                       | 95    |                |              | dB     |

| OII / IDC                                                                        | $ADC = 1 V^{1}$                                                                    |       | 113            |              | dB     |

| Common-Mode Rejection 50/60 Hz <sup>1</sup>                                      | 50/60 Hz ± 1 Hz, 16.6 Hz and 50 Hz<br>update rate, chop on                         |       | 113            |              | ub     |

|                                                                                  | $ADC = 7.8 \text{ mV}$ , range $\pm 20 \text{ mV}$                                 | 95    |                |              | dB     |

|                                                                                  | $ADC = 1 \text{ V, range } \pm 1.2 \text{ V}$                                      | 90    |                |              | dB     |

| Normal-Mode Rejection<br>50/60 Hz <sup>1</sup>                                   |                                                                                    |       |                |              |        |

| On ADC                                                                           | 50/60 Hz ± 1 Hz, 16.6 Hz f <sub>ADC</sub> , chop on                                | 75    |                |              | dB     |

|                                                                                  | $50/60 \text{ Hz} \pm 1 \text{ Hz}$ , 16.6 Hz $f_{ADC}$ , chop off                 | 67    |                |              | dB     |

| VOLTAGE REFERENCE                                                                | , , , , , , , , , , , , , , , , , , , ,                                            | 1     |                |              |        |

| ADC Precision Reference                                                          |                                                                                    |       |                |              |        |

| Internal VREF                                                                    |                                                                                    |       | 1.2            |              | V      |

| Initial Accuracy <sup>1</sup>                                                    | Measured at $T_A = 25^{\circ}C$                                                    | -0.06 | - <del>-</del> | +0.06        | %      |

| Reference Temperature Coefficient <sup>1, 12</sup>                               |                                                                                    | -20   | ±10            | +20          | ppm/°C |

| Power Supply Rejection                                                           |                                                                                    |       | 70             |              | dB     |

Rev. PrA | Page 5 of 100

| Parameter                                               | Test Conditions/Comments                        | Min             | Тур                | Max          | Unit            |

|---------------------------------------------------------|-------------------------------------------------|-----------------|--------------------|--------------|-----------------|

| External Reference Input<br>Range <sup>13</sup>         |                                                 | 0.1             |                    | AVDD         | V               |

| V <sub>REF</sub> Divide by 2 Initial Error <sup>1</sup> |                                                 |                 | 0.1                |              | %               |

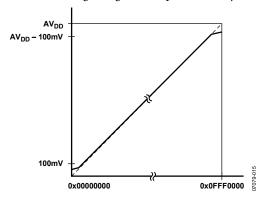

| DAC CHANNEL SPECIFICATIONS                              | $R_L = 5 \text{ k}\Omega, C_L = 100 \text{ pF}$ |                 |                    |              |                 |

| Voltage Range                                           |                                                 |                 | $0-V_{\text{REF}}$ |              | V               |

|                                                         |                                                 |                 | 0 – AVDD           |              | V               |

| 12-BIT MODE                                             |                                                 |                 |                    |              |                 |

| DC Specifications <sup>14</sup>                         |                                                 |                 |                    |              |                 |

| Resolution                                              |                                                 | 12              |                    |              | Bits            |

| Relative Accuracy                                       |                                                 |                 | ±2                 |              | LSB             |

| Differential Nonlinearity                               | Guaranteed monotonic                            |                 | ±0.2               | ±1           | LSB             |

| Offset Error                                            | 1.2 V internal reference                        |                 | ±2                 | ±15          | mV              |

| Gain Error                                              | V <sub>REF</sub> range (reference = 1.2 V)      |                 |                    | ±1           | %               |

|                                                         | AVDD range                                      |                 |                    | ±1           | %               |

| Gain Error Mismatch                                     |                                                 |                 |                    | 0.1          | % of full       |

|                                                         |                                                 |                 |                    |              | scale on        |

| 16 DIT MODE                                             | -                                               |                 |                    |              | DAC             |

| 16-BIT MODE                                             |                                                 |                 |                    |              |                 |

| DC Specifications <sup>15</sup>                         |                                                 | 1.4             |                    |              | D:4 -           |

| Resolution                                              |                                                 | 14              | . •                |              | Bits            |

| Relative Accuracy                                       | For 14-bit resolution                           |                 | ±3                 | _            | LSB             |

| Differential Nonlinearity                               | Guaranteed monotonic (14 bits)                  |                 | ±0.5               | ±1           | LSB             |

| Offset Error                                            | 1.2 V internal reference                        |                 | ±2                 | ±15          | mV              |

| Gain Error                                              | V <sub>REF</sub> range (reference = 1.2 V)      |                 |                    | ±1           | %               |

|                                                         | AVDD range                                      |                 |                    | ±1           | %               |

| Gain Error Mismatch                                     |                                                 |                 |                    | 0.1          | % of full       |

|                                                         |                                                 |                 |                    |              | scale on<br>DAC |

| DAC AC CHARACTERISTICS                                  |                                                 |                 |                    |              | Dite            |

| Voltage Output Settling Time                            |                                                 |                 | 10                 |              | μs              |

| Digital-to-Analog Glitch                                | 1 LSB change at major carry (where              |                 | ±20                |              | nV-sec          |

| Energy                                                  | maximum number of bits                          |                 |                    |              |                 |

| -                                                       | simultaneously change in the DACxDAT            |                 |                    |              |                 |

|                                                         | register)                                       |                 |                    |              |                 |

| TEMPERATURE SENSOR <sup>16</sup>                        | After user calibration                          |                 |                    |              |                 |

| Accuracy                                                | MCU in power down or standby mode               |                 | ±4                 |              | °C              |

| Thermal Impedance                                       | 32-lead LFCSP                                   |                 | TBD                |              | °C/W            |

|                                                         | 48-lead LFCSP                                   |                 | TBD                |              | °C/W            |

|                                                         | 48-lead LFQFP                                   |                 | TBD                |              | °C/W            |

| POWER-ON RESET (POR)                                    |                                                 |                 |                    |              |                 |

| POR Trip Level                                          | Refers to voltage at VDD pin                    |                 |                    |              |                 |

|                                                         | Power-on level                                  |                 | 2.0                |              | V               |

|                                                         | Power-down level                                |                 | 2.25               |              | V               |

| RESET Timeout from POR                                  | Maximum supply ramp between 1.8 V               |                 |                    | 128          | ms              |

|                                                         | to 2.25 V; after POR trip, VDD must             |                 |                    |              |                 |

|                                                         | reach 2.25 V within this time limit             |                 |                    |              |                 |

| EXCITATION CURRENT SOURCES                              |                                                 |                 |                    |              |                 |

| Output Current                                          | Available from each current source              | 200             | 1000               |              | μΑ              |

| Initial Tolerance at 25°C                               |                                                 |                 | ±5                 |              | %               |

| Drift                                                   |                                                 |                 | 200                |              | ppm/°C          |

| Initial Current matching at                             | Matching between both current                   |                 | ±0.5               |              | %               |

| 25°C                                                    | sources                                         |                 |                    |              |                 |

| Drift matching                                          |                                                 |                 | 20                 |              | ppm/°C          |

| Line Regulation (AV <sub>DD</sub> )                     | $AV_{DD} = 2.5 V \pm 5\%$                       |                 | 0.2                |              | %/V             |

| Output Compliance <sup>1</sup>                          |                                                 | $AV_{DD} - 0.7$ |                    | AGND - 30 mV | V               |

Rev. PrA | Page 6 of 100

| WATCHDOG TIMER (WDT)         Timeout Period¹         32.768 kHz clock, 256 prescale         0.008         512         sec           Timeout Step Size         7.8         ms           FLASH/EE MEMORY¹         10,000         Cycles           Data Retention¹8         20         Years           DIGITAL INPUTS         All digital inputs except NTRST         Input Leakage Current         Input (high) = DVDD         ±1         ±10         μA           Input Pull-up Current         Input (low) = 0 V         10         20         80         μA           Input Leakage Current         NTRST only: input (low) = 0 V         ±1         ±10         μA           Input Pull-Down Current         NTRST only: input (high) = DVDD         30         55         100         μA           LOGIC INPUTS¹         All logic inputs         0.4         V           VINL, Input Low Voltage         0.4         V           VINL, Input Low Voltage         0.8         V           VINL, Input High Voltage         1.7         V           VINL, Input High Voltage         1.7         V           VINL, Input Low Voltage         1.7         V           VINL, Input Low Voltage         1.2         pF           ON-CHIP OSCILLATORS         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timeout Step Size 7.8 ms  FLASH/EE MEMORY¹ Endurance¹² Data Retention¹8 DIGITAL INPUTS Input Leakage Current Input (high) = DVDD Input Leakage Current Input Leakage Current Input (low) = 0 V Input Leakage Current Input High Vollage VINH, Input Low Voltage VINH, Input High Voltage VINH, Input Low Voltage VINH, Input Low Voltage VINH, Input Low Voltage VINH, Input High Voltage VINH, Input High Voltage VINH, Input High Voltage VINH, Input High Voltage VINH, Input Low Voltage VINH, In  |

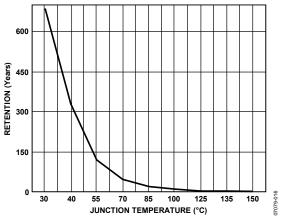

| FLASH/EE MEMORY¹   Endurance¹²   10,000   20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Endurance   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Data Retention 18  Digital Input S  Input Leakage Current Input (high) = DVDD Input Leakage Current Input (low) = 0 V Input Leakage Current Input Leakage Current Input Leakage Current Input (low) = 0 V Input Leakage Current Input Leakage Current Input Leakage Current Input Leakage Current Input Pull-Down Current Input Pull-Down Current Input NTRST only: input (low) = 0 V Input Pull-Down Current Input Low Voltage VINL, Input Low Voltage VINH, Input High Voltage VINH, Input High Voltage VINL, Input Low Vol  |

| Data Retention   18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Input Leakage Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Input Leakage Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Input Pull-up Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Input Capacitance Input Leakage Current Input Pull-Down Current Input Low Voltage Input Low Voltage Input Low Voltage Inputs, XTAL1 Only Input Low Voltage Inputs, XTAL1 Only Input High Voltage Input Low Voltage Inpu  |

| Input Leakage Current Input Pull-Down Current Input Pull-Down Current NTRST only: input (low) = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Input Pull-Down Current   NTRST only: input (high) = DVDD   30   55   100   μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LOGIC INPUTS¹ All logic inputs  VINL, Input Low Voltage VINH, Input High Voltage  CRYSTAL OSCILLATOR¹ Logic Inputs, XTAL1 Only VINL, Input Low Voltage VINH, Input High Voltage VINH, Input High Voltage VINH, Input High Voltage TATAL2 Capacitance TON-CHIP OSCILLATORS Oscillator Accuracy  All logic inputs O.4 V V V V V V V V V V V V V V V V V V V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VINL, Input Low Voltage VINH, Input High Voltage  CRYSTAL OSCILLATOR¹ Logic Inputs, XTAL1 Only VINL, Input Low Voltage VINH, Input High Voltage VINH, Input High Voltage 1.7 XTAL1 Capacitance 12 pF XTAL2 Capacitance 0N-CHIP OSCILLATORS Oscillator Accuracy 1-3 1-4  0.4  V V V V V V V V V V V V V V V V V V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VINH, Input High Voltage  CRYSTAL OSCILLATOR¹  Logic Inputs, XTAL1 Only  VINL, Input Low Voltage  VINH, Input High Voltage  1.7  XTAL1 Capacitance  TAL2 Capacitance  ON-CHIP OSCILLATORS  Oscillator  Accuracy  V  V  V  V  V  V  V  V  Accuracy  Accuracy  D.8  V  V  V  V  V  V  Accuracy  Accuracy  D.8  V  V  V  V  V  V  V  V  V  V  Accuracy  Accuracy  Accuracy  V  Accuracy  Accuracy  V  V  Accuracy  Accuracy  V  Accuracy  V  Accuracy  Accuracy  V  Accuracy   |

| CRYSTAL OSCILLATOR¹         Logic Inputs, XTAL1 Only           VINL, Input Low Voltage         0.8         V           VINH, Input High Voltage         1.7         V           XTAL1 Capacitance         12         pF           XTAL2 Capacitance         12         pF           ON-CHIP OSCILLATORS         32,768         kHz           Accuracy         -3         +3         %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Logic Inputs, XTAL1 Only VINL, Input Low Voltage VINH, Input High Voltage 1.7 XTAL1 Capacitance 12 pF XTAL2 Capacitance 12 pF ON-CHIP OSCILLATORS Oscillator Accuracy 32,768 kHz 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VINL, Input Low Voltage VINH, Input High Voltage VINH, Input High Voltage 1.7  XTAL1 Capacitance 12  pF  XTAL2 Capacitance 12  pF  ON-CHIP OSCILLATORS Oscillator Accuracy  -3  +3  0.8  V  V  KHZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VINH, Input High Voltage XTAL1 Capacitance 112 pF XTAL2 Capacitance 12 ON-CHIP OSCILLATORS Oscillator Accuracy 1.7  V  V  pF  12 pF  14 pF  15 pF  16 pF  17 pF  18 |

| XTAL1 Capacitance         12         pF           XTAL2 Capacitance         12         pF           ON-CHIP OSCILLATORS         32,768         kHz           Accuracy         -3         +3         %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTAL2 Capacitance         12         pF           ON-CHIP OSCILLATORS         32,768         kHz           Accuracy         -3         +3         %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ON-CHIP OSCILLATORS Oscillator Accuracy  32,768 kHz -3 +3 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

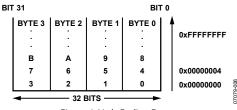

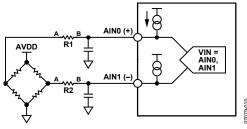

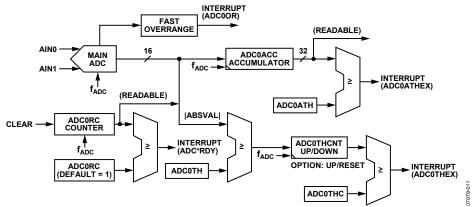

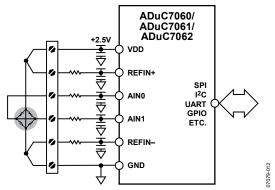

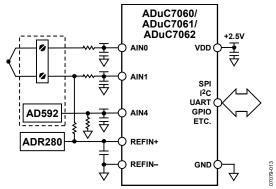

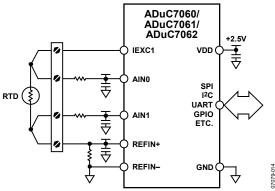

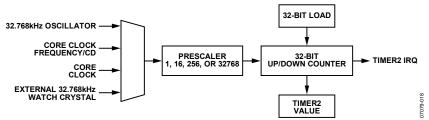

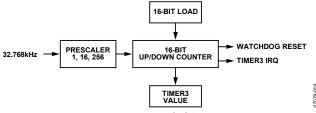

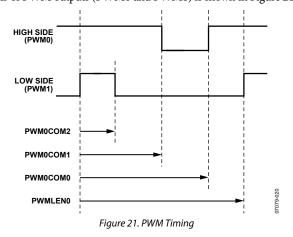

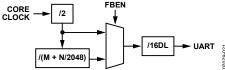

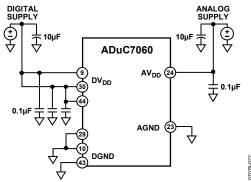

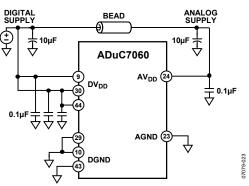

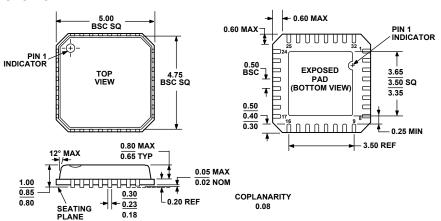

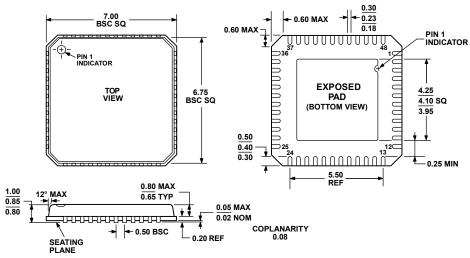

| Oscillator         32,768         kHz           Accuracy         -3         +3         %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |