# **DSP16210 Digital Signal Processor**

#### **Features**

- Optimized for applications requiring large internal memory, flexible I/O, and high cycle efficiency speech coding, speech compression, and channel coding

- Large on-chip dual-port RAM (60 Kwords of DPRAM)—eliminates need for fast external SRAM

- 2-input 40-bit arithmetic logic unit (ALU) with add/compare/select (ACS) for Viterbi acceleration

- 3-input adder

- DMA-based I/O—minimizes DSP core overhead for I/O processing

- Flexible power management modes for low system power dissipation

- Provides 200 DSP MIPS

- 10 ns instruction cycle time at 3 V

- Dual 16 x 16-bit multiplication and 40-bit accumulation in one instruction cycle for efficient algorithm implementations

- 31-instruction by 32-bit interruptible do-loop cache for high-speed, program-efficient, zero-overhead looping

- Nested interrupts and three interrupt priority levels for efficient control and task management operations

- On-chip boot ROM with hardware development system and boot code for flexible downloading

- On-chip, programmable, PLL clock synthesizer

- Enhanced serial I/O (ESIO) port designed to multiplex/demultiplex 64 Kbits/s, 32 Kbits/s, 16 Kbits/s, and 8 Kbits/s channels

- 26 Mbits/s simple serial I/O (SSIO) port coupled with DMA to support low-overhead I/O

- 16-bit parallel host interface (PHIF16) coupled with DMA to support low-overhead I/O

- Supports either 8-bit or 16-bit external bus configurations (8-bit external configuration supports either 8-bit or 16-bit logical transfers)

- Supports either Motorola<sup>1</sup> or Intel<sup>2</sup> protocols

- 8-bit control I/O interface for increased flexibility and lower system costs

- *IEEE*<sup>3</sup> 1149.1 test port (JTAG boundary scan)

- Full-speed in-circuit emulation hardware development system on-chip with eight address and two data watchpoint units for efficient application development

- Pin compatible with the DSP1620

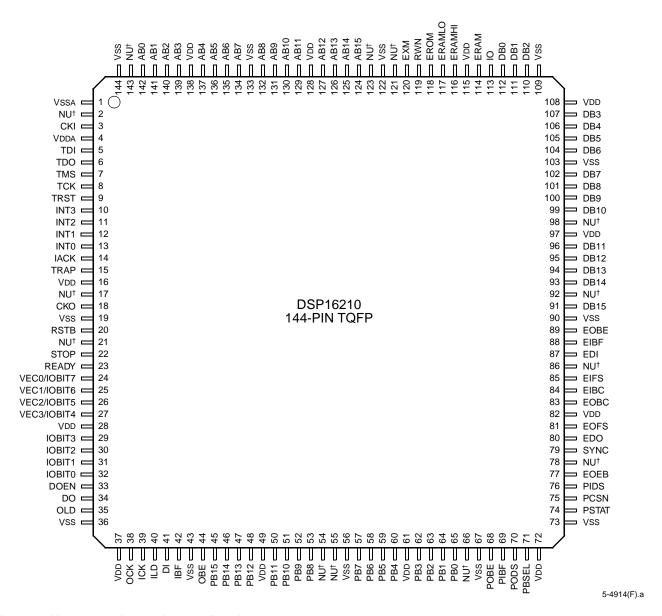

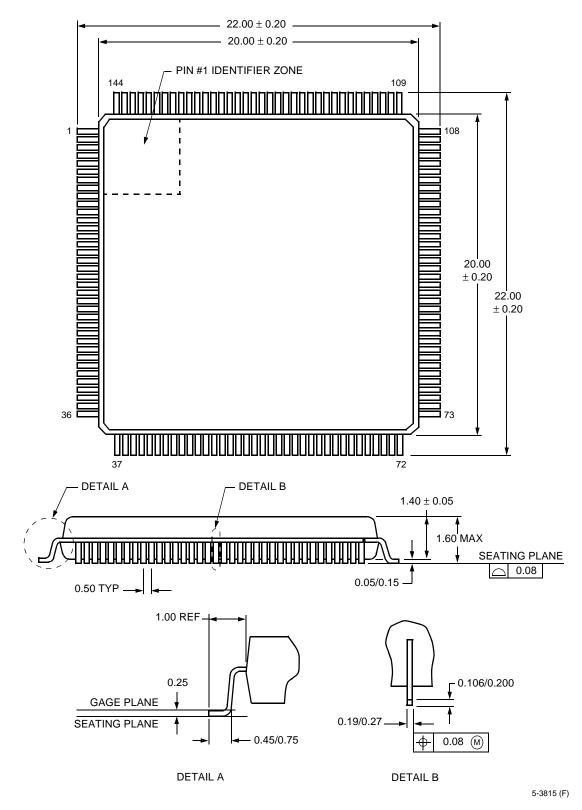

- 144-pin TQFP package

# **Description**

The DSP16210 is the first DSP device based on the DSP16000 digital signal processing core. It is manufactured in a 0.35  $\mu m$  CMOS technology and offers a 10 ns instruction cycle time at 3 V operation. Designed specifically for applications requiring a large amount of memory, a flexible DMA-based I/O structure, and high cycle efficiency, the DSP16210 is a signal coding device that can be programmed to perform a wide variety of fixed-point signal processing functions. The DSP16210 includes a mix of peripherals specifically intended to support processing-intensive but cost-sensitive applications.

The large on-chip RAM (60 Kwords of dual-port RAM) supports downloadable system design—a must for infrastructure applications—to support field upgrades for evolving coding standards. The DSP16210 can address up to 192 Kwords of external storage in both its code/coefficient memory address space and data memory address space. In addition, there is an internal boot ROM (IROM) that includes system boot code and hardware development system (HDS) code.

This device also contains a bit manipulation unit (BMU) and a two-input, 40-bit arithmetic logic unit (ALU) with add/compare/select (ACS) for enhanced signal coding efficiency and Viterbi acceleration.

To optimize I/O throughput and reduce the I/O service routine burden on the DSP core, the DSP16210 is equipped with two modular I/O units (MIOUs) that manage the simple serial I/O port (SSIO) and the 16-bit parallel host interface (PHIF16) peripherals. The MIOUs provide transparent DMA transfers between the peripherals and on-chip dual-port RAM.

The combination of large on-chip RAM, low power dissipation, fast instruction cycle times, and efficient I/O management makes the DSP16210 an ideal solution in a variety of emerging applications.

- 1. Motorola is a registered trademark of Motorola, Inc.

- 2. Intel is a registered trademark of Intel Corporation.

- 3. *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

# **Table of Contents**

| Contents                                                                | Page | Contents                                                            | Page |

|-------------------------------------------------------------------------|------|---------------------------------------------------------------------|------|

| ➤Features                                                               | 1    | ➤ Enhanced Serial I/O (ESIO) Unit                                   | 32   |

| ➤Description                                                            | 1    | ➤ Input Section                                                     |      |

| Notation Conventions                                                    | 9    | Output Section                                                      | 36   |

| ➤ Hardware Architecture                                                 | 9    | Modular I/O Units (MIOUs)                                           | 42   |

| ➤ DSP16210 Architectural Overview                                       | 9    | > IORAM                                                             | 42   |

| DSP16000 Core                                                           |      | MIOU Registers                                                      | 42   |

| ➤ Clock Synthesizer (PLL)                                               | 9    | MIOU Commands                                                       | 43   |

| > Dual-Port RAM (DPRAM)                                                 | 9    | > I/O Buffer Configuration                                          | 45   |

| Internal Boot ROM (IROM)                                                |      | Length Counters and MIOU Interrupts                                 | 46   |

| > IORAM and Modular I/O Units (MIOUs)                                   |      | > DMA Input Flow Control                                            |      |

| External Memory Interface (EMI)                                         |      | DMA Output Flow Control                                             |      |

| > Bit I/O (BIO) Unit                                                    |      | MIOU Performance                                                    |      |

| ➤ Enhanced Serial I/O (ESIO) Unit                                       |      | > Powering Down an MIOU                                             |      |

| > Simple Serial I/O (SSIO) Unit                                         |      | MIOU Command Latencies                                              |      |

| > Parallel Host Interface (PHIF16)                                      |      | ➤ Simple Serial I/O (SSIO) Unit                                     |      |

| Timers                                                                  |      | Programmable Modes                                                  |      |

| > Test Access Port (JTAG)                                               |      | ➤ Parallel Host Interface (PHIF16)                                  |      |

| Hardware Development System (HDS)                                       |      | > Programmability                                                   |      |

| > Pin Multiplexing                                                      |      | ➤ Bit Input/Output Unit (BIO)                                       |      |

| ➤ DSP16000 Core Architectural Overview                                  |      | ➤ Pin Multiplexing                                                  |      |

| System Control and Cache (SYS)                                          |      | ➤ Timers                                                            |      |

| Data Arithmetic Unit (DAU)                                              |      | ➤ Hardware Development System (HDS)                                 |      |

| <ul> <li>Y-Memory Space Address Arithmetic</li> </ul>                   |      | > JTAG Test Port                                                    |      |

| Unit (YAAU)                                                             | 15   | ➤ Clock Synthesis                                                   |      |

| <ul> <li>X-Memory Space Address Arithmetic</li> </ul>                   |      | <ul> <li>Phase-Lock Loop (PLL) Operation</li> </ul>                 |      |

| Unit (XAAU)                                                             | 15   | <ul> <li>Phase-Lock Loop (PLL) Operating</li> </ul>                 |      |

| > Reset                                                                 |      | Frequency                                                           | 58   |

| <ul> <li>Reset After Powerup or Power Interruptio</li> </ul>            | _    | <ul> <li>Phase-Lock Loop (PLL) Locking</li> </ul>                   |      |

| RSTB Pin Reset                                                          |      | <ul> <li>Phase-Lock Loop (PLL) Programming</li> </ul>               | 50   |

| > JTAG Controller Reset                                                 |      | Restrictions                                                        | 50   |

|                                                                         |      | <ul> <li>Phase-Lock Loop (PLL) Programming</li> </ul>               | 59   |

|                                                                         |      | Example                                                             | 60   |

|                                                                         |      | Phase-Lock Loop (PLL) Frequency                                     | 60   |

|                                                                         |      | Accuracy and Jitter                                                 | 60   |

| Interrupt Request Clearing Latency                                      |      |                                                                     |      |

| <ul><li>INT[3:0] and TRAP Pins</li><li>Low-Power Standby Mode</li></ul> |      | Phase-Lock Loop (PLL) Power Connection Payer Management             |      |

|                                                                         |      | Power Management                                                    |      |

| <ul> <li>Memory Maps</li> <li>Boot from External ROM</li> </ul>         |      | <ul><li>The powerc Control Register Bits</li><li>STOP Pin</li></ul> |      |

|                                                                         |      |                                                                     |      |

| Data Memory Map Selection                                               |      |                                                                     |      |

| External Memory Interface (EMI)                                         | 21   | > AWAIT Bit of the <b>alf</b> Register                              |      |

| Latency for Programming <b>mwait</b> and <b>ioc</b>                     | 07   | Power Management Examples                                           |      |

| Registers                                                               |      | Software Architecture                                               |      |

| Programmable Access Time                                                |      | ➤ Instruction Set Quick Reference                                   |      |

| > READY Pin Enables                                                     |      | Conditions Based on the State of Flags                              |      |

| Enable Delays                                                           |      | > Registers                                                         |      |

| Memory Map Selection                                                    |      | Peripheral Register Write-Read Latency                              |      |

| RWN Advance                                                             |      | Register Overview                                                   |      |

| CKO Pin Configuration                                                   |      | > Register Settings                                                 |      |

| Write Data Drive Delay                                                  |      | > Reset States                                                      |      |

| Functional Timing                                                       |      | RB Field Encoding                                                   |      |

| READY Pin                                                               | 31   | ➤Pin Information                                                    | 116  |

# Table of Contents (continued)

| Contents Pag                                    | ge | Contents                                 | Page |

|-------------------------------------------------|----|------------------------------------------|------|

| ➤Signal Descriptions1                           | 21 | ➤ Power Dissipation                      | 137  |

| > System Interface and Control I/O Interface1   | 22 | ➤Timing Characteristics and Requirements |      |

| > System Interface1                             | 22 | ➤ Phase-Lock Loop                        | 139  |

| Control I/O Interface1                          |    | > Wake-Up Latency                        | 140  |

| ➤ External Memory Interface1                    | 23 | ➤ DSP Clock Generation                   |      |

| ➤ ESIO Interface1                               |    | > Reset Circuit                          | 142  |

| > SSIO Interface1                               | 24 | > Reset Synchronization                  | 143  |

| > PHIF16 Interface1                             |    | > JTAG                                   |      |

| > JTAG Test Interface1                          |    | ➤ Interrupt and Trap                     |      |

| ➤DSP16210 Boot Routines1                        | 26 | ➤ Bit I/O                                |      |

| > Commands1                                     | 27 | > External Memory Interface              | 147  |

| ➤Device Characteristics1                        | 33 | > PHIF16                                 |      |

| ➤ Absolute Maximum Ratings1                     | 33 | > Simple Serial I/O                      | 161  |

| ➤ Handling Precautions1                         | 33 | ➤ Enhanced Serial I/O                    | 166  |

| ➤ Recommended Operating Conditions1             |    | ➤Outline Diagrams                        | 170  |

| Package Thermal Considerations                  |    | ➤ 144-Pin TQFP Outline Diagram           |      |

| ➤ Electrical Characteristics and Requirements 1 |    | · ·                                      |      |

# **List of Figures**

| Figures   | F                                                                                                              | Page |

|-----------|----------------------------------------------------------------------------------------------------------------|------|

|           | DSP16210 Block Diagram                                                                                         |      |

| Figure 2. | DSP16000 Core Block Diagram                                                                                    | 16   |

|           | INT[3:0] and TRAP Timing                                                                                       |      |

|           | Interleaved Internal DPRAM                                                                                     |      |

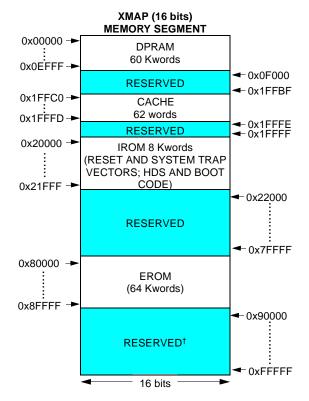

|           | X-Memory Space Memory Map                                                                                      |      |

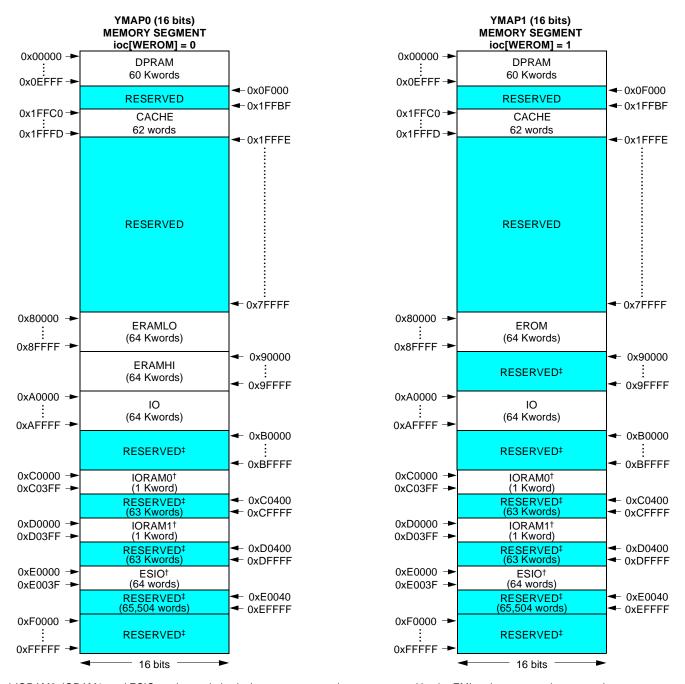

|           | Y-Memory Space Memory Maps                                                                                     |      |

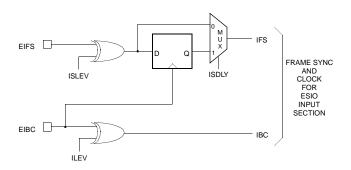

|           | Input Control Signal Conditioning                                                                              |      |

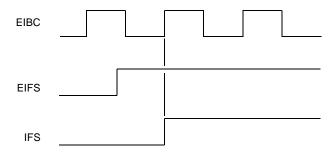

|           | Frame Sync Timing with ILEV = ISLEV = 0 and ISDLY = 1                                                          |      |

|           | Input Functional Timing                                                                                        |      |

| -         | D. Input Demultiplexer (IDMX) and Register File Structure                                                      |      |

|           | 1. Serial Input Clocking Example                                                                               |      |

|           | 2. Output Control Signal Conditioning                                                                          |      |

|           | 3. Output Functional Timing                                                                                    |      |

|           | 4. Output Multiplexer (OMX) and Register File Structure                                                        |      |

|           | 5. Serial Output Clocking Example                                                                              |      |

|           | 6. Modular I/O Units                                                                                           |      |

| -         | 7. Input and Output Buffer Configuration in IORAM(0,1)                                                         |      |

|           | 3. Clock Synthesizer (PLL) Block Diagram                                                                       |      |

| •         | 9. Internal Clock Selection and Disable Logic                                                                  |      |

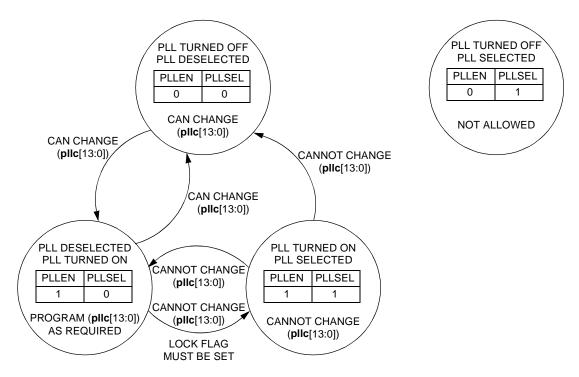

|           | O. Allowable States and State Changes of <b>pllc</b> Register Fields                                           |      |

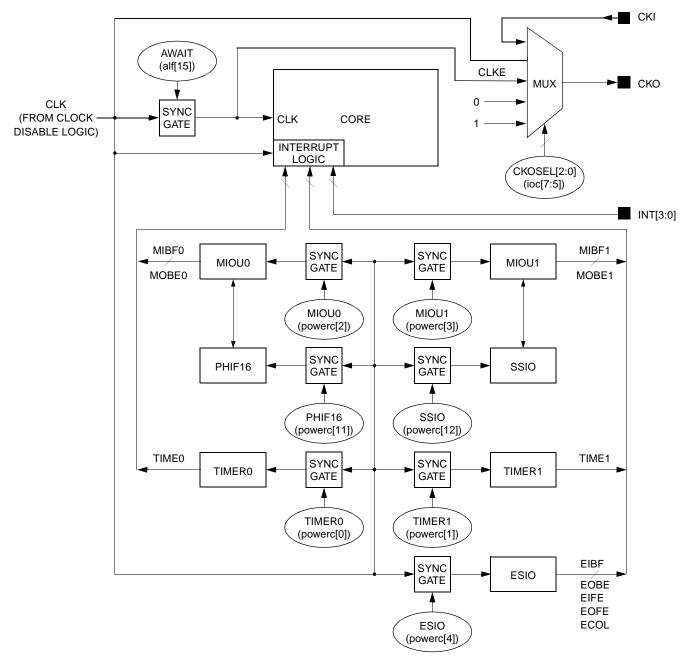

| -         | 1. Power Management and Clock Distribution                                                                     |      |

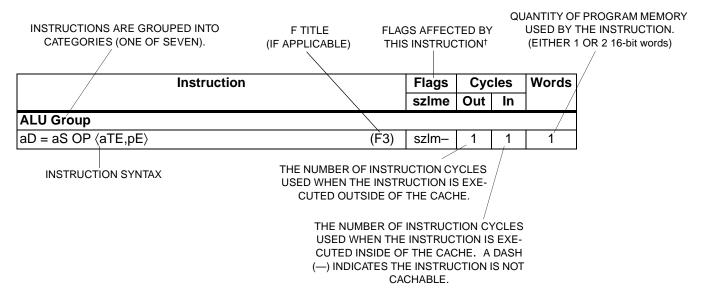

|           | 2. Interpretation of the Instruction Set Summary Table                                                         |      |

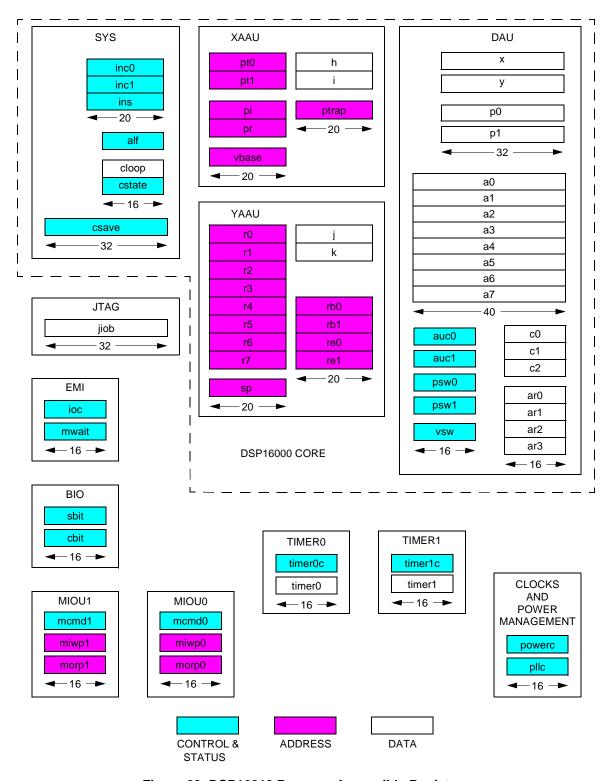

|           | 3. DSP16210 Program-Accessible Registers                                                                       |      |

|           | 4. DSP16210 144-Pin TQFP Pin Diagram (Top View)                                                                |      |

|           | 5. DSP16210 Pinout by Interface                                                                                |      |

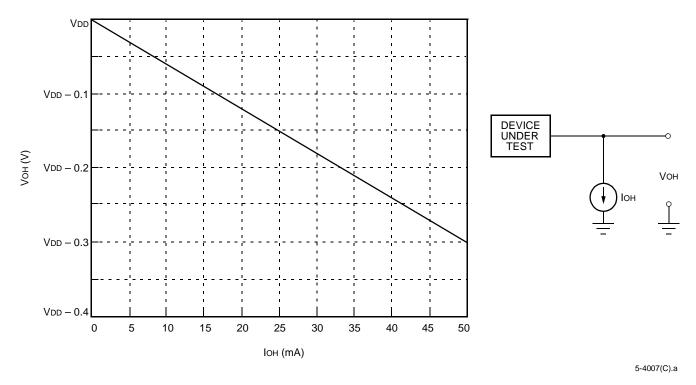

|           | 6. Plot of Von vs. Ion Under Typical Operating Conditions                                                      |      |

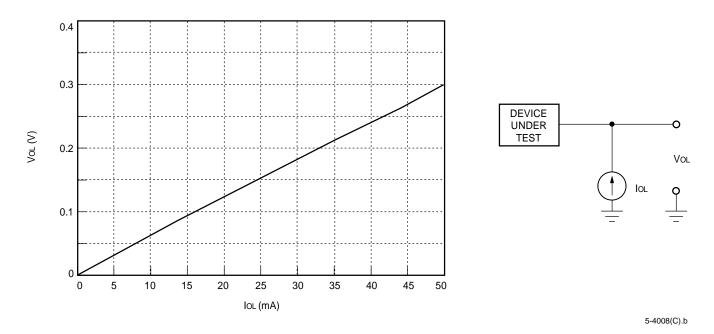

|           | 7. Plot of VoL vs. IoL Under Typical Operating Conditions                                                      |      |

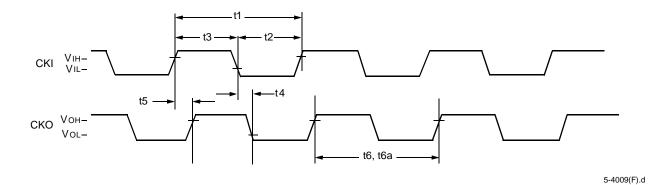

|           | 3. I/O Clock Timing Diagram                                                                                    |      |

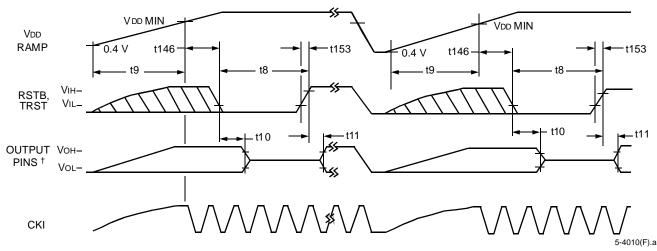

|           | 9. Powerup Reset and Device Reset Timing Diagram                                                               |      |

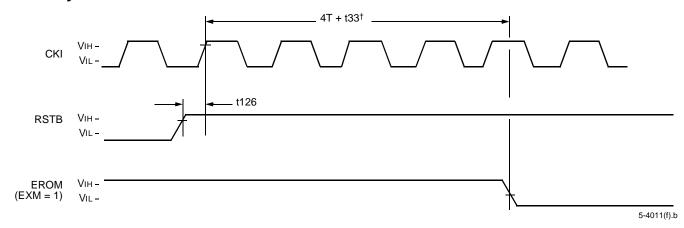

| -         | D. Reset Synchronization Timing                                                                                |      |

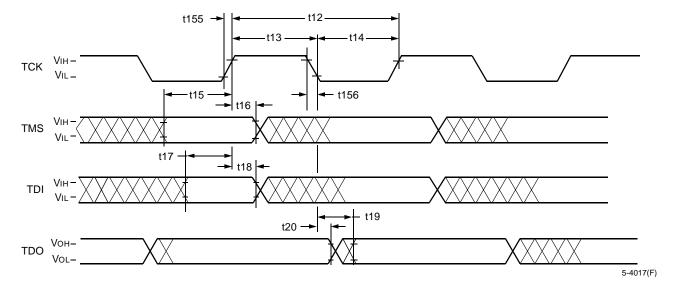

| •         | 1. JTAG I/O Timing Diagram                                                                                     |      |

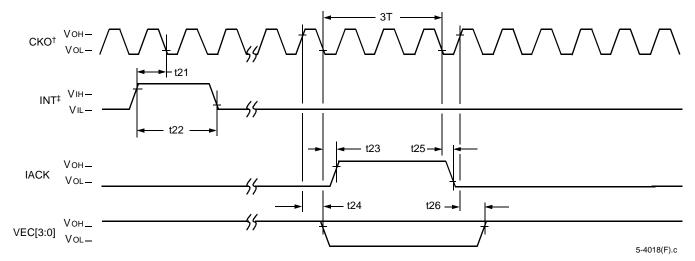

|           | 2. Interrupt and Trap Timing Diagram                                                                           |      |

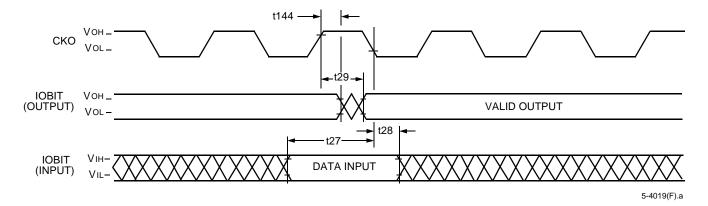

|           | 3. Write Outputs Followed by Read Inputs ( <b>cbit = IMMEDIATE</b> ; <b>a1 = sbit</b> ) Timing Characteristics |      |

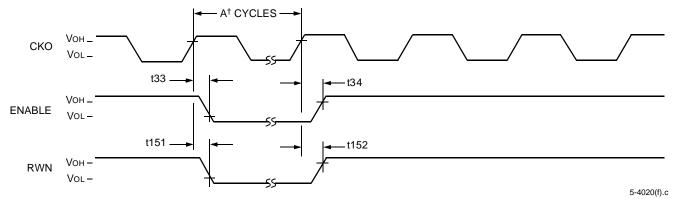

| -         | 4. Enable Transition Timing                                                                                    |      |

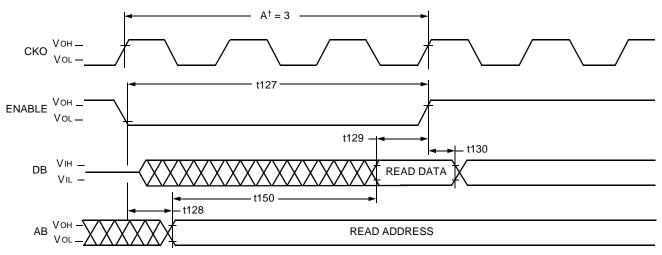

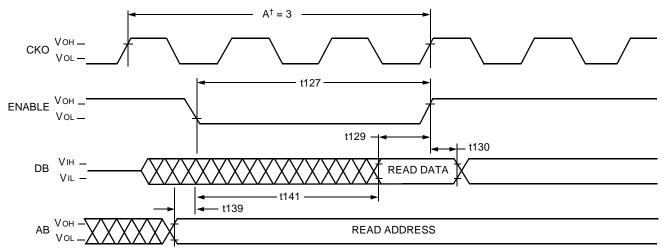

|           | 6. External Memory Data Read Timing Diagram (No Delayed Enable)                                                |      |

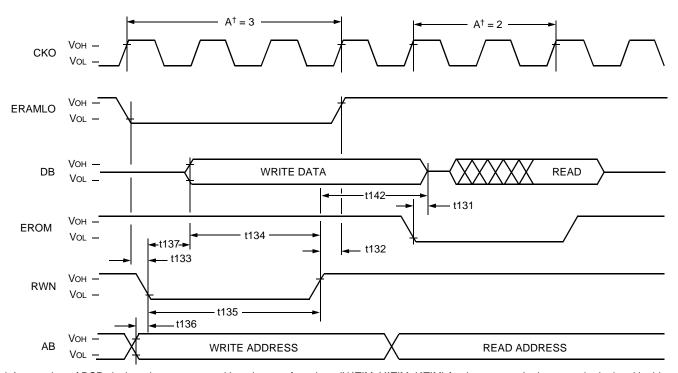

|           | 7. External Memory Data Write Timing Diagram (DENB2 = 0, DENB1 = 0, DENB0 = 0)                                 |      |

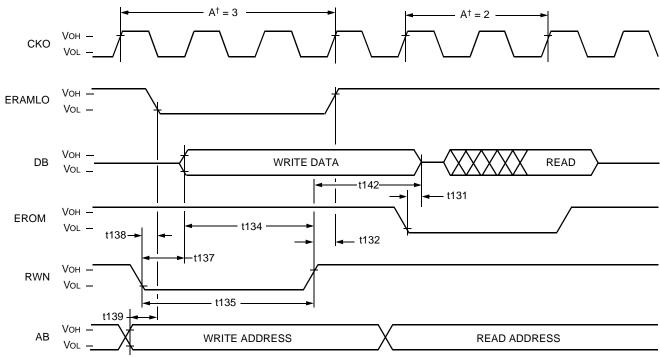

|           | 3. External Memory Data Write Timing Diagram (DENB2 = 0, DENB1 = 0, DENB0 = 0)                                 |      |

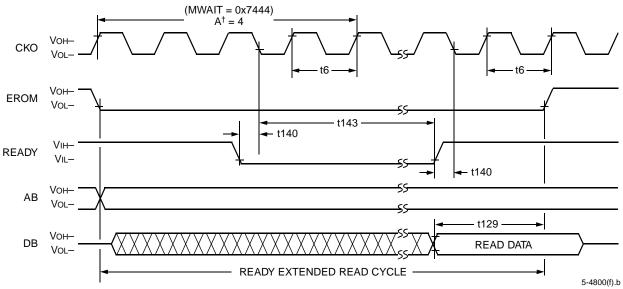

|           | 9. READY Extended Read Cycle Timing Diagram (DENB2 = 0, DENB1 = 1, DENB0 = 0)                                  |      |

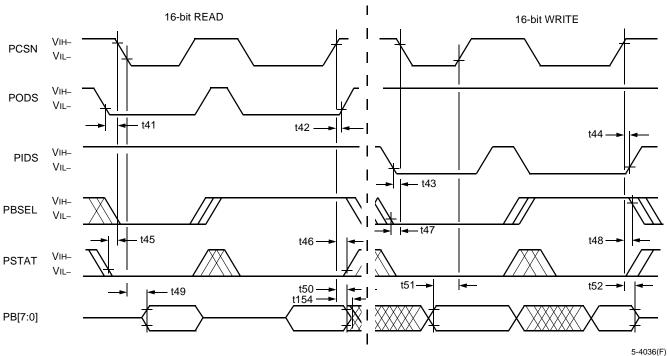

|           | D. PHIF16 <i>Intel</i> Mode Signaling (Read and Write) Timing Diagram                                          |      |

|           | 1. PHIF16 Intel Mode Signaling (Nead and White) Timing Diagram                                                 |      |

|           | 2. PHIF16 <i>Motorola</i> Mode Signaling (Read and Write) Timing Diagram                                       |      |

|           | 3. PHIF16 <i>Motorola</i> Mode Signaling (Nead and White) Finning Diagram                                      |      |

|           | 4. PHIF16 Intel or Motorola Mode Signaling (Status Register Read) Timing Diagram                               |      |

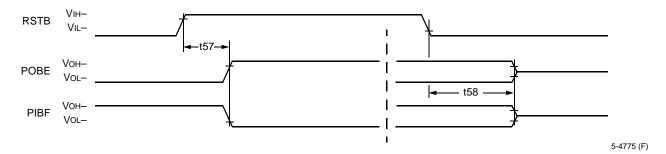

|           | 5. PIBF and POBE Reset Timing Diagram                                                                          |      |

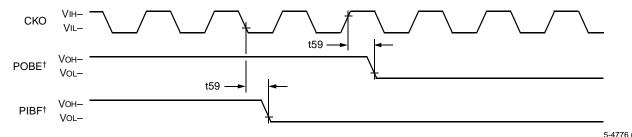

| -         | 5. POBE and PIBF Disable Timing Diagram                                                                        |      |

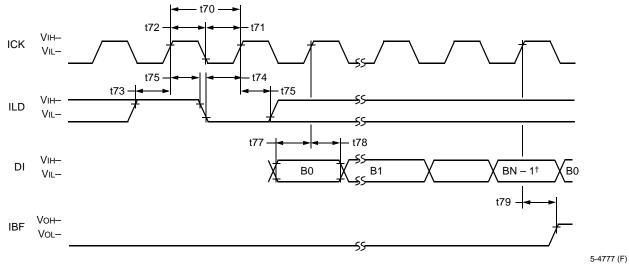

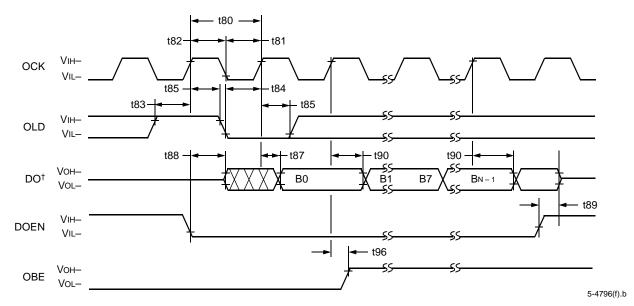

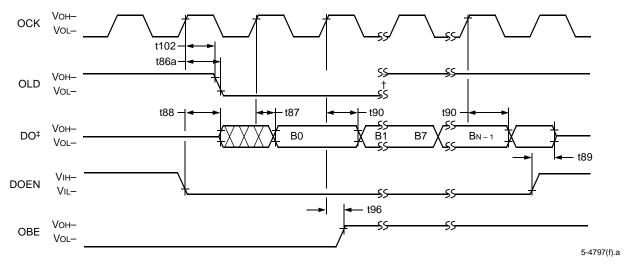

|           | 7. SSIO Passive Mode Input Timing Diagram                                                                      |      |

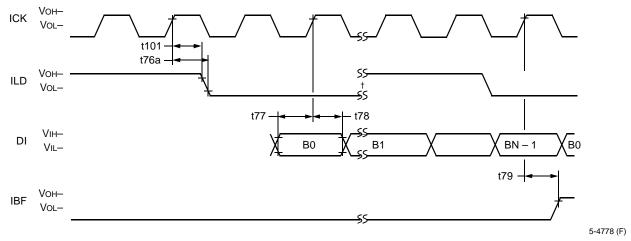

|           | 3. SSIO Active Mode Input Timing Diagram                                                                       |      |

|           | 9. SSIO Passive Mode Output Timing Diagram                                                                     |      |

|           | D. SSIO Active Mode Output Timing Diagram                                                                      |      |

|           | 1. Serial I/O Active Mode Clock Timing                                                                         |      |

# List of Figures (continued)

| Figure                                         | Page |

|------------------------------------------------|------|

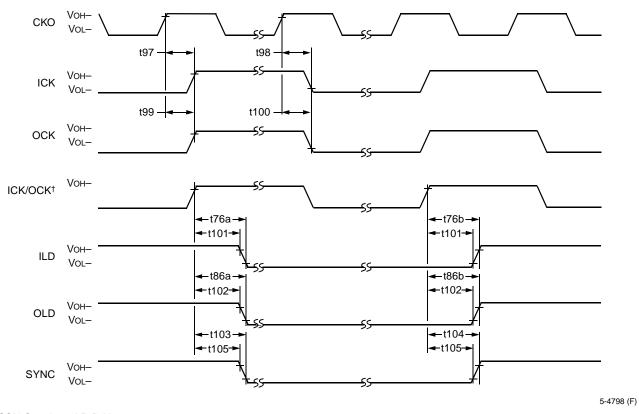

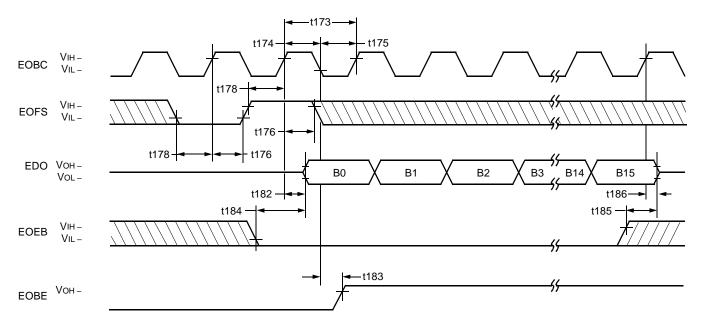

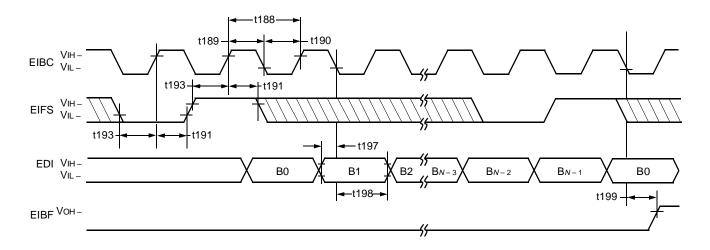

| ➤ Figure 52. Simple Mode Input Timing Diagram  | 166  |

| ➤ Figure 53. Simple Mode Output Timing Diagram |      |

| ➤ Figure 54. Frame Mode Input Timing Diagram   | 168  |

| ➤ Figure 55. Frame Mode Output Timing Diagram  |      |

# **List of Tables**

| Tables      |                                                                      | Page |

|-------------|----------------------------------------------------------------------|------|

| ➤ Table 1.  | DSP16210 Block Diagram Legend                                        |      |

| ➤ Table 2.  | DSP16000 Core Block Diagram Legend                                   |      |

| ➤ Table 3.  | State of Device Output and Bidirectional Pins During and After Reset |      |

| ➤ Table 4.  | Interrupt and User Trap Vector Table                                 | 21   |

| ➤ Table 5.  | Interrupt Control 0 and 1 (inc0, inc1) Registers                     | 22   |

| ➤ Table 6.  | Interrupt Status (ins) Register                                      | 22   |

| ➤ Table 7.  | Interrupt Request Clearing Latency                                   | 23   |

| ➤ Table 8.  | Access Time and Wait-States                                          | 28   |

| ➤ Table 9.  | Wait-States                                                          | 31   |

| ➤ Table 10. | ESIO Memory Map (Input Section)                                      | 32   |

|             | Input Channel Start Bit Registers                                    |      |

| ➤ Table 12. | ESIO Memory Map (Output Section)                                     | 36   |

| ➤ Table 13. | Output Channel Start Bit Registers                                   | 39   |

| ➤ Table 14. | ESIO Interrupts                                                      | 41   |

| ➤ Table 15. | Instructions for Programming MIOU Registers                          | 42   |

| ➤ Table 16. | MIOU(0,1) 16-Bit Directly Program-Accessible Registers               | 43   |

| ➤ Table 17. | MIOU Write-Only Command-Accessible Registers                         | 43   |

| ➤ Table 18. | MIOU(0,1) Command (mcmd(0,1)) Register                               | 44   |

| ➤ Table 19. | Effect of Reset on MIOU Interrupts and Registers                     | 44   |

|             | MIOU Interrupts                                                      |      |

| ➤ Table 21. | MIOU Command Latencies                                               | 48   |

| ➤ Table 22. | PHIF16 Output Function                                               | 51   |

|             | PHIF16 Input Function                                                |      |

| ➤ Table 24. | PHIF16 Status ( <b>PSTAT</b> ) Register                              | 51   |

|             | BIO Operations                                                       |      |

| ➤ Table 26. | BIO Flags                                                            | 52   |

|             | JTAG Boundary-Scan Register                                          |      |

|             | Clock Source Selection                                               |      |

|             | pllc Field Values Nbits[2:0] and Mbits[2:0]                          |      |

|             | Example Calculation of M and N                                       |      |

|             | DSP16210 Instruction Groups                                          |      |

|             | Instruction Set Summary                                              |      |

|             | Notation Conventions for Instruction Set Descriptions                |      |

|             | Overall Replacement Table                                            |      |

|             | F1 Instruction Syntax                                                |      |

|             | F1E Function Statement Syntax                                        |      |

|             | DSP16210 Conditional Mnemonics                                       |      |

|             | Program-Accessible Registers by Type, Listed Alphabetically          |      |

|             | ESIO Memory-Mapped Registers                                         |      |

|             | MIOU-Accessible Registers                                            |      |

|             | DMA-Accessible Registers                                             |      |

|             | alf Register                                                         |      |

| ➤ Table 43. | auc0 (Arithmetic Unit Control 0) Register                            | 92   |

|             | auc1 (Arithmetic Unit Control 1) Register                            |      |

|             | cbit (BIO Control) Register                                          |      |

|             | cstate (Cache State) Register                                        |      |

|             | ICR (ESIO Input Control) Register                                    |      |

|             | ICSB(0—7) (ESIO Input Channel Start Bit) Registers                   |      |

|             | ICSL(0—1) (ESIO Input Channel Sample Length) Registers               |      |

|             | ICVV (ESIO Input Channel Valid Vector) Register                      |      |

|             | ID (JTAG Identification) Register                                    |      |

# List of Tables (continued)

| Tables      |                                                                 | Page |

|-------------|-----------------------------------------------------------------|------|

| ➤ Table 52. | inc(0—1) (Interrupt Control) Registers                          | 97   |

| ➤ Table 53. | ins (Interrupt Status) Register                                 | 98   |

| ➤ Table 54. | ioc (I/O Configuration) Register                                | 99   |

| ➤ Table 55. | mcmd(0—1) (MIOU(0—1) Command) Registers                         | 100  |

| ➤ Table 56. | miwp(0—1) (MIOU(0—1) IORAM Input Write Pointer) Registers       | 100  |

| ➤ Table 57. | morp(0—1) (MIOU(0—1) IORAM Output Read Pointer) Registers       | 101  |

|             | mwait (EMI Configuration) Register                              |      |

| ➤ Table 59. | OCR (ESIO Output Control) Register                              | 102  |

| ➤ Table 60. | OCSB(0—7) (ESIO Output Channel Start Bit) Registers             | 103  |

| ➤ Table 61. | OCSL(0—1) (ESIO Output Channel Sample Length) Registers         | 103  |

|             | OCVV (ESIO Output Channel Valid Vector) Register                |      |

|             | PHIFC (PHIF16 Control) Register                                 |      |

|             | plic (Phase-Lock Loop Control) Register                         |      |

| ➤ Table 65. | powerc (Power Control) Register                                 | 106  |

|             | PSTAT (PHIF16 Status) Register                                  |      |

|             | psw0 (Processor Status Word 0) Register                         |      |

|             | psw1 (Processor Status Word 1) Register                         |      |

|             | sbit (BIO Status/Control) Register                              |      |

|             | SSIOC (SSIO Control) Register                                   |      |

|             | timer(0,1) (TIMER(0,1) Running Count) Register                  |      |

|             | timer(0,1)c (TIMER(0,1) Control) Register                       |      |

|             | vsw (Viterbi Support Word) Register                             |      |

|             | Core Register States After Reset—40-bit Registers               |      |

|             | Core Register States After Reset—32-bit Registers               |      |

|             | Core Register States After Reset—20-bit Registers               |      |

|             | Core Register States After Reset—16-bit Registers               |      |

|             | Peripheral (Off-Core) Register States After Reset               |      |

|             | RB Field                                                        |      |

|             | Pin Descriptions                                                |      |

|             | Command Encoding for Boot Routines                              |      |

|             | Absolute Maximum Ratings                                        |      |

|             | Recommended Operating Conditions                                |      |

|             | Package Thermal Considerations                                  |      |

|             | Electrical Characteristics and Requirements                     |      |

|             | Power Dissipation                                               |      |

|             | Frequency Ranges for PLL Output                                 |      |

|             | PLL Loop Filter Settings and Lock-In Time                       |      |

|             | Wake-Up Latency                                                 |      |

|             | Timing Requirements for Input Clock                             |      |

|             | Timing Characteristics for Input Clock and Output Clock         |      |

|             | Timing Requirements for Powerup Reset and Device Reset          |      |

|             | Timing Characteristics for Powerup Reset and Device Reset       |      |

|             | Timing Requirements for Reset Synchronization Timing            |      |

|             | Timing Requirements for JTAG I/O                                |      |

|             | Timing Requirements for JTAG I/O                                |      |

|             | Timing Characteristics for Trag I/O                             |      |

|             |                                                                 |      |

|             | Timing Characteristics for Interrupt and Trap                   |      |

|             | Timing Requirements for BIO Input Read                          |      |

|             | Timing Characteristics for BIO Output                           |      |

|             |                                                                 |      |

| rable 10∠   | 2. Timing Characteristics for External Memory Access (DENB = 0) | 148  |

# List of Tables (continued)

| Tables                                                                                          | Page |

|-------------------------------------------------------------------------------------------------|------|

| ➤ Table 103.Timing Requirements for External Memory Read (DENB = 0)                             | 148  |

| ➤ Table 104.Timing Characteristics for External Memory Access (DENB = 1)                        | 149  |

| ➤ Table 105.Timing Requirements for External Memory Read (DENB = 1)                             | 149  |

| ➤ Table 106.Timing Characteristics for External Memory Data Write (RWNADV = 0, DENB = 0)        | 150  |

| ➤ Table 107.Timing Characteristics for External Memory Data Write (RWNADV = 1, DENB = 1)        | 151  |

| ➤ Table 108.Timing Requirements for READY Extended Read Cycle Timing                            | 152  |

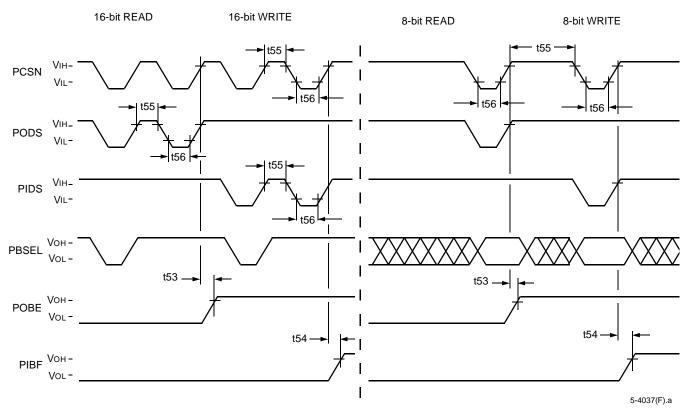

| ➤ Table 109.Timing Requirements for PHIF16 Intel Mode Signaling (Read and Write)                | 153  |

| ➤ Table 110.Timing Characteristics for PHIF16 Intel Mode Signaling (Read and Write)             | 154  |

| ➤ Table 111.Timing Requirements for PHIF16 Intel Mode Signaling (Pulse Period and Flags)        | 155  |

| ➤ Table 112.Timing Characteristics for PHIF16 Intel Mode Signaling (Pulse Period and Flags)     | 155  |

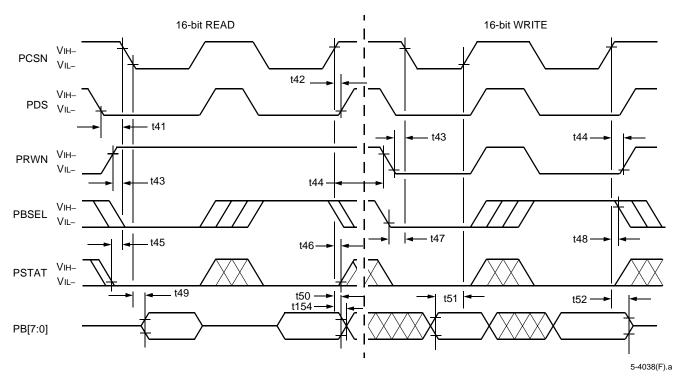

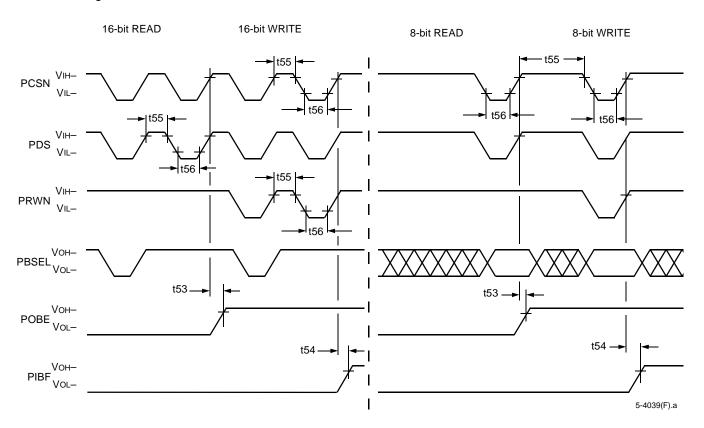

| ➤ Table 113. Timing Requirements for PHIF16 Motorola Mode Signaling (Read and Write)            | 156  |

| ➤ Table 114.Timing Characteristics for PHIF16 Motorola Mode Signaling (Read and Write)          | 157  |

| ➤ Table 115. Timing Characteristics for PHIF16 Motorola Mode Signaling (Pulse Period and Flags) | 158  |

| ➤ Table 116. Timing Requirements for PHIF16 Motorola Mode Signaling (Pulse Period and Flags)    | 158  |

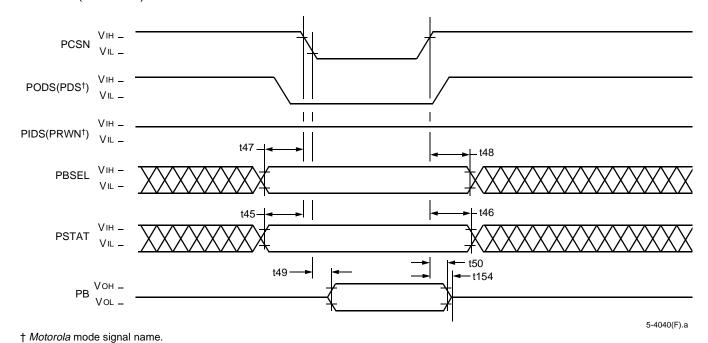

| ➤ Table 117. Timing Requirements for Intel and Motorola Mode Signaling (Status Register Read)   | 159  |

| ➤ Table 118.Timing Characteristics for Intel and Motorola Mode Signaling (Status Register Read) | 159  |

| ➤ Table 119.PHIF16 Timing Characteristics for PIBF and POBE Reset                               | 160  |

| ➤ Table 120.PHIF16 Timing Characteristics for POBE and PIBF Disable                             | 160  |

| ➤ Table 121.Timing Requirements for Serial Inputs (Passive Mode)                                | 161  |

| ➤ Table 122.Timing Characteristics for Serial Outputs (Passive Mode)                            | 161  |

| ➤ Table 123.Timing Requirements for Serial Inputs (Active Mode)                                 | 162  |

| ➤ Table 124.Timing Characteristics for Serial Outputs (Active Mode)                             | 162  |

| ➤ Table 125.Timing Requirements for Serial Inputs (Passive Mode)                                | 163  |

| ➤ Table 126.Timing Characteristics for Serial Outputs (Passive Mode)                            | 163  |

| ➤ Table 127.Timing Characteristics for Serial Output (Active Mode)                              | 164  |

| ➤ Table 128.Timing Characteristics for Signal Generation (Active Mode)                          | 165  |

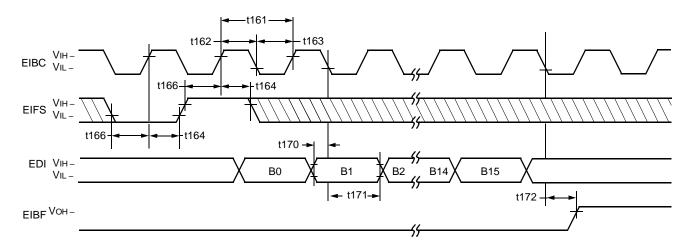

| ➤ Table 129.Timing Requirements for ESIO Simple Input Mode                                      | 166  |

| ➤ Table 130.Timing Characteristics for ESIO Simple Input Mode                                   | 166  |

| ➤ Table 131.Timing Requirements for ESIO Simple Output Mode                                     | 167  |

| ➤ Table 132.Timing Characteristics for ESIO Simple Output Mode                                  | 167  |

| ➤ Table 133.Timing Requirements for ESIO Frame Input Mode                                       |      |

| ➤ Table 134.Timing Characteristics for ESIO Frame Input Mode                                    |      |

| ➤ Table 135.Timing Requirements for ESIO Frame Output Mode                                      | 169  |

| ➤ Table 136 Timing Characteristics for ESIO Frame Output Mode                                   | 169  |

#### **Notation Conventions**

The following notation conventions apply to this data sheet:

lower-case Registers that are directly writable or

readable by DSP16210 core instruc-

tions are lower-case.

UPPER-CASE Device flags, I/O pins, and registers

that are not directly writable or readable by DSP16210 core instructions

are upper-case.

**boldface** Register names and DSP16210 core

instructions are printed in boldface when used in text descriptions.

italics Documentation variables that are re-

placed are printed in italics.

courier DSP16210 program examples are

printed in courier font.

[] Square brackets enclose a range of

numbers that represents multiple bits in a single register or bus. The range of numbers is delimited by a colon. For example, **ioc**[7:5] are bits 7—5 of the

program-accessible ioc register.

Angle brackets enclose a list of items

delimited by commas or a range of items delimited by a dash (—), one of which is selected if used in an instruction. For example, ICSB(0—7) represents the eight memory-mapped

registers ICSB0, ICSB1, . . . , ICSB7, and the general instruction

$aTE\langle h, I \rangle = RB$  can be replaced with

a0h = timer0.

# **Hardware Architecture**

The DSP16210 device is a 16-bit fixed-point programmable digital signal processor (DSP). The DSP16210 consists of a DSP16000 core together with on-chip memory and peripherals. Advanced architectural features with an expanded instruction set deliver a dramatic increase in performance for signal coding algorithms. This increase in performance together with an efficient design implementation results in an extremely cost- and power-efficient solution for wireless and multimedia applications.

#### **DSP16210 Architectural Overview**

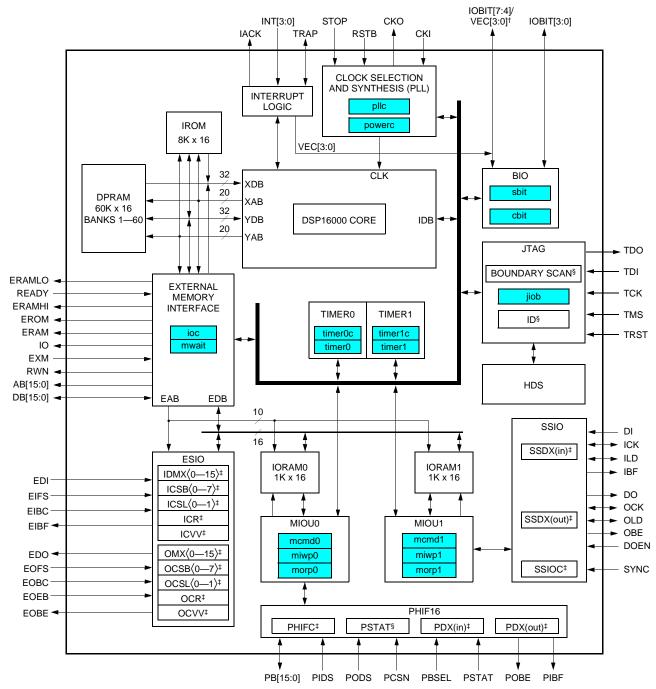

Figure 1 on page 10 shows a block diagram of the DSP16210. The following blocks make up this device.

#### DSP16000 Core

The DSP16000 core is the signal-processing engine of the DSP16210. It is a modified Harvard architecture with separate sets of buses for the instruction/coefficient (X-memory) and data (Y-memory) spaces. Each set of buses has 20 bits of address and 32 bits of data. The core contains data and address arithmetic units and control for on-chip memory and peripherals.

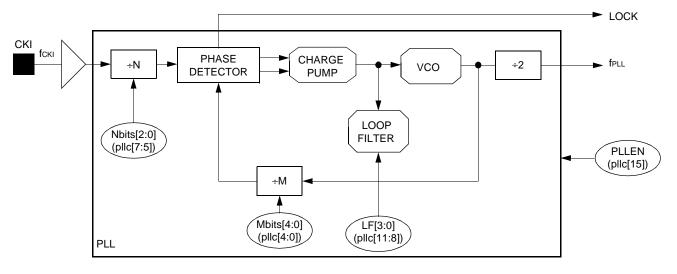

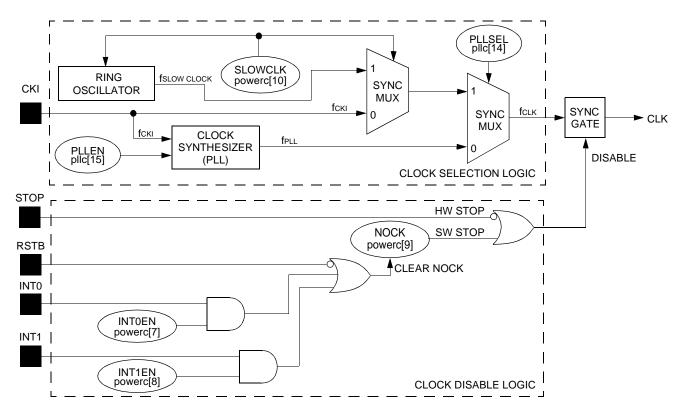

#### **Clock Synthesizer (PLL)**

The DSP16210 exits device reset with an input clock (CKI) as the source for the internal clock (CLK). An onchip clock synthesizer (PLL) that runs at a frequency multiple of CKI can also be used to generate CLK. The clock synthesizer is deselected and powered down on reset. For low-power operation, an internally generated slow clock can drive the DSP.

The clock synthesizer and other programmable clock sources are discussed in Clock Synthesis beginning on page 56. The use of these programmable clock sources for power management is discussed in Power Management beginning on page 61.

#### **Dual-Port RAM (DPRAM)**

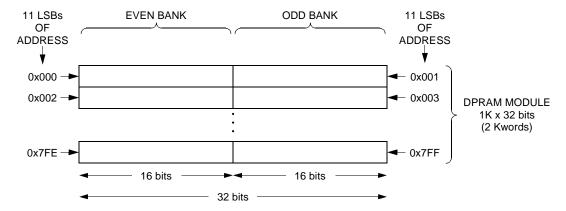

This block contains 60 banks (banks 1—60) of zero wait-state memory. Each bank consists of 1K 16-bit words and has separate address and data ports to the instruction/coefficient (X-memory) and data (Y-memory) spaces. DPRAM is organized into even and odd interleaved banks where each even/odd pair is a 32-bit wide module (see Figure 4 on page 25 for details). Placing instructions and Y-memory data in the same 2K module of DPRAM is not supported and may cause undefined results.

A program can be downloaded from slow off-chip memory into DPRAM, and then executed without waitstates. DPRAM is also useful for improving convolution performance in cases where the coefficients are adaptive. Since DPRAM can be downloaded through the JTAG port, full-speed remote in-circuit emulation is possible.

# **DSP16210 Architectural Overview (continued)**

<sup>†</sup> VEC0 corresponds to IOBIT7, VEC1 corresponds to IOBIT6, VEC2 corresponds to IOBIT5, and VEC3 corresponds to IOBIT4.

Figure 1. DSP16210 Block Diagram

<sup>‡</sup> These registers are not directly program accessible.

<sup>§</sup> These registers are accessible through pins only.

# **DSP16210 Architectural Overview** (continued)

Table 1. DSP16210 Block Diagram Legend

| Symbol     | Description                                       |  |

|------------|---------------------------------------------------|--|

| BIO        | Bit I/O Unit                                      |  |

| cbit       | BIO Control Register                              |  |

| CLK        | Internal Clock Signal                             |  |

| DPRAM      | Dual-port Random-Access Memory                    |  |

| EAB        | EMI Address Bus                                   |  |

| EDB        | EMI Data Bus                                      |  |

| ESIO       | Enhanced Serial I/O Unit                          |  |

| HDS        | Hardware Development System Unit                  |  |

| ICR        | ESIO Input Control Register                       |  |

| ICSB(0—7)  | ESIO Input Channel Start Bit Registers            |  |

| ICSL(0—1)  | ESIO Input Channel Sample Length Registers        |  |

| ICVV       | ESIO Input Channel Valid Vector Register          |  |

| IDMX(0—15) | ESIO Input Demultiplexer Registers                |  |

| ID         | JTAG Device Identification Register               |  |

| IDB        | Internal Data Bus                                 |  |

| ioc        | I/O Configuration Register                        |  |

| IORAM0     | Internal I/O RAM 0: Shared with MIOU0             |  |

| IORAM1     | Internal I/O RAM 1: Shared with MIOU1             |  |

| IROM       | Internal Boot Read-Only Memory                    |  |

| jiob       | JTAG Test Register                                |  |

| JTAG       | JTAG Test Port                                    |  |

| MIOU0      | Modular I/O Unit 0: Controls PHIF16               |  |

| mcmd0      | MIOU0 Command Register                            |  |

| miwp0      | MIOU0 IORAM0 Input Write Pointer                  |  |

| morp0      | MIOU0 IORAM0 Output Read Pointer                  |  |

| MIOU1      | Modular I/O Unit 1: Controls SSIO                 |  |

| mcmd1      | MIOU1 Command Register                            |  |

| miwp1      | MIOU1 IORAM1 Input Write Pointer                  |  |

| morp1      | MIOU1 IORAM1 Output Read Pointer                  |  |

| mwait      | EMI Configuration Register                        |  |

| OCR        | ESIO Output Control Register                      |  |

| OCSB(0—7)  | ESIO Output Channel Start Bit Registers           |  |

| OCSL(0—1)  | ESIO Output Channel Sample Length Registers       |  |

| OCVV       | ESIO Output Channel Valid Vector Register         |  |

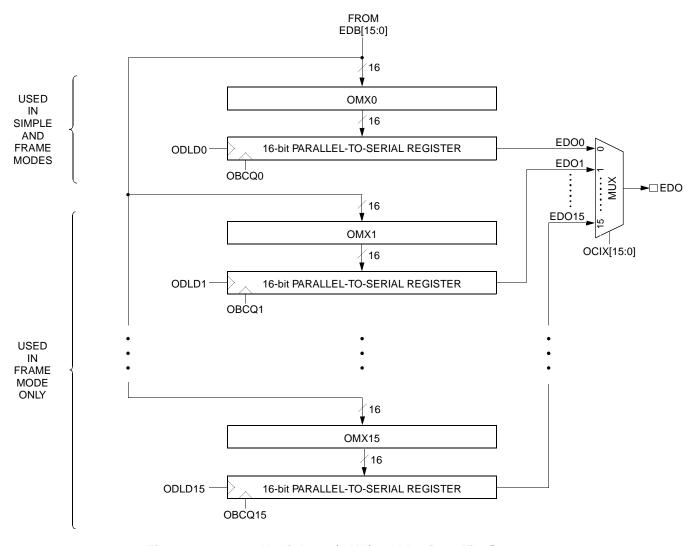

| OMX(0—15)  | ESIO Output Multiplexer Registers                 |  |

| PDX(in)    | PHIF16 Input Register; Readable by MIOU0          |  |

| PDX(out)   | PHIF16 Output Register; Writable by MIOU0         |  |

| PHIF16     | 16-bit Parallel Host Interface                    |  |

| PHIFC      | PHIF16 Control Register: Programmed Through MIOU0 |  |

| PLL<br>"   | Phase-Lock Loop                                   |  |

| plic       | Phase-Lock Loop Control Register                  |  |

#### **DSP16210 Architectural Overview** (continued)

Table 1. DSP16210 Block Diagram Legend (continued)

| Symbol    | Description                                     |  |

|-----------|-------------------------------------------------|--|

| powerc    | Power Control Register                          |  |

| PSTAT     | PHIF16 Status Register                          |  |

| sbit      | BIO Status/Control Register                     |  |

| SSDX(in)  | SSIO Input Register; Readable by MIOU1          |  |

| SSDX(out) | SSIO Output Register; Writable by MIOU1         |  |

| SSIO      | Simple Serial I/O Unit                          |  |

| SSIOC     | SSIO Control Register: Programmed Through MIOU1 |  |

| TIMER0    | Programmable Timer 0                            |  |

| timer0    | Timer Running Count Register for TIMER0         |  |

| timer0c   | Timer Control Register for TIMER0               |  |

| TIMER1    | Programmable Timer 1                            |  |

| timer1    | Timer Running Count Register for TIMER1         |  |

| timer1c   | Timer Control Register for TIMER1               |  |

| XAB       | X-Memory Space Address Bus                      |  |

| XDB       | X-Memory Space Data Bus                         |  |

| YAB       | Y-Memory Space Address Bus                      |  |

| YDB       | Y-Memory Space Data Bus                         |  |

#### Internal Boot ROM (IROM)

The DSP16210 includes a boot ROM that contains hardware development code and boot routines. The boot routines are available for use by the programmer and are detailed in DSP16210 Boot Routines beginning on page 126.

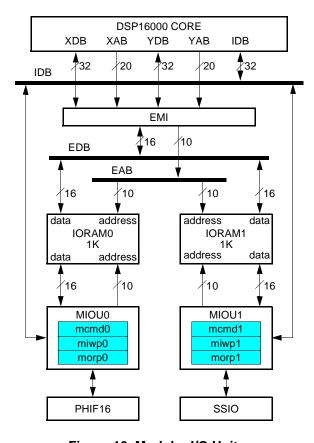

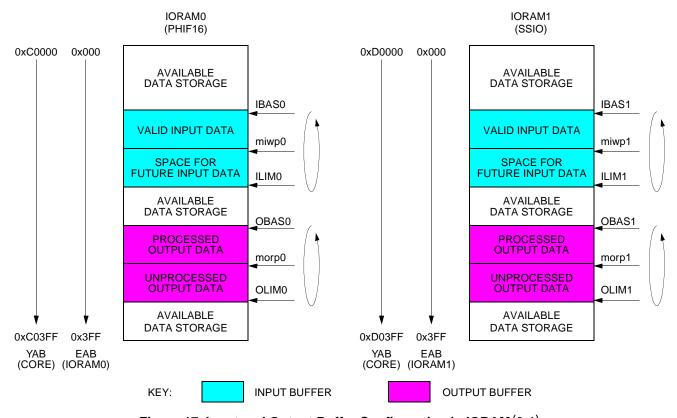

#### **IORAM** and **Modular I/O Units (MIOUs)**

IORAM storage consists of two 1 Kword banks of memory, IORAM0 and IORAM1. Each IORAM bank has two 16-bit data and two 10-bit address ports; an IORAM bank can be shared with the core and a modular I/O unit (MIOU) to implement a DMA-based I/O system. IORAM supports concurrent core execution and MIOU I/O processing.

MIOU0 (controls PHIF16) is attached to IORAM0; MIOU1 (controls SSIO) is attached to IORAM1. Portions of IORAM not dedicated to I/O processing can be used as general-purpose data storage.

Placing instructions and Y-memory data in the same IORAM is not supported and may cause undefined results.

The IORAMs and MIOUs are described in detail in Modular I/O Units (MIOUs) beginning on page 42.

#### **External Memory Interface (EMI)**

The EMI connects the DSP16210 to external memory and I/O devices. It multiplexes the two sets of core buses (X and Y) onto a single set of external buses—a 16-bit address bus (AB[15:0]) and 16-bit data bus (DB[15:0]). These external buses can access external RAM (ERAMHI/ERAMLO), external ROM (EROM), and memory-mapped I/O space (IO).

The EMI also manages the on-chip IORAM and ESIO storage. It multiplexes the two sets of core buses onto a single set of internal buses—a 10-bit address bus (EAB[9:0]) and 16-bit data bus (EDB[15:0])—to interface to the IORAMs and ESIO memory-mapped registers.

Instructions can transparently reference external memory, IORAM, and ESIO storage from either set of core buses. The EMI automatically translates a single 32-bit access into two 16-bit accesses and vice versa.

The EMI is described in detail in External Memory Interface (EMI) beginning on page 27.

#### **DSP16210 Architectural Overview** (continued)

# Bit I/O (BIO) Unit

The BIO unit provides convenient and efficient monitoring and control of eight individually configurable pins (IOBIT[7:0]). When configured as outputs, the pins can be individually set, cleared, or toggled. When configured as inputs, individual pins or combinations of pins can be tested for patterns. Flags returned by the BIO are testable by conditional instructions. See Bit Input/Output Unit (BIO) beginning on page 52 for more details.

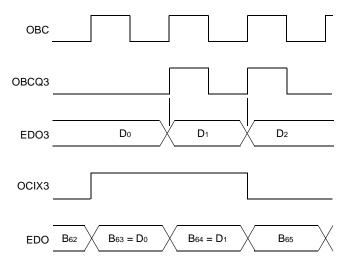

# Enhanced Serial I/O (ESIO) Unit

The ESIO is a programmable, hardware-managed, passive, double-buffered full-duplex serial input/output port designed to support glueless multichannel I/O processing on a TDM (time-division multiplex) highway. In simple mode, the ESIO supports data rates of up to 26 Mbits/s for a single channel with either 8-bit or 16-bit data lengths. In frame mode, the ESIO processes up to 16 logical TDM channels with a data rate of up to 8.192 Mbits/s. For more information on the ESIO, see Enhanced Serial I/O (ESIO) Unit beginning on page 32.

#### Simple Serial I/O (SSIO) Unit

The SSIO unit offers a full-duplex, double-buffered external channel that operates at up to 26 Mbits/s. Commercially available codecs and time-division multiplex channels can be interfaced to the SSIO with few, if any, additional components.

The SSIO is a DMA peripheral managed by MIOU1. See Simple Serial I/O (SSIO) Unit beginning on page 49 for more information.

#### Parallel Host Interface (PHIF16)

The PHIF16 is a DMA peripheral managed by MIOU0. It is a passive 16-bit parallel port that can be configured to interface to either an 8- or 16-bit external bus containing other Lucent Technologies DSPs, microprocessors, or off-chip I/O devices. The PHIF16 port supports either *Motorola* or *Intel* protocols.

When operating in the 16-bit external bus configuration, PHIF16 can be programmed to swap high and low bytes. When operating in 8-bit external bus configuration, PHIF16 is accessed in either an 8-bit or 16-bit logical mode. In 16-bit mode, the host selects either a high

or low byte access; in 8-bit mode, only the low byte is accessed.

Additional software-programmable features allow for a glueless host interface to microprocessors (see Parallel Host Interface (PHIF16) beginning on page 49).

#### **Timers**

The two timers can be used to provide an interrupt, either single or repetitive, at the expiration of a programmed interval. More than nine orders of magnitude of interval selection are provided. The timers can be stopped and restarted at any time under program control. See Timers beginning on page 53 for more information.

# **Test Access Port (JTAG)**

The DSP16210 provides a test access port that conforms to *IEEE* 1149.1 (JTAG). The JTAG port provides boundary scan test access and also controls the Hardware Development System (HDS). See JTAG Test Port beginning on page 54 for details.

#### **Hardware Development System (HDS)**

The HDS is an on-chip hardware module available for debugging assembly-language programs that execute on the DSP16000 core in real-time. The main capability of the HDS is in allowing controlled visibility into the core's state during program execution. The HDS is enhanced with powerful debugging capabilities such as complex breakpointing conditions, multiple data/address watchpoint registers, and an intelligent trace mechanism for recording discontinuities. See Hardware Development System (HDS) beginning on page 54 for details.

# **Pin Multiplexing**

The upper four BIO pins (IOBIT[7:4]) are multiplexed with the vectored interrupt identification pins (VEC[3:0]). Specifically, VEC0 is multiplexed with IOBIT7, VEC1 with IOBIT6, VEC2 with IOBIT5, and VEC3 with IOBIT4. VEC[3:0] are connected to the package pins and IOBIT[7:4] are disconnected immediately after device reset. To select IOBIT[7:4] to be connected to these pins, the program must set EBIO (bit 8 of the **ioc** register).

# **DSP16000 Core Architectural Overview**

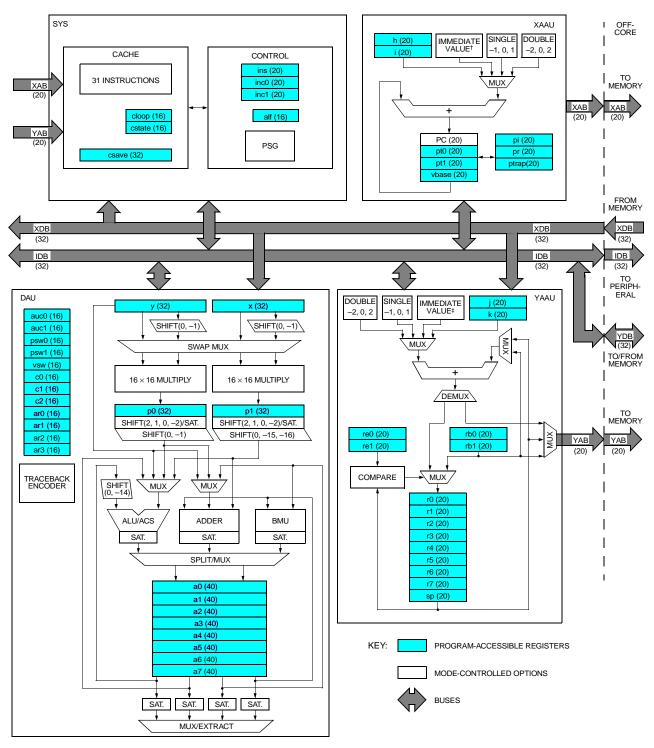

See the *DSP16000 Digital Signal Processor Core* Information Manual for a complete description of the DSP16000 core. Figure 2 on page 16 shows a block diagram of the core that consists of four major blocks: System Control and Cache (SYS), Data Arithmetic Unit (DAU), Y-Memory Space Address Arithmetic Unit (YAAU), and X-Memory Space Address Arithmetic Unit (XAAU). Bits within the **auc0** and **auc1** registers configure the DAU mode-controlled operations.

#### System Control and Cache (SYS)

This section consists of the control block and the cache.

The control block provides overall system coordination that is mostly invisible to the user. The control block includes an instruction decoder and sequencer, a pseudorandom sequence generator (PSG), an interrupt and trap handler, a wait-state generator, and low-power standby mode control logic. An interrupt and trap handler provides a user-locatable vector table and three levels of user-assigned interrupt priority.

SYS contains the **alf** register, which is a 16-bit register that contains AWAIT, a power-saving standby mode bit, and peripheral flags. The **inc0** and **inc1** registers are 20-bit interrupt control registers, and **ins** is a 20-bit interrupt status register.

Programs use the instruction cache to store and execute repetitive operations such as those found in an FIR or IIR filter section. The cache can contain up to 31 16-bit and 32-bit instructions. The code in the cache can repeat up to  $2^{16} - 1$  times without looping overhead. Operations in the cache that require a coefficient access execute at twice the normal rate because the XAAU and its associated bus are not needed for fetching instructions. The cache greatly reduces the need for writing in-line repetitive code and, therefore, reduces instruction/coefficient memory size requirements. In addition, the use of cache reduces power consumption because it eliminates memory accesses for instruction fetches.

The **cloop** register controls the cache loop count. The **cstate** register contains the current state of the cache. The 32-bit **csave** register holds the opcode of the instruction following the loop instruction in X-memory. The cache provides a convenient, low-overhead looping structure that is interruptible, savable, and restorable. The cache is addressable in both the X and

Y memory spaces. An interrupt or trap handling routine can save and restore **cloop**, **cstate**, **csave**, and the contents of the cache.

#### **Data Arithmetic Unit (DAU)**

The DAU is a power-efficient, dual-MAC (multiply/accumulate) parallel-pipelined structure that is tailored to communications applications. It can perform two double-word (32-bit) fetches, two multiplications, and two accumulations in a single instruction cycle. The dual-MAC parallel pipeline begins with two 32-bit registers, x and y. The pipeline treats the 32-bit registers as four 16-bit signed registers if used as input to two signed 16-bit x 16-bit multipliers. Each multiplier produces a full 32-bit result stored into registers **p0** and **p1**. The DAU can direct the output of each multiplier to a 40-bit ALU or a 40-bit 3-input ADDER. The ALU and ADDER results are each stored in one of eight 40-bit accumulators, a0 through a7. The ALU includes an ACS (add/compare/select) function for Viterbi decoding. The DAU can direct the output of each accumulator to the ALU/ACS, the ADDER, or a 40-bit BMU (bit manipulation unit).

The ALU implements addition, subtraction, and various logical operations. To support Viterbi decoding, the ALU has a split mode in which it computes two simultaneous 16-bit additions or subtractions. This mode, available in a specialized dual-MAC instruction, is used to compute the distance between a received symbol and its estimate.

The ACS provides the add/compare/select function required for Viterbi decoding. This unit provides flags to the traceback encoder for implementing mode-controlled side-effects for ACS operations. The source operands for the ACS are any two accumulators, and results are written back to one of the source accumulators.

The BMU implements barrel-shift, bit-field insertion, bit-field extraction, exponent extraction, normalization, and accumulator shuffling operations. **ar0** through **ar3** are auxiliary registers whose main function is to control BMU operations.

The user can enable overflow saturation to affect the multiplier output and the results of the three arithmetic units. Overflow saturation can also affect an accumulator value as it is transferred to memory or other register. These features accommodate various speech coding standards such as GSM-FR, GSM-HR, and GSM-EFR. Shifting in the arithmetic pipeline occurs at several stages to accommodate various standards for mixed-and double-precision multiplications.

# **DSP16000 Core Architectural Overview** (continued)

The DAU contains control and status registers **auc0**, **auc1**, **psw0**, **psw1**, **vsw**, and **c0—c2**.

The arithmetic unit control registers **auc0** and **auc1** select or deselect various modes of DAU operation. These modes include scaling of the products, saturation on overflow, feedback to the **x** and **y** registers from accumulators **a6** and **a7**, simultaneous loading of **x** and **y** registers with the same value (used for single-cycle squaring), and clearing the low half of registers when loading the high half to facilitate fixed-point operations.

The processor status word registers **psw0** and **psw1** contain flags set by ALU/ACS, ADDER, or BMU operations. They also include information on the current status of the interrupt controller.

The vsw register is the Viterbi support word associated with the traceback encoder. The traceback encoder is a specialized block for accelerating Viterbi decoding. It performs mode-controlled side-effects for three MAC instruction group compare functions: cmp0(), cmp1(), and cmp2(). The vsw register controls the modes. The side-effects allow the DAU to store, with no overhead, state information necessary for traceback decoding. Side-effects use the c1 counter, the ar0 and ar1 auxiliary registers, and bits 1 and 0 of vsw.

The **c1** and **c0** counters are 16-bit signed registers used to count events such as the number of times the program has executed a sequence of code. The **c2** register is a holding register for counter **c1**. Conditional instructions control these counters and provide a convenient method of program looping.

# Y-Memory Space Address Arithmetic Unit (YAAU)

The YAAU supports high-speed, register-indirect, data memory addressing and postincrementing of the address register. Eight 20-bit pointer registers (r0—r7) store read or write addresses for the Y-memory space. Two sets of 20-bit registers (rb0 and re0; rb1 and re1) define the upper and lower boundaries of two zero-overhead circular buffers for efficient filter implementations. The j and k registers are two 20-bit signed registers that are used to hold user-defined postincrement values for r0—r7. Fixed increments of +1, -1, 0, +2, and -2 are also available. (Postincrement options 0 and -2 are not available for some specialized transfers. See the DSP16000 Digital Signal Processor Core Information Manual for details.)

The YAAU includes a 20-bit stack pointer (sp). The data move group includes a set of stack instructions that consists of push, pop, stack-relative, and pipelined stack-relative operations. The addressing mode used for the stack-relative instructions is register-plus-displacement indirect addressing (the displacement is optional). The displacement is specified as either an immediate value as part of the instruction or a value stored in j or k. The YAAU computes the address by adding the displacement to sp and leaves the contents of sp unchanged. The data move group also includes instructions with register-plus-displacement indirect addressing for the pointer registers r0—r6 in addition to sp.

The data move group of instructions includes instructions for loading and storing any YAAU register from or to memory or another core register. It also includes instructions for loading any YAAU register with an immediate value stored with the instruction. The pointer arithmetic group of instructions allows adding of an immediate value or the contents of the **j** or **k** register to any YAAU pointer register and storing the result to any YAAU register.

#### X-Memory Space Address Arithmetic Unit (XAAU)

The XAAU contains registers and an adder that control the sequencing of instructions in the processor. The program counter (PC) automatically increments through the instruction space. The interrupt return register **pi**, the subroutine return register **pr**, and the trap return register ptrap are automatically loaded with return addresses that direct the return to main program execution from interrupt service routines, subroutines, and trap service routines, respectively. High-speed, register-indirect, read-only memory addressing with postincrementing is done with the pt0 and pt1 registers. The signed registers h and i are used to hold a user-defined signed postincrement value. Fixed postincrement values of 0, +1, -1, +2, and -2 are also available. (Postincrement options 0 and -2 are available only if the target of the data transfer is an accumulator vector. See the DSP16000 Digital Signal Processor Core Information Manual for details.)

The data move group of instructions includes instructions for loading and storing any XAAU register from or to memory or another core register. It also includes instructions for loading any XAAU register with an immediate value stored with the instruction.

**vbase** is the 20-bit vector base offset register. The user programs this register with the base address of the interrupt and trap vector table.

# **DSP16000 Core Architectural Overview** (continued)

$<sup>\</sup>dagger$  Associated with  $\mbox{\bf PC}\mbox{-relative}$  branch addressing.

Figure 2. DSP16000 Core Block Diagram

<sup>‡</sup> Associated with register-plus-displacement indirect addressing.

# **DSP16000 Core Architectural Overview** (continued)

Table 2. DSP16000 Core Block Diagram Legend

| Symbol           | Name                                                                                                    |  |

|------------------|---------------------------------------------------------------------------------------------------------|--|

| 16 x 16 MULTIPLY | 16-bit x 16-bit Multiplier                                                                              |  |

| a0—a7            | Accumulators 0—7                                                                                        |  |

| ADDER            | 3-input 40-bit Adder/Subtractor                                                                         |  |

| alf              | AWAIT and Flags                                                                                         |  |

| ALU/ACS          | 40-bit Arithmetic Logic Unit and Add/Compare/Select Function—used in Viterbi decoding                   |  |

| ar0—ar3          | Auxiliary Registers 0—3                                                                                 |  |

| auc0, auc1       | Arithmetic Unit Control Registers                                                                       |  |

| BMU              | 40-bit Bit Manipulation Unit                                                                            |  |

| c0, c1           | Counters 0 and 1                                                                                        |  |

| c2               | Counter Holding Register                                                                                |  |

| cloop            | Cache Loop Count                                                                                        |  |

| COMPARE          | Comparator                                                                                              |  |

| csave            | Cache Save Register                                                                                     |  |

| cstate           | Cache State Register                                                                                    |  |

| DAU              | Data Arithmetic Unit                                                                                    |  |

| h                | Pointer Postincrement Register for the X-Memory Space                                                   |  |

| i                | Pointer Postincrement Register for the X-Memory Space                                                   |  |

| IDB              | Internal Data Bus                                                                                       |  |

| inc0, inc1       | Interrupt Control Registers 0 and 1                                                                     |  |

| ins              | Interrupt Status Register                                                                               |  |

| j                | Pointer Postincrement/Offset Register for the Y-Memory Space                                            |  |

| k                | Pointer Postincrement/Offset Register for the Y-Memory Space                                            |  |

| MUX              | Multiplexer                                                                                             |  |

| p0, p1           | Product Registers 0 and 1                                                                               |  |

| PC               | Program Counter                                                                                         |  |

| pi               | Program Interrupt Return Register                                                                       |  |

| pr               | Program Return Register                                                                                 |  |

| PSG              | Pseudorandom Sequence Generator                                                                         |  |

| psw0, psw1       | Processor Status Word Registers 0 and 1                                                                 |  |

| pt0, pt1         | Pointers 0 and 1 to X-Memory Space                                                                      |  |

| ptrap            | Program Trap Return Register                                                                            |  |

| r0—r7            | Pointers 0—7 to Y-Memory Space                                                                          |  |

| rb0, rb1         | Circular Buffer Pointers 0 and 1 (begin address)                                                        |  |

| re0, re1         | Circular Buffer Pointers 0 and 1 (end address)                                                          |  |

| SAT              | Saturation                                                                                              |  |

| SHIFT            | Shifting Operation                                                                                      |  |

| sp               | Stack Pointer                                                                                           |  |

| SPLIT/MUX        | Split/Multiplexer—routes the appropriate ALU/ACS, BMU, and ADDER outputs to the appropriate accumulator |  |

| SWAP MUX         | Swap Multiplexer—routes the appropriate data to the appropriate multiplier input                        |  |

| SYS              | System Control and Cache                                                                                |  |

#### **DSP16000 Core Architectural Overview** (continued)

Table 2. DSP16000 Core Block Diagram Legend (continued)

| Symbol | Name                                                       |  |

|--------|------------------------------------------------------------|--|

| vbase  | Vector Base Offset Register                                |  |

| vsw    | Viterbi Support Word—associated with the traceback encoder |  |

| Х      | Multiplier Input Register                                  |  |

| XAAU   | X-Memory Space Address Arithmetic Unit                     |  |

| XAB    | X-Memory Space Address Bus                                 |  |

| XDB    | X-Memory Space Data Bus                                    |  |

| У      | Multiplier Input Register                                  |  |

| YAAU   | Y-Memory Space Address Arithmetic Unit                     |  |

| YAB    | Y-Memory Space Address Bus                                 |  |

| YDB    | Y-Memory Space Data Bus                                    |  |

# Reset

The DSP16210 has two negative-assertion external reset input pins: RSTB and TRST. RSTB is used to reset the DSP16210. The primary function of TRST is to reset the JTAG controller.

#### **Reset After Powerup or Power Interruption**

At initial powerup or if power is interrupted, a reset is required and both TRST and RSTB must be asserted (low) simultaneously for at least seven CKI cycles (see Reset Circuit on page 142 for details). The TRST pin must be asserted even if the JTAG controller is not used by the application. Failure to properly reset the device on powerup or after a power interruption can lead to a loss of communication with the DSP16210 pins.

#### **RSTB Pin Reset**

Reset initializes the state of user registers, synchronizes the internal clocks, and initiates code execution. The device is properly reset by asserting RSTB (low) for at least seven CKI cycles. After RSTB is deasserted, there is a delay of several CKI cycles before the device begins executing instructions (see Reset Synchronization on page 143 for details). The DSP16210 samples the state of the EXM pin when RSTB is deasserted to determine whether it boots from IROM at location 0x20000 (EXM = 0) or from EROM at location 0x80000 (EXM = 1). See Reset States on page 113 for the values of the user registers after reset.

Table 3 on page 19 defines the states of the output and bidirectional pins both during and after reset. It does not include the TDO output pin, because its state is not affected by RSTB but by the JTAG controller.

Reset (continued)

**RSTB Pin Reset** (continued)

Table 3. State of Device Output and Bidirectional Pins During and After Reset

| Туре           | Pin                                     | State of Pin During Reset<br>(RSTB = 0) |                                            | State of Pin After Reset<br>(RSTB 0→1)     |

|----------------|-----------------------------------------|-----------------------------------------|--------------------------------------------|--------------------------------------------|

| Output         | AB[15:0], EIBF, PIBF,<br>IBF, IACK      | 3-state                                 |                                            | logic low                                  |

|                | EOBE, POBE, OBE                         | 3-s                                     | tate                                       | logic high                                 |

|                | DO                                      | 3-s                                     | tate                                       | 3-state                                    |

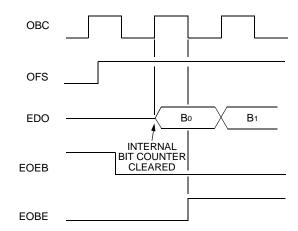

|                | EDO                                     | 3-s                                     | tate                                       | 3-state                                    |

|                | RWN, EROM,<br>ERAMHI, ERAMLO,           | INT0 = 0<br>(deasserted)                | logic high                                 | logic high                                 |

|                | ERAM, IO                                | INT0 = 1<br>(asserted)                  | 3-state                                    |                                            |

|                | СКО                                     | INT0 = 0<br>(deasserted)                | internal clock<br>(CLK = CKI) <sup>†</sup> | internal clock<br>(CLK = CKI) <sup>†</sup> |

|                |                                         | INT0 = 1<br>(asserted)                  | 3-state                                    |                                            |

| Bidirectional  | VEC[3:0]/IOBIT[7:4]                     | 3-state                                 |                                            | logic high <sup>‡</sup>                    |

| (Input/Output) | IOBIT[3:0], TRAP,<br>OLD, OCK, ILD, ICK | 3-state                                 |                                            | configured as input                        |

|                | DB[15:0], PB[15:0]                      | 3-state                                 |                                            | 3-state                                    |

<sup>†</sup> During and after reset, the internal clock is selected as the CKI input pin and the CKO output pin is selected as the internal clock.

#### **JTAG Controller Reset**

The recommended method of resetting the JTAG controller is to assert RSTB and TRST simultaneously. An alternative method is to clock TCK through at least five cycles with TMS held high. Both methods ensure that the user has control of the device pins. JTAG controller reset does not initialize user registers, synchronize

internal clocks, or initiate code execution unless RSTB is also asserted.

Reset of the JTAG controller places it in the test logic reset (TLR) state. While in the TLR state, the DSP16210 3-states all bidirectional pins, clears all boundary-scan cells for unidirectional outputs, and deasserts (high) all external memory interface enable signals (EROM, ERAM, ERAMHI, ERAMLO, and IO). This prevents logic contention.

<sup>‡</sup> The ioc register (Table 54 on page 99) is cleared after reset, including its EBIO field that controls the multiplexing of the VEC0/IOBIT7, VEC1/IOBIT6, VEC2/IOBIT5, and VEC3/IOBIT4 pins. Therefore, after reset, these pins are configured as the VEC[3:0] outputs, which are initialized as logic high during reset.

# **Interrupts and Trap**

The DSP16210 supports the following interrupts and traps:

- 15 hardware interrupts with three levels of user-assigned priority.

- 64 software interrupts (icall IM6 instruction).

- The TRAP input pin. (The TRAP pin is configured as an output only under JTAG control to support HDS multiple-processor debugging.) By default, after reset, the TRAP pin is configured as an input and is connected directly to the core via the PTRAP signal. If the TRAP pin is asserted, the core vectors to a user-supplied trap service routine at location vbase + 0x4.

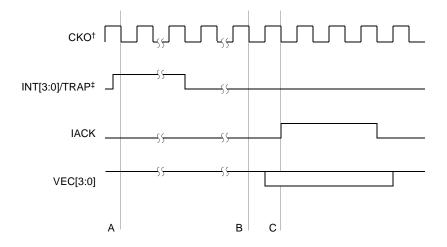

Five pins of the DSP16210 are devoted to signaling interrupt service status. The IACK pin goes high when the core begins to service an interrupt or trap, and goes low three internal clock (CLK) cycles later. Four pins, VEC[3:0], carry a code indicating which of the interrupts or trap is being serviced. Table 4 on page 21 contains the encodings used by each interrupt.

If an interrupt or trap condition arises, a sequence of actions service the interrupt or trap before the DSP16210 resumes regular program execution. The interrupt and trap vectors are in contiguous locations in memory, and the base (starting) address of the 352-word vector table is configurable in the **vbase** register. Table 4 on page 21 describes the vector table. Assigning each interrupt and trap source to a unique location differentiates selection of their service routines. When an interrupt or trap is taken, the core saves the contents of **PC** and vectors execution to the appropriate interrupt service routine (ISR) or trap service routine (TSR).

There are 15 hardware interrupts with three levels of user-assigned priority. Interrupts are globally enabled by executing the **ei** (enable interrupts) instruction and globally disabled by executing the **di** (disable interrupts) instruction. The user assigns priorities and individually disables (masks) interrupts by configuring the **inc0** and **inc1** registers. The **ins** register contains status information for each interrupt. The **psw1** register includes control and status bits associated with the interrupt handler. When an interrupt is taken, the **pi** register holds the interrupt return address.

Software interrupts allow the testing of interrupt routines and their operation when interrupts occur at specific code locations. Programmers and system architects can observe behavior of complex code segments when interrupts occur (e.g., multilevel subroutine nesting, cache loops, etc.).

A trap is similar to an interrupt but has the highest possible priority. Traps cannot be disabled by executing a **di** instruction. Traps do not nest, i.e., a TSR cannot be trapped. The state of the **psw1** register is unaffected by traps. When a trap is taken, the **ptrap** register holds the trap return address.

An interrupt or trap service routine can be either a fourword entry in the vector table or a larger service routine reached via a **goto** instruction in the vector table, in either case. The service routine must end with a **treturn** instruction for traps or an **ireturn** instruction for interrupts. Executing **ireturn** globally enables interrupts (executing **treturn** does not).

#### **Interrupt Registers**

The software interrupt and the traps are always enabled and do not have a corresponding bit in the **ins** register. Other vectored interrupts are enabled in the **inc0** and **inc1** registers (Table 5 on page 22) and monitored in the **ins** register (Table 6 on page 22). One of three priority levels for each hardware interrupt can be configured using two consecutive bits of **inc0** or **inc1**. There are two reasons for assigning priorities to interrupts.

- Nesting interrupts, i.e., an interrupt service routine can be interrupted by an interrupt of higher priority.

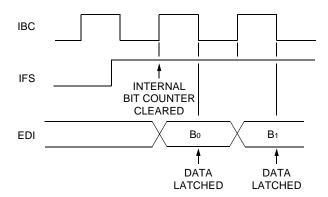

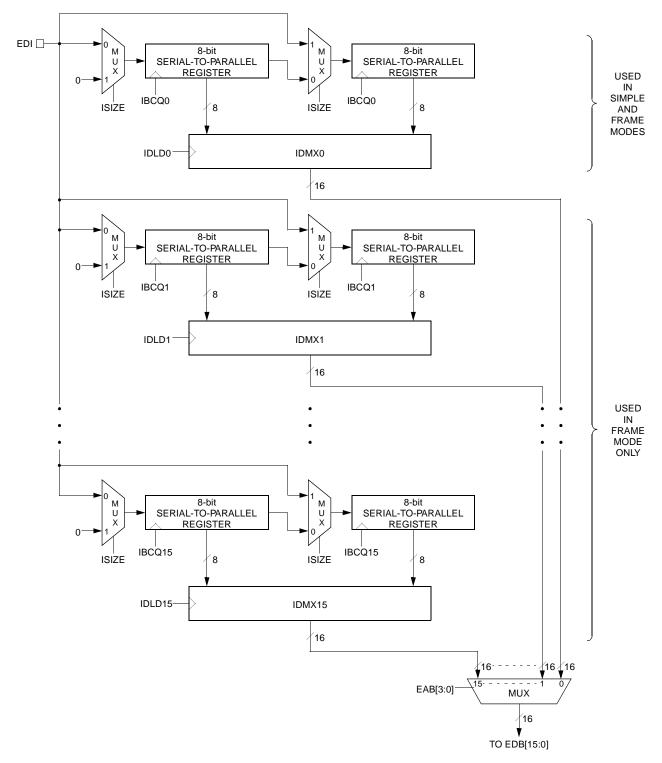

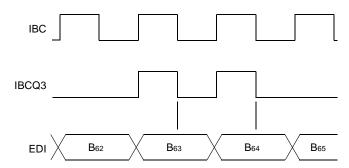

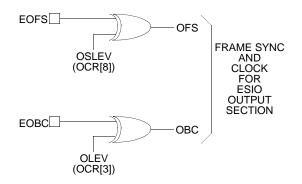

- Servicing concurrent interrupts according to their priority.