# **DISTINCTIVE CHARACTERISTICS**

- SMD/DESC qualified

- Both Binary and BCD counting

- Single +5-V supply

- Three independent 16-bit counters

- DC to 5 MHz

- Programmable counter modes

- Bus-oriented I/O

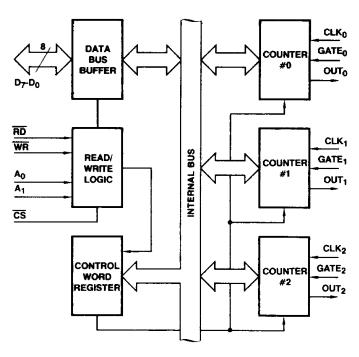

#### **GENERAL DESCRIPTION**

The 8253 is a programmable counter/timer chip designed for use with 8080A/8085A microprocessors. It uses NMOS technology with a single +5-V supply and is a direct replacement for Intel's 8253/8253-5.

Each device is organized as three independent 16-bit counters, each counter having a rate of up to 5 MHz. All modes of operation are software-programmable. For improved performance devices, see the Am9513A System Timing Controller.

#### **BLOCK DIAGRAM**

BD003760

Power { +5 V Supplies { GND

Publication # Rev. Amendment

07935 B /0

Issue Date: November 1987

# CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

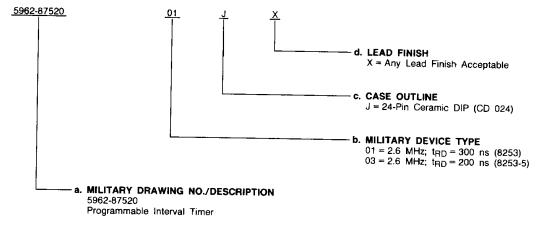

### **MILITARY ORDERING INFORMATION**

# Standard Military Drawing (SMD)/DESC Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. Standard Military Drawing (SMD)/DESC products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for SMD/DESC products is formed by a combination of: a. Military Drawing Part Number

b. Device Type

c. Case Outline

d. Lead Finish

# Valid Combinations 5962-8752001 JX 5962-8752003 JX

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### MILITARY ORDERING INFORMATION (Cont'd.)

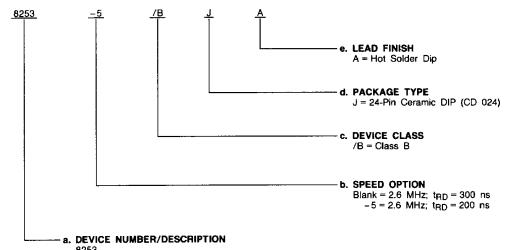

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) for APL products is formed by a combination of: **a. Device Number**

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

# Programmable Interval Timer

| Valid Co | Valid Combinations |  |  |  |  |

|----------|--------------------|--|--|--|--|

| 8253     |                    |  |  |  |  |

| 8253-5   | /BJA               |  |  |  |  |

#### Group A Tests

Group A Tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

# ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65 to +150°C     |

|-------------------------------------|

| Voltage On Any Pin                  |

| with Respect to Ground0.5 to +7.0 V |

| Power Dissipation                   |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

| Military (M) Devices               |   |       |

|------------------------------------|---|-------|

| Temperature (T <sub>C</sub> )55 to | o | 125°C |

| Supply Voltage (V <sub>CC</sub> )5 | / | ±10%  |

Operating ranges define those limits between which the functionality of the device is guaranteed.

**DC CHARACTERISTICS** over operating range (for SMD/DESC and APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter       | Parameter                      |                                                 | 8253-5                                           |                         | 8253 |                         | 1    |

|-----------------|--------------------------------|-------------------------------------------------|--------------------------------------------------|-------------------------|------|-------------------------|------|

| Symbol          | Description                    | Test Conditions                                 | Min.                                             | Max.                    | Min. | Max.                    | Unit |

| V <sub>IL</sub> | Input LOW Voltage              | $V_{CC} = 5 \text{ V } \pm 10\%$                | 5* at                                            | 7                       | 5*   |                         |      |

| V <sub>IH</sub> | Input HIGH Voltage             | V <sub>CC</sub> = 5 V ± 10%                     | 2.                                               | V <sub>CC</sub> + .5 V* |      | .7                      | V    |

| VOL             | Output LOW Voltage             | I <sub>OL</sub> = 1.6 mA.                       |                                                  | VCC T.5 V               | 2.2  | V <sub>CC</sub> + .5 V* | V    |

|                 | Colput LOW Voltage             | V <sub>CC</sub> = 5 V ± 10%                     |                                                  | 0.45                    |      | 0.45                    | V    |

| V <sub>OH</sub> | Output HIGH Voltage            | $I_{OH} = -150 \mu A$ , $V_{CC} = 5 V \pm 10\%$ | 2.1                                              |                         | 2.4  |                         |      |

| hL h            | input Load Current             | $V_{IN} = V_{CC}$ to $V_{CC} = Max$             |                                                  | ±20                     |      | ± 20                    | μA   |

| lofL            | Output Float Leakage           | VOUT = C V,                                     |                                                  | ± 20                    |      | ±20                     |      |

|                 |                                | VC = Wa                                         | <del>                                     </del> |                         |      | -20                     | μΑ   |

| lcc             | V <sub>CC</sub> Supply Current | Out to Olloaded<br>Static (Note 1)              |                                                  | 140                     |      | 140                     | mA   |

CAPACITANCE TC = 25°C; CC GD = 0 V

| Parameter<br>Symbol | Parametric Description | Test Conditions                 | Min. | Тур. | Max. | Unit                                             |

|---------------------|------------------------|---------------------------------|------|------|------|--------------------------------------------------|

| C <sub>IN</sub> †   | Input Capacitance      | f <sub>C</sub> = 1 MHz          |      |      | 10*  | <del>                                     </del> |

| C <sub>I/O</sub> †  | I/O Capacitance        | Unmeasured pins returned to VSS |      |      |      | pF                                               |

| *Guarantand         | by docion, and the t   |                                 |      |      | 20 * | pF                                               |

\*Guaranteed by design; not tested. †Not included in Group A tests.

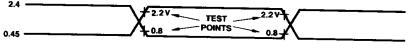

# SWITCHING TEST WAVEFORM

WF006951

Input

SWITCHING CHARACTERISTICS over operating range (for SMD/DESC and APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted) (Note 2)

| Danam star    |                           | 8253                                                    |      | 8253-5 |          |      |      |  |

|---------------|---------------------------|---------------------------------------------------------|------|--------|----------|------|------|--|

| No. Parameter |                           | Parameter Description                                   | Min. | Max.   | Min.     | Max. | Unit |  |

| READ C'       | YCLE                      |                                                         |      |        |          |      |      |  |

| 1             | t <sub>AR</sub>           | Address Stable Before READ                              | 50   |        | 30       |      | ns   |  |

| 2             | tRA                       | Address Hold Time for READ                              | 5    |        | 5        | 1    | ns   |  |

| 3             | t <sub>RR</sub>           | READ Pulse Width                                        | 400  |        | 300      | 1    | ns   |  |

| 4             | t <sub>RD</sub> (Note 3)  | Data Delay from READ                                    |      | 900    | <u> </u> | 200  | ns   |  |

| 5             | tof                       | READ to Data Floating                                   | 25   | 1      | 25       | 100  | ns   |  |

| 6             | t <sub>RV</sub>           | Recovery Time Between READ and Any Other Control Signal |      |        | 1        |      | μs   |  |

| WRITE C       | YCLE                      |                                                         | 1    |        |          |      |      |  |

| 7             | taw                       | Address Stable Before WRITE                             | 50   |        | 30       |      | ns   |  |

| 8             | twa                       | Address Hold Time for WRITE                             | 30   |        | 30       |      | ns   |  |

| 9             | tww                       | WRITE Pulse Width                                       | 400  |        | 300      |      | ns   |  |

| 10            | t <sub>DW</sub>           | Data Setup Time for WRITE                               | 300  |        | 250      |      | ns   |  |

| 11            | twD                       | Data Hold Time for WRITE                                | 40   |        | 30       |      | ns   |  |

| 12            | t <sub>RV</sub>           | Recovery Time Between RITE of Any Other Control Signal  | 1    |        | 1        |      | μs   |  |

| CLOCK A       | AND GATE TIMIN            | G (Note 2)                                              | -    |        | •        | •    |      |  |

| 13            | t <sub>CLK</sub>          | Clock Period                                            | 380  | DC     | 380      | DC   | ns   |  |

| 14            | tpwH                      | HIGH Puise Widne                                        | 230  |        | 230      |      | ns   |  |

| 15            | tpwL                      | LOW DUST Widay                                          | 150  |        | 150      |      | ns   |  |

| 16            | tgw                       | Gant With High                                          | 150  |        | 150      |      | ns   |  |

| 17            | t <sub>GL</sub>           | Catt Wath LOW                                           | 100  |        | 100      |      | ns   |  |

| 18            | tgs                       | ate Betup Time to CLKt                                  | 100  |        | 100      |      | ns   |  |

| 19            | tgн                       | Gate Hold Time After CLK1                               | 55   |        | 55       |      | ns   |  |

| 20            | t <sub>OD</sub> (Note 3)  | Output Delay from CLK1                                  |      | 400    |          | 400  | ns   |  |

| 21            | t <sub>ODG</sub> (Note 3) | Output Delay from Gate                                  | Ī    | 300    |          | 300  | ns   |  |

Notes: 1.  $I_{CC}$  is measured in a static condition with no output loads applied. 2. Test Conditions:  $V_{CC}=5$  V  $\pm 10\%$   $V_{IL}=0.45$  V,  $V_{IH}=2.4$  V  $V_{OL}=0.8$  V,  $V_{OH}=2.2$  V  $I_{OL}=1.6$  mA,  $I_{OH}=150$   $\mu$ A

3. Test Condition:  $C_{L}=100$  pF  $\pm 20$  pF.