# 32M-Bit CMOS Low Voltage Dual Operation Flash Memory

# Preliminary 4M-Byte by 8-Bit (Byte Mode) / 2M-Word by 16-Bit (Word Mode)

### Features

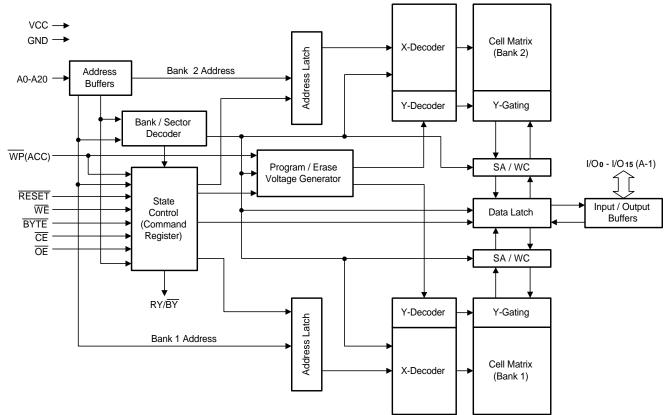

- Two bank organization enabling simultaneous execution of erase / program and read

- Bank organization: 2 banks (8 Mbits + 24 Mbits)

- Memory organization:

- 4,194,304 words x 8 bits (BYTE mode)

- 2,097,152 words x 16 bits (WORD mode)

- Sector organization:

- 71 sectors (8 Kbytes / 4 Kwords × 8 sectors, 64 Kbytes / 32 Kwords × 63 sectors)

- 2 types of sector organization

- T type: Boot sector allocated to the highest address (sector)

- B type: Boot sector allocated to the lowest address (sector)

- 3-state output

- Automatic program

- Program suspend / resume

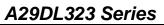

- Unlock bypass program

- Automatic erase

- Chip erase

- Sector erase (sectors can be combined freely)

- Erase suspend / resume

- Program / Erase completion detection

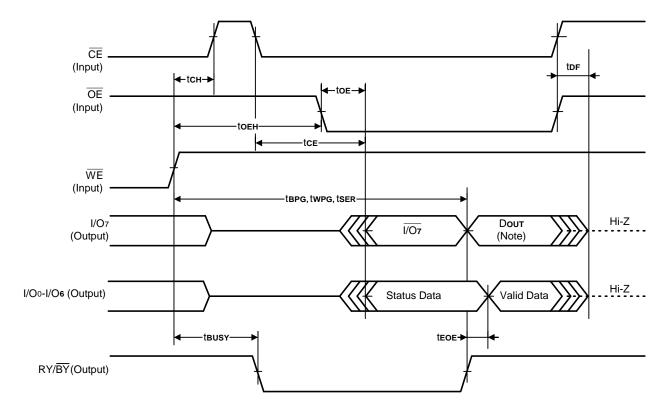

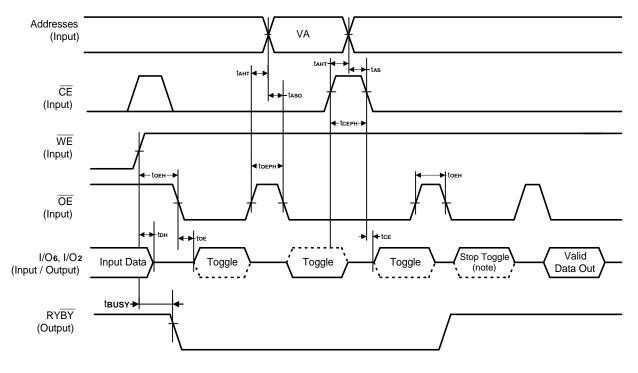

- Detection through data polling and toggle bits

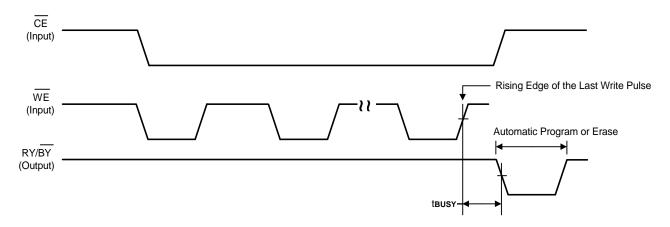

- Detection through  $RY/\overline{BY}$  pin

### **General Description**

The A29DL323 is a flash memory organized of 33,554,432 bits and 71 sectors. Sectors of this memory can be erased at a low voltage (2.7 to 3.6 V) supplied from a single power source, or the contents of the entire chip can be erased. Two modes of memory organization, BYTE mode (4,194,304 words × 8 bits) and WORD mode (2,097,152 words × 16 bits), are selectable so that the memory can be programmed in byte or word units.

The A29DL323 can be read while its contents are being erased or programmed. The memory cell is divided into two banks. While sectors in one bank are being erased or programmed, data can be read from the other bank thanks to the simultaneous execution architecture. The banks are 8 Mbits and 24 Mbits.

This flash memory comes in two types. The T type has a boot sector located at the highest address (sector) and the B type has a boot sector at the lowest address (sector).

- Sector group protection

- Any sector group can be protected

- Any protected sector group can be temporary unprotected

- Sectors can be used for boot application

- Hardware reset and standby using RESET pin

- Automatic sleep mode

- Boot block sector protect by WP (ACC) pin

- Conforms to common flash memory interface (CFI)

- Extra One Time Protect Sector provided

| Part No. | Access<br>time<br>(Max.) | Operating<br>supply<br>voltage | (Activ | ipply current<br>'e mode)<br>/lax.) | cur | ndby<br>rent<br>ax.) |

|----------|--------------------------|--------------------------------|--------|-------------------------------------|-----|----------------------|

| A29DL323 |                          | 2.7V~<br>3.6V                  | 16mA   | 30mA                                | `   | A                    |

- Operating ambient temperature: -40 to 85°C

- Program / erase time

- Program: 9.0 µs / byte (TYP.)

- 11.0 µs / word (TYP.)

- Sector erase: 0.7 s (TYP.)

- Number of program / erase: 1,000,000 times (MIN.)

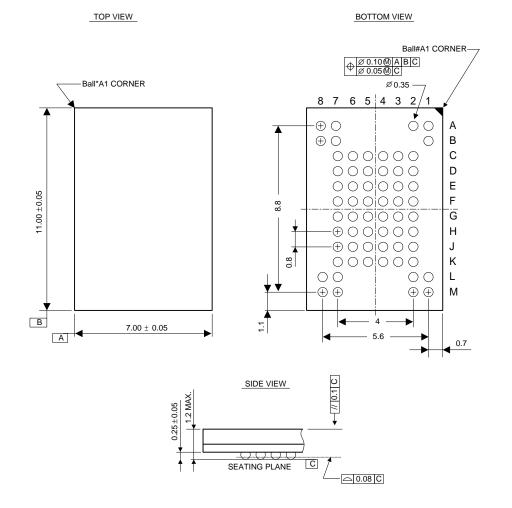

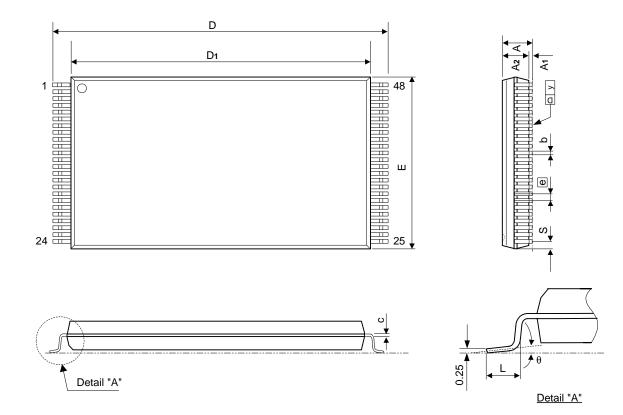

- Package options

- 48-pin TSOP (I) or 63-ball TFBGA

Because the A29DL323 enables the boot sector to be erased, it is ideal for storing a boot program. In addition, program code that controls the flash memory can be also stored, and the program code can be programmed or erased without the need to load it into RAM. Eight small sectors for storing parameters are provided, each of which can be erased in 8 Kbytes units.

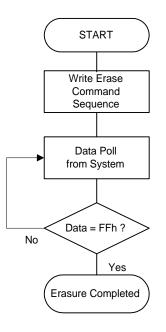

Once a program or erase command sequence has been executed, an automatic program or automatic erase function internally executes program or erase and verification automatically.

Because the A29DL323 can be electrically erased or programmed by writing an instruction, data can be reprogrammed on-board after the flash memory has been installed in a system, making it suitable for a wide range of applications.

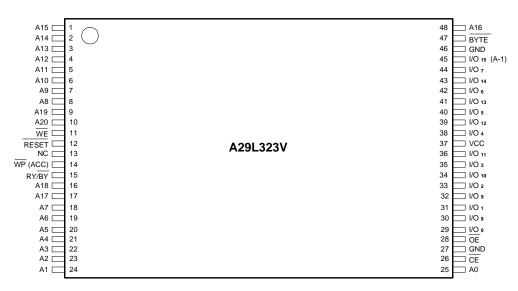

### **Pin Configurations**

TSOP (I)

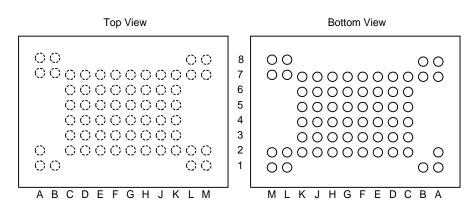

| Το | p Vi | ew |

|----|------|----|

|    |      |    |

|   | А  | В  | С     | D                     | Е   | F   | G    | Н     | J          | К    | L  | Μ  |

|---|----|----|-------|-----------------------|-----|-----|------|-------|------------|------|----|----|

| 1 | NC | NC |       |                       |     |     |      |       |            |      | NC | NC |

| 2 | NC | NC | A13   | A12                   | A14 | A15 | A16  | BYTE  | I/O15(A-1) | GND  | NC | NC |

| 3 |    |    | A9    | A8                    | A10 | A11 | I/O7 | I/O14 | I/O13      | I/O6 |    |    |

| 4 |    |    | WE    | RESET                 | NC  | A19 | I/O5 | I/O12 | VCC        | I/O4 |    |    |

| 5 |    |    | RY/BY | $\overline{WP}$ (ACC) | A18 | A20 | I/O2 | I/O10 | I/O11      | I/O3 |    |    |

| 6 |    |    | A7    | A17                   | A6  | A5  | I/Oo | I/O8  | I/O9       | I/O1 |    |    |

| 7 | NC |    | A3    | A4                    | A2  | A1  | A0   | CE    | OE         | GND  | NC | NC |

| 8 | NC | NC |       |                       |     |     |      |       |            |      | NC | NC |

### **Block Diagram**

### **Pin Descriptions**

| Pin         | No.     | Description                       |  |  |  |  |  |

|-------------|---------|-----------------------------------|--|--|--|--|--|

| A0 -        | - A20   | Address Inputs                    |  |  |  |  |  |

| I/Oo ·      | · I/O14 | Data Inputs/Outputs               |  |  |  |  |  |

|             | I/O15   | Data Input/Output, Word Mode      |  |  |  |  |  |

| I/O15 (A-1) | A-1     | LSB Address Input, Byte Mode      |  |  |  |  |  |

| Ē           | E       | Chip Enable                       |  |  |  |  |  |

| Ŵ           | /E      | Write Enable                      |  |  |  |  |  |

| Ē           | )E      | Output Enable                     |  |  |  |  |  |

| RE          | SET     | Hardware Reset Input              |  |  |  |  |  |

| Β̈́Υ        | ΊΈ      | Mode Select                       |  |  |  |  |  |

| RY,         | /BY     | Ready/BUSY - Output               |  |  |  |  |  |

| WP          | (ACC)   | Write Protect (Accelerated) Input |  |  |  |  |  |

| G           | ND      | Ground                            |  |  |  |  |  |

| V           | 00      | Power Supply                      |  |  |  |  |  |

| NC          | Note    | No Connection                     |  |  |  |  |  |

Note: Some signals can be applied because this pin is not connected to the inside of the chip.

# Input / Output Pin Function

| Pin Name      | Input / Output | Function                                                                                          |

|---------------|----------------|---------------------------------------------------------------------------------------------------|

| A0 to A20     | Input          | Address input pins.                                                                               |

|               |                | A0 to A20 are used differently in the BYTE mode and the WORD mode.                                |

|               |                | BYTE MODE                                                                                         |

|               |                | A0 to A20 are used as the upper 21 bits of total 22 bits of address input pin.                    |

|               |                | (The least significant bit (A-1) is combined to I/O15.)                                           |

|               |                | WORD MODE                                                                                         |

|               |                | A0 to A20 are used as 21 bits address input pin.                                                  |

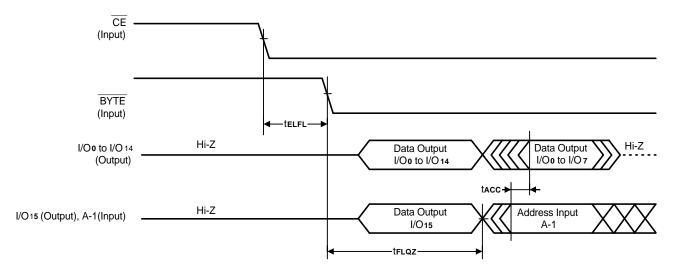

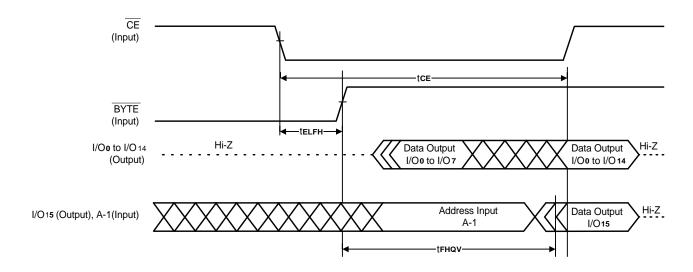

| I/O0 to I/O14 | Input / Output | Data input / output pins.                                                                         |

|               |                | $I/O_0$ to $I/O_{14}$ are used differently in the BYTE mode and the WORD mode.                    |

|               |                | BYTE MODE                                                                                         |

|               |                | $I/O_0$ to $I/O_7$ are used as the 8 bits data input / output pins.                               |

|               |                | I/O <sub>8</sub> to I/O <sub>14</sub> are Hi-Z.                                                   |

|               |                | WORD MODE                                                                                         |

|               |                | $I/O_0$ to $I/O_{14}$ are used as the lower 15 bits of total 16 bits of data input / output pins. |

|               |                | (The most significant bit (I/O15) is combined to A-1.)                                            |

| I/O15, A-1    | Input / Output | I/O15, A1 are used differently in the BYTE mode and the WORD mode.                                |

|               |                | BYTE MODE                                                                                         |

|               |                | The least significant address input pin (A-1)                                                     |

|               |                | WORD MODE                                                                                         |

|               |                | The most significant data input / output pin (I/O15)                                              |

| CE            | Input          | This pin inputs the signal that activates the chip.                                               |

|               |                | When high level, the chip enters the standby mode.                                                |

| OE            | Input          | This pin inputs the read operation control signal.                                                |

|               |                | When high level, output is Hi-Z.                                                                  |

| WE            | Input          | This pin inputs the write operation control signal.                                               |

|               |                | When low level, command input is accepted.                                                        |

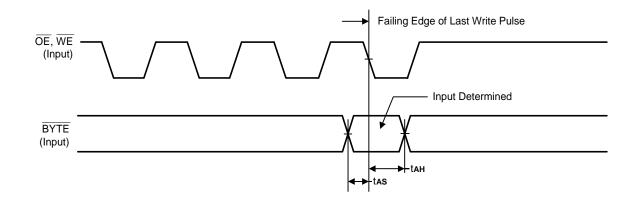

| BYTE          | Input          | The pin for switching BYTE mode and WORD mode.                                                    |

|               |                | High level : WORD MODE (2M words x 16 bits)                                                       |

|               |                | Low level : BYTE MODE (4M words x 8 bits)                                                         |

| RESET         | Input          | This pin inputs hardware reset.                                                                   |

|               |                | When low level, hardware reset is performed.                                                      |

|               |                | If 11.5 to 12.5 V is applied to RESET, the chip enters the temporary sector group                 |

|               |                | unprotect mode.                                                                                   |

| RY/BY         | Output         | This pin indicates whether automatic program / erase is currently being executed. It uses         |

|               |                | open drain connection.                                                                            |

|               |                | Low level indicates the busy state during which the device is performing automatic program erase. |

|               |                | High level indicates the device is in the ready state and will accept the next operation. In      |

|               |                | this case, the device is either in the erase suspend mode or the standby mode.                    |

| WP (ACC)      | Input          | This pin selects the boot block sector protect mode or accelerated mode.                          |

|               |                | Low level: The boot block (2 sectors) is protected.                                               |

|               |                | High level: The boot block is unprotected.                                                        |

|               |                | VACC level: Accelerated mode is selected.                                                         |

| VCC           | -              | Supply Voltage                                                                                    |

| GND           | -              | Ground                                                                                            |

| NC            | -              | No Connection                                                                                     |

|               | -              |                                                                                                   |

All Pins except  $\overline{WP}$  (ACC),  $\overline{RESET}$  ..... .....-0.5V Note1 to VCC + 0.4 (4.0V max.) Note2 Supply Voltage with Respect to GND (VCC)

# Notes:

1. -2.0V (Min.) (Pulse width  $\leq$  20ns)

**Absolute Maximum Ratings\***

2. VCC + 0.5V (Max.) (Pulse width  $\leq$  20ns)

Input / Output Voltage with Respect to GND

# **Bus Operations**

The following table shows the operation modes of the dual operation flash memory. Before turning on power, input

Storage Temperature (Tstg) .....-55°C to + 125°C

Operating Ambient Temperature (TA) .....

.....-40°C to + 85°C

WP (ACC), RESET .....-0.5V Note1 to 13.0V

# A29DL323 Series

#### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to this device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of these specification is not implied or intended. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

### **Recommended Operating Conditions**

| Operating Ambient Temperature (TA)  |

|-------------------------------------|

| -40°C to +85°C                      |

| Supply Voltage (VCC) +2.7V to +3.6V |

GND  $\pm$  0.2 V to the RESET until VCC  $\geq$  VCC (min.).

| Operat               | ion             | CE | ŌĒ | WE | I/O15,<br>A-1 | A6  | A1      | A0   | I/O₀ to<br>I/O7 | I/O8 to<br>I/O15 | RESET | WP<br>(ACC) |

|----------------------|-----------------|----|----|----|---------------|-----|---------|------|-----------------|------------------|-------|-------------|

| Read (Note)          | BYTE mode       | L  | L  | Н  | A-1           | Add | lress i | nput | Data output     | Hi-Z             | Н     | Х           |

|                      | WORD mode       | L  | L  | Н  | Х             | Add | lress i | nput | Data out        | put              | Н     | Х           |

| Write                | BYTE mode       | L  | Н  | L  | A-1           | Add | lress i | nput | Data input      | Hi-Z             | Н     | Note3       |

|                      | WORD mode       | L  | Н  | L  | Х             | Add | lress i | nput | Data inp        | out              | Н     | Note3       |

| Standby              | •               | Н  | Х  | Х  | Х             | Х   | Х       | Х    | Hi-Z            | Hi-Z             | Н     | Х           |

| Hardware reset / Sta | andby           | Х  | Х  | Х  | Х             | Х   | Х       | Х    | Hi-Z            | Hi-Z             | L     | Х           |

| Output Disable       |                 | L  | Н  | Н  | Х             | Х   | Х       | Х    | Hi-Z            | Hi-Z             | Н     | Х           |

| Temporary Sector G   | Group Unprotect | Х  | Х  | Х  | Х             | Х   | Х       | Х    | Hi-Z o          | r                | Vid   | Note3       |

|                      |                 |    |    |    |               |     |         |      | Data input /    | output           |       |             |

| Automatic Sleep      | BYTE mode       | L  | L  | Н  | A-1           | Add | lress i | nput | Data output     | Hi-Z             | Н     | Х           |

| Mode                 | WORD mode       | L  | L  | Н  | Х             | Add | lress i | nput | Data out        | put              | Н     | Х           |

| Boot Block Sector F  | Protect         | Х  | Х  | Х  | Х             | Х   | Х       | Х    | Hi-Z o          | r                | Х     | L           |

|                      |                 |    |    |    |               |     |         |      | Data input /    | output           |       |             |

| Accelerated Mode     | BYTE mode       | L  | Н  | L  | A-1           | Add | lress i | nput | Data input      | Hi-Z             | Н     | VACC        |

|                      | WORD mode       | L  | Н  | L  | Х             | Add | lress i | nput | Data inp        | out              | Н     | VACC        |

Table 1. A29DL323 Bus Operations

Note: When OE = VIL, VIL can be applied to WE. When OE = VIH, a write operation is started.

Remarks: 1. H : VIH, L : VIL, : VIH or VIL, VID : 11.5 V to 12.5 V, VACC : 8.5 V to 9.5 V

If an address is held longer than the minimum read cycle time (trc), the automatic sleep mode is set.

If WP (ACC)=VIL, sector 0,1,140, and 141 remain protected. If WP (ACC)=VIH, protection on sectors 0,1,140, and 141 depends on whether they were last protected or unprotected using the method described in "Sector/Sector Block Protection and Unprotection". If WP (ACC)=VIH, all sectors will be unprotected.

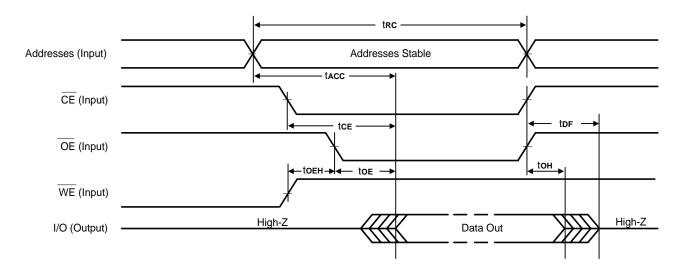

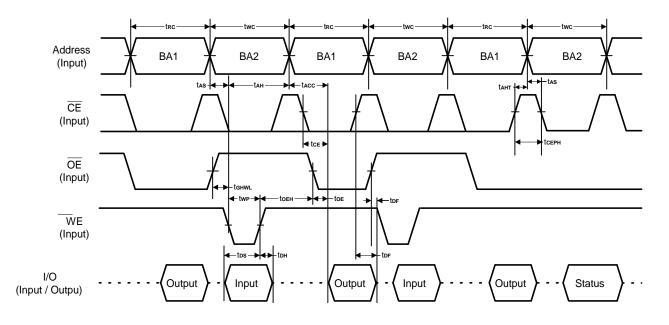

### **Read Operation**

The read operation is controlled by the OE and /OE. The /CE is used to select a device, and the  $\overline{OE}$  controls data output. The following three access times are used depending on the condition.

- Address access time (tacc): Time until valid data is output after an address has been determined (however, after CE).

- $\overline{CE}$  access time (tce): Time until valid data is output after  $\overline{CE}$  has been determined (however, after address).

- OE access time (toe): Time until valid data is output after OE has been determined (however, OE must be input after tacc-toe, tce-toe after address and CE have been determined).

On power-up, the device is automatically set in the read mode. To read the device without changing address immediately after power application, either execute hardware reset or briefly lower  $\overline{CE}$  to VIL from VIH.

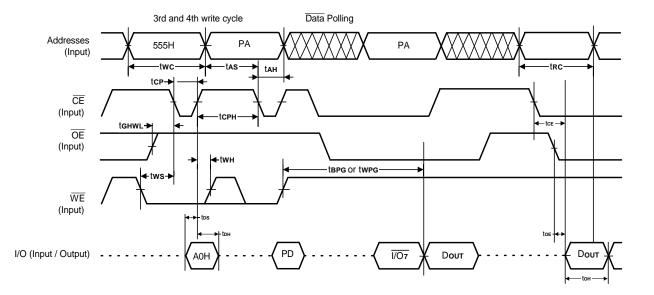

For the timing waveform, refer to Timing Waveform for Read Cycle (1).

### Write Operation

The operation of the device is controlled by writing commands to the registers. The command register is a function that latches the address and data necessary for executing an instruction and does not occupy the memory area.

If an illegal address or data is written or if an address or data is written in the wrong sequence, the device is reset to the read mode.

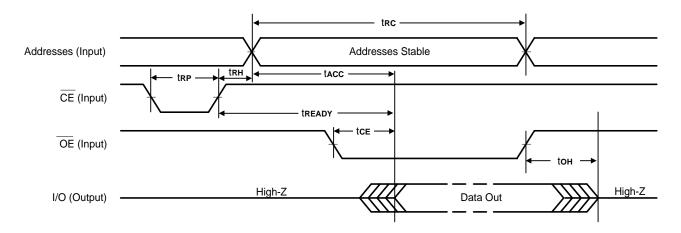

#### Standby Mode

The standby mode is set when VIH is input to the  $\overline{CE}$ . The current consumption in the standby mode can be lowered to 5  $\mu$ A or less in two ways.

One is to use CE and  $\overline{\text{RESET}}$ . Input VCC  $\pm$  0.3 V to CE and  $\overline{\text{RESET}}$ . However, while automatic programming or erasing is being executed, the operating supply current (lcc2) does not decrease to 5µA or lower even if  $\overline{\text{CE}} = \text{VIH}$ . If a read operation is executed in the standby mode, data is output at  $\overline{\text{CE}}$  access time.

The other is to input GND  $\pm$  0.3 V to the RESET. At this time, the level of  $\overrightarrow{CE}$  is VIH or VIL. In this case, tRH is required for the device to return to the read mode from the standby mode.

For the timing waveform, refer to Timing Waveform for Read Cycle (2).

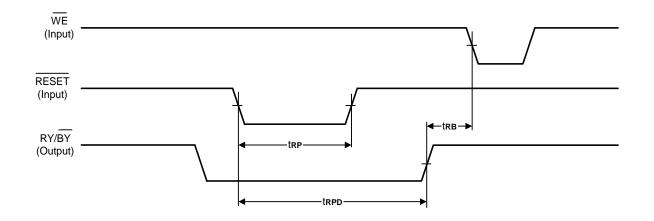

#### **Hardware Reset Pin**

The device is reset to the read mode if V<sub>IL</sub> is input to the RESET for the duration of trep and V<sub>IH</sub> for the duration of trep. While V<sub>IL</sub> is being input to the RESET, all commands are ignored, and the output pins go into a Hi-Z state. If the voltage on RESET is kept to GND  $\pm$  0.2 V at this time, the current consumption can be lowered to 5µA or less. If V<sub>IH</sub> is input to the RESET, tready is required until data is output. For the timing waveform, refer to Timing Waveform for Read Cycle (2).

### **Output Disable Mode**

Output from the device is disabled (Hi-Z state) if V\_{IH} is input to the  $\overline{\text{OE}}$  .

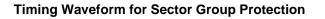

### **Sector Group Protection**

Protect the sector group by using a command.  $\overline{OE}$  or  $\overline{WE}$  control is no need.

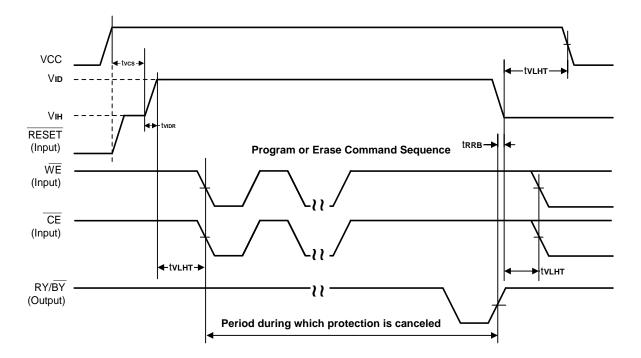

### **Temporary Sector Group Unprotect**

Protection of a sector group can be temporarily canceled. When V<sub>ID</sub> is input to  $\overrightarrow{\text{RESET}}$ , the temporary sector group unprotect mode is set. If a protected sector is selected in this mode, it can be programmed or erased. If the mode is canceled, the sector group is protected again.

For the timing waveform, refer to Timing Waveform for Temporary Sector Group Unprotect.

### **Product ID**

Read the product ID code by using a command.

#### Automatic Sleep Mode

The automatic sleep mode is used to reduce the power consumption substantially during a read operation.

If an address is held longer than the minimum read cycle time ( $t_{RC}$ ), the sleep mode (low power consumption mode) is automatically set. In this mode, the output data is latched and continuously output.

In the automatic sleep mode,  $\overline{CE}$ ,  $\overline{WE}$ , and  $\overline{OE}$  do not have to be controlled. At this time, the current consumption decreases to 5µA or less. During dual operation, however, the current consumption is power supply current (lcc6, lcc7).

If the address is changed, the automatic sleep mode is canceled automatically, the device returns to the read mode, and the data of the newly input address is output.

#### **Boot Block Sector Protect**

The boot block sector protect mode protects the two sectors of the boot block. This mode is set when V<sub>IL</sub> is input to  $\overline{WP}$  (ACC). If V<sub>IL</sub> is input to  $\overline{WP}$  (ACC) even in the temporary sector group unprotect mode, the boot block remains protected and protection of the other sectors is temporarily canceled.

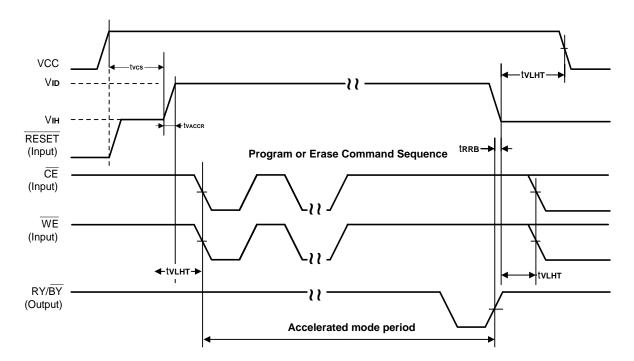

#### **Accelerated Mode**

This mode is used to program the device at high speed, and the programming time can be shortened to about 60%. To program the device in the accelerated mode, input VACC to  $\overline{WP}$  (ACC) and use an unlock bypass program command. Therefore, ordinary commands can be used for programming or detection of completion of programming. If VACC is input to  $\overline{WP}$  (ACC), the device is automatically set in the unlock bypass mode. Therefore, the unlock bypass set command and reset command are not necessary. The accelerated mode is automatically canceled if the input of VACC to  $\overline{WP}$  (ACC) is stopped. In the accelerated mode, protection of the sector group is temporarily canceled. Exercise care in programming the device at this time.

For the timing waveform, refer to Timing Waveform for Accelerated Mode.

#### **Dual Operation**

This device can execute a program or erase operation and a read operation simultaneously. By selecting bank 1 or 2 by changing the bank address, one bank can execute a read operation while the other bank is executing a program or erase operation. When changing the bank address, no wait cycle is necessary. Note that two or more program or erase operation. When changing the bank address, no wait cycle is necessary. Note that two or more operations cannot be executed at the same time in the same bank.

The following table shows the combinations of bank operations.

For the timing waveform, refer to Timing Waveform for Dual Operation.

#### Table 2. Dual Operation

| Case | Operation of Bank 1 | Operation of Bank 2 |

|------|---------------------|---------------------|

| 1    | Read mode           | Read mode           |

| 2    | Read mode           | Product ID          |

| 3    | Read mode           | Program (Note 1)    |

| 4    | Read mode           | Erase (Note 2)      |

| 5    | Product ID          | Read mode           |

| 6    | Program (Note 1)    | Read mode           |

| 7    | Erase (Note 2)      | Read mode           |

Notes 1. The program operation is suspended by the program suspend command, and addresses not being programmed to at this time can only be read.

2. The erase operation is suspended by the erase suspend command. The sector not erased at this time can be read or programmed.

| Bank   | Sector |     |     | Sect  | or Ad  | dress | Table |     |     |     | Sector Size         | Address Range   | (in hexadecimal) |

|--------|--------|-----|-----|-------|--------|-------|-------|-----|-----|-----|---------------------|-----------------|------------------|

|        |        |     | Ban | k Add | ress T | able  |       |     |     |     | (Kbytes/<br>Kwords) | Byte Mode       | Word Mode        |

|        |        | A20 | A19 | A18   | A17    | A16   | A15   | A14 | A13 | A12 | (worus)             | (x 8)           | (x16)            |

| Bank 1 | SA70   | 1   | 1   | 1     | 1      | 1     | 1     | 1   | 1   | 1   | 8/4                 | 3FFFFFH-3FE000H | 1FFFFFH-1FF000H  |

|        | SA69   | 1   | 1   | 1     | 1      | 1     | 1     | 1   | 1   | 0   | 8/4                 | 3FDFFFH-3FC000H | 1FEFFFH-1FE000H  |

|        | SA68   | 1   | 1   | 1     | 1      | 1     | 1     | 1   | 0   | 1   | 8/4                 | 3FBFFFH-3FA000H | 1FDFFFH-1FD000H  |

|        | SA67   | 1   | 1   | 1     | 1      | 1     | 1     | 1   | 0   | 0   | 8/4                 | 3F9FFFH-3F8000H | 1FCFFFH-1FC000H  |

|        | SA66   | 1   | 1   | 1     | 1      | 1     | 1     | 0   | 1   | 1   | 8/4                 | 3F7FFFH-3F6000H | 1FBFFFH-1FB000H  |

|        | SA65   | 1   | 1   | 1     | 1      | 1     | 1     | 0   | 1   | 0   | 8/4                 | 3F5FFFH-3F4000H | 1FAFFFH-1FA000H  |

|        | SA64   | 1   | 1   | 1     | 1      | 1     | 1     | 0   | 0   | 1   | 8/4                 | 3F3FFFH-3F2000H | 1F9FFFH-1F9000H  |

|        | SA63   | 1   | 1   | 1     | 1      | 1     | 1     | 0   | 0   | 0   | 8/4                 | 3F1FFFH-3F0000H | 1F8FFFH-1F8000H  |

|        | SA62   | 1   | 1   | 1     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 3EFFFFH-3E0000H | 1F7FFFH-1F0000H  |

|        | SA61   | 1   | 1   | 1     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 3DFFFFH-3D0000H | 1EFFFFH-1E8000H  |

|        | SA60   | 1   | 1   | 1     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 3CFFFFH-3C0000H | 1E7FFFH-1E0000H  |

|        | SA59   | 1   | 1   | 1     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 3BFFFFH-3B0000H | 1DFFFFH-1D8000H  |

|        | SA58   | 1   | 1   | 1     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 3AFFFFH-3A0000H | 1D7FFFH-1D0000H  |

|        | SA57   | 1   | 1   | 1     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 39FFFFH-390000H | 1CFFFFH-1C8000H  |

|        | SA56   | 1   | 1   | 1     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 38FFFFH-380000H | 1C7FFFH-1C0000H  |

|        | SA55   | 1   | 1   | 0     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 37FFFFH-370000H | 1BFFFFH-1B8000H  |

|        | SA54   | 1   | 1   | 0     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 36FFFFH-360000H | 1B7FFFH-1B0000H  |

|        | SA53   | 1   | 1   | 0     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 35FFFFH-350000H | 1AFFFFH-1A8000H  |

|        | SA52   | 1   | 1   | 0     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 34FFFFH-340000H | 1A7FFFH-1A0000H  |

|        | SA51   | 1   | 1   | 0     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 33FFFFH-330000H | 19FFFFH-198000H  |

|        | SA50   | 1   | 1   | 0     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 32FFFFH-320000H | 197FFFH-190000H  |

|        | SA49   | 1   | 1   | 0     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 31FFFFH-310000H | 18FFFFH-188000H  |

|        | SA48   | 1   | 1   | 0     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 30FFFFH-300000H | 187FFFH-180000H  |

| Bank 2 | SA47   | 1   | 0   | 1     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 2FFFFFH-2F0000H | 17FFFFH-178000H  |

|        | SA46   | 1   | 0   | 1     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 2EFFFFH-2E0000H | 177FFFH-170000H  |

|        | SA45   | 1   | 0   | 1     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 2DFFFFH-2D0000H | 16FFFFH-168000H  |

|        | SA44   | 1   | 0   | 1     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 2CFFFFH-2C0000H | 167FFFH-160000H  |

|        | SA43   | 1   | 0   | 1     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 2BFFFFH-2B0000H | 15FFFFH-158000H  |

|        | SA42   | 1   | 0   | 1     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 2AFFFFH-2A0000H | 157FFFH-150000H  |

|        | SA41   | 1   | 0   | 1     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 29FFFFH-290000H | 14FFFFH-148000H  |

|        | SA40   | 1   | 0   | 1     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 28FFFFH-280000H | 147FFFH-140000H  |

|        | SA39   | 1   | 0   | 0     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 27FFFFH-270000H | 13FFFFH-138000H  |

|        | SA38   | 1   | 0   | 0     | 1      | 1     | 0     | х   | Х   | Х   | 64/32               | 26FFFFH-260000H | 137FFFH-130000H  |

|        | SA37   | 1   | 0   | 0     | 1      | 0     | 1     | х   | Х   | х   | 64/32               | 25FFFFH-250000H | 12FFFFH-128000H  |

|        | SA36   | 1   | 0   | 0     | 1      | 0     | 0     | х   | х   | х   | 64/32               | 24FFFFH-240000H | 127FFFH-120000H  |

|        | SA35   | 1   | 0   | 0     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 23FFFFH-230000H | 11FFFFH-118000H  |

# Table 3. A29DL323 Top Boot Block Sector Address Table

# A29DL323 Series

| Bank   | Sector |     |     | Sect  | or Ad  | dress | Table | •   |     |     | Sector Size         | Address Range   | (in hexadecimal) |

|--------|--------|-----|-----|-------|--------|-------|-------|-----|-----|-----|---------------------|-----------------|------------------|

|        |        |     | Ban | k Add | ress T | able  |       |     |     |     | (Kbytes/<br>Kwords) | Byte Mode       | Word Mode        |

|        |        | A20 | A19 | A18   | A17    | A16   | A15   | A14 | A13 | A12 | (words)             | (x 8)           | (x16)            |

| Bank 2 | SA34   | 1   | 0   | 0     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 22FFFFH-220000H | 117FFFH-110000H  |

|        | SA33   | 1   | 0   | 0     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 21FFFFH-210000H | 10FFFFH-108000H  |

|        | SA32   | 1   | 0   | 0     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 20FFFFH-200000H | 107FFFH-100000H  |

|        | SA31   | 0   | 1   | 1     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 1FFFFFH-1F0000H | 0FFFFFH-0F8000H  |

|        | SA30   | 0   | 1   | 1     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 1EFFFFH-1E0000H | 0F7FFFH-0F0000H  |

|        | SA29   | 0   | 1   | 1     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 1DFFFFH-1D0000H | 0EFFFFH-0E8000H  |

|        | SA28   | 0   | 1   | 1     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 1CFFFFH-1C0000H | 0E7FFFH-0E0000H  |

|        | SA27   | 0   | 1   | 1     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 1BFFFFH-1B0000H | 0DFFFFH-0D8000H  |

|        | SA26   | 0   | 1   | 1     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 1AFFFFH-1A0000H | 0D7FFFH-0D0000H  |

|        | SA25   | 0   | 1   | 1     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 19FFFFH-190000H | 0CFFFFH-0C8000H  |

|        | SA24   | 0   | 1   | 1     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 18FFFFH-180000H | 0C7FFFH-0C0000H  |

|        | SA23   | 0   | 1   | 0     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 17FFFFH-170000H | 0BFFFFH-0B8000H  |

|        | SA22   | 0   | 1   | 0     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 16FFFFH-160000H | 0B7FFFH-0B0000H  |

|        | SA21   | 0   | 1   | 0     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 15FFFFH-150000H | 0AFFFFH-0A8000H  |

|        | SA20   | 0   | 1   | 0     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 14FFFFH-140000H | 0A7FFFH-0A0000H  |

|        | SA19   | 0   | 1   | 0     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 13FFFFH-130000H | 09FFFFH-098000H  |

|        | SA18   | 0   | 1   | 0     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 12FFFFH-120000H | 097FFFH-090000H  |

|        | SA17   | 0   | 1   | 0     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 11FFFFH-110000H | 08FFFFH-088000H  |

|        | SA16   | 0   | 0   | 1     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 10FFFFH-100000H | 087FFFH-080000H  |

|        | SA15   | 0   | 0   | 1     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 0FFFFFH-0F0000H | 07FFFFH-078000H  |

|        | SA14   | 0   | 0   | 1     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 0EFFFFH-0E0000H | 077FFFH-070000H  |

|        | SA13   | 0   | 0   | 1     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 0DFFFFH-0D0000H | 06FFFFH-068000H  |

|        | SA12   | 0   | 0   | 1     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 0CFFFFH-0C0000H | 067FFFH-060000H  |

|        | SA11   | 0   | 0   | 1     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 0BFFFFH-0B0000H | 05FFFFH-058000H  |

|        | SA10   | 0   | 0   | 1     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 0AFFFFH-0A0000H | 057FFFH-050000H  |

|        | SA9    | 0   | 0   | 1     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 09FFFFH-090000H | 04FFFFH-048000H  |

|        | SA8    | 0   | 0   | 1     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 08FFFFH-080000H | 047FFFH-040000H  |

|        | SA7    | 0   | 0   | 0     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 07FFFFH-070000H | 03FFFFH-038000H  |

|        | SA6    | 0   | 0   | 0     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 06FFFFH-060000H | 037FFFH-030000H  |

|        | SA5    | 0   | 0   | 0     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 05FFFFH-050000H | 02FFFFH-028000H  |

|        | SA4    | 0   | 0   | 0     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 04FFFFH-040000H | 027FFFH-020000H  |

|        | SA3    | 0   | 0   | 0     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 03FFFFH-030000H | 01FFFFH-018000H  |

|        | SA2    | 0   | 0   | 0     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 02FFFFH-020000H | 017FFFH-010000H  |

|        | SA1    | 0   | 0   | 0     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 01FFFFH-010000H | 00FFFFH-008000H  |

|        | SA0    | 0   | 0   | 0     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 00FFFFH-000000H | 007FFFH-000000H  |

# Table 3. A29DL323 Top Boot Block Sector Address Table (continued)

# A29DL323 Series

| Bank   | Sector |     |     | Sect  | or Ad  | dress | Table |     |     |     | Sector Size         | Address Range   | (in hexadecimal) |

|--------|--------|-----|-----|-------|--------|-------|-------|-----|-----|-----|---------------------|-----------------|------------------|

|        |        |     | Ban | k Add | ress T | able  |       |     |     |     | (Kbytes/<br>Kwords) | Byte Mode       | Word Mode        |

|        |        | A20 | A19 | A18   | A17    | A16   | A15   | A14 | A13 | A12 | rworus)             | (x 8)           | (x16)            |

| Bank 2 | SA70   | 1   | 1   | 1     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 3FFFFFH-3F0000H | 1FFFFFH-1F8000H  |

|        | SA69   | 1   | 1   | 1     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 3EFFFFH-3E0000H | 1F7FFFH-1F0000H  |

|        | SA68   | 1   | 1   | 1     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 3DFFFFH-3D0000H | 1EFFFFH-1E8000H  |

|        | SA67   | 1   | 1   | 1     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 3CFFFFH-3C0000H | 1E7FFFH-1E0000H  |

|        | SA66   | 1   | 1   | 1     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 3BFFFFH-3B0000H | 1DFFFFH-1D8000H  |

|        | SA65   | 1   | 1   | 1     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 3AFFFFH-3A0000H | 1D7FFFH-1D0000H  |

|        | SA64   | 1   | 1   | 1     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 39FFFFH-390000H | 1CFFFFH-1C8000H  |

|        | SA63   | 1   | 1   | 1     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 38FFFFH-380000H | 1C7FFFH-1C0000H  |

|        | SA62   | 1   | 1   | 0     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 37FFFFH-370000H | 1BFFFFH-1B8000H  |

|        | SA61   | 1   | 1   | 0     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 36FFFFH-360000H | 1B7FFFH-1B0000H  |

|        | SA60   | 1   | 1   | 0     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 35FFFFH-350000H | 1AFFFFH-1A8000H  |

|        | SA59   | 1   | 1   | 0     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 34FFFFH-340000H | 1A7FFFH-1A0000H  |

|        | SA58   | 1   | 1   | 0     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 33FFFFH-330000H | 19FFFFH-198000H  |

|        | SA57   | 1   | 1   | 0     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 32FFFFH-320000H | 197FFFH-190000H  |

|        | SA56   | 1   | 1   | 0     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 31FFFFH-310000H | 18FFFFH-188000H  |

|        | SA55   | 1   | 1   | 0     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 30FFFFH-300000H | 187FFFH-180000H  |

|        | SA54   | 1   | 0   | 1     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 2FFFFFH-2F0000H | 17FFFFH-178000H  |

|        | SA53   | 1   | 0   | 1     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 2EFFFFH-2E0000H | 177FFFH-170000H  |

|        | SA52   | 1   | 0   | 1     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 2DFFFFH-2D0000H | 16FFFFH-168000H  |

|        | SA51   | 1   | 0   | 1     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 2CFFFFH-2C0000H | 167FFFH-160000H  |

|        | SA50   | 1   | 0   | 1     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 2BFFFFH-2B0000H | 15FFFFH-158000H  |

|        | SA49   | 1   | 0   | 1     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 2AFFFFH-2A0000H | 157FFFH-150000H  |

|        | SA48   | 1   | 0   | 1     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 29FFFFH-290000H | 14FFFFH-148000H  |

|        | SA47   | 1   | 0   | 1     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 28FFFFH-280000H | 147FFFH-140000H  |

|        | SA46   | 1   | 0   | 0     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 27FFFFH-270000H | 13FFFFH-138000H  |

|        | SA45   | 1   | 0   | 0     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 26FFFFH-260000H | 137FFFH-130000H  |

|        | SA44   | 1   | 0   | 0     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 25FFFFH-250000H | 12FFFFH-128000H  |

|        | SA43   | 1   | 0   | 0     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 24FFFFH-240000H | 127FFFH-120000H  |

|        | SA42   | 1   | 0   | 0     | 0      | 1     | 1     | Х   | Х   | Х   | 64/32               | 23FFFFH-230000H | 11FFFFH-118000H  |

|        | SA41   | 1   | 0   | 0     | 0      | 1     | 0     | Х   | Х   | Х   | 64/32               | 22FFFFH-220000H | 117FFFH-110000H  |

|        | SA40   | 1   | 0   | 0     | 0      | 0     | 1     | Х   | Х   | Х   | 64/32               | 21FFFFH-210000H | 10FFFFH-108000H  |

|        | SA39   | 1   | 0   | 0     | 0      | 0     | 0     | Х   | Х   | Х   | 64/32               | 20FFFFH-200000H | 107FFFH-100000H  |

|        | SA38   | 0   | 1   | 1     | 1      | 1     | 1     | Х   | Х   | Х   | 64/32               | 1FFFFFH-1F0000H | 0FFFFFH-0F8000H  |

|        | SA37   | 0   | 1   | 1     | 1      | 1     | 0     | Х   | Х   | Х   | 64/32               | 1EFFFFH-1E0000H | 0F7FFFH-0F0000H  |

|        | SA36   | 0   | 1   | 1     | 1      | 0     | 1     | Х   | Х   | Х   | 64/32               | 1DFFFFH-1D0000H | 0EFFFFH-0E8000H  |

|        | SA35   | 0   | 1   | 1     | 1      | 0     | 0     | Х   | Х   | Х   | 64/32               | 1CFFFFH-1C0000H | 0E7FFFH-0E0000H  |

### Table 4. A29DL323 Bottom Boot Block Sector Address Table

# A29DL323 Series

| Bank   | Sector |     |     | Sect  | or Ad  | dress | Table |     |     | Sector Size | Address Range       | (in hexadecimal) |                  |

|--------|--------|-----|-----|-------|--------|-------|-------|-----|-----|-------------|---------------------|------------------|------------------|

|        |        |     | Ban | k Add | ress T | able  |       |     |     |             | (Kbytes/<br>Kwords) | Byte Mode        | Word Mode        |

|        |        | A20 | A19 | A18   | A17    | A16   | A15   | A14 | A13 | A12         |                     | (x 8)            | (x16)            |

| Bank 2 | SA34   | 0   | 1   | 1     | 0      | 1     | 1     | Х   | Х   | Х           | 64/32               | 1BFFFFH-1B0000H  | 0DFFFFH- 0D8000H |

|        | SA33   | 0   | 1   | 1     | 0      | 1     | 0     | Х   | Х   | Х           | 64/32               | 1AFFFFH-1A0000H  | 0D7FFFH- 0D0000H |

|        | SA32   | 0   | 1   | 1     | 0      | 0     | 1     | Х   | Х   | Х           | 64/32               | 19FFFFH-190000H  | 0CFFFFH-0C8000H  |

|        | SA31   | 0   | 1   | 1     | 0      | 0     | 0     | Х   | Х   | Х           | 64/32               | 18FFFFH-180000H  | 0C7FFFH-0C0000H  |

|        | SA30   | 0   | 1   | 0     | 1      | 1     | 1     | Х   | Х   | Х           | 64/32               | 17FFFFH-170000H  | 0BFFFFH-0B8000H  |

|        | SA29   | 0   | 1   | 0     | 1      | 1     | 0     | Х   | Х   | Х           | 64/32               | 16FFFFH-160000H  | 0B7FFFH-0B0000H  |

|        | SA28   | 0   | 1   | 0     | 1      | 0     | 1     | Х   | Х   | Х           | 64/32               | 15FFFFH-150000H  | 0AFFFFH-0A8000H  |

|        | SA27   | 0   | 1   | 0     | 1      | 0     | 0     | Х   | Х   | Х           | 64/32               | 14FFFFH-140000H  | 0AFFFFH-0A0000H  |

|        | SA26   | 0   | 1   | 0     | 0      | 1     | 1     | Х   | Х   | Х           | 64/32               | 13FFFFH-130000H  | 09FFFFH-098000H  |

|        | SA25   | 0   | 1   | 0     | 0      | 1     | 0     | Х   | Х   | Х           | 64/32               | 12FFFFH- 120000H | 097FFFH- 090000H |

|        | SA24   | 0   | 1   | 0     | 0      | 0     | 1     | Х   | Х   | Х           | 64/32               | 11FFFFH-110000H  | 08FFFFH-088000H  |

|        | SA23   | 0   | 1   | 0     | 0      | 0     | 0     | Х   | Х   | Х           | 64/32               | 10FFFFH-100000H  | 087FFFH-080000H  |

|        | SA22   | 0   | 0   | 1     | 1      | 1     | 1     | Х   | Х   | Х           | 64/32               | 0FFFFFH-0F0000H  | 07FFFFH-078000H  |

|        | SA21   | 0   | 0   | 1     | 1      | 1     | 0     | Х   | Х   | Х           | 64/32               | 0EFFFFH-0E0000H  | 077FFFH-070000H  |

|        | SA20   | 0   | 0   | 1     | 1      | 0     | 1     | Х   | Х   | Х           | 64/32               | 0DFFFFH-0D0000H  | 06FFFFH-068000H  |

|        | SA19   | 0   | 0   | 1     | 1      | 0     | 0     | Х   | Х   | Х           | 64/32               | 0CFFFFH-0C0000H  | 067FFFH-060000H  |

|        | SA18   | 0   | 0   | 1     | 0      | 1     | 1     | Х   | Х   | Х           | 64/32               | 0BFFFFH-0B0000H  | 05FFFFH-058000H  |

|        | SA17   | 0   | 0   | 1     | 0      | 1     | 0     | Х   | Х   | Х           | 64/32               | 0AFFFFH-0A0000H  | 057FFFH-050000H  |

|        | SA16   | 0   | 0   | 1     | 0      | 0     | 1     | Х   | Х   | Х           | 64/32               | 09FFFFH-090000H  | 04FFFFH-048000H  |

|        | SA15   | 0   | 0   | 1     | 0      | 0     | 0     | Х   | Х   | Х           | 64/32               | 08FFFFH-080000H  | 047FFFH-040000H  |

|        | SA14   | 0   | 0   | 0     | 1      | 1     | 1     | Х   | Х   | Х           | 64/32               | 07FFFFH-070000H  | 03FFFFH-038000H  |

|        | SA13   | 0   | 0   | 0     | 1      | 1     | 0     | Х   | Х   | Х           | 64/32               | 06FFFFH-060000H  | 037FFFH-030000H  |

|        | SA12   | 0   | 0   | 0     | 1      | 0     | 1     | Х   | Х   | Х           | 64/32               | 05FFFFH-050000H  | 02FFFFH-028000H  |

|        | SA11   | 0   | 0   | 0     | 1      | 0     | 0     | Х   | Х   | Х           | 64/32               | 04FFFFH-040000H  | 027FFFH-020000H  |

|        | SA10   | 0   | 0   | 0     | 0      | 1     | 1     | Х   | Х   | Х           | 64/32               | 03FFFFH-030000H  | 01FFFFH-018000H  |

|        | SA9    | 0   | 0   | 0     | 0      | 1     | 0     | Х   | Х   | Х           | 64/32               | 02FFFFH-020000H  | 017FFFH-010000H  |

|        | SA8    | 0   | 0   | 0     | 0      | 0     | 1     | Х   | Х   | Х           | 64/32               | 01FFFFH-010000H  | 00FFFFH-008000H  |

|        | SA7    | 0   | 0   | 0     | 0      | 0     | 0     | 1   | 1   | 1           | 64/32               | 00FFFFH-00E000H  | 007FFFH-007000H  |

|        | SA6    | 0   | 0   | 0     | 0      | 1     | 1     | 1   | 1   | 0           | 64/32               | 00DFFFH-00C000H  | 006FFFH-006000H  |

|        | SA5    | 0   | 0   | 0     | 0      | 0     | 0     | 1   | 0   | 1           | 64/32               | 00BFFFH-00A000H  | 005FFFH-005000H  |

|        | SA4    | 0   | 0   | 0     | 0      | 0     | 0     | 1   | 0   | 0           | 64/32               | 009FFFH-008000H  | 004FFFH-004000H  |

|        | SA3    | 0   | 0   | 0     | 0      | 0     | 0     | 0   | 1   | 1           | 64/32               | 007FFFH-006000H  | 003FFFH-003000H  |

|        | SA2    | 0   | 0   | 0     | 0      | 0     | 0     | 0   | 1   | 0           | 64/32               | 005FFFH-004000H  | 002FFFH-002000H  |

|        | SA1    | 0   | 0   | 0     | 0      | 0     | 0     | 0   | 0   | 1           | 64/32               | 003FFFH-002000H  | 001FFF-001000H   |

|        | SA0    | 0   | 0   | 0     | 0      | 0     | 0     | 0   | 0   | 0           | 64/32               | 001FFFH-000000H  | 000FFFH-000000H  |

# Table 4. A29DL323 Bottom Boot Block Sector Address Table (continued)

| Sector Group | A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 | Size               | Sector      |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------------|-------------|

| SGA0         | 0   | 0   | 0   | 0   | 0   | 0   | Х   | Х   | Х   | 64 KB (1 Sector)   | FSA0        |

| SGA1         | 0   | 0   | 0   | 0   | 0   | 1   | Х   | Х   | Х   | 192 KB (3 Sectors) | FSA1–FSA3   |

|              |     |     |     |     | 1   | 0   |     |     |     |                    |             |

|              |     |     |     |     | 1   | 1   |     |     |     |                    |             |

| SGA2         | 0   | 0   | 0   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA4–FSA7   |

| SGA3         | 0   | 0   | 0   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA8–FSA11  |

| SGA4         | 0   | 0   | 1   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA12–FSA15 |

| SGA5         | 0   | 1   | 0   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA16–FSA19 |

| SGA6         | 0   | 1   | 0   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA20–FSA23 |

| SGA7         | 0   | 1   | 1   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA24–FSA27 |

| SGA8         | 0   | 1   | 1   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA28–FSA31 |

| SGA9         | 0   | 1   | 1   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA32–FSA35 |

| SGA10        | 1   | 0   | 0   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA36–FSA39 |

| SGA11        | 1   | 0   | 1   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA40–FSA43 |

| SGA12        | 1   | 0   | 1   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA44–FSA47 |

| SGA13        | 1   | 1   | 0   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA48–FSA51 |

| SGA14        | 1   | 1   | 0   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA52–FSA55 |

| SGA15        | 1   | 1   | 1   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA56–FSA59 |

| SGA16        | 1   | 1   | 1   | 1   | 0   | 0   | Х   | Х   | Х   | 192 KB (3 Sectors) | FSA60–FSA62 |

|              |     |     |     |     | 0   | 1   |     |     |     |                    |             |

|              |     |     |     |     | 1   | 0   |     |     |     |                    |             |

| SGA17        | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 8 KB (1 Sector)    | FSA63       |

| SGA18        | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 1   | 8 KB (1 Sector)    | FSA64       |

| SGA19        | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 1   | 0   | 8 KB (1 Sector)    | FSA65       |

| SGA20        | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 1   | 1   | 8 KB (1 Sector)    | FSA66       |

| SGA21        | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 8 KB (1 Sector)    | FSA67       |

| SGA22        | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 1   | 8 KB (1 Sector)    | FSA68       |

| SGA23        | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 8 KB (1 Sector)    | FSA69       |

| SGA24        | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 8 KB (1 Sector)    | FSA70       |

# Table 5. A29DL323 Top Boot Sector Group Address Table

Remark X: VIH or VIL

| Sector Group | A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 | Size               | Sector      |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------------|-------------|

| SGA0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 8 KB (1 Sector)    | FSA0        |

| SGA1         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 8 KB (1 Sector)    | FSA1        |

| SGA2         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 8 KB (1 Sector)    | FSA2        |

| SGA3         | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 8 KB (1 Sector)    | FSA3        |

| SGA4         | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 8 KB (1 Sector)    | FSA4        |

| SGA5         | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 8 KB (1 Sector)    | FSA5        |

| SGA6         | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 8 KB (1 Sector)    | FSA6        |

| SGA7         | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 8 KB (1 Sector)    | FSA7        |

| SGA8         | 0   | 0   | 0   | 0   | 0   | 1   | Х   | Х   | Х   | 192 KB (3 Sectors) | FSA8–FSA10  |

|              |     |     |     |     | 1   | 0   |     |     |     |                    |             |

|              |     |     |     |     | 1   | 1   |     |     |     |                    |             |

| SGA9         | 0   | 0   | 0   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA11–FSA14 |

| SGA10        | 0   | 0   | 1   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA15–FSA18 |

| SGA11        | 0   | 0   | 1   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA19–FSA22 |

| SGA12        | 0   | 1   | 0   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA23–FSA26 |

| SGA13        | 0   | 1   | 0   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA27–FSA30 |

| SGA14        | 0   | 1   | 1   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA31–FSA34 |

| SGA15        | 0   | 1   | 1   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA35–FSA38 |

| SGA16        | 1   | 0   | 0   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA39–FSA42 |

| SGA17        | 1   | 0   | 0   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA43-FSA46 |

| SGA18        | 1   | 0   | 1   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA47-FSA50 |

| SGA19        | 1   | 0   | 1   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA51-FSA54 |

| SGA20        | 1   | 1   | 0   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA55-FSA58 |

| SGA21        | 1   | 1   | 0   | 1   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA59–FSA62 |

| SGA22        | 1   | 1   | 1   | 0   | Х   | Х   | Х   | Х   | Х   | 256 KB (4 Sectors) | FSA63-FSA66 |

| SGA23        | 1   | 1   | 1   | 1   | 0   | 0   | Х   | Х   | Х   | 192 KB (3 Sector)  | FSA67–FSA69 |

|              |     |     |     |     | 0   | 1   |     |     |     |                    |             |

|              |     |     |     |     | 1   | 0   |     |     |     |                    |             |

| SGA24        | 1   | 1   | 1   | 1   | 1   | 1   | Х   | Х   | Х   | 64 KB (1 Sector)   | FSA70       |

# Table 6. A29DL323 Bottom Boot Sector Group Address Table

Remark X: VIH or VIL

| Produc            | t ID Co      | de             |                            | Inp | out |     |                        |               |               |               |               |               |               |      | 0    | utput        |      |      |      |      |              |              |      |           |

|-------------------|--------------|----------------|----------------------------|-----|-----|-----|------------------------|---------------|---------------|---------------|---------------|---------------|---------------|------|------|--------------|------|------|------|------|--------------|--------------|------|-----------|

|                   |              |                | A12<br>to                  | A6  | A1  | A0  | A-1<br><sub>Note</sub> | <b>I/O</b> 15 | <b>I/O</b> 14 | <b>I/O</b> 13 | <b>I/O</b> 12 | <b>I/O</b> 11 | <b>I/O</b> 10 | I/O9 | I/O8 | <b>I/O</b> 7 | I/O6 | I/O₅ | I/O₄ | I/O₃ | <b>I/O</b> 2 | <b>I/O</b> 1 | I/O0 | HEX       |

|                   |              |                | A20                        |     |     |     | 1                      |               |               |               |               |               |               |      |      |              |      |      |      |      |              |              |      |           |

| Manufa            | cturer       | Code           | Х                          | Vil | Vil | Vil | VIL                    | 0             | 0             | 0             | 0             | 0             | 0             | 0    | 0    | 0            | 0    | 0    | 1    | 0    | 0            | 0            | 0    | 10H       |

| Device<br>Code    | BYTE<br>mode | Top<br>Boot    | х                          | Vi∟ | Vı∟ | Vı∟ | Vi∟                    | Hi-Z          | Hi-Z          | Hi-Z          | Hi-Z          | Hi-Z          | Hi-Z          | Hi-Z | Hi-Z | 0            | 1    | 0    | 1    | 0    | 0            | 0            | 0    | 50H       |

|                   |              | Bottom<br>Boot |                            |     |     |     |                        | Hi-Z          | Hi-Z          | Hi-Z          | Hi-Z          | Hi-Z          | Hi-Z          | Hi-Z | Hi-Z | 0            | 1    | 0    | 1    | 0    | 0            | 1            | 1    | 53H       |

|                   | WOR<br>D     | Top<br>Boot    | Х                          | Vi∟ | Vı∟ | Vін | Х                      | 0             | 0             | 1             | 0             | 0             | 0             | 1    | 0    | 0            | 1    | 0    | 1    | 0    | 0            | 0            | 0    | 2250H     |

|                   | mode         | Bottom<br>Boot |                            |     |     |     |                        | 0             | 0             | 1             | 0             | 0             | 0             | 1    | 0    | 0            | 1    | 0    | 1    | 0    | 0            | 1            | 1    | 2253H     |

| Sector<br>Protect | •            |                | Sector<br>Group<br>Address |     | Vін | Vil | Vil                    | 0             | 0             | 0             | 0             | 0             | 0             | 0    | 0    | 0            | 0    | 0    | 0    | 0    | 0            | 0            | 1    | 01H Note2 |

Table 7. A29DL323 Product ID Code (Manufacture Code / Device Code)

Notes: 1. A-1 is valid only in the BYTE mode. I/O<sub>8</sub> to I/O<sub>14</sub> go into a high-impedance state in the BYTE mode, and I/O<sub>15</sub> is A-1 of the lowest address.

2. If 01H is output, the sector group is protected. If 00H is output, the sector group is unprotected.

Remark X: VIH or VIL

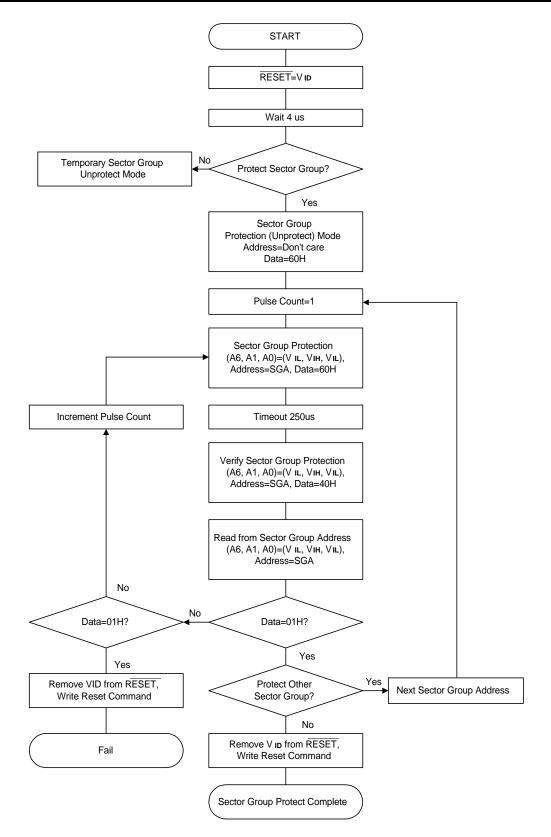

### **Sector Group Protection**

This command performs sector group protection.

By applying Vib to RESET and writing 60H to any address, the device enters the sector group protection mode.

Sector group protection is started by inputting the sector group address of the sector group to be protected to A12 to A20, inputting (A6, A1, A0) = (VIL, VIH, VIL), and writing 60H. After a timeout of 250 $\mu$ s, sector group protection is completed.

Next, with the sector group address input to A12 to A20, the device enters the sector group protection verify mode by inputting (A6, A1, A0) = (VIL, VIH, VIL), and writing 40H. When read is performed in this state, the sector group protection verify result is output to I/O0. If "1" is output to I/O0, the verified sector group is protected. If "1" was not output to I/O0, sector group protection failed, so perform sector group protection again.

For the timing waveform and flow chart, refer to Timing Waveform for Sector Group Protection and Figure 1.

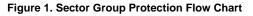

#### Sector Group Unprotect

This command performs sector group unprotect.

Sector group unprotect is performed for all sector group. Unprotect cannot be performed for specific sector group. Moreover, all sector groups must be protected priors to unprotect.

The device enters the sector group unprotect mode by applying VID to  $\overrightarrow{\text{RESET}}$  and writing 60H to any address.

If unprotected sector group exist, first perform sector group protection for these sector groups. To protect a sector group, input the sector group address of the sector group to be protected to the sector group address input pin, input (A6, A1, A0) = (VIL, VIH, VIL), and write 60H (refer to Sector Group Protection).

Sector group unprotect is started by inputting (A6, A1, A0) =  $(V_{IH}, V_{IH}, V_{IL})$ , and writing 60H to any address.

Following a timeout of 15 ms, sector group unprotect is completed.

Unprotect verification must be performed for each sector group.

The device enters the sector group unprotect verification mode by inputting the sector group address to input pin of sector group address and writing 40H, with input (A6, A1, A0) = (VIH, VIH, VIL).

If reading is performed in this state, the sector group unprotect verification result is output to  $I/O_0$ . If the verified sector group is unprotected, "0" is output to  $I/O_0$ . If "0" is not output to  $I/O_0$ , this means that unprotect failed, so perform sector group unprotect again.

For the flow chart, refer to Figure 2. Sector Group Unprotect Flow Chart.

#### Query

The dual operation flash memory conforms to CFI (Common Flash memory Interface). CFI enables information about a device such as the device specifications, memory density, and supply voltage to be read. Therefore, the software of the host system can support the software algorithm of a specific vendor used by a device by using the CFI. For details, refer to the CFI specifications.

By writing the Query command (98H) and giving an address, the device information corresponding to that address can be read. If the device information is read in the WORD mode (16 bits), the upper bytes of data ( $I/O_{15}$  to  $I/O_8$ ) are "0".

To end the Query mode, writes the read / reset command.

### **Extra One Time Protect Sector Entry**

The dual operation flash memory has a sector area that has One Time Protect function. This area does not allow code that has been written to the area to be changed. This area can be programmed or erased until it is protected.

Once it has been protected, however, protection can never be canceled. Therefore, care must be exercised when using this area.

The Extra One Time Protect Sector area has a density of 64 Kbytes and exits at the same addresses as the 8 Kbytes sector. These addresses are 3F0000H to 3FFFFFH for top boot in the BYTE mode (1F8000H to 1FFFFFH in the WORD mode), and 000000H to 00FFFFH for bottom boot in the BYTE mode (000000H to 007FFFH in the WORD mode). Because boot block areas (8 Kbytes x 8 sectors) usually appear in the areas of these addresses, the Extra One Time Protect Sector entry command sequence must be written to enter them as the Extra One Time Protect Sector area. The status in which the Extra One Time Protect Sector area appears is the Extra One Time Protect Sector mode.

In the Extra One Time Protect Sector mode, the other sectors, except the boot block area, can be read. In addition, the Extra One Time Protect Sector area can be read, programmed, or erased in this mode. To exit from the Extra One Time Protect Sector mode, the Extra One Time Protect Sector Reset command sequence must be written.

#### Extra One Time Protect Sector Program

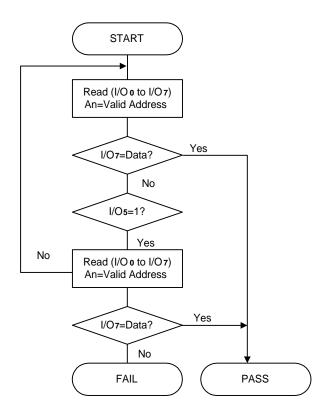

To program data to the Extra One Time Protect Sector area, write the Extra One Time Protect Sector Program command sequence in the Extra One Time Protect Sector mode. This command is no different from the conventional program command except that it must be written in the Extra One Time Protect Sector mode. Therefore, completion of execution of this command is detected in the same manner as the conventional detection method of using I/O<sub>7</sub> data polling, I/O<sub>6</sub> toggle bit, and RY/BY. Care must be exercised in selecting a program destination address. If a program destination address other than the one in the Extra One Time Protect Sector area is selected, the data of that address is changed.

#### Extra One Time Protect Sector Erase

To erase the Extra One Time Protect Sector area, write the Extra One Time Protect Sector erase command sequence in the Extra One Time Protect Sector mode. This command is the same as the conventional sector erase command except that it must be written in the Extra One Time Protect Sector mode. Therefore, completion of execution of this command is detected in the same manner as the conventional detection method of using  $I/O_7$  data polling,  $I/O_6$  toggle bit, and RY/  $\overrightarrow{BY}$ . Care must be exercised in selecting a sector address to erase. If a sector address other than the one in the Extra One Time Protect Sector area is selected, the data of that sector is changed.

#### **Extra One Time Protect Sector Protection**

The following write operations are used to protect the Extra One Time Protect area during the Extra One Time Protect Sector mode.

Write the sector group protection setup command (60H) in the Extra One Time Protect Sector mode.

. Set (A6, A1, A0) = (V\_{IL}, V\_{IH}, V\_{IL}), and set the sector address that selects the Extra One Time Protect Sector.

. Write the sector group protection command (60H).

Because the sequence is the same as the conventional command sequence to protect a sector group except that the Extra One Time Protect Sector mode must be set and that VID is not input to the RESET, the same command

sequence can be used.

For details of how to protect a sector group, refer to Sector Group Protection.

If an address other than the one of the Extra One Time Protect Sector area is specified as a sector address, the other sectors are affected. Once the sector has been protected, protection can never be canceled. Exercise utmost care when protecting a sector.

#### Hardware Data Protection

This device requires two unlock cycles for program / erase command sequence to prevent illegal program / erase. Moreover, a hardware data protect function is provided as follows.

#### Low VCC Write Inhibit

To prevent an illegal write cycle during VCC transition, the command register and program / erase circuit is disabled and all write cycles are ignored while VCC is  $V_{LKO}$  or lower. Write commands are ignored until VCC becomes equal to or greater than  $V_{LKO}$ .

#### Logical Inhibit

The write cycle is inhibited under any of the following conditions :  $\overline{OE} = V_{IL}$ ,  $\overline{CE} = V_{IH}$ , or  $\overline{WE} = V_{IH}$ . To start a write cycle,  $\overline{CE} = V_{IL}$  and  $\overline{WE} = V_{IL}$  must be set while /OE = V\_{IH}.

#### **Power-Up Write Inhibit**

Even if  $\overline{WE} = \overline{CE} = V_{IL}$  and  $\overline{OE} = V_{IH}$  are satisfied at power-up, no commands are accepted at the rising edge of  $\overline{WE}$ . The device is automatically reset to the read mode at power ON.

#### Write Pulse "Glitch" Protection

Because  $\overline{\text{OE}}$ ,  $\overline{\text{CE}}$ , and /WE reject a noise pulse of 5 ns (typical) or less as an invalid pulse, a write operation is not started.

#### **Sector Group Protection**

The dual operation flash memory can be protected by the user in sector group units. For details, refer to Sector Group Protection.

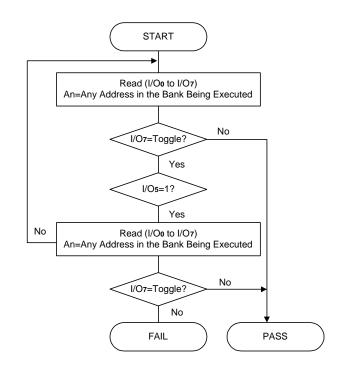

Figure 2. Sector Group Unprotect Flow Chart

## **CFI Code List**

| Address A6 to A0 | Data I/O15 to I/O0 | Description                                                             |

|------------------|--------------------|-------------------------------------------------------------------------|

| 10H              | 0051H              | "QRY" (ASCII code)                                                      |

| 11H              | 0052H              |                                                                         |

| 12H              | 0059H              |                                                                         |

| 13H              | 0002H              | Main command set                                                        |

| 14H              | 0000H              | 2 : AMD/FJ standard type                                                |

| 15H              | 0040H              | Start address of PRIMARY table                                          |

| 16H              | 0000H              |                                                                         |

| 17H              | 0000H              | Auxiliary command set                                                   |

| 18H              | 0000H              | 00H : Not supported                                                     |

| 19H              | 0000H              | Start address of auxiliary algorithm table                              |

| 1AH              | 0000H              |                                                                         |

| 1BH              | 0027H              | Minimum VCC voltage (program / erase)                                   |

|                  |                    | I/O7 to I/O4 : 1 V/bit                                                  |

|                  |                    | I/O3 to I/O0 : 100 mV/bit                                               |

| 1CH              | 0036H              | Maximum VCC voltage (program / erase)                                   |

|                  |                    | I/O7 to I/O4 : 1 V/bit                                                  |

|                  |                    | I/O3 to I/O0 : 100 mV/bit                                               |

| 1DH              | 0000H              | Minimum VPP voltage                                                     |

| 1EH              | 0000H              | Maximum VPP voltage                                                     |

| 1FH              | 0004H              | Typical word program time (2 <sup>N</sup> µs)                           |

| 20H              | 0000H              | Typical buffer program time (2 <sup>N</sup> μs)                         |

| 21H              | 000AH              | Typical sector erase time (2 <sup>N</sup> ms)                           |

| 22H              | 0000H              | Typical chip erase time (2 <sup>N</sup> ms)                             |

| 23H              | 0005H              | Maximum word program time (typical time $\times 2^{N}$ )                |

| 24H              | 0000H              | Maximum buffer program time (typical time $\times 2^{N}$ )              |

| 25H              | 0004H              | Maximum sector erasing time (typical time $\times 2^{N}$ )              |

| 26H              | 0000H              | Maximum chip erasing time (typical time $\times 2^{N}$ )                |

| 27H              | 0016H              | Capacity (2 <sup>N</sup> Bytes)                                         |

| 28H              | 0002H              | I/O information                                                         |

| 29H              | 0000H              | 2 : x8/x16-bit organization                                             |

| 2AH              | 0000H              | Maximum number of bytes when two banks are programmed (2 <sup>N</sup> ) |

| 2BH              | 0000H              | , , , , , , , , , , , , , , , , , , , ,                                 |

| 2CH              | 0002H              | Type of erase block                                                     |

| 2DH              | 0007H              | Information about erase block 1                                         |

| 2EH              | 0000H              | Bit0 to $15: y =$ number of sectors                                     |

| 2FH              | 0020H              | Bit16 to 31 : z = size                                                  |

| 30H              | 0000H              | (Z × 256 Bytes)                                                         |

| 31H              | 003EH              | Information about erase block 2                                         |

| 32H              | 0000H              | bit0 to 15 : y = number of sectors                                      |

| 33H              | 0000H              | bit16 to 31 : $z = size$                                                |

| 34H              | 0001H              | (z × 256 Bytes)                                                         |

| 40H              | 0050H              | "PRI" (ASCII code)                                                      |

| 41H              | 0052H              |                                                                         |

| 42H              | 0049H              |                                                                         |

# **CFI Code List (continued)**

| Address A6 to A0 | Data I/O15 to I/O0 | Description                                       |

|------------------|--------------------|---------------------------------------------------|

| 43H              | 0031H              | Main version (ASCII code)                         |

| 44H              | 0032H              | Minor version (ASCII code)                        |

| 45H              | 0000H              | Address during command input                      |

|                  |                    | 00H : Necessary                                   |

|                  |                    | 01H : Unnecessary                                 |

| 46H              | 0002H              | Temporary erase suspend function                  |

|                  |                    | 00H : Not supported                               |

|                  |                    | 01H : Read only                                   |

|                  |                    | 02H : Read / Program                              |

| 47H              | 0001H              | Sector group protection                           |

|                  |                    | 00H : Not supported                               |

|                  |                    | 01H : Supported                                   |

| 48H              | 0001H              | Temporary sector group protection                 |

|                  |                    | 00H : Not supported                               |

|                  |                    | 01H : Supported                                   |

| 49H              | 0004H              | Sector group protection algorithm                 |

| 4AH              | 00XXH              | Number of sectors of bank 2                       |

|                  |                    | 00H : Not supported                               |

|                  |                    | 30H : A29DL323UX                                  |

| 4BH              | 0000H              | Burst mode                                        |

|                  |                    | 00H : Not supported                               |

| 4CH              | 0000H              | Page mode                                         |

|                  |                    | 00H : Not supported                               |

| 4DH              | 0085H              | Minimum Vacc voltage                              |

|                  |                    | I/O7 to I/O4 : 1 V/bit                            |

|                  |                    | I/O <sub>3</sub> to I/O <sub>0</sub> : 100 mV/bit |

| 4EH              | 0095H              | Maximum VACC voltage                              |

|                  |                    | I/O7 to I/O4 : 1 V/bit                            |

|                  |                    | I/O <sub>3</sub> to I/O <sub>0</sub> : 100 mV/bit |

| 4FH              | 00XXH              | Boot organization                                 |

|                  |                    | 02H : Bottom boot (A29DL323UX-XX)                 |

|                  |                    | 03H : Top boot (A29DL323TX-XX)                    |

| 50H              | 0001H              | Temporary program suspend function                |

|                  |                    | 00H : Not supported                               |

|                  |                    | 01H : Supported                                   |

### **Command Definitions**

#### Writing Commands

All operations are executed by writing a command.

To write a command, the write cycle of a standard microprocessor is used.

The operation of the device is controlled by writing a command to a register. The command register is a function that latches the address and data necessary for executing an instruction and does not occupy the memory area.

If an illegal address or data is written or if an address or data is written in the wrong sequence, the device is reset to the read mode.

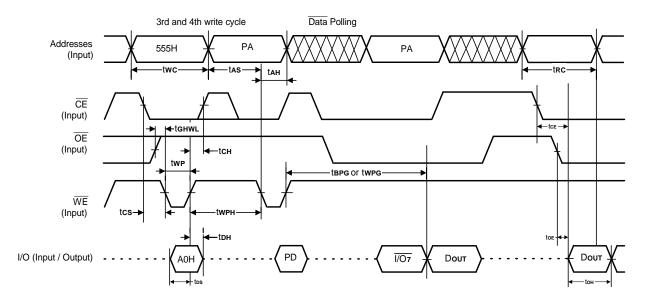

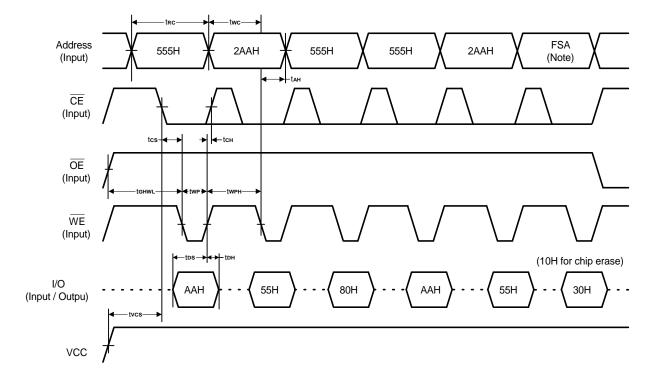

Table 8. shows the commands and command sequences.

#### Read / Reset Command

This command resets the device to the read mode.

The read mode is maintained until the contents of the command register are changed.

Once the device is in the read mode, no command is necessary for reading data. Data read can be performed using the read cycle of a standard microprocessor.

The read mode is maintained until the contents of the command register are changed.

#### Product ID