## 1.0 Features

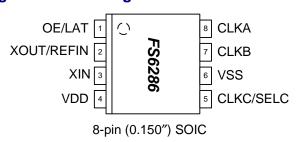

- Dual phase-locked loop (PLL) device with three output clock frequencies

- 3.3V supply voltage

- Small circuit board footprint (8-pin 0.150" SOIC)

- OE/LAT pin enables/disables CLKC output (see Table 1)

- SELC is latched on rising edge of OE/LAT input

- Custom frequency selections available contact your local AMI Sales Representative for more information

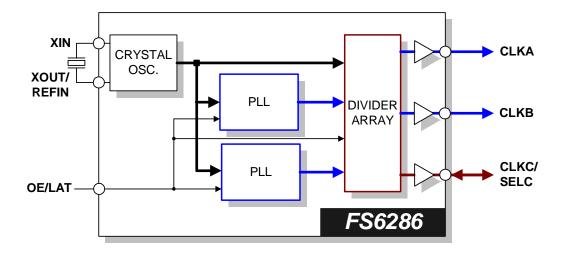

## **Figure 1: Pin Configuration**

## video/addio systems.

**Description**

2.0

The FS6286 is a monolithic CMOS clock generator IC designed to minimize cost and component count in digital video/audio systems.

All frequencies are ratiometrically derived from the crystal oscillator frequency. The locking of all the output frequencies together can eliminate unpredictable artifacts in video systems and reduce electromagnetic interference (EMI) due to frequency harmonic stacking.

**Table 1: Crystal / Output Frequencies**

| DEVICE    | f <sub>XIN</sub><br>(MHz) | CLKA **<br>(MHz)                         | CLKB **<br>(MHz)                         | CLKC<br>(MHz) |                                         |

|-----------|---------------------------|------------------------------------------|------------------------------------------|---------------|-----------------------------------------|

| FS6286-01 | 14.31818                  | 25.0000<br>(f <sub>XIN</sub> * 110 / 63) | 25.0000<br>(f <sub>XIN</sub> * 110 / 63) | SELC=0        | 40.000<br>(f <sub>XIN</sub> * 176 / 63) |

|           |                           |                                          |                                          | SELC=1        | 80.000<br>(f <sub>XIN</sub> *352 / 63 ) |

$<sup>^{\</sup>star\star}$  - CLKA and CLKB are always enabled (not affected by Oe/Lat Input Level)

NOTE: Contact AMI for custom PLL frequencies, OE, and LAT options

Figure 2: Block Diagram