# 2526 AND 2536

## **USB DUAL POWER CONTROL SWITCHES**

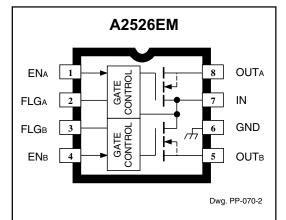

Note that the A2526EM (DIP) and the A2526EL (SOIC) are electrically identical and share a common terminal number assignment.

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>IN</sub> 6.0 V                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Voltage, V <sub>OUT</sub> 6.0 V                                                                                                                                                                                                                                                                                                                                                               |

| Output Current,                                                                                                                                                                                                                                                                                                                                                                                      |

| I <sub>OUT</sub> Internally Limited                                                                                                                                                                                                                                                                                                                                                                  |

| ENABLE Voltage Range,                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>EN</sub> 0.3 V to 10 V                                                                                                                                                                                                                                                                                                                                                                        |

| Fault Flag Voltage, V <sub>FLG</sub> 8.0 V                                                                                                                                                                                                                                                                                                                                                           |

| Fault Flag Current, I <sub>FLG</sub> 50 mA                                                                                                                                                                                                                                                                                                                                                           |

| Package Power Dissipation,                                                                                                                                                                                                                                                                                                                                                                           |

| rackage rower Dissipation,                                                                                                                                                                                                                                                                                                                                                                           |

| P <sub>D</sub>                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                      |

| P <sub>D</sub> See Graph                                                                                                                                                                                                                                                                                                                                                                             |

| P <sub>D</sub>                                                                                                                                                                                                                                                                                                                                                                                       |

| $P_D$ See Graph<br>Operating Temperature Range,<br>$T_A$ 40°C to +85°C                                                                                                                                                                                                                                                                                                                               |

| $\begin{array}{c} P_D & & & \\ \text{Operating Temperature Range,} \\ T_A & & & -40^\circ\text{C to } +85^\circ\text{C} \\ \text{Junction Temperature, } T_J & & & & +150^\circ\text{C*} \end{array}$                                                                                                                                                                                                |

| $\begin{array}{c} P_{D} & & \\ \hline \end{array} & \\ Operating Temperature Range, \\ T_{A} & \\ \hline \end{array} & \begin{array}{c} -40^{\circ}C \ to \ +85^{\circ}C \\ \hline \\ Junction Temperature, \ T_{J} & \\ \hline \end{array} & \begin{array}{c} +150^{\circ}C^{*} \\ \hline \\ Storage Temperature Range, \end{array}$                                                                |

| $\begin{array}{c} P_{D} & & & \\ \text{Operating Temperature Range,} & \\ T_{A} & & & -40^{\circ}\text{C to } +85^{\circ}\text{C} \\ \text{Junction Temperature, } T_{J} & & & +150^{\circ}\text{C*} \\ \text{Storage Temperature Range,} & \\ T_{S} & & & -65^{\circ}\text{C to } 150^{\circ}\text{C} \\ \end{array}$                                                                               |

| $\begin{array}{c} P_{D} & \dots & \text{See Graph} \\ \text{Operating Temperature Range,} \\ T_{A} & \dots & -40^{\circ}\text{C to } +85^{\circ}\text{C} \\ \text{Junction Temperature, } T_{J} & \dots & +150^{\circ}\text{C*} \\ \text{Storage Temperature Range,} \\ T_{S} & \dots & -65^{\circ}\text{C to } 150^{\circ}\text{C} \\ \text{* Fault conditions that produce excessive} \end{array}$ |

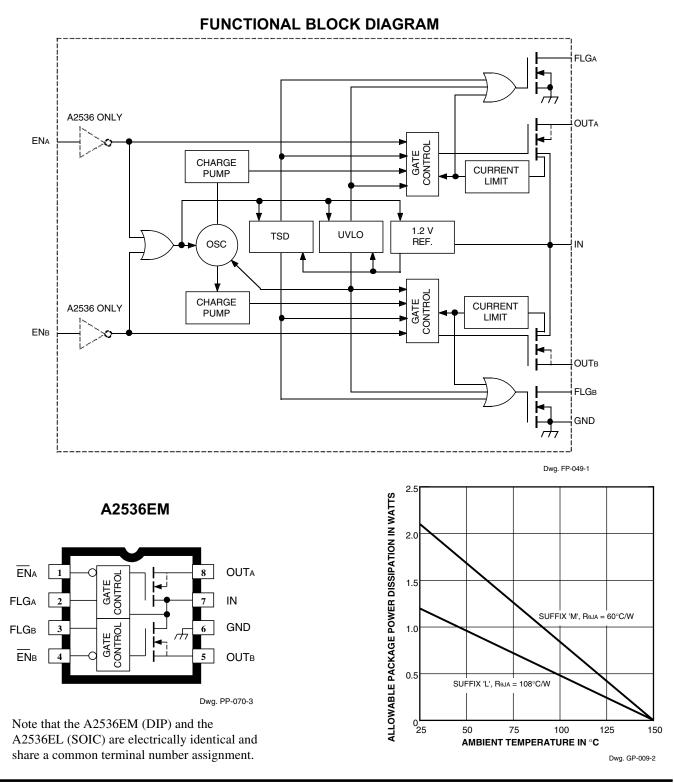

The A2526EL/M and A2536EL/M are integrated high-side dual power switches, optimized for self-powered and bus-powered Universal Serial Bus (USB) applications. Few external components are necessary to satisfy USB requirements. The A2526EL/EM ENABLE inputs are active high; the A2536EL/EM are active low.

All devices are ideally suited for USB applications. Each switch channel supplies up to 500 mA as required by USB peripheral devices. In addition, the switch's low on-resistance permits achieving the USB voltage-drop requirements. Fault current is limited to typically 750 mA, satisfying the UL 25 VA safety requirements, and a flag output is available to indicate a fault condition to the local USB controller. Momentary voltage drops that may occur on the upstream port when the switch is enabled in bus-powered applications is eliminated by a "soft start" feature.

Additional features include thermal shutdown to prevent catastrophic switch failure from high-current loads, undervoltage lockout to ensure that the device remains OFF unless there is a valid input voltage present, and 3.3 V and 5 V logic-compatible enable inputs.

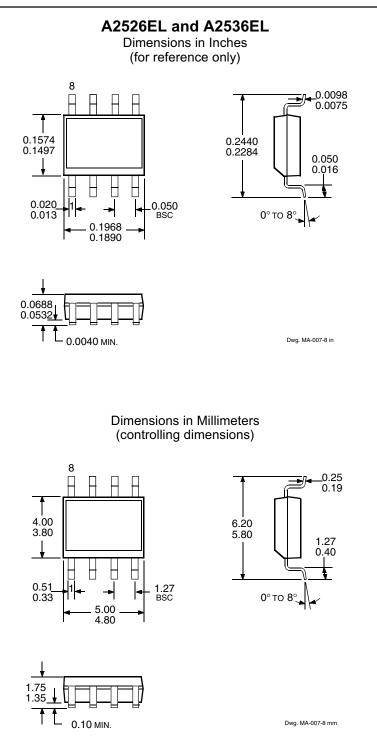

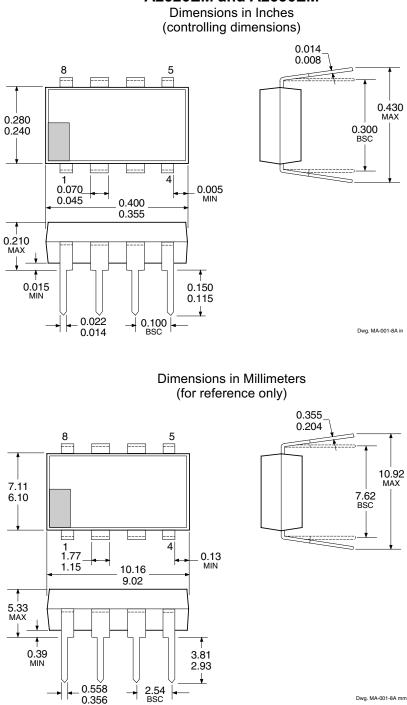

These switches are provided in 8-pin mini-DIP (suffix 'M') and 8-lead SOIC (suffix 'L') packages.

## Features

- 2.7 V to 5.8 V Input

- Up to 500 mA Continuous Load Current per Port

- 140 mΩ Maximum ON-Resistance

- 1.25 A Maximum Short-Circuit Current Limit

- Individual Open-Drain Fault Flag Outputs

- 125 µA Typical ON-State Supply Current

- <1 µA Typical OFF-State Supply Current</p>

- Outputs Can be Forced Higher Than Input (off-state)

- Thermal Shutdown

- 2.2 V Typical Undervoltage Lockout

- 0.6 ms Turn On (soft-start) and Fast Turn Off

- A2526 (active-high) Improved Replacement for MIC2526-1

- A2536 (active-low) Improved Replacement for MIC2526-2

## Applications

- USB Hosts and Self-Powered Hubs

- USB Bus-Powered Hubs

- Hot Plug-In Power Supplies

- Battery-Charger Circuits

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 Copyright © 2000, Allegro MicroSystems, Inc.

|                             |                                                                                                 | Limits |       |      |       |  |

|-----------------------------|-------------------------------------------------------------------------------------------------|--------|-------|------|-------|--|

| Parameter                   | Test Conditions                                                                                 | Min    | Тур   | Max  | Units |  |

| Operating Voltage Range     | V <sub>IN</sub>                                                                                 | 2.7    | _     | 5.8  | V     |  |

| Switch Resistance           | V <sub>IN</sub> = 5 V, I <sub>OUT</sub> = 500 mA                                                | _      | 100   | 140  | mΩ    |  |

|                             | VIN = 3.3 V, IOUT = 500 mA                                                                      | _      | 100   | 140  | mΩ    |  |

| Output Leakage Current      | Each output (output disabled), $V_{IN}$ = 5 V, $V_{OUT}$ = 0                                    | _      | <1.0  | 10   | μA    |  |

| Maximum Load Current        | Each output                                                                                     | 500    | _     | _    | mA    |  |

| Short-Circuit Current Limit | Each output (enabled into load), V <sub>OUT</sub> = 4 V                                         | 0.5    | 0.75  | 1.25 | А     |  |

| Current-Limit Threshold     | Ramped load applied to enabled output, $V_{\text{OUT}} \leq 4~\text{V}$                         | -      | 0.9   | _    | А     |  |

| ENABLE Input Threshold      | Low-to-high transition                                                                          | -      | 2.1   | 2.4  | V     |  |

|                             | High-to-low transition                                                                          | 0.8    | 1.9   | _    | V     |  |

| ENABLE Input Hysteresis     |                                                                                                 | -      | 0.2   | _    | V     |  |

| ENABLE Input Current        | V <sub>EN</sub> = 0 V to 5.5 V                                                                  | -      | ±0.01 | ±1.0 | μA    |  |

| ENABLE Input Cap.           |                                                                                                 | -      | 1.0   | _    | pF    |  |

| Output Turn-On Delay        | $\rm R_L$ = 10 $\Omega,  \rm C_L$ = 1 $\mu \rm F,  50\%   V_{\rm ENABLE}$ to 10% $\rm V_{OUT}$  | Ι      | 0.5   | _    | ms    |  |

| Output Turn-On Rise Time    | $\rm R_L$ = 10 $\Omega,  \rm C_L$ = 1 $\mu \rm F,  10\%   V_{\rm OUT}$ to 90% $\rm V_{\rm OUT}$ | Ι      | 0.6   | _    | ms    |  |

| Output Turn-Off Delay       | $\rm R_L$ = 10 $\Omega, C_L$ = 1 $\mu F, 50\% \; V_{\rm ENABLE}$ to 90% $V_{\rm OUT}$           | Ι      | 10    | _    | μs    |  |

| Output Turn-Off Fall Time   | $\rm R_L$ = 10 $\Omega, \rm C_L$ = 1 $\mu \rm F, 90\% \; V_{\rm OUT}$ to 10% $\rm V_{\rm OUT}$  | Ι      | 25    | _    | μs    |  |

| Error Flag Output           | V <sub>IN</sub> = 5 V, I <sub>L</sub> = 10 mA                                                   | Ι      | 8.0   | _    | Ω     |  |

| Resistance                  | V <sub>IN</sub> = 3.3 V, I <sub>L</sub> = 10 mA                                                 | Ι      | 10    | _    | Ω     |  |

| Error Flag Off Current      | V <sub>FLG</sub> = 5 V                                                                          | -      | 0.01  | _    | μA    |  |

| Supply Current              | Both switches disabled (see note), OUT = open                                                   | -      | 0.2   | 5.0  | μA    |  |

|                             | Both switches enabled (see note), OUT = open                                                    | _      | 125   | 160  | μA    |  |

| UVLO Threshold              | Increasing V <sub>IN</sub>                                                                      | -      | 2.35  | _    | V     |  |

|                             | Decreasing V <sub>IN</sub>                                                                      | -      | 2.2   | _    | V     |  |

| Over-Temperature            | Increasing T <sub>J</sub>                                                                       | Ι      | 165   | _    | °C    |  |

| Shutdown Threshold          | Decreasing T <sub>J</sub>                                                                       | -      | 155   | _    | °C    |  |

## **Electrical Characteristics** at $T_A = 25^{\circ}C$ , $V_{IN} = 5 V$ , each output tested separately (unless otherwise noted).

Note — Disabled is  $\leq 0.8$  V and enabled is  $\geq 2.4$  V (active high) for the A2526EL/EM. Disabled is  $\geq 0.8$  V<sub>IN</sub> and enabled is  $\leq 0.8$  V (active low) for the A2536EL/EM.

## FUNCTIONAL DESCRIPTION

#### **Power switch**

The power switch is an N-channel MOSFET with a maximum on-state resistance of 140 m $\Omega$  (V<sub>IN</sub> = 5 V). Configured as a high-side switch, the power switch prevents current flow in either direction if disabled. The drain body diode is disconnected from the source when the switch is OFF allowing the output voltage to exceed the input voltage without causing current conduction. The power switch supplies a minimum of 500 mA per switch.

#### Charge pump

An internal charge pump supplies power to the driver circuit and provides the necessary voltage to pull the gate of the MOSFET above the source. The charge pump operates from input voltages as low as 2.7 V. The charge pump is limited to  $2.5 \,\mu$ A to establish a controlled turn on time of typically 1 ms.

#### Driver

The driver controls the gate voltage of the power switch. To limit large current surges and reduce the associated electromagnetic interference (EMI) produced, the driver incorporates circuitry that controls the rise times and fall times of the output voltage. The rise time is typically 1 ms.

## ENABLE (EN or EN)

The logic enable disables the power switch and the bias for the charge pump, driver, and other circuitry to reduce the supply current to less than 5  $\mu$ A maximum when a logic high is present on EN (A2526) or a logic low is present (A2536). The proper logic level restores bias to the drive and control circuits and turns the power ON. The enable input is a compatible with both TTL and CMOS logic levels.

## Fault Flag (FLG)

This open drain output is asserted (active low) when an overcurrent or over temperature condition is encountered. The output will remain asserted until the overcurrent or over temperature condition is removed.

#### **Current sense**

A sense FET monitors the current supplied to the load. The sense FET measures current more efficiently than conventional resistance methods. When an overload or short circuit is encountered, the current-sense circuitry sends a control signal to the driver. The driver in turn reduces the gate voltage and drives the power FET into its saturation region, which switches the output into a constant-current mode and holds the current constant while varying the voltage on the load.

#### Thermal sense

An internal thermal-sense circuit shuts off the power switch when the junction temperature rises to approximately 165°C. Hysteresis is built into the thermal sense circuit. After the device has cooled approximately 10°C, the switch turns back ON. The switch continues to cycle off and on until the fault is removed.

## Undervoltage lockout

A voltage-sense circuit monitors the input voltage. When the input voltage is approximately 2 V, a control signal turns OFF the power switch.

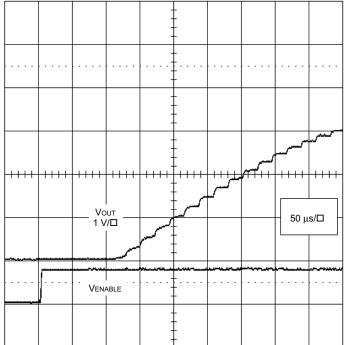

## **NO-LOAD SWITCHING PERFORMANCE**

|       |           |                |                                                | -<br>-<br>-<br>-                          |             |       |        |         |

|-------|-----------|----------------|------------------------------------------------|-------------------------------------------|-------------|-------|--------|---------|

|       | Vo<br>1 V | <br>)UT<br>//□ |                                                |                                           |             |       |        |         |

| -++++ | ++++      | -++++          | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- |                                           | ++++        | -++++ | - 50 μ | s/□ -   |

|       |           |                |                                                |                                           |             |       |        | <u></u> |

|       | Ven/      | ABLE           |                                                | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | <br><u></u> |       |        |         |

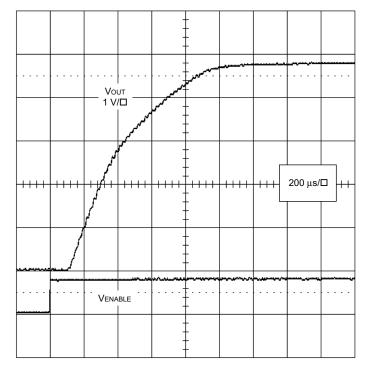

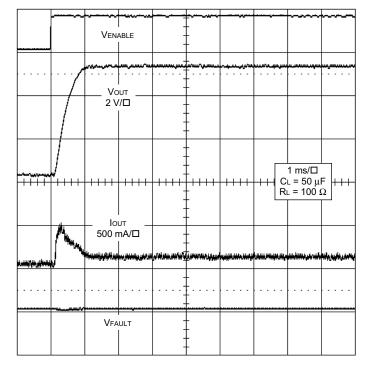

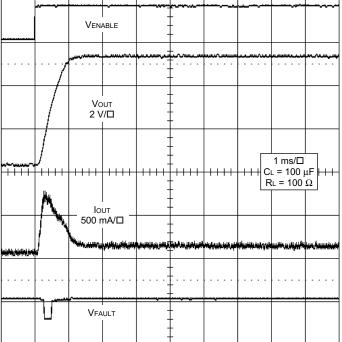

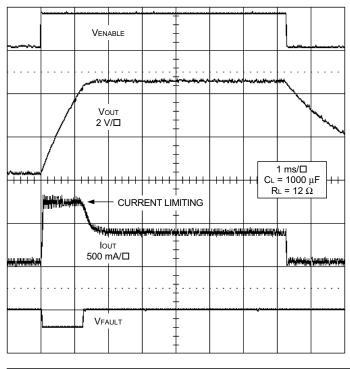

## CAPACITIVE-LOAD SWITCHING PERFORMANCE

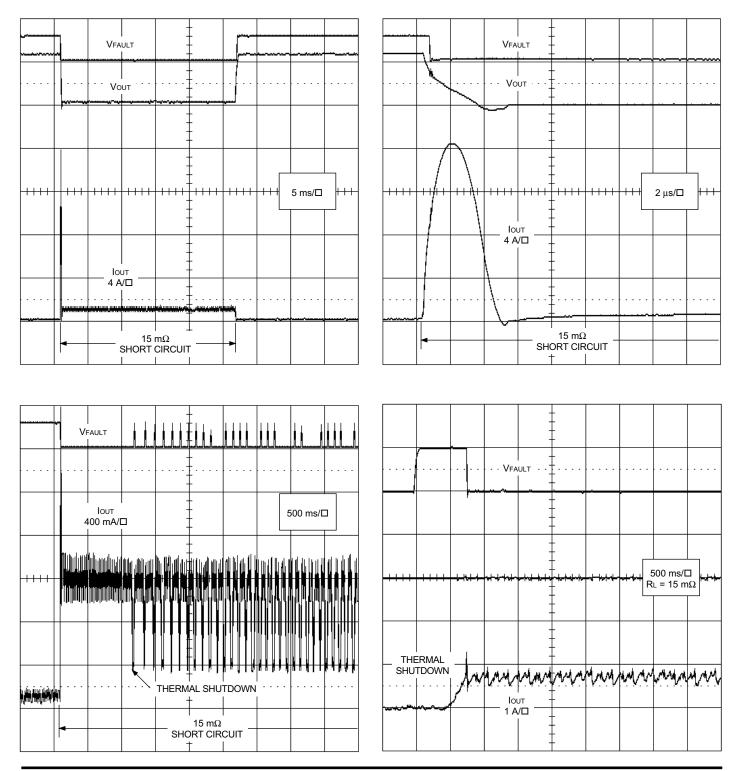

## **OUTPUT SHORT-CIRCUIT PERFORMANCE**

www.allegromicro.com

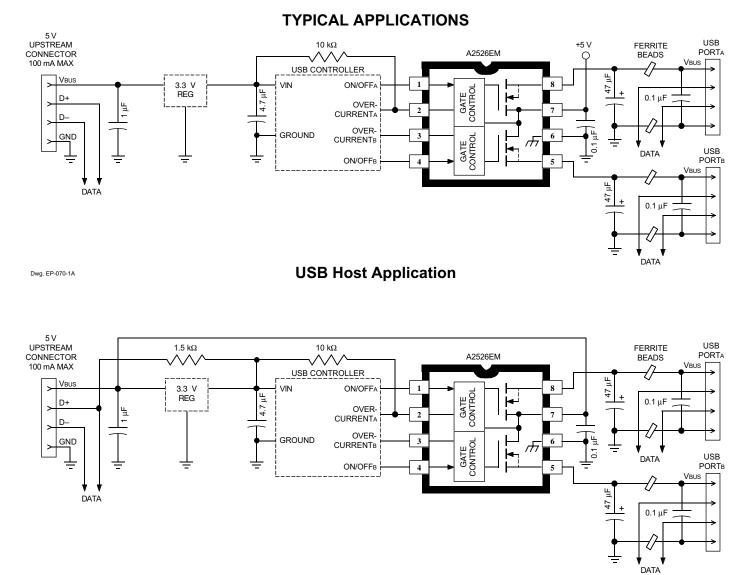

## **APPLICATIONS INFORMATION**

#### Overcurrent

A sense FET is employed for overcurrent conditions. Unlike current-sense resistors, sense FETs do not increase the series resistance of the current path. When an overcurrent condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Complete shutdown occurs only if the fault is present long enough to activate thermal limiting.

Three possible overload conditions can occur. In the first condition, the output has been shorted before the device is enabled or between  $V_{\rm IN}$  has been applied. The device senses the short and immediately switches into a constant-current output.

In the second condition, the short occurs while the device is enabled. At the instant the short occurs, very high currents may flow for a short time before the current-limit circuit can react . After the current-limit circuit has tripped (reached the overcurrent trip threshold) the device switches into constantcurrent mode.

In the third condition, the load has been gradually increased beyond the recommended operating current. The current is permitted to rise until the current-limit threshold is reached or until the thermal limit of the device is exceeded. The device is capable of delivering current up to the current-limit threshold without damage. Once the threshold has been reached, the device switches into its constant-current mode.

## Fault Flag (FLG)

The FLG open-drain output is asserted (active low) when an overcurrent or over-temperature condition is encountered. The output will remain asserted until the overcurrent or overtemperature condition is removed. Connecting a heavy capacitive load to an enabled device can cause momentary false over-current reporting from the inrush current flowing through the device, charging the downstream capacitor. An RC filter can be connected to the terminal to reduce false overcurrent reporting. Using low-ESR electrolytic capacitors on the output lowers the inrush current flow through the device during hotplug events by providing a low impedance energy source, thereby reducing erroneous overcurrent reporting.

#### Power dissipation and junction temperature

The low on-resistance of the n-channel MOSFET allows small surface-mount packages, such as an SOIC, to pass large currents. The thermal resistance of these packages are high compared to those of power packages; it is good design practice to check power dissipation and junction temperature. The first step is to find  $r_{DS(on)}$  at the input voltage and operating temperature. Next, calculate the power dissipation using:

$P_D = r_{DS(on)} \times I^2$

Finally, calculate the junction temperature:

$T_{\rm J} = P_{\rm D} \times R_{\rm \theta JA} + T_{\rm A}$

where:

$T_A$  = ambient temperature °C

$R_{\theta JA}$  = thermal resistance (SOIC = 108°C/W, DIP = 60°C/W).

#### **Thermal protection**

Thermal protection prevents damage to the IC when heavyoverload or short-circuit faults are present for extended periods of time. The faults force these devices into constant-current mode, which causes the voltage across the high-side switch to increase; under short-circuit conditions, the voltage across the switch is equal to the input voltage. The increased dissipation causes the junction temperature to rise to high levels. The protection circuit senses the junction temperature of the switch and shuts it OFF. Hysteresis is built into the thermal sense circuit, and after the device has cooled approximately 20°, the switch turns back ON. The switch continues to cycle in this manner until the load fault or input power is removed.

#### Undervoltage lock-out (UVLO)

An undervoltage lockout ensures that the power switch is in the OFF state at power up. Whenever the input voltage falls below approximately 2 V, the power switch will be quickly turned OFF. This facilitates the design of hot-insertion systems where it is not possible to turn OFF the power switch before input power is removed. The UVLO will also keep the switch from being turned ON until the power supply has reached at least 2 V, even if the switch is enabled. Upon reinsertion, the power switch will be turned ON, with a controlled rise time to reduce EMI and voltage overshoots.

#### Power supply considerations

A 0.1  $\mu$ F ceramic bypass capacitor between IN and GND, close to the device, is recommended. Placing a high-value electrolytic capacitor on the output terminals is also desirable when the output load is heavy. The capacitor reduces power supply transients that may cause ringing on the input. Also, bypassing the output with a 0.01  $\mu$ F to 0.1  $\mu$ F ceramic capacitor improves the immunity of the device to short-circuit transients.

Dwg. EP-070-11A

NOTES: 1. Lead spacing tolerance is non-cumulative.

2. Exact body and lead configuration at vendor's option within limits shown.

A2526EM and A2536EM

NOTES: 1. Leads 1, 4, 5, and 8 may be half leads at vendor's option.

- 2. Lead thickness is measured at seating plane or below.

- 3. Lead spacing tolerance is non-cumulative.

- 4. Exact body and lead configuration at vendor's option within limits shown.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.