# ASDN010 Schottky Diode Array

#### **Features**

- Provides protection regardless of card loading conditions

- Fast turn on and reverse revovery characteristics

- 24 pin QSOP package has a small footprint, saving valuable board space

- 18 channel, dual rail clamping capacity

- Ideal for applications that require noise immunity and low power consumption

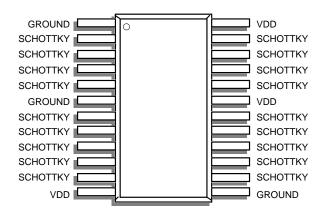

Pin Configuration — Top view

#### **Description**

The ASDN010 is a Schottky Diode Memory Bus Terminator designed to eliminate overshoot and undershoot problems caused by reflections on high speed lines, while maintaining noise immunity and minimizing any losses in power consumption.

The ASDN010 is an ideal terminator for applications such as SDRAM bus lines, or v2.1 66MHz PCI busses.

The ASDN010 supports up to 18 terminated lines. Each line can be simultaneously clamped to both ground and power supply rails, allowing effective termination under a wide variety of loading conditions.

#### QSOP (MWP)

## **Ordering Information**

| Package     | Temperature Range | Order Code |

|-------------|-------------------|------------|

| 14-Pin QSOP | 0 to 70° C        | ASDN010MWP |

© ASTEC Semiconductor 1

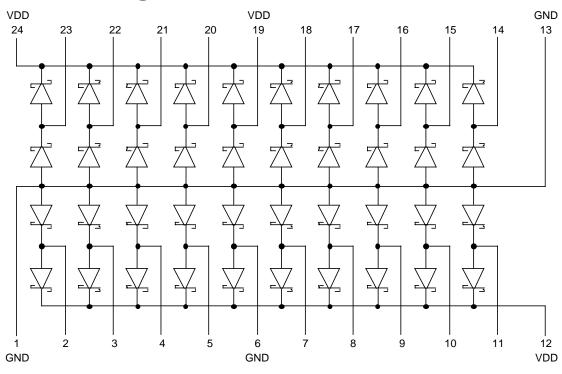

## **Functional Block Diagram**

## **Absolute Maximum Ratings**

| Parameter                              | Symbol             | Rating       | Units |  |

|----------------------------------------|--------------------|--------------|-------|--|

| Supply Voltage                         | $V_{DD}$           | -0.3 to +7.0 | V     |  |

| Channel clamp current (continuous)     | I <sub>CLAMP</sub> | ±50          | mA    |  |

| Operating Temperature                  |                    | 0 to 70      | °C    |  |

| Package Power Rating (QSOP @ 70°C)     |                    | 1.00 (max.)  | W     |  |

| Junction Temperature                   | TJ                 | 150          | °C    |  |

| Storage Temperature                    | T <sub>STG</sub>   | - 65 to 150  | °C    |  |

| Lead Temperature, Soldering 10 Seconds | TL                 | 300          | °C    |  |

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended Conditions**

| Parameter | Symbol           | Rating | Unit |

|-----------|------------------|--------|------|

| Voltage   | $V_{VDD}$        | 20     | V    |

| Current   | I <sub>VDD</sub> | 10     | mA   |

## **Typical Thermal Resistances**

| Package θ <sub>JA</sub> |          | θЈС    | Typical Derating |

|-------------------------|----------|--------|------------------|

| 24L-QSOP                | 110° C/W | 8° C/W | 9.1 mW/°C        |

#### **Electrical Characteristics**

Electrical Characteristics are guaranteed over full junction temperature range (0 to  $70^{\circ}$  C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. The conditions are:  $V_{VDD} = 20V$  and  $I_{VDD} = 10$  mA unless otherwise stated.

| Parameter                   | Symbol          | Test<br>Condition                                                  | Min | Тур          | Max          | Unit   |

|-----------------------------|-----------------|--------------------------------------------------------------------|-----|--------------|--------------|--------|

| Diode Forward Voltage       | V <sub>F</sub>  | I <sub>F</sub> = 16 mA<br>I <sub>F</sub> = 50 mA                   |     | 0.65<br>0.80 | 0.85<br>1.00 | V<br>V |

| Max. Bus Speed (see note 1) |                 | $Z_{\rm O} = 50\Omega$ , Logic Swing 0.4V to 3.0V                  |     | 125          |              | MHz    |

| Channel leakage             | I <sub>CL</sub> | $0 \le V_{IN} \le V_{DD}$                                          |     | 0.1          | 5.0          | μΑ     |

| Input Capacitance           |                 | $f = 1 \text{ MHz}, V_{IN} = 2.5V, T_A = 25^{\circ}C, V_{DD} = 5V$ |     | 5            |              | pF     |

| ESD Protection              |                 | MIL-STD-883, Method 3015                                           | 2   |              |              | KV     |

Note 1: The presence of a Schottky diode for clamping bus overshoots will cause additional delays of signal edges. These delays are the result of diode characteristics such as forward voltage, diode capacitance and the reverse recovery phenomenon. The ground clamp diode is most critical, particularly if VLSI circuits such as static or dynamic memories are directly connected to busses without any buffer stages. The incremental delay observed on a positive edge following a negative transition that forward biased the Schottky diode is less than 800 pS. That represents less than 10% of the 125 MHz (8 nS period) bus cycle time.

## **Typical Performance Curves**

None available at time of printing