# **ADS1250**

For most current data sheet and other product information, visit www.burr-brown.com

# Resolution 20-Bit Data Acquisition System ANALOG-TO-DIGITAL CONVERTER

## **FEATURES**

- 20 BITS NO MISSING CODES

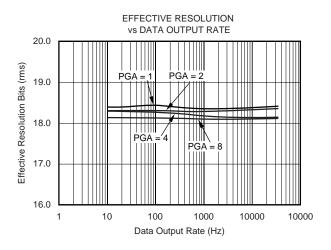

- 18 BITS EFFECTIVE RESOLUTION UP TO 25kHz DATA RATE

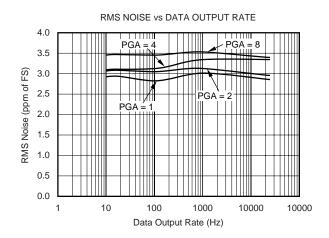

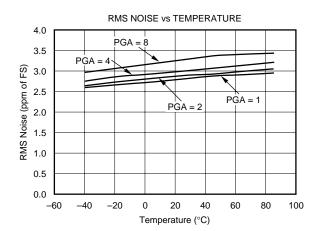

- LOW NOISE: 2.8ppm at PGA = 1

- DIFFERENTIAL INPUTS

- INL: 0.002% (MAX)

- PROGRAMMABLE FULL SCALE

- I/O CONTROLLED PGA: 1, 2, 4, 8

- EXTERNAL REFERENCE

## **APPLICATIONS**

- CARDIAC DIAGNOSTICS

- DIRECT THERMOCOUPLE INTERFACE

- BLOOD ANALYSIS

- INFRARED PYROMETER

- LIQUID/GAS CHROMATOGRAPHY

- PRECISION PROCESS CONTROL

# DESCRIPTION

The ADS1250 is a precision, wide dynamic range, delta-sigma, analog-to-digital converter with 20-bit resolution operating from a single +5V supply. The delta-sigma architecture is used for wide dynamic range and to guarantee 20 bits of no missing code performance. An effective resolution of 18 bits (2.8ppm of rms noise) is achieved for conversion rates up to 25kHz. The dynamic range of the converter is further increased by providing a low-noise Programmable Gain Amplifier (PGA) with gain stages of 1, 2, 4, or 8 for low level input signals.

The ADS1250 is designed for high-resolution measurement applications in cardiac diagnostics, smart transmitters, industrial process control, weigh scales, chromatography and portable instrumentation. The converter includes a flexible synchronous serial interface and offers a three-wire control mode for low-cost isolation.

The ADS1250 is a single-channel converter and is offered in an SOL-16 package.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Bivd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

All specifications at  $T_{MIN}$  to  $T_{MAX}$ ,  $V_D = V_S = +5V$ , CLK = 9.6MHz, PGA = 1, and  $V_{REF} = 4.096$ , unless otherwise specified.

|                                                                                                                                                                                          |                                                                             | ADS1250U             |                                                        |                                      |                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------|--------------------------------------------------------|--------------------------------------|--------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                | CONDITIONS                                                                  | MIN                  | TYP                                                    | MAX                                  | UNITS                                                        |

| ANALOG INPUT Input Voltage Range <sup>(1)</sup> Programmable Gain Amplifier Input Impedance (differential) Input Capacitance Input Leakage                                               | G = Gain G = Gain G = Gain At +25°C At T <sub>MIN</sub> to T <sub>MAX</sub> | AGND<br>1            | 104/G<br>6 • G<br>5                                    | ±V <sub>REF</sub> /G<br>8<br>50<br>1 | V<br>kΩ<br>pF<br>pA<br>nA                                    |

| DYNAMIC CHARACTERISTICS  Data Rate  Bandwidth  Serial Clock (SCLK)  System Clock Input (CLK)                                                                                             | 3dB                                                                         | 5.4                  |                                                        | 25<br>9.6<br>9.6                     | kHz<br>kHz<br>MHz<br>MHz                                     |

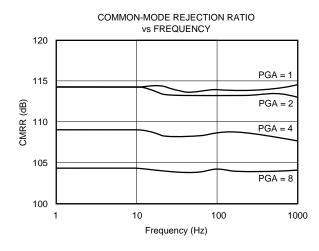

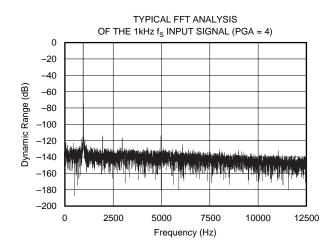

| ACCURACY Integral Linearity Error <sup>(2)</sup> THD Noise Resolution No Missing Codes Common-Mode Rejection <sup>(3)</sup> Gain Error Offset Error Gain Sensitivity to V <sub>REF</sub> | 1kHz Input; 0.1dB below FS at DC $V_{REF} = 4.096V \pm 0.1V$                | 90                   | ±0.0012<br>97<br>2.8<br>20<br>20<br>105<br>±100<br>1:1 | ±0.0020 3.8 1 ±200                   | % of FSR dB ppm of FSR, rms Bits Bits dB % of FSR ppm of FSR |

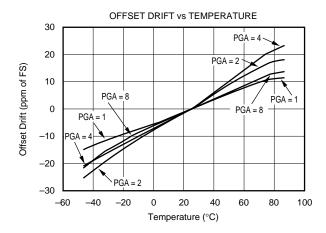

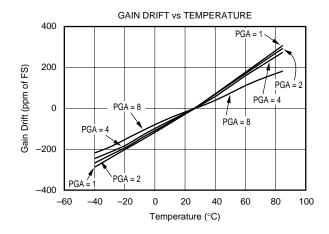

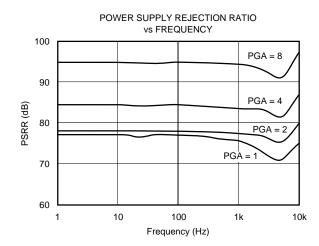

| Power Supply Rejection Ratio  PERFORMANCE OVER TEMPERATURE Offset Drift Gain Drift                                                                                                       |                                                                             | 60                   | 78<br>0.25<br>5.0                                      |                                      | dB<br>ppm/°C<br>ppm/°C                                       |

| VOLTAGE REFERENCE V <sub>REF</sub> Load Current                                                                                                                                          |                                                                             | 3.996V               | 4.096<br>125                                           | 4.196                                | V<br>μA                                                      |

| DIGITAL INPUT/OUTPUT Logic Family Logic Level: V <sub>IH</sub> V <sub>IL</sub> V <sub>OH</sub> V <sub>OL</sub> Data Format                                                               | I <sub>OH</sub> = -500μA<br>I <sub>OL</sub> = 500μA                         | +4.0<br>-0.3<br>+4.5 | CMOS  ary Two's Complen                                | +V <sub>D</sub> + 0.3<br>+0.8<br>0.4 | V<br>V<br>V                                                  |

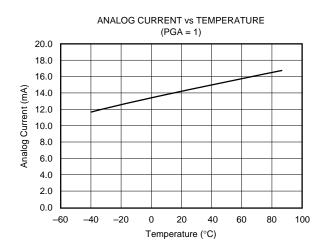

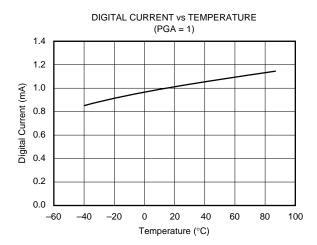

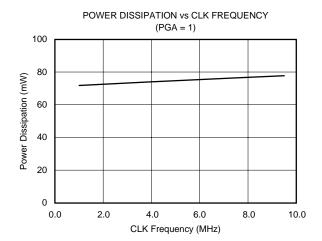

| POWER SUPPLY REQUIREMENTS Operation Quiescent Current, Analog Quiescent Current, Digital Operating Power                                                                                 | V = +5VDC<br>V = +5VDC                                                      | +4.75                | +5<br>14<br>1<br>75                                    | +5.25<br>100                         | VDC<br>mA<br>mA<br>mW                                        |

| TEMPERATURE RANGE Operating Storage                                                                                                                                                      |                                                                             | -40<br>-60           |                                                        | +85<br>+100                          | °C<br>°C                                                     |

NOTES: (1) In order to achieve the converter's full-scale range, the input must be fully differential. If the input is single-ended ( $+V_{IN}$  or  $-V_{IN}$  is fixed), then the full-scale range is one-half that of the differential range. (2) Applies to full-differential signals. (3) The common-mode rejection test is performed with a 100mV differential input.

#### **ABSOLUTE MAXIMUM RATINGS**

| Analog Input: Current             |                                     |

|-----------------------------------|-------------------------------------|

|                                   | ±10mA, Continuous                   |

| Voltage                           | AGND -0.3V to V <sub>S</sub> + 0.3V |

| V <sub>S</sub> to V <sub>D</sub>  | 0.3V to 6V                          |

| V <sub>S</sub> to AGND            |                                     |

| V <sub>D</sub> to DGND            | 0.3V to 6V                          |

| AGND to DGND                      |                                     |

| V <sub>REF</sub> Voltage to AGND  | 0.3V to V <sub>S</sub> + 0.3V       |

| Digital Input Voltage to DGND     | –0.3V to V <sub>D</sub> + 0.3V      |

| Digital Output Voltage to DGND    | 0.3V to V <sub>D</sub> + 0.3V       |

| Lead Temperature (soldering, 10s) | +300°C                              |

| Power Dissipation (any package)   | 500mW                               |

|                                   |                                     |

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection methods.

#### **PACKAGE/ORDERING INFORMATION**

| PRODUCT  | PACKAGE | PACKAGE<br>DRAWING<br>NUMBER | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(1)</sup> | TRANSPORT<br>MEDIA     |

|----------|---------|------------------------------|-----------------------------------|--------------------|-----------------------------------|------------------------|

| ADS1250U | SOL-16  | 211                          | -40°C to +85°C                    | ADS1250U           | ADS1250U<br>ADS1250U/1K           | Rails<br>Tape and Reel |

NOTE: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /1K indicates 1000 devices per reel). Ordering 1000 pieces of "ADS1250U/1K" will get a single 1000-piece Tape and Reel.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

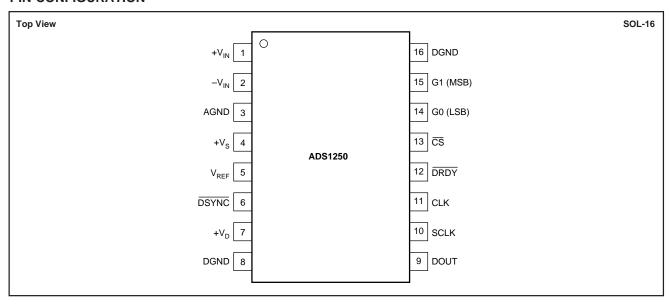

## **PIN CONFIGURATION**

# **PIN DESCRIPTIONS**

| PIN | NAME             | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | +V <sub>IN</sub> | Analog Input: Positive Input of the Differential Analog Input.                                                                                                                                                                                                                                                 |

| 2   | $-V_{IN}$        | Analog Input: Negative Input of the Differential Analog Input.                                                                                                                                                                                                                                                 |

| 3   | AGND             | Analog Input: Analog Ground.                                                                                                                                                                                                                                                                                   |

| 4   | +V <sub>S</sub>  | Analog Input: Analog Power Supply Voltage, +5V.                                                                                                                                                                                                                                                                |

| 5   | $V_{REF}$        | Analog Input: Reference Voltage Input.                                                                                                                                                                                                                                                                         |

| 6   | DSYNC            | Digital Input: Data Synchronization. A falling edge on this input will reset the modulator count and place the modulator in a hold state. The modulator is released from the hold state on the rising edge of DSYNC. This can be used to synchronize multiple ADS1250s.                                        |

| 7   | +V <sub>D</sub>  | Digital Input: Digital Power Supply Voltage, +5V.                                                                                                                                                                                                                                                              |

| 8   | DGND             | Digital Input: Digital Ground.                                                                                                                                                                                                                                                                                 |

| 9   | DOUT             | Digital Output: Serial Data Output. The serial data is clocked out of the serial data output shift register through this pin. The pin is driven when $\overline{\text{CS}}$ is LOW, and high impedance when $\overline{\text{CS}}$ is HIGH.                                                                    |

| 10  | SCLK             | Digital Input: Serial Clock. The serial clock is in the form of a CMOS-compatible clock. The serial clock can operate up to the device's system clock frequency. The serial clock can be either a free-running clock or noncontinuous clock, with either type of clock; the serial data output is gated by CS. |

| 11  | CLK              | Digital Input: Device System Clock. The system clock is in the form of a CMOS-compatible clock.                                                                                                                                                                                                                |

| 12  | DRDY             | Digital Output: Data Ready. A falling edge on this output indicates that a new output word is available from the ADS1250 data output register.                                                                                                                                                                 |

| 13  | <del>CS</del>    | Digital Input: Chip Select. Active LOW logic input used to enable serial data output from the ADS1250. $\overline{CS}$ controls the state of the DOUT pin. If $\overline{CS}$ is HIGH, DOUT is high impedance; if $\overline{CS}$ is LOW, DOUT drives the bus. $\overline{CS}$ can be used in three ways:      |

|     |                  | (1) If the ADS1250 shares the bus with other devices, $\overline{\text{CS}}$ is used as serial data output enable for communications.                                                                                                                                                                          |

|     |                  | (2) If the ADS1250 shares the bus with other devices and SCLK is a free-running clock, $\overline{CS}$ is used to gate serial data out of the device.                                                                                                                                                          |

|     |                  | (3) If the ADS1250 is the only device on the bus, $\overline{\text{CS}}$ can be tied LOW to always enable serial data output for a two-wire interface.                                                                                                                                                         |

|     |                  | Refer to the Serial Communications section of this data sheet for more detail.                                                                                                                                                                                                                                 |

| 14  | G0               | Digital Input: Gain Selection Control (LSB).                                                                                                                                                                                                                                                                   |

| 15  | G1               | Digital Input: Gain Selection Control (MSB).                                                                                                                                                                                                                                                                   |

| 16  | DGND             | Digital Input: Digital Ground.                                                                                                                                                                                                                                                                                 |

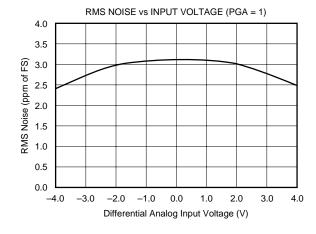

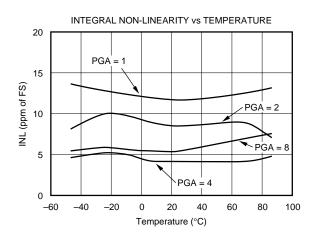

# TYPICAL PERFORMANCE CURVES

At  $T_A = +25^{\circ}C$ ,  $V_D = V_S = +5V$ , CLK = 9.6MHz, PGA = 1, and  $V_{REF} = 4.096$ , unless otherwise specified.

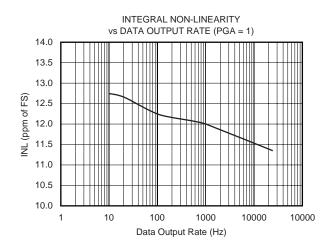

# **TYPICAL PERFORMANCE CURVES (Cont.)**

At  $T_A = +25$ °C,  $V_D = V_S = +5V$ , CLK = 9.6MHz, PGA = 1, and  $V_{REF} = 4.096$ , unless otherwise specified.

# **TYPICAL PERFORMANCE CURVES (Cont.)**

At  $T_A$  = +25°C,  $V_D$  =  $V_S$  = +5V, CLK = 9.6MHz, PGA = 1, and  $V_{REF}$  = 4.096, unless otherwise specified.

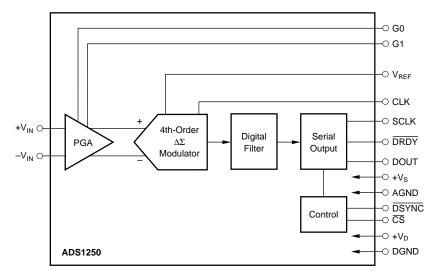

# THEORY OF OPERATION

The ADS1250 is a precision, high dynamic range, 20-bit, delta-sigma, A/D converter capable of achieving very highresolution digital results at high data rates. The analog input signal is continuously sampled at a rate determined by the frequency of the system clock (CLK). The sampled analog input is modulated by the delta-sigma A/D modulator, followed by a digital filter value. A programmable gain function is also incorporated in the delta-sigma modulator with larger input sampling capacitors for higher gains. A sinc<sup>5</sup> digital low-pass filter processes the output of the delta-sigma modulator and writes the result into the data output register. The DRDY pin is pulled LOW indicating that new data is available to be read by the external microcontroller/microprocessor. As shown in the block diagram, the main functional blocks of the ADS1250 are the programmable gain amplifier, a fourth-order delta-sigma modulator, a digital filter, control logic, and a serial interface. Each of these functional blocks is described below.

#### **ANALOG INPUT**

The ADS1250 contains a fully differential analog input with programmable gain. The fully differential switched capacitor architecture provides low system noise, common-mode rejection of 105dB, and excellent power supply rejection. The selectable gains on the input are 1, 2, 4, or 8, which gives a bipolar input voltage range from -4.096 to +4.096V, to  $-512 \mathrm{mV}$  to  $+512 \mathrm{mV}$ , when the reference input voltage equals +4.096V. The bipolar ranges are with respect to  $-\mathrm{V_{IN}}$  and not with respect to GND.

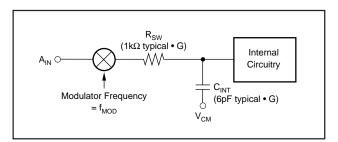

Figure 1 shows the basic input structure of the ADS1250. The analog input impedance is directly related to the sampling frequency of the input capacitor ( $f_{MOD}$ ), and the gain setting (G) of the device. The sampling frequency of the input capacitor is derived from the system clock (CLK). Therefore, a lower CLK rate decreases the sampling frequency, which results in a higher analog input impedance.

FIGURE 1. Analog Input Structure.

Additionally, a lower gain setting (G) decreases the sampling capacitor size, which results in a higher analog input impedance. This can be seen in the following equation:

$$A_{IN} \text{ Impedance } (\Omega) = \frac{9.6 \text{ MHz} \bullet 104E3}{\text{CLK} \bullet \text{G}}$$

With regard to the analog input signal, the overall analog performance of the device is affected by three items. First, the input impedance can affect accuracy. If the source impedance of the input signal is significant, or if there is passive filtering prior to the ADS1250, a significant portion of the signal can be lost across this external impedance. The magnitude of the effect is dependent on the desired system performance.

Second, the current into or out of the analog inputs must be limited. Under no conditions should the current into or out of the analog inputs exceed 10mA.

Third, to prevent aliasing of the input signal, the bandwidth of the analog input signal must be band limited. The bandwidth is a function of the system clock frequency. With a system clock frequency of 9.6MHz, the data output rate is 25kHz, with a -3dB frequency of 5.4kHz. The -3dB frequency scales with the system clock frequency.

To guarantee the best linearity of the ADS1250, a fully differential signal is recommended.

#### PROGRAMMABLE GAIN AMPLIFIER

The PGA gain setting is programmed via the PGA pins on the ADS1250. Changes in the gain setting (G) of the PGA results in an increase in the input capacitor size. Therefore, higher gain settings result in a lower analog input impedance.

The PGA of the ADS1250 can be set to a gain of 1, 2, 4, or 8, substantially increasing the dynamic range of the converter and simplifying the interface to the more common transducers (see Table I).

| GAIN SETTING |    |            | ANALOG INPUT            |                         |  |

|--------------|----|------------|-------------------------|-------------------------|--|

| G1           | G0 | GAIN VALUE | DIFFERENTIAL<br>FSR (V) | SINGLE-ENDED<br>FSR (V) |  |

| 0            | 0  | 1          | 8.192                   | 4.096                   |  |

| 0            | 1  | 2          | 4.096                   | 2.048                   |  |

| 1            | 0  | 4          | 2.048                   | 1.024                   |  |

| 1            | 1  | 8          | 1.024                   | 0.512                   |  |

NOTE: Based on a 4.096V reference. The ADS1250 allows common-mode voltage as long as the absolute input voltage on +V $_{\rm IN}$  or -V $_{\rm IN}$  does not go below AGND or above +V $_{\rm S}$ .

TABLE I. Full-Scale Range versus PGA Setting.

#### **DELTA-SIGMA MODULATOR**

The modulator clock is generated by dividing the system clock by 6. With a nominal system clock frequency of 9.6MHz, the modulator clock frequency is 1.6MHz (9.6MHz/6). The output from the modulator is oversampled 64 times by the digital filter. Therefore, with 1.6MHz modulator clock (derived from a 9.6MHz system clock), the data output rate is 25kHz (1.6MHz/64). The data output rate scales directly with the system clock frequency, as shown in Table II.

| CLK (MHz)                            | DATA OUTPUT RATE (Hz) |  |  |

|--------------------------------------|-----------------------|--|--|

| 9.600000                             | 25,000                |  |  |

| 7.372800(1)                          | 19,200                |  |  |

| 6.144000 <sup>(1)</sup>              | 16,000                |  |  |

| 6.000000(1)                          | 15,625                |  |  |

| 4.915200(1)                          | 12,800                |  |  |

| 3.686400(1)                          | 9,600                 |  |  |

| 3.072000(1)                          | 8,000                 |  |  |

| 2.457600 <sup>(1)</sup>              | 6,400                 |  |  |

| 1.843200(1)                          | 4,800                 |  |  |

| 0.921600                             | 2,400                 |  |  |

| 0.460800                             | 1,200                 |  |  |

| 0.384000                             | 1,000                 |  |  |

| 0.192000                             | 500                   |  |  |

| 0.038400                             | 100                   |  |  |

| 0.023040                             | 60                    |  |  |

| 0.019200                             | 50                    |  |  |

| 0.011520                             | 30                    |  |  |

| 0.009600                             | 25                    |  |  |

| 0.007680                             | 20                    |  |  |

| 0.006400                             | 16.67                 |  |  |

| 0.005760                             | 15                    |  |  |

| 0.004800                             | 12.50                 |  |  |

| 0.003840                             | 10                    |  |  |

| NOTE: (1) Standard Clock Oscillator. |                       |  |  |

TABLE II. CLK Rate versus Data Output Rate.

## **REFERENCE INPUT**

Unlike the analog input, the reference input impedance has no dependency on the PGA gain setting.

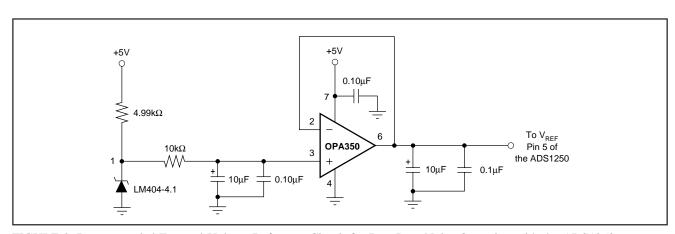

Reference input takes an average current of  $125\mu A$  with a 9.6MHz system clock. This current will be proportional to the system clock. A buffered reference is needed for ADS1250. The recommended reference circuit is shown in Figure 2.

Reference voltages higher than 4.096V will increase the full-scale range, while the absolute internal circuit noise of the converter remains the same. This will decrease the noise in terms of ppm of full scale. However, using a higher reference voltage will also degrade linearity. Therefore, the use of a higher reference voltage is not recommended.

Reference voltages lower than 4.096V will decrease the full-scale range, while the absolute internal circuit noise at the converter remains the same. This will increase the noise in terms of ppm of full scale. However, using a lower reference voltage will not degrade linearity. Therefore, the use of a lower reference voltage will reduce the effective resolution.

#### **DIGITAL FILTER**

The digital filter is a sinc<sup>5</sup> and is described by the following transfer function:

$$|H(f)| = \begin{cases} \sin\left(\frac{\pi \cdot f \cdot 64}{f_{MOD}}\right)^5 \\ 64 \cdot \sin\left(\frac{\pi \cdot f}{f_{MOD}}\right) \end{cases}$$

or

$$H(z) = \left(\frac{1 - z^{-64}}{64 \cdot (1 - z^{-1})}\right)^5$$

The digital filter of the ADS1250 computes the digital result based on the most recent outputs from the delta-sigma modulator. At the most basic level, the digital filter can be thought of as simply averaging the modulator results in a weighted form and presenting this average as the digital result. The digital result is calculated from the digital filter every 64 modulator clock cycles, or  $6 \cdot 64 = 384$  system clock cycles (refer to the Delta-Sigma Modulator section). However, if there is a significant change in the analog input, five full conversions are needed for the digital filter to settle. If the analog input change occurs asynchronously to the  $\overline{DRDY}$  pulse, six conversions are needed for the conversion to fully settle. Furthermore, the group delay is only 2.5 conversions due to the digital filter's linear phase response.

FIGURE 2. Recommended External Voltage Reference Circuit for Best Low Noise Operation with the ADS1250.

The digital output rate, or data rate, scales directly with the system CLK frequency. This allows the data output rate to be changed over a very wide range (five orders of magnitude) by changing the system CLK frequency. However, it is important to note that the –3dB point of the filter is 0.216 times the data output rate. Therefore, the data output rate should allow for sufficient margin to prevent attenuation of the signal of interest.

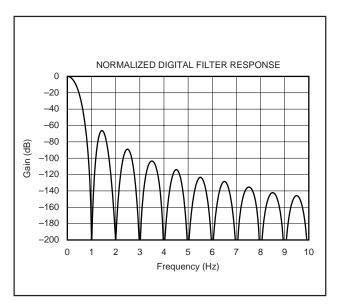

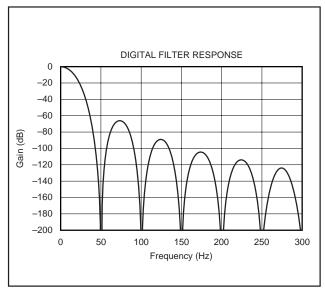

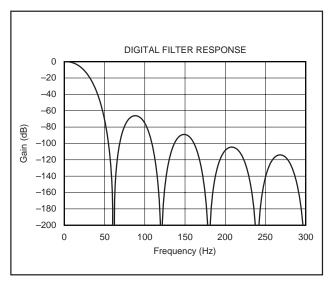

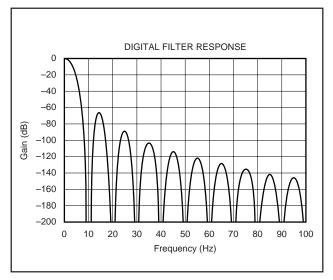

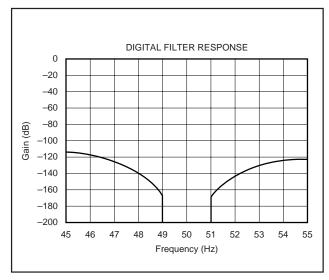

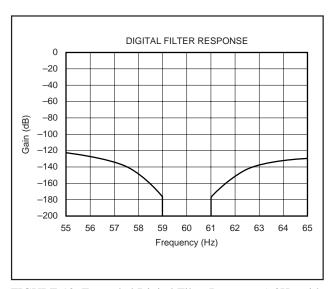

Since the conversion result is essentially an average, the data output rate determines the location of the resulting notches in the digital filter (see Figure 3). Note that the first notch is located at the data output rate frequency, and subsequent notches are located at integer multiples of the data output rate to allow for rejection of not only the fundamental frequency, but also harmonic frequencies. In this manner, the data output rate can be used to set specific notch frequencies in the digital filter response.

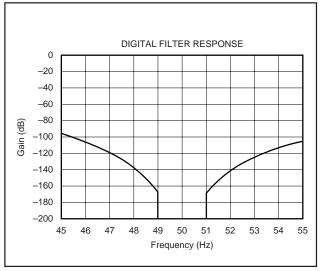

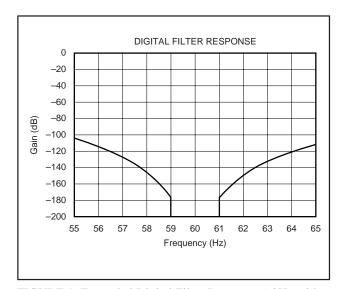

For example, if rejection of the power line frequency is desired, the data output rate can simply be set to the power line frequency. For 50Hz rejection, the system CLK frequency should be 19.200kHz; this will set the data output rate to 50Hz (see Table II and Figure 4). For 60Hz rejection, the system CLK frequency should be 23.040kHz; this will set the data output rate to 60Hz (see Table II and Figure 5). If both 50Hz and 60Hz rejection is required, then the system CLK should be 3.840kHz; this will set the data output rate to 10Hz and reject both 50Hz and 60Hz (See Table II and Figure 6).

FIGURE 3. Normalized Digital Filter Response.

There is an additional benefit in using a lower data output rate. It will provide better rejection of signals in the frequency band of interest. For example, with a 50Hz data output rate, a significant signal at 75Hz may alias back into the passband at 25Hz. This is due to the fact that rejection at 75Hz may only be 66dB in the stopband (frequencies higher than the first notch frequency), as shown in Figure 4. However, setting the data output rate to 10Hz will provide 135dB rejection at 75Hz (see Figure 6). A similar benefit is gained at frequencies near the data output rate (see Figures 7, 8, 9, and 10). If a slower data output rate does not meet the system requirements, the analog front end can be designed to provide the needed attenuation to prevent aliasing. Additionally the data output rate may be increased and additional digital filtering may be done in the processor or controller.

#### CONTROL LOGIC

The control logic is used for communications and control of the ADS1250.

#### **Power-Up Sequence**

Prior to power-up, all digital and analog input pins must be LOW. At the time of power-up, these signal inputs can be biased to a voltage other than 0V, however, they should never exceed  $+V_S$  or  $+V_D$ .

Once the ADS1250 powers up, the  $\overline{DRDY}$  line will pulse LOW on the first conversion. This data will not be valid. The sixth pulse of  $\overline{DRDY}$  will be valid data from the analog input signal.

FIGURE 4. Digital Filter Response (50Hz).

FIGURE 5. Digital Filter Response (60Hz).

FIGURE 7. Expanded Digital Filter Response (50Hz with a 50Hz Notch).

FIGURE 9. Expanded Digital Filter Response (60Hz with a 60Hz Notch).

FIGURE 6. Digital Filter Response (10Hz Multiples).

FIGURE 8. Expanded Digital Filter Response (50Hz with a 10Hz Notch).

FIGURE 10. Expanded Digital Filter Response (60Hz with a 10Hz Notch).

ADS1250

11

#### **DSYNC**

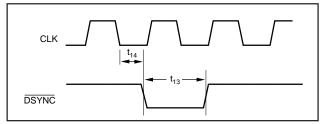

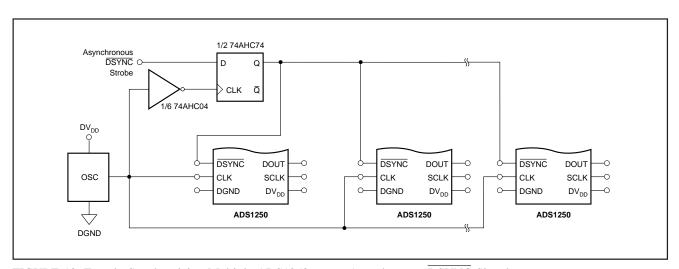

The DSYNC signal can be used is two ways. First, DSYNC can be used to synchronize multiple converters. This is done by applying a negative-going pulse on DSYNC. The negative pulse resets the current modulator count to zero and places it in a hold state. The modulator is released from the hold state and synchronization occurs on the rising edge of DSYNC. DSYNC does not reset the internal data to zero. Synchronization assumes that each ADS1250 is driven from the same system clock. If the DSYNC pulse is completely asynchronous to the master clock, some ADS1250s may start-up one CLK clock cycle before the others.

FIGURE 11. DSYNC to CLK Timing for Synchronizing Multiple ADS1250s.

Therefore, the output data will be synchronized, but only to within one CLK clock cycle. To ensure exact synchronization to the same CLK clock edge, the timing relationship between the  $\overline{DSYNC}$  and CLK signals must be observed, as shown in Figure 11 and Table III. Figure 12 shows a simple circuit which can be used to clock multiple ADS1250s from one ADS1250, as well as to ensure that an asynchronous  $\overline{DSYNC}$  signal will exactly synchronize all the converters.

The second use of  $\overline{DSYNC}$  is to reset the modulator count to zero in order to obtain valid data as quickly as possible. For example, if the analog input signal is changed significantly on the ADS1250, the current conversion cycle will be a mix of the old data and the new data. Five conversions are needed for the digital filter to settle. Therefore, the sixth conversion will be valid data. However, if the analog input signal is changed and then  $\overline{DSYNC}$  is used to reset the modulator count, the modulator data at the end of the current conversion cycle will be entirely from the new signal. After four additional conversion cycles, the output data will be completely valid. Note that the conversion cycle in which  $\overline{DSYNC}$  is used will be slightly longer than normal. Its length will depend on when  $\overline{DSYNC}$  was set.

FIGURE 12. Exactly Synchronizing Multiple ADS1250s to an Asynchronous DSYNC Signal.

| SYMBOL          | DESCRIPTION                                                                                                                                  | MIN | TYP | MAX                        | UNITS |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------------------------|-------|

| t <sub>1</sub>  | DOR Write Time (Using $\overline{\text{CS}}$ )                                                                                               |     |     | 6 • CLK                    | ns    |

| t <sub>2</sub>  | DRDY LOW Time                                                                                                                                |     |     | 6 • CLK                    | ns    |

| t <sub>3</sub>  | DOR Write Time (CS HIGH)                                                                                                                     |     |     | 6 • CLK                    | ns    |

| t <sub>4</sub>  | DRDY HIGH Time                                                                                                                               |     |     | 6 • CLK                    | ns    |

| t <sub>5</sub>  | Rising Edge of CLK to Falling Edge of DRDY                                                                                                   |     |     | 30                         | ns    |

| t <sub>6</sub>  | Falling Edge of DRDY to Falling Edge of CS                                                                                                   | 30  |     |                            | ns    |

| t <sub>7</sub>  | Falling Edge of CS to Rising Edge of DRDY                                                                                                    |     |     | 6 • CLK                    | ns    |

| t <sub>8</sub>  | Falling Edge of CS to Rising Edge of SCLK or                                                                                                 |     |     |                            |       |

|                 | Falling Edge of DRDY to Rising Edge of SCLK if CS is Tied LOW                                                                                | 30  |     |                            | ns    |

| t <sub>9</sub>  | Falling Edge of $\overline{CS}$ to DOUT Valid or Falling Edge of $\overline{DRDY}$ to DOUT Valid if $\overline{CS}$ is Tied LOW (Setup Time) |     |     | 30                         | 20    |

|                 | ,                                                                                                                                            | 5   |     | 30                         | ns    |

| t <sub>10</sub> | Falling Edge of SCLK to DOUT Valid (Hold Time)                                                                                               | 5   |     |                            | ns    |

| t <sub>11</sub> | Falling Edge of SCLK to Next DOUT Valid (Setup Time)                                                                                         |     |     | 30                         | ns    |

| t <sub>12</sub> | Rising Edge of CS to DOUT High Impedance                                                                                                     |     |     | 30                         | ns    |

| t <sub>13</sub> | DSYNC Pulse Width                                                                                                                            | 100 |     | CLK                        | ns    |

| t <sub>14</sub> | Falling Edge of CLK to Falling Edge of DSYNC                                                                                                 |     |     | $\frac{\text{CLK}}{2} - 5$ | ns    |

TABLE III. Digital Timing.

#### CS

The  $\overline{CS}$  signal controls the state of DOUT. If  $\overline{CS}$  is HIGH, DOUT is in a high-impedance state. When  $\overline{CS}$  is LOW, DOUT drives the bus.

#### **DRDY**

The  $\overline{DRDY}$  signal is used to indicate that new data has been loaded into the data output register and is ready to be read. The operation of  $\overline{DRDY}$  depends on how the  $\overline{CS}$  signal is used. The specifics of the three communications methods are described in the Serial Interface section.

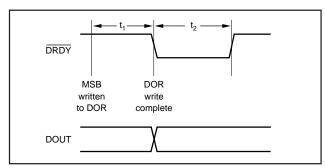

In the first case, which is typical for three-wire serial communications ( $\overline{CS}$  tied LOW),  $\overline{DRDY}$  would normally be HIGH. The result of the A/D conversion would be written to the DOR from MSB to LSB in the time defined by  $t_1$ . The  $\overline{DRDY}$  line would then pulse LOW for time defined by  $t_2$ , as shown in Figure 13.

FIGURE 13. DRDY Pulse (CS tied LOW).

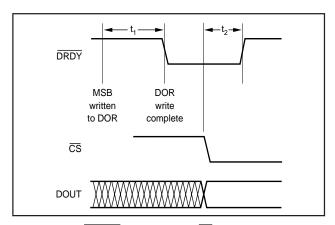

In the second case, which is typical for four-wire serial communications ( $\overline{CS}$  used),  $\overline{DRDY}$  would normally be HIGH. The result of the A/D conversion would be written to the DOR from MSB to LSB in the time defined by  $t_1$ . The  $\overline{DRDY}$  would go LOW after the DOR write is completed. After taking  $\overline{CS}$  LOW, the  $\overline{DRDY}$  line would remain LOW for the time defined by  $t_2$ , as shown in Figure 14.

FIGURE 14. DRDY Pulse (using CS).

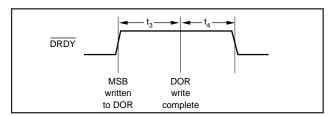

In the third case,  $\overline{CS}$  is left HIGH, which may be used if data is only periodically read from the ADS1250. In this case,  $\overline{DRDY}$  would normally be LOW.  $\overline{DRDY}$  would go HIGH immediately prior to the MSB being written to the DOR. The result of the A/D conversion would be written from

MSB to LSB in the time defined by  $t_3$ . The  $\overline{DRDY}$  line would stay HIGH for the time defined by  $t_4$ , as shown in Figure 15.

FIGURE 15. DRDY Pulse (CS HIGH).

Reading  $\overline{DRDY}$  during the time shown by  $t_1$  and  $t_3$  (Figures 13, 14, and 15) will result in invalid data being read. This is due to the fact that writes to the DOR are not blocked. Subsequently, a read from DOR during this time will result in a combination of old and new data.

#### **SERIAL INTERFACE**

The ADS1250 includes a simple serial interface which can be connected to microcontrollers and digital signal processors in a variety of ways. Communications with the ADS1250 can commence on the first detection of the  $\overline{DRDY}$  pulse after power up, although data will not be valid until the sixth conversion.

It is important to note that the data from the ADS1250 is a 20-bit result transmitted MSB-first in Binary Two's Complement format, as shown in Table IV.

| DIFFERENTIAL VOLTAGE INPUT | DIGITAL OUTPUT (HEX) |  |

|----------------------------|----------------------|--|

| +Full Scale                | 7FFFFH               |  |

| Zero                       | 00000H               |  |

| -Full Scale                | 80000H               |  |

TABLE IV. ADS1250 Data Format (Binary Two's Complement).

The entire 20-bit result can be read out of the device by simply providing 20 SCLKs during serial communication with the part. However, the most common method of communicating with the device is with a standard SSI interface, such as SPI. This protocol is based on 8-bit or 16-bit data transfers. It is possible to use a standard 8-bit or 16-bit data transfer with the ADS1250. For instance, if only 16 bits of data are read, the internal bit pointer will automatically reset to the MSB of the DOR on the next  $\overline{\text{DRDY}}$  pulse. This will ensure that the next read from the DOR will begin with the MSB of newly converted data. If more than 20 bits of data are read, the data will be 0 padded. Therefore, if 24 bits of data are read from the ADS1250, the lowest four bits of the 24-bit data transfer are read as 0s (0 padded).

The only limitation on SCLK is that it cannot be higher than 9.6MHz. Therefore, it is possible to run CLK at a lower frequency than SCLK. For instance, it is possible to run CLK at 23.040kHz for a 60Hz notch, and run SCLK at 9.6MHz to achieve high-speed serial communications. Additionally, the data must be clocked out before the next  $\overline{DRDY}$  to ensure valid data, as described in the  $\overline{DRDY}$  section.

There are three basic methods of receiving data from the ADS1250. The first two methods involve a four-wire interface and the third method is a three-wire interface.

#### Method 1: Four-Wire Interface

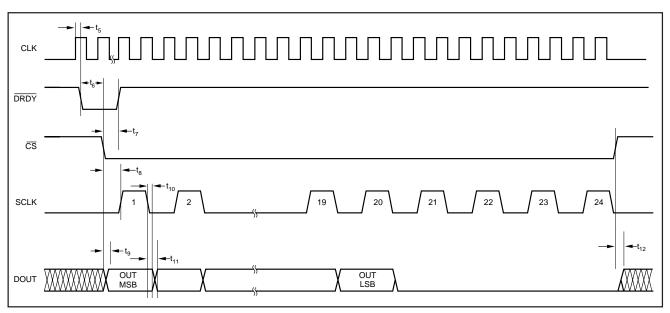

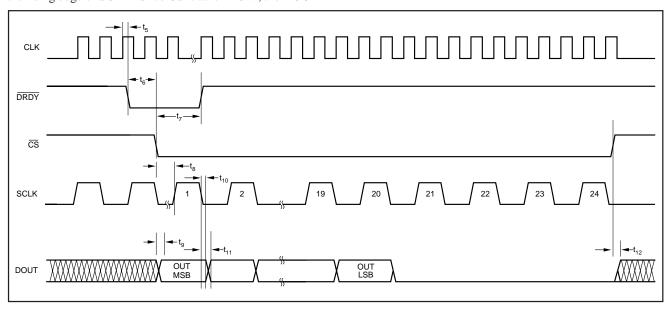

The most common method of receiving data is <u>using</u> a simple four-wire interface ( $\overline{CS}$ , SCLK, DOUT, and  $\overline{DRDY}$ ). The  $\overline{DRDY}$  line will pulse LOW after the DOR is updated. The processor would then take  $\overline{CS}$  LOW to select the device for communication. Once  $\overline{CS}$  is taken LOW, the DOUT would be driven to the level dictated by the MSB of the data

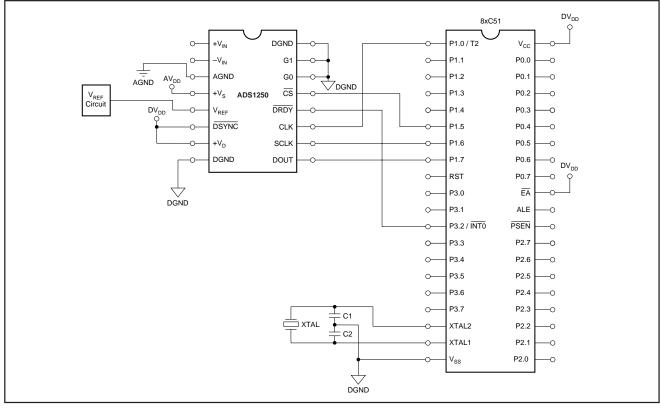

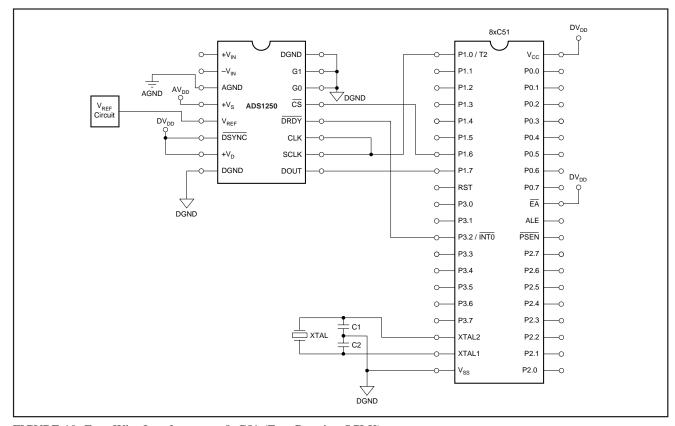

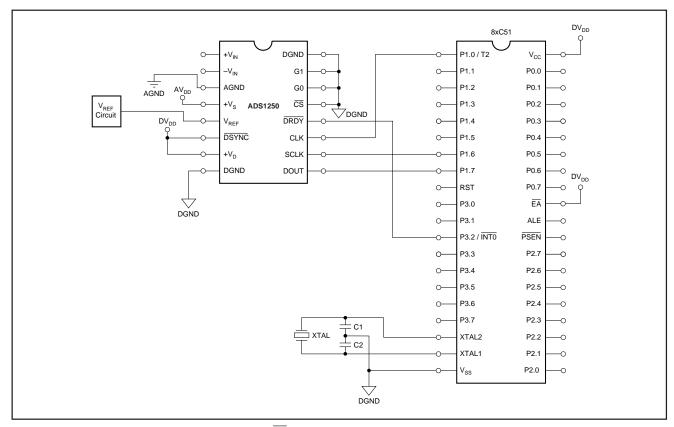

output register. The processor would provide 20 (or 24) SCLKs to read the contents of the DOR. The data bits in the DOR are shifted out on the DOUT pin after the falling edge of SCLK. If more than 20 bits of data are read, the data is 0 padded. Taking  $\overline{\text{CS}}$  HIGH will take DOUT to a high-impedance state. The timing for the data transfer is shown in Figure 16 (see Table III). A simple four-wire interface using this method is shown in Figure 17. The P1.0 output from the 8xC51 is a free-running clock.

FIGURE 16. Method 1: Four-Wire Interface Using Noncontinuous SCLK.

FIGURE 17. Four-Wire Interface to an 8xC51.

#### Method 2: Four-Wire Interface

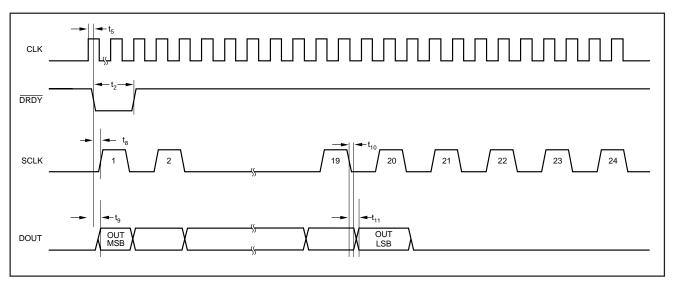

The second method of receiving data also uses a simple four-wire interface ( $\overline{CS}$ , SCLK, DOUT, and  $\overline{DRDY}$ ). The main difference from method 1 is that SCLK is a freerunning clock. The  $\overline{DRDY}$  line will pulse LOW for the time defined by  $\underline{t_2}$  after the DOR is updated. The processor would then take  $\overline{CS}$  LOW to select the device for communication. The recommended method of using  $\overline{CS}$  is to take  $\overline{CS}$  LOW on the falling edge of SCLK. The only timing constraint of  $\overline{CS}$  is that the setup time ( $\underline{t_9}$ ) for the data must be met before the rising edge of SCLK. Once  $\overline{CS}$  is taken LOW, the DOUT

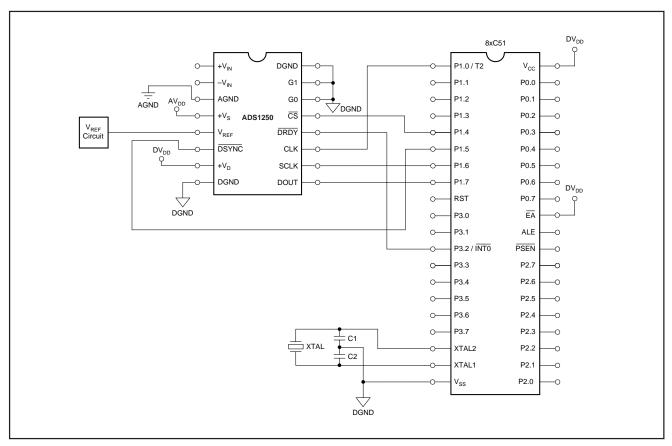

would be driven to the level dictated by the MSB of the data output register.  $\overline{CS}$  would be held low for 20 (or 24) SCLKs to read the contents of the DOR. The data bits in the DOR are shifted out on the DOUT pin after the falling edge of SCLK. If  $\overline{CS}$  is held low for more than 20 SCLKs, the data would be 0 padded. Taking  $\overline{CS}$  HIGH will take DOUT to a high-impedance state. The timing for the data transfer is shown in Figure 18 (see Table III). A simple four-wire interface is shown in Figure 19. The P1.0 output from the 8xC51 is a free-running clock.

FIGURE 18. Method 2: Four-Wire Interface Using a Free-Running SCLK.

FIGURE 19. Four-Wire Interface to an 8xC51 (Free-Running SCLK).

#### Method 3: Three-Wire Interface

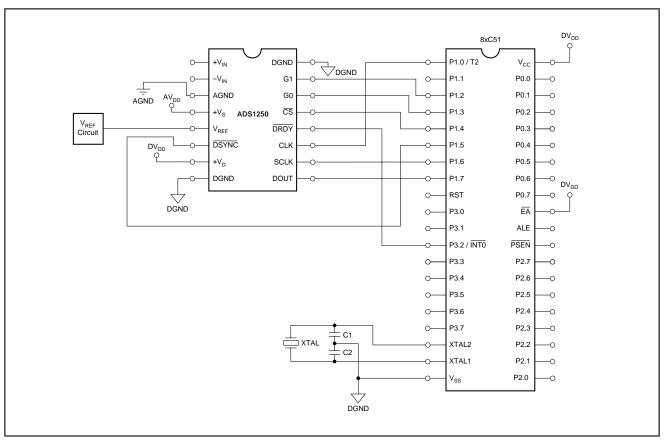

The third method of receiving data uses a simple three-wire interface (SCLK, DOUT, and  $\overline{DRDY}$ ). The main difference from method 1 is that  $\overline{CS}$  is tied LOW, therefore, the DOUT pin is always driving the bus. The  $\overline{DRDY}$  line will pulse LOW after the DOR is updated. Since  $\overline{CS}$  is tied LOW (the DOUT pin is enabled for output), the level dictated by the MSB of the data output register would be driven on the bus. The processor would provide 20 (or 24) SCLKs to read the contents of the DOR. The data bits in the DOR are shifted out on the DOUT pin after the falling edge of SCLK. If more

than 20 bits of data are read, the data is 0 padded. Since  $\overline{\text{CS}}$  is tied LOW, the bus will be driven to the state of the last bit that was shifted out of the DOR. The timing for the data transfer is shown in Figure 20 (see Table III). A simple three-wire interface using this method is shown in Figure 21. The P1.0 output from the 8xC51 is a free-running clock.

Figure 22 shows a five-wire interface using  $\overline{DSYNC}$ . The communication with the ADS1250 is the same as described in Method 1. Figure 23 shows a full interface using  $\overline{DSYNC}$ , G1, and G0. The communication with ADS1250 is the same as described in Method 1.

FIGURE 20. Method 3: Two-Wire Interface ( $\overline{\text{CS}}$  tied LOW).

FIGURE 21. Three-Wire Interface to an 8xC51 (CS tied LOW).

FIGURE 22. Five-Wire Interface to an 8xC51.

17

FIGURE 23. Full Interface to an 8xC51.

#### **SOFTWARE GAIN**

The excellent performance, flexibility, and low cost of the ADS1250 allows the converter to be considered for designs which would not normally need a 20-bit ADC. For example, many designs utilize a 12-bit converter and a high gain INA or PGA for digitizing low amplitude signals. For some of these applications, the ADS1250 by itself may be a solution. The digital result of the converter can simply be shifted up by "n" bits in the main controller, resulting in a gain of "n" times G, where G is the gain setting. While this type of manipulation of the output data is obvious, it is easy to miss how much the gain can be increased in this manner on a 20-bit converter. For

example, shifting the result by 4 bits when the ADS1250 is set to a gain of 8 results in an effective gain of 128.

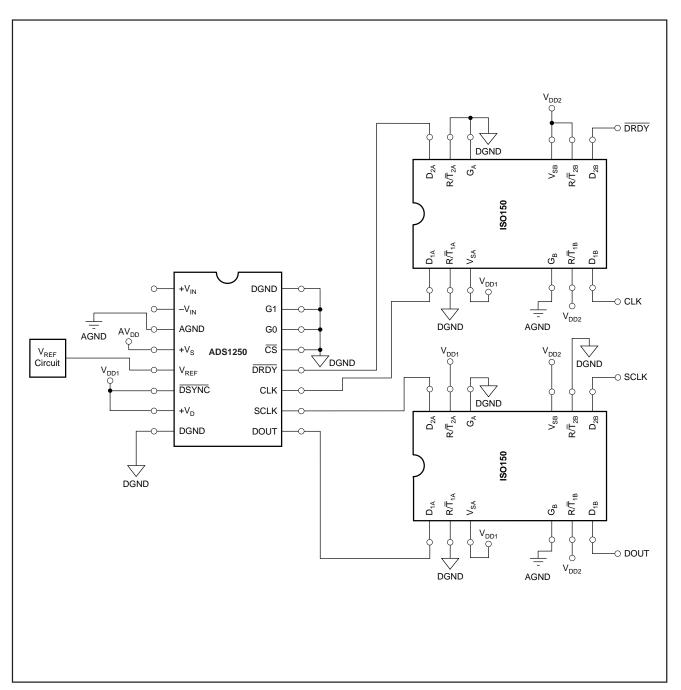

#### Isolation

The serial interface of the ADS1250 provides for simple isolation methods. An example of an isolated four-wire interface is shown in Figure 19. The ISO150 is used to transmit the digital clocks over the isolation barrier. In addition, the digital output of the ADS1250 can, in some cases, drive opto-isolators directly. Note that DOUT is tristated for the majority of the conversion period and the opto-isolator connection must take this into account.

FIGURE 24. Isolated Four-Wire Interface.

# **LAYOUT**

#### **POWER SUPPLIES**

The analog supply should be well regulated and low noise. For designs requiring very high resolution from the ADS1250, power supply rejection will be a concern. Avoid running digital lines under the device as they may couple noise onto the die. The requirements for the digital supply are not as strict, however, high frequency noise on V<sub>D</sub> can capacitively couple into the analog portion of the ADS1250. This noise can originate from switching power supplies, very fast microprocessors, or digital signal processors. For either supply, high frequency noise will alias back into the passband of the digital filter, affecting the conversion result. If one supply must be used to power the ADS1250, the V<sub>S</sub> supply should be used to power V<sub>D</sub>. This connection can be made via a  $10\Omega$  resistor which, along with the decoupling capacitors, will provide some filtering between V<sub>D</sub> and V<sub>S</sub>. In some systems, a direct connection can be made. Experimentation may be the best way to determine the appropriate connection between  $V_S$  and  $V_D$ .

#### **GROUNDING**

The analog and digital sections of the design should be carefully and cleanly partitioned. Each section should have its own ground plane with no overlap between them. AGND should be connected to the analog ground plane as well as all other analog grounds. DGND should be connected to the digital ground plane and all digital signals referenced to this plane. The ADS1250 pinout is such that the converter is cleanly separated into an analog and digital portion. This should allow simple layout of the analog and digital sections of the design. For a single converter system, AGND and DGND of the ADS1250 should be connected together, underneath the converter. Do not join the ground planes, but connect the two with a moderate signal trace. For multiple converters, connect the two ground planes at one location as central to all of the converters as possible. In some cases, experimentation may be required to find the best point to connect the two planes together. The printed circuit board can be designed to provide different analog/digital ground connections via short jumpers. The initial prototype can be used to establish which connection works best.

#### **DECOUPLING**

Good decoupling practices should be used for the ADS1250 and for all components in the design. All decoupling capacitors, but specifically the  $0.1\mu F$  ceramic capacitors, should be placed as close as possible to the pin being decoupled. A  $1\mu F$  to  $10\mu F$  capacitor, in parallel with a  $0.1\mu F$  ceramic capacitor, should be used to decouple  $V_S$  to AGND. At a minimum, a  $0.1\mu F$  ceramic capacitor should be used to decouple  $V_D$  to DGND, as well as for the digital supply on each digital component.

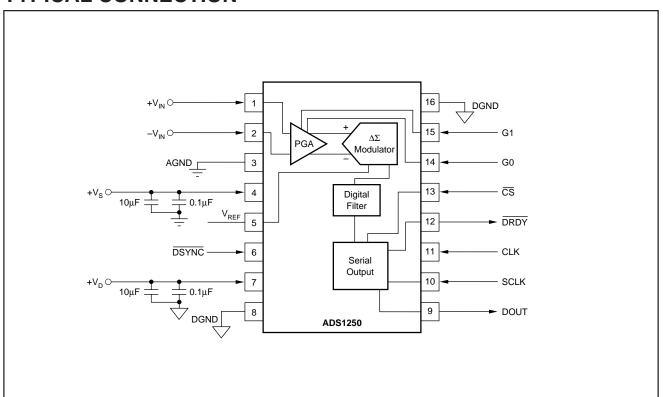

# TYPICAL CONNECTION

FIGURE 25. Connection Diagram.

# SYSTEM CONSIDERATIONS

The recommendations for power supplies and grounding will change depending on the requirements and specific design of the overall system. Achieving 20 bits noise performance is a great deal more difficult than achieving 12 bits of noise performance. In general, a system can be broken up into four different stages:

- · Analog Processing

- Analog Portion of the ADS1250

- Digital Portion of the ADS1250

- · Digital Processing

For the simplest system consisting of minimal analog signal processing (basic filtering and gain), a microcontroller, and one clock source, high resolution can be achieved by powering all components by a common power supply. In addition, all components can share a common ground plane. Thus, there would be no distinctions between "analog" or "digital" power and ground. The layout should still include a power plane, a ground plane, and careful decoupling. In a more extreme case, the design could include: multiple ADS1250s; extensive analog signal processing; one or more microcontrollers, digital signal processors, or microprocessors; many different clock sources; and interconnections to various other systems. High resolution will be very difficult to achieve for this design. The approach would be to break the system into as many different parts as possible. For example, each ADS1250 may have its own "analog" processing front end, its own analog power and ground (possibly shared with the analog front end), and its own "digital" power and ground. The converter's "digital" power and ground would be separate from the power and ground for the system's processors, RAM, ROM, and "glue" logic.

#### **DEFINITION OF TERMS**

An attempt has been made to be consistent with the terminology used in this data sheet. In that regard, the definition of each term is given as follows:

**Analog Input Differential Voltage**—For an analog signal that is fully differential, the voltage range can be compared to that of an instrumentation amplifier. For example, if both

analog inputs of the ADS1250 are at 2.048V, the differential voltage is 0V. If one input is at 0V and the other is at 4.096V, the differential voltage magnitude is 4.096V. This is the case regardless of which input is at 0V and which is at 4.096V. The analog input differential voltage is given by the following equation:

$$+V_{IN}--V_{IN} \\$$

A positive digital output is produced whenever the analog input differential voltage is positive, while a negative digital output is produced whenever the differential is negative. For example, with a 4.096V reference and a gain setting of 2, a positive full-scale output is produced when the analog input differential is 2.048V. A negative full-scale output is produced when the differential voltage is -2.048V. In each case, the actual input voltages must remain within the AGND to  $V_S$  range (see Table I).

**Actual Analog Input Voltage**—The voltage at any one analog input relative to AGND.

**Full-Scale Range (FSR)**—As with most A/D converters, the full-scale range of the ADS1250 is defined as the "input" which produces the positive full-scale digital output minus the "input" which produces the negative full-scale digital output. For example, with a 4.096V reference and a gain setting of 2, the differential full-scale range is 2.048V - (-2.048V) = 4.096V.

**Least Significant Bit (LSB) Weight**—This is the theoretical amount of voltage that the differential voltage at the analog input would have to change in order to observe a change in the output data of one least significant bit. It is computed as follows:

$$LSB Weight = \frac{Full - Scale Range}{2^{N}}$$

where N is the number of bits in the digital output.

**Conversion Cycle**—The term conversion cycle, as used here, refers to the time period between  $\overline{DRDY}$  pulses.