For most current data sheet and other product information, visit www.burr-brown.com

# Dual 500kHz, 12-Bit, 2 + 2 Channel Simultaneous Sampling ANALOG-TO-DIGITAL CONVERTER

## **FEATURES**

- 4 INPUT CHANNELS

- FULLY DIFFERENTIAL INPUTS

- 2µs TOTAL THROUGHPUT PER CHANNEL

- GUARANTEED NO MISSING CODES

- PARALLEL INTERFACE

- 1MHz EFFECTIVE SAMPLING RATE

- LOW POWER: 40mW

## **APPLICATIONS**

- MOTOR CONTROL

- MULTI-AXIS POSITIONING SYSTEMS

- 3-PHASE POWER CONTROL

## DESCRIPTION

The ADS7862 is a dual 12-bit, 500kHz analog-to-digital converter (A/D) with 4 fully differential input channels grouped into two pairs for high speed simultaneous signal acquisition. Inputs to the sample-and-hold amplifiers are fully differential and are maintained differential to the input of the A/D converter. This provides excellent common-mode rejection of 80dB at 50kHz which is important in high noise environments.

The ADS7862 offers parallel interface and control inputs to minimize software overhead. The output data for each channel is available as a 12-bit word. The ADS7862 is offered in an TQFP-32 package and is full specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C operating range.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

All specifications  $T_{MIN}$  to  $T_{MAX}$ ,  $+V_A = +V_D = +5V$ ,  $V_{REF} = internal +2.5V$  and  $f_{CLK} = 8MHz$ ,  $f_{SAMPLE} = 500kHz$ , unless otherwise noted.

|                                    |                                                           | ADS7862Y          |       | ADS7862YB              |        | ]    |         |          |

|------------------------------------|-----------------------------------------------------------|-------------------|-------|------------------------|--------|------|---------|----------|

| PARAMETER                          | CONDITIONS                                                | MIN               | TYP   | MAX                    | MIN    | TYP  | MAX     | UNITS    |

| RESOLUTION                         |                                                           |                   |       | 12                     |        |      | *       | Bits     |

| ANALOG INPUT                       |                                                           |                   |       |                        |        |      |         |          |

| Input Voltage Range-Bipolar        | V <sub>CENTER</sub> = Internal V <sub>REF</sub> at 2.5V   | -V <sub>REF</sub> |       | +V <sub>REF</sub>      | *      |      | *       | V        |

| Absolute Input Range               | +IN                                                       | -0.3              |       | V <sub>CC</sub> + 0.3  |        |      |         | V        |

|                                    | -IN                                                       | -0.3              |       | V <sub>CC</sub> + 0.3  |        |      |         | V        |

| Input Capacitance                  |                                                           |                   | 15    |                        |        | *    |         | pF       |

| Input Leakage Current              | CLK = GND                                                 |                   | ±1    |                        |        | *    |         | μA       |

| SYSTEM PERFORMANCE                 |                                                           |                   |       |                        |        |      |         |          |

| No Missing Codes                   |                                                           | 12                |       |                        | *      |      |         | Bits     |

| Integral Linearity                 |                                                           | '-                | ±0.75 | ±2                     | ,      | ±0.5 | ±1      | LSB      |

| Integral Linearity Match           |                                                           |                   | 0.5   | 1                      |        | ±0.5 | ±1<br>* | LSB      |

| ,                                  |                                                           |                   | 1     | '                      |        |      |         | 1        |

| Differential Linearity             | Defended to DEE                                           |                   | ±0.75 |                        |        | ±0.5 | ±1      | LSB      |

| Bipolar Offset Error               | Referenced to REF <sub>IN</sub>                           |                   | ±0.75 | ±3                     |        | ±0.5 | ±2      | LSB      |

| Bipolar Offset Error Match         | D ( ) ( DEE                                               |                   | .0.45 | 3                      |        |      | 2       | LSB      |

| Positive Gain Error                | Referenced to REF <sub>IN</sub>                           |                   | ±0.15 | ±0.75                  |        | ±0.1 | ±0.5    | % of FSR |

| Positive Gain Error Match          |                                                           |                   |       | 2                      |        |      | 1       | LSB      |

| Negative Gain Error                | Referenced to REF <sub>IN</sub>                           |                   | ±0.15 | ±0.75                  |        | ±0.1 | ±0.5    | % of FSR |

| Negative Gain Error Match          |                                                           |                   |       | 2                      |        |      | 1       | LSB      |

| Common-Mode Rejection Ratio        | At DC                                                     |                   | 80    |                        |        | *    |         | dB       |

|                                    | $V_{IN} = \pm 1.25 Vp-p$ at $50 kHz$                      |                   | 80    |                        |        | *    |         | dB       |

| Noise                              |                                                           |                   | 120   |                        |        | *    |         | μVrms    |

| Power Supply Rejection Ratio       |                                                           |                   | ±0.5  | ±2                     |        | *    | *       | LSB      |

| SAMPLING DYNAMICS                  |                                                           |                   |       |                        |        |      |         |          |

| Conversion Time per A/D            |                                                           |                   | 1.75  |                        |        | *    |         |          |

| Acquisition Time                   |                                                           |                   | 0.25  |                        |        | *    |         | μs       |

| •                                  |                                                           | 500               | 0.25  |                        | *      |      |         | μs       |

| Throughput Rate                    |                                                           | 500               | 0.5   |                        | *      | .,   |         | kHz      |

| Aperture Delay                     |                                                           |                   | 3.5   |                        |        | *    |         | ns       |

| Aperture Delay Matching            |                                                           |                   | 100   |                        |        | *    |         | ps       |

| Aperture Jitter                    |                                                           |                   | 50    |                        |        | *    |         | ps       |

| Small-Signal Bandwidth             |                                                           |                   | 40    |                        |        | *    |         | MHz      |

| DYNAMIC CHARACTERISTICS            |                                                           |                   |       |                        |        |      |         |          |

| Total Harmonic Distortion          | $V_{IN} = \pm 2.5 Vp-p \text{ at } 100 kHz$               |                   | 75    |                        |        | *    |         | dB       |

| SINAD                              | $V_{IN} = \pm 2.5 \text{Vp-p at } 100 \text{kHz}$         |                   | 71    |                        |        | *    |         | dB       |

| Spurious Free Dynamic Range        | V <sub>IN</sub> = ±2.5Vp-p at 100kHz                      |                   | -78   |                        |        | *    |         | dB       |

| Channel-to-Channel Isolation       | $V_{IN} = \pm 2.5 \text{Vp-p} \text{ at } 100 \text{kHz}$ |                   |       | -80                    |        |      | *       | dB       |

| VOLTAGE REFERENCE                  | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                     |                   |       |                        |        |      |         | -        |

|                                    |                                                           | 0.475             | 0.5   | 0.505                  |        |      |         | l ,,     |

| Internal                           |                                                           | 2.475             | 2.5   | 2.525                  | *      | *    | *       | V        |

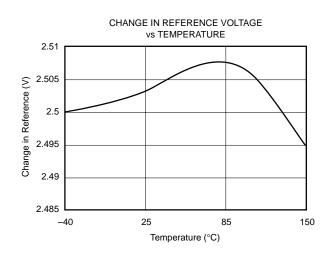

| Internal Drift                     |                                                           |                   | ±25   |                        |        | *    |         | ppm/°C   |

| Internal Noise                     |                                                           |                   | 50    |                        |        | *    |         | μVр-р    |

| Internal Source Current            |                                                           |                   | 2     |                        |        | *    |         | mA       |

| Internal Load Rejection            |                                                           |                   | 0.005 |                        |        | *    |         | mV/μA    |

| Internal PSRR                      |                                                           |                   | 65    |                        |        | *    |         | dB       |

| External Voltage Range             |                                                           | 1.2               | 2.5   | 2.6                    | *      | *    | *       | V        |

| Input Current                      |                                                           |                   | 0.05  | 1                      |        | *    | *       | μΑ       |

| Input Capacitance                  |                                                           |                   | 5     |                        |        | *    |         | pF       |

| DIGITAL INPUT/OUTPUT               |                                                           |                   |       |                        |        |      |         | 1        |

| Logic Family                       |                                                           |                   | CMOS  |                        |        | *    |         |          |

| Logic Levels: V <sub>IH</sub>      | I <sub>IH</sub> = +5μA                                    | 3.0               | 0.000 | +V <sub>DD</sub> + 0.3 | *      | "    | *       | V        |

| =                                  |                                                           | -0.3              |       | 0.8                    | *<br>* |      | *       | V V      |

| V <sub>IL</sub>                    | I <sub>IL</sub> = +5μA                                    |                   |       | 0.0                    |        |      | 不       | l v      |

| V <sub>OH</sub>                    | I <sub>OH</sub> = -500μA                                  | 3.5               |       | 04                     | *      |      |         | 1        |

| V <sub>OL</sub>                    | I <sub>OL</sub> = 500μA                                   | 0.0               |       | 0.4                    | .,     |      | *       | V NALI-  |

| External Clock                     |                                                           | 0.2               | <br>  | 8                      | *      |      | *       | MHz      |

| Data Format                        |                                                           | Binary Two's      |       | mplement               |        | *    |         |          |

| POWER SUPPLY REQUIREMENTS          |                                                           |                   |       |                        |        |      |         |          |

| Power Supply Voltage, +V           |                                                           | 4.75              | 5     | 5.25                   | *      | *    | *       | V        |

| Quiescent Current, +V <sub>A</sub> |                                                           |                   | 5     | 8                      |        | *    | *       | mA       |

| Power Dissipation                  |                                                           |                   | 25    | 40                     |        | *    | *       | mW       |

| I                                  | I                                                         | I                 | 1     |                        |        | 1    |         | 1        |

<sup>\*</sup> Specifications same as ADS7862Y.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

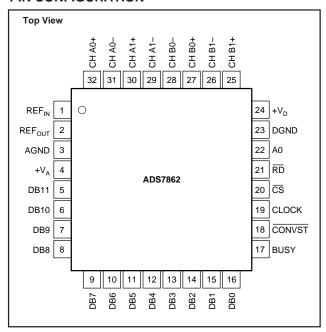

#### **PIN CONFIGURATION**

#### **ABSOLUTE MAXIMUM RATINGS**

|   | Analog Inputs to AGND: Any Channel Input $-0.3V$ to $(+V_D + 0.3V)$ REF <sub>IN</sub> $-0.3V$ to $(+V_D + 0.3V)$ |

|---|------------------------------------------------------------------------------------------------------------------|

| ı | Digital Inputs to DGND $-0.3V$ to $(+V_D + 0.3V)$                                                                |

| ı | Ground Voltage Differences: AGND, DGND ±0.3V                                                                     |

| ı | +V <sub>D</sub> to AGND0.3V to +6V                                                                               |

| ı | Power Dissipation                                                                                                |

| ı | Maximum Junction Temperature+150°C                                                                               |

| ı | Operating Temperature Range40°C to +85°C                                                                         |

| ı | Storage Temperature Range65°C to +150°C                                                                          |

| ı | Lead Temperature (soldering, 10s) +300°C                                                                         |

|   |                                                                                                                  |

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **PIN DESCRIPTIONS**

| PIN | NAME               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | REF <sub>IN</sub>  | Reference Input                                                                                                                                                                                                                                                                                                                                               |

| 2   | REF <sub>OUT</sub> | +2.5V Reference Output. Connect directly to REF $_{\rm IN}$ (pin 1) when using internal reference.                                                                                                                                                                                                                                                            |

| 3   | AGND               | Analog Ground                                                                                                                                                                                                                                                                                                                                                 |

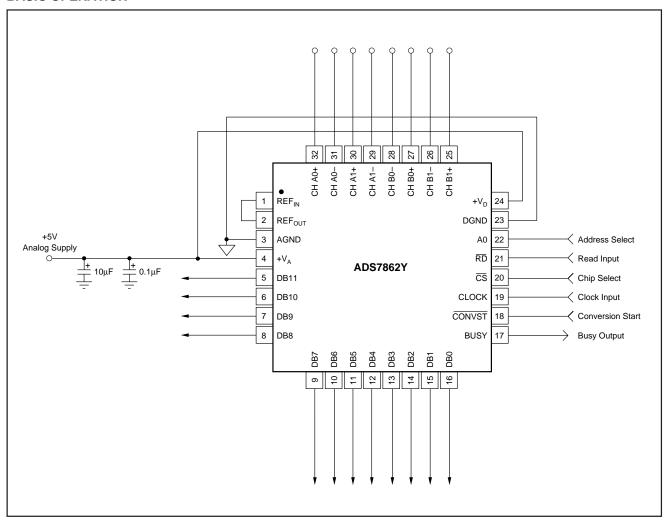

| 4   | +V <sub>A</sub>    | Analog Power Supply, +5VDC. Connect directly to digital power supply (pin 24). Decouple to analog ground with a $0.1\mu F$ ceramic capacitor and a $10\mu F$ tantalum capacitor.                                                                                                                                                                              |

| 5   | DB11               | Data Bit 11, MSB                                                                                                                                                                                                                                                                                                                                              |

| 6   | DB10               | Data Bit 10                                                                                                                                                                                                                                                                                                                                                   |

| 7   | DB9                | Data Bit 9                                                                                                                                                                                                                                                                                                                                                    |

| 8   | DB8                | Data Bit 8                                                                                                                                                                                                                                                                                                                                                    |

| 9   | DB7                | Data Bit 7                                                                                                                                                                                                                                                                                                                                                    |

| 10  | DB6                | Data Bit 6                                                                                                                                                                                                                                                                                                                                                    |

| 11  | DB5                | Data Bit 5                                                                                                                                                                                                                                                                                                                                                    |

| 12  | DB4                | Data Bit 4                                                                                                                                                                                                                                                                                                                                                    |

| 13  | DB3                | Data Bit 3                                                                                                                                                                                                                                                                                                                                                    |

| 14  | DB2                | Data Bit 2                                                                                                                                                                                                                                                                                                                                                    |

| 15  | DB1                | Data Bit 1                                                                                                                                                                                                                                                                                                                                                    |

| 16  | DB0                | Data Bit 0, LSB                                                                                                                                                                                                                                                                                                                                               |

| 17  | BUSY               | HIGH when a conversion is in progress.                                                                                                                                                                                                                                                                                                                        |

| 18  | CONVST             | Convert Start                                                                                                                                                                                                                                                                                                                                                 |

| 19  | CLOCK              | An external CMOS-compatible clock can be applied to the CLOCK input to synchronize the conversion process to an external source. The CLOCK pin controls the sampling rate by the equation: CLOCK 16 • f <sub>SAMPLE</sub> .                                                                                                                                   |

| 20  | cs                 | Chip Select                                                                                                                                                                                                                                                                                                                                                   |

| 21  | RD                 | Synchronization pulse for the parallel output. During a Read operation, the first falling edge selects the A register and the second edge selects the B register, A0, then controls whether input 0 or input 1 is read.                                                                                                                                       |

| 22  | A0                 | On the falling edge of Convert Start, when A0 is LOW Channel A0 and Channel B0 are converted and when it is HIGH, Channel A1 and Channel B1 are converted. During a Read operation, the first falling edge selects the A register and the second edge selects the B of $\overline{\text{RD}}$ register, A0, then controls whether input 0 or input 1 is read. |

| 23  | DGND               | Digital Ground. Connect directly to analog ground (pin 3).                                                                                                                                                                                                                                                                                                    |

| 24  | +V <sub>D</sub>    | Digital Power Supply, +5VDC                                                                                                                                                                                                                                                                                                                                   |

| 25  | CH B1+             | Non-Inverting Input Channel B1                                                                                                                                                                                                                                                                                                                                |

| 26  | CH B1-             | Inverting Input Channel B1                                                                                                                                                                                                                                                                                                                                    |

| 27  | CH B0+             | Non-Inverting Input Channel B0                                                                                                                                                                                                                                                                                                                                |

| 28  | CH B0-             | Inverting Input Channel B0                                                                                                                                                                                                                                                                                                                                    |

| 29  | CH A1-             | Inverting Input Channel A1                                                                                                                                                                                                                                                                                                                                    |

| 30  | CH A1+             | Non-Inverting Input Channel A1                                                                                                                                                                                                                                                                                                                                |

| 31  | CH A0-             | Inverting Input Channel A0                                                                                                                                                                                                                                                                                                                                    |

| 32  | CH A0+             | Non-Inverting Input Channel A0                                                                                                                                                                                                                                                                                                                                |

#### PACKAGE/ORDERING INFORMATION

| PRODUCT                                        | MAXIMUM<br>RELATIVE<br>ACCURACY<br>(LSB) | MAXIMUM<br>GAIN<br>ERROR<br>(%) | PACKAGE            | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | SPECIFICATION<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING <sup>(2)</sup> | ORDERING<br>NUMBER <sup>(3)</sup>                              | TRANSPORT<br>MEDIA |

|------------------------------------------------|------------------------------------------|---------------------------------|--------------------|---------------------------------------------|---------------------------------------|-----------------------------------|----------------------------------------------------------------|--------------------|

| ADS7862Y<br>ADS7862Y<br>ADS7862YB<br>ADS7862YB | ±2<br>=<br>±1<br>=                       | ±0.75<br>"<br>±0.5              | TQFP-32<br>TQFP-32 | 351<br>"<br>351<br>"                        | -40°C to +85°C<br>-40°C to +85°C      | A62<br>A62                        | ADS7862Y/250<br>ADS7862Y/2K5<br>ADS7862YB/250<br>ADS7862YB/2K5 |                    |

NOTE: (1) For detail drawing and dimension table, please see end of data sheet or Package Drawing File on Web. (2) Performance Grade information is marked on the reel. (3) Models with a slash(/) are available only in Tape and reel in quantities indicated (e.g. /250 indicates 250 units per reel, /2K5 indicates 2500 devices per reel). Ordering 2500 pieces of "ADS7862Y/2K5" will get a single 2500-piece Tape and Reel. For detailed Tape and Reel mechanical information, refer to the www.burr-brown.com web site under Applications and Tape and Reel Orientation and Dimensions.

#### **BASIC OPERATION**

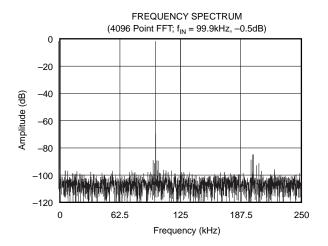

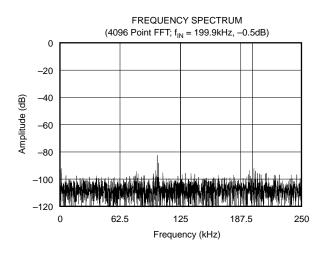

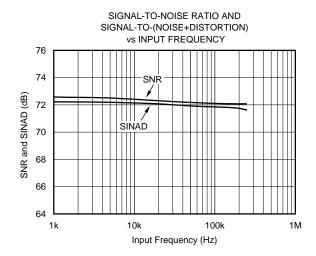

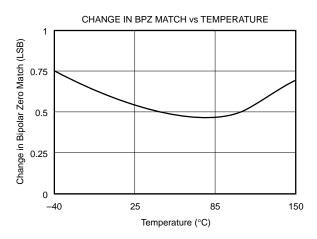

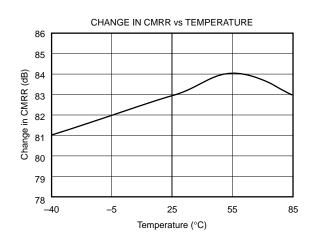

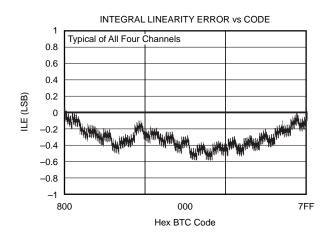

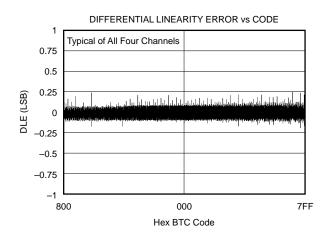

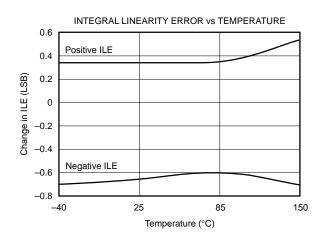

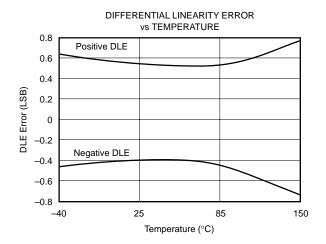

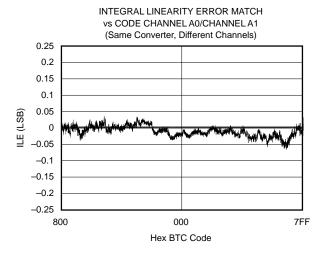

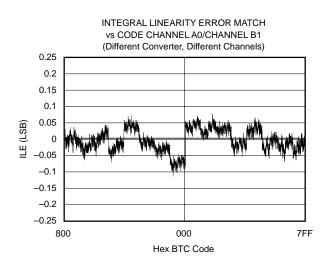

# TYPICAL PERFORMANCE CURVES

At  $T_A = +25^{\circ}C$ ,  $+V_A = +V_D = +5V$ ,  $V_{REF} = internal +2.5V$  and  $f_{CLK} = 8MHz$ ,  $f_{SAMPLE} = 500kHz$ , unless otherwise noted.

5

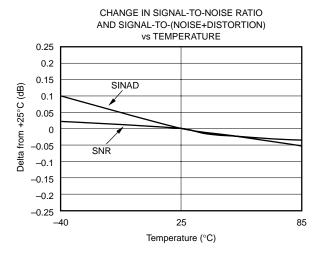

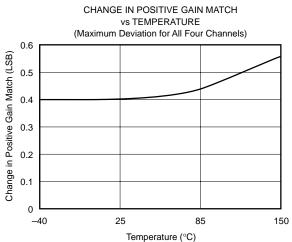

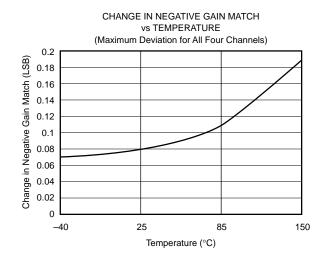

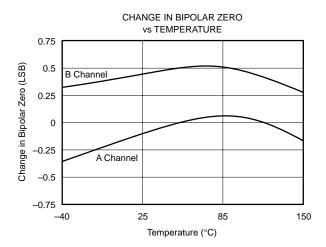

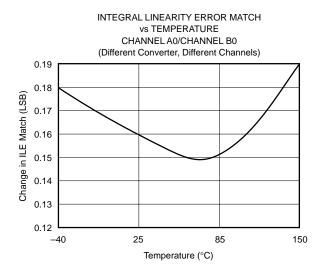

# **TYPICAL PERFORMANCE CURVES (Cont.)**

At  $T_A = +25^{\circ}C$ ,  $+V_A = +V_D = +5V$ ,  $V_{REF} = internal +2.5V$  and  $f_{CLK} = 8MHz$ ,  $f_{SAMPLE} = 500kHz$ , unless otherwise noted.

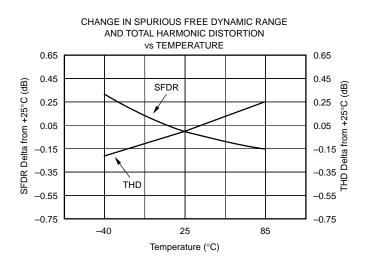

# TYPICAL PERFORMANCE CURVES (Cont.)

At  $T_A = +25^{\circ}C$ ,  $+V_A = +V_D = +5V$ ,  $V_{REF} = internal +2.5V$  and  $f_{CLK} = 8MHz$ ,  $f_{SAMPLE} = 500kHz$ , unless otherwise noted.

7

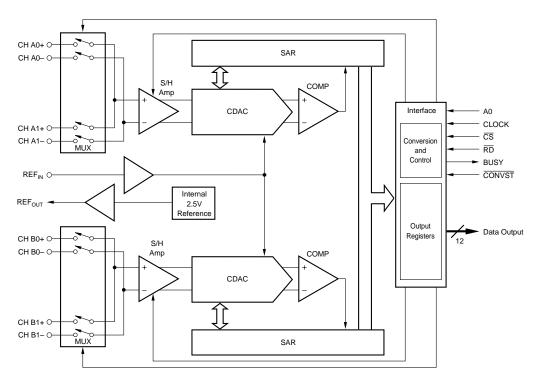

# INTRODUCTION

The ADS7862 is a high speed, low power, dual 12-bit A/D converter that operates from a single +5V supply. The input channels are fully differential with a typical common-mode rejection of 80dB. The part contains dual 2µs successive approximation A/Ds, two differential sample-and-hold amplifiers, an internal +2.5V reference with REF<sub>IN</sub> and REF<sub>OUT</sub> pins and a high speed parallel interface. There are four analog inputs that are grouped into two channels (A and B) selected by the A0 input (A0 LOW selects Channels A0 and B0, while A0 HIGH selects Channels A1 and B1). Each A/D converter has two inputs (A0 and A1 and B0 and B1) that can be sampled and converted simultaneously, thus preserving the relative phase information of the signals on both analog inputs. The part accepts an analog input voltage in the range of  $-V_{REF}$  to  $+V_{REF}$ , centered around the internal +2.5V reference. The part will also accept bipolar input ranges when a level shift circuit is used at the front end (see Figure 7).

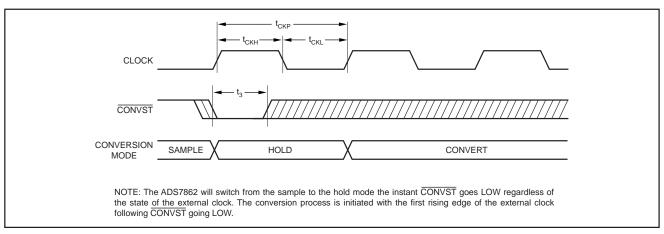

A conversion is initiated on the ADS7862 by bringing the CONVST pin LOW for a minimum of 15ns. CONVST LOW places both sample-and-hold amplifiers in the hold state simultaneously and the conversion process is started on both channels. The BUSY output will then go HIGH and remain HIGH for the duration of the conversion cycle. Depending on the status of the A0 pin, the data will either reflect a conversion of Channel 0 (A0 LOW) or Channel 1 (A0 HIGH). The data can be read from the parallel output bus following the conversion by bringing both  $\overline{\text{RD}}$  and  $\overline{\text{CS}}$  LOW.

Conversion time for the ADS7862 is  $1.75\mu s$  when an 8MHz external clock is used. The corresponding acquisition time is  $0.25\mu s$ . To achieve maximum output rate (500kHz), the read function can be performed immediately at the start of the next conversion.

NOTE: This mode of operation is described in more detail in the Timing and Control section of this data sheet.

#### **SAMPLE-AND-HOLD SECTION**

The sample-and-hold amplifiers on the ADS7862 allow the A/Ds to accurately convert an input sine wave of full-scale amplitude to 12-bit accuracy. The input bandwidth of the sample-and-hold is greater than the Nyquist rate (Nyquist equals one-half of the sampling rate) of the A/D even when the A/D is operated at its maximum throughput rate of 500kHz. The typical small-signal bandwidth of the sample-and-hold amplifiers is 40MHz.

Typical aperture delay time or the time it takes for the ADS7862 to switch from the sample to the hold mode following the  $\overline{\text{CONVST}}$  pulse is 3.5ns. The average delta of repeated aperture delay values is typically 50ps (also known as aperture jitter). These specifications reflect the ability of the ADS7862 to capture AC input signals accurately at the exact same moment in time.

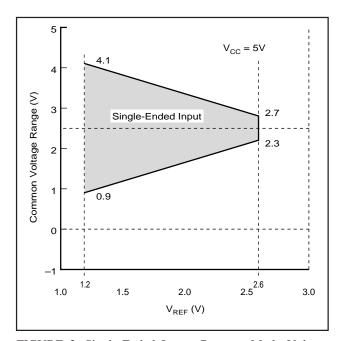

#### REFERENCE

Under normal operation, the REF $_{\rm OUT}$  pin (pin 2) should be directly connected to the REF $_{\rm IN}$  pin (pin 1) to provide an internal +2.5V reference to the ADS7862. The ADS7862 can operate, however, with an external reference in the range of 1.2V to 2.6V for a corresponding full-scale range of 2.4V to 5.2V.

The internal reference of the ADS7862 is double-buffered. If the internal reference is used to drive an external load, a buffer is provided between the reference and the load applied to pin 2 (the internal reference can typically source 2mA of current—load capacitance should not exceed 100pF). If an external reference is used, the second buffer provides isolation between the external reference and the CDAC. This buffer is also used to recharge all of the capacitors of both CDACs during conversion.

#### **ANALOG INPUT**

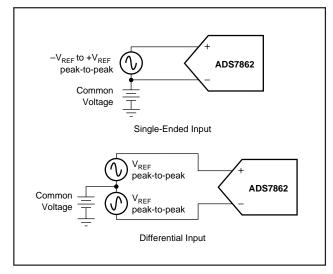

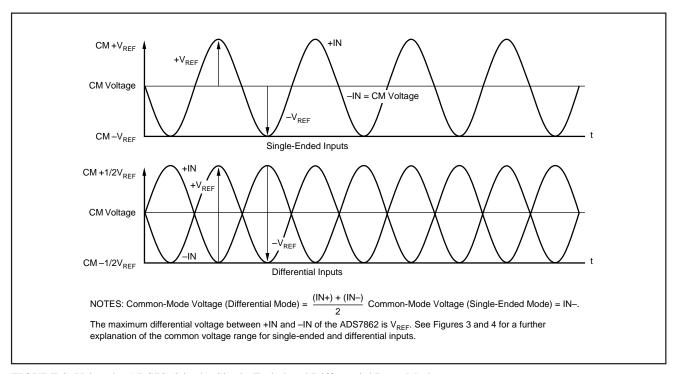

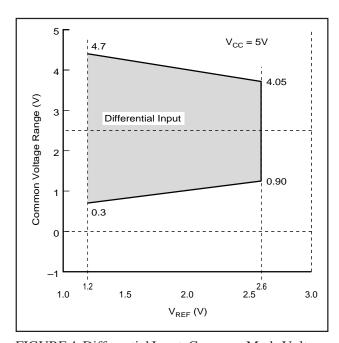

The analog input is bipolar and fully differential. There are two general methods of driving the analog input of the ADS7862: single-ended or differential (see Figures 1 and 2). When the input is single-ended, the –IN input is held at the common-mode voltage. The +IN input swings around the same common voltage and the peak-to-peak amplitude is the (common-mode +V<sub>REF</sub>) and the (common-mode –V<sub>REF</sub>). The value of V<sub>REF</sub> determines the range over which the common-mode voltage may vary (see Figure 3).

When the input is differential, the amplitude of the input is the difference between the +IN and -IN input, or: (+IN) – (-IN). The peak-to-peak amplitude of each input is  $\pm 1/2 V_{REF}$  around this common voltage. However, since the inputs are  $180^{\circ}$  out of phase, the peak-to-peak amplitude of the differential voltage is  $+V_{REF}$  to  $-V_{REF}$ . The value of  $V_{REF}$  also determines the range of the voltage that may be common to both inputs (see Figure 4).

FIGURE 1. Methods of Driving the ADS7862 Single-Ended or Differential.

FIGURE 2. Using the ADS7862 in the Single-Ended and Differential Input Modes.

FIGURE 3. Single-Ended Input: Common-Mode Voltage Range vs  $V_{REF}$ .

In each case, care should be taken to ensure that the output impedance of the sources driving the +IN and -IN inputs are matched. Otherwise, this may result in offset error, which will change with both temperature and input voltage.

The input current on the analog inputs depend on a number of factors: sample rate, input voltage, and source impedance. Essentially, the current into the ADS7862 charges the internal capacitor array during the sampling period. After this

FIGURE 4. Differential Input: Common-Mode Voltage Range vs  $V_{REF}$ .

capacitance has been fully charged, there is no further input current. The source of the analog input voltage must be able to charge the input capacitance (15pF) to a 12-bit settling level within 2 clock cycles. When the converter goes into the hold mode, the input impedance is greater than  $1G\Omega$ .

Care must be taken regarding the absolute analog input voltage. The +IN input should always remain within the range of GND -300 mV to  $V_{\rm DD}+0.3 V.$

#### TRANSITION NOISE

Figure 5 shows a histogram plot for the ADS7862 following 8,000 conversions of a DC input. The DC input was set at output code 2046. All but one of the conversions had an output code result of 2046 (one of the conversions resulted in an output of 2047). The histogram reveals the excellent noise performance of the ADS7862.

FIGURE 5. Histogram of 8,000 Conversions of a DC Input.

#### **BIPOLAR INPUTS**

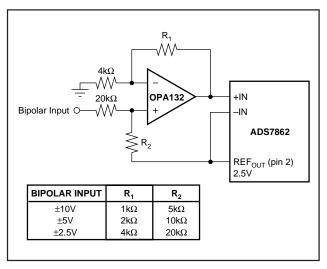

The differential inputs of the ADS7862 were designed to accept bipolar inputs ( $-V_{REF}$  and  $+V_{REF}$ ) around the internal reference voltage (2.5V), which corresponds to a 0V to 5V input range with a 2.5V reference. By using a simple op amp circuit featuring a single amplifier and four external resistors, the ADS7862 can be configured to except bipolar inputs. The conventional  $\pm 2.5$ V,  $\pm 5$ V, and  $\pm 10$ V input ranges can be interfaced to the ADS7862 using the resistor values shown in Figure 7.

#### **TIMING AND CONTROL**

The ADS7862 uses an external clock (CLOCK, pin 19) which controls the conversion rate of the CDAC. With an 8MHz external clock, the A/D sampling rate is 500 kHz which corresponds to a  $2\mu \text{s}$  maximum throughput time.

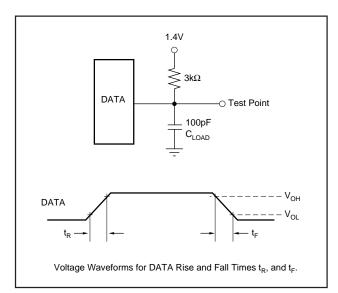

FIGURE 6. Test Circuits for Timing Specifications.

FIGURE 7. Level Shift Circuit for Bipolar Input Ranges.

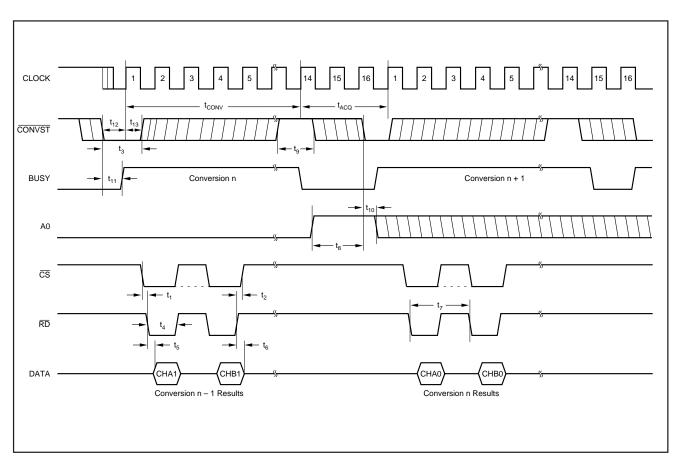

Three timing diagrams are used to explain the operation of the ADS7862. Figure 8 shows the timing relationship between the CLOCK, CONVST (pin 18) and the conversion

FIGURE 8. Conversion Mode.

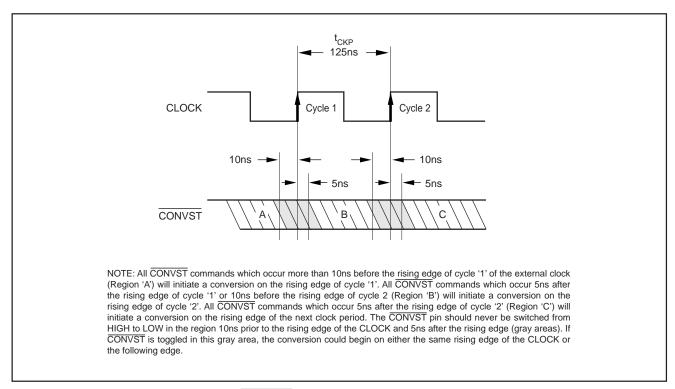

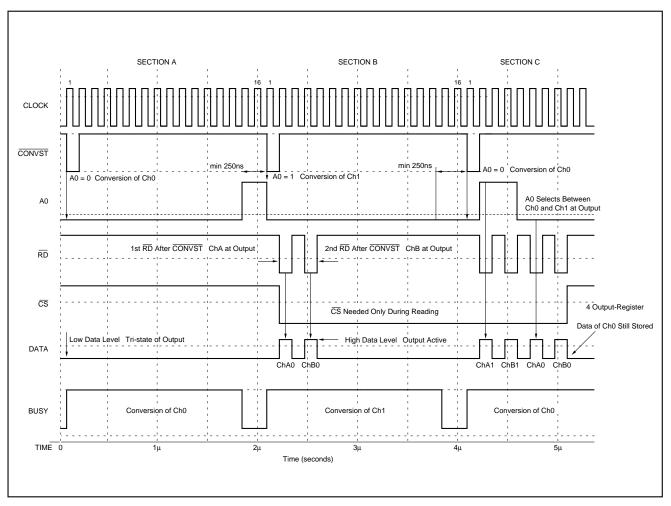

mode. Figure 9, in conjunction with Table I, shows the basic read/write functions of the ADS7862 and highlights all of the timing specifications. Figure 10 shows a more detailed description of initiating a conversion using CONVST. Figure 11 illustrates three consecutive conversions and, with the accompanying text, describes all of the read and write capabilities of the ADS7862.

| DESCRIPTION           | ANALOG INPUT                                                  |                 |                         |  |  |  |  |

|-----------------------|---------------------------------------------------------------|-----------------|-------------------------|--|--|--|--|

| Full-Scale Input Span | -V <sub>REF</sub> to +V <sub>REF</sub> <sup>(1)</sup>         | DIGITAL OUTPUT  |                         |  |  |  |  |

| Least Significant     | (-V <sub>REF</sub> to +V <sub>REF</sub> )/4096 <sup>(2)</sup> | BINARY TWO'S CO | BINARY TWO'S COMPLEMENT |  |  |  |  |

| Bit (LSB)             | ( KEI KEI /                                                   | BINARY CODE     | HEX CODE                |  |  |  |  |

| +Full Scale           | 4.99878V                                                      | 0111 1111 1111  | 7FF                     |  |  |  |  |

| Midscale              | 2.5V                                                          | 0000 0000 0000  | 000                     |  |  |  |  |

| Midscale - 1 LSB      | 2.49878V                                                      | 1111 1111 1111  | FFF                     |  |  |  |  |

| -Full Scale           | 0V                                                            | 1000 0000 0000  | 800                     |  |  |  |  |

NOTES: (1)  $-V_{REF}$  to  $+V_{REF}$  around  $V_{REF}$ . With a 2.5V reference, this corresponds to a 0V to 5V input span. (2) 1.22mV with a 2.5V reference.

TABLE I. Ideal Input Voltages and Output Codes.

The Figure 11 timing diagram can be divided into three sections: (a) initiating a conversion (n-2), (b) starting a second conversion (n-1) while reading the data output from the previous conversion (n-2), and (c) starting a third conversion (n) while reading both previous conversions (n-2) and (n-1). In this sequence, Channel 0 is converted

first followed by Channel 1. Channel 1 can be converted prior to Channel 0 if the user wishes by simply starting the conversion process with the A0 pin at logic HIGH (Channel 1) followed by logic LOW (Channel 0).

#### **TIMING SPECIFICATIONS**

| SYMBOL            | DESCRIPTION                           | MIN | TYP | MAX  | UNITS |

|-------------------|---------------------------------------|-----|-----|------|-------|

| t <sub>CONV</sub> | Conversion Time                       |     |     | 1.75 | μs    |

| t <sub>ACQ</sub>  | Acquisition Time                      |     |     | 0.25 | μs    |

| t <sub>CKP</sub>  | Clock Period                          | 125 |     | 5000 | ns    |

| t <sub>CKL</sub>  | Clock LOW                             | 40  |     |      | ns    |

| t <sub>CKH</sub>  | Clock HIGH                            | 40  |     |      | ns    |

| t <sub>1</sub>    | CS to RD Setup Time                   | 0   |     |      | ns    |

| t <sub>2</sub>    | CS to RD Hold Time                    | 0   |     |      | ns    |

| t <sub>3</sub>    | CONVST LOW                            | 15  |     |      | ns    |

| t <sub>4</sub>    | RD Pulse Width                        | 30  |     |      | ns    |

| t <sub>5</sub>    | RD to Valid Data (Bus Access)         |     | 16  | 25   | ns    |

| t <sub>6</sub>    | RD to HI-Z Delay (Bus Relinquish)     |     | 10  | 20   | ns    |

| t <sub>7</sub>    | Time Between Conversion Reads         | 40  |     |      | ns    |

| t <sub>8</sub>    | Address Setup Time                    | 250 |     |      | ns    |

| t <sub>9</sub>    | CONVST HIGH                           | 20  |     |      | ns    |

| t <sub>10</sub>   | Address Hold Time                     | 20  |     |      | ns    |

| t <sub>11</sub>   | CONVST to BUSY Propagation Delay      |     |     | 30   | ns    |

| t <sub>12</sub>   | CONVST LOW Prior to CLOCK Rising Edge | 10  |     |      | ns    |

| t <sub>13</sub>   | CONVST LOW After CLOCK Rising Edge    | 5   |     |      | ns    |

| t <sub>F</sub>    | Data Fall Time                        |     | 13  | 25   | ns    |

| t <sub>R</sub>    | Data Rise Time                        |     | 20  | 30   | ns    |

FIGURE 9. Reading and Writing to the ADS7862 During the Same Cycle.

FIGURE 10. Timing Between CLOCK and CONVST to Start a Conversion.

FIGURE 11. ADS7862 Timing Diagram Showing Complete Functionality.

#### **SECTION A**

Conversions are initiated by bringing the CONVST pin (pin 18) LOW for a minimum of 5ns (after the 5ns minimum requirement has been met, the CONVST pin can be brought HIGH). The ADS7862 will switch from the sample to the hold mode on the falling edge of the CONVST command. Following the first rising edge of the external clock after a CONVST LOW, the ADS7862 will begin conversion (this first rising edge of the external clock represents the start of clock cycle one; the ADS7862 requires sixteen cycles to complete a conversion). The input channel is also latched in at this point in time. The A0 input (pin 22) must be selected 250ns prior to the CONVST pin going LOW so that the correct address will be selected prior to conversion. The BUSY output will go HIGH immediately following CONVST going LOW. BUSY will stay HIGH through the conversion process and return LOW when the conversion has ended. After CONVST has remained LOW for the minimum time, the ADS7862 will switch from the hold mode to the conversion mode synchronous to the next rising edge of the external clock and conversion 'n – 2' will begin. Both  $\overline{RD}$ (pin 21) and  $\overline{CS}$  (pin 20) can be HIGH during and before a conversion. However, they must both be LOW to enable the output bus and read data out.

#### **SECTION B**

The  $\overline{\text{CONVST}}$  pin is switched from HIGH to LOW a second time to initiate conversion 'n - 1'. Again, the address must be selected 250ns prior to  $\overline{\text{CONVST}}$  going LOW to ensure that the new address is selected for conversion. Both the  $\overline{\text{RD}}$  and  $\overline{\text{CS}}$  pins are brought LOW in order to enable the parallel output bus with the 'n - 2' conversion results of Channel A0. While continuing to hold  $\overline{\text{CS}}$  LOW,  $\overline{\text{RD}}$  is held LOW for a minimum of 30ns which enables the output bus with the Channel A0 results of conversion 'n - 2'. The  $\overline{\text{RD}}$  pin is toggled from HIGH to LOW a second time in order to enable the output bus with the Channel B0 results of conversion 'n - 2'.

#### **SECTION C**

$\overline{\text{CONVST}}$  is brought LOW for a third time to initiate conversion 'n' (Channel 0). While the conversion is in process, the results for both conversions 'n – 2' and 'n – 1' can be read. The address pin is brought HIGH while  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  are brought LOW which enables the output bus with the Channel A1 results of conversion 'n – 1'. The  $\overline{\text{RD}}$  pin is toggled from HIGH to LOW for a second time in Section C and the 'n – 1' conversion results for Channel B1 appear at the output bus. The address pin (A0) is then brought LOW and the read process repeats itself with the most recent conversion results for Channel 0 (n – 2) appearing at the output bus.

#### **READING DATA**

The ADS7862 outputs full parallel data in Binary Two's Complement data output format. The parallel output will be active when  $\overline{CS}$  (pin 20) and  $\overline{RD}$  (pin 21) are both LOW. The

output data should not be read 125ns prior to the falling edge of  $\overline{CONVST}$  and 10ns after the falling edge. Any other combination of  $\overline{CS}$  and  $\overline{RD}$  will tri-state the parallel output. Valid conversion data can be read on pins 5 through 16 (MSB-LSB). Refer to Table I for ideal output codes.

## LAYOUT

For optimum performance, care should be taken with the physical layout of the ADS7862 circuitry. This is particularly true if the CLOCK input is approaching the maximum throughput rate.

The basic SAR architecture is sensitive to glitches or sudden changes on the power supply, reference, ground connections and digital inputs that occur just prior to latching the output of the analog comparator. Thus, driving any single conversion for an n-bit SAR converter, there are n "windows" in which large external transient voltages can affect the conversion result. Such glitches might originate from switching power supplies, nearby digital logic or high power devices. The degree of error in the digital output depends on the reference voltage, layout, and the exact timing of the external event. Their error can change if the external event changes in time with respect to the CLOCK input.

With this in mind, power to the ADS7862 should be clean and well bypassed. A  $0.1\mu F$  ceramic bypass capacitor should be placed as close to the device as possible. In addition, a  $1\mu F$  to  $10\mu F$  capacitor is recommended. If needed, an even larger capacitor and a  $5\Omega$  or  $10\Omega$  series resistor may be used to low-pass filter a noisy supply. On average, the ADS7862 draws very little current from an external reference as the reference voltage is internally buffered. If the reference voltage is external and originates from an op amp, make sure that it can drive the bypass capacitor or capacitors without oscillation. A bypass capacitor is not necessary when using the internal reference (tie pin 1 directly to pin 2).

The AGND and DGND pins should be connected to a clean ground point. In all cases, this should be the 'analog' ground. Avoid connections which are too close to the grounding point of a microcontroller or digital signal processor. If required, run a ground trace directly from the converter to the power supply entry point. The ideal layout will include an analog ground plane dedicated to the converter and associated analog circuitry.

## **APPLICATIONS**

An applications section will be added featuring the ADS7862 interfacing to popular DSP processors. The updated data sheet will be available in the near future on the Burr-Brown web site:

http://www.burr-brown.com/