# Monolithic 16-Bit Resolution DIGITAL-TO-ANALOG CONVERTER

#### **FEATURES**

- COMPLETE D/A CONVERTER: Internal Voltage Reference

±3V Output Operational Amplifier

Pinout Allows I<sub>OUT</sub> (±1.0mA) Option

No external components required

- 0.012% LINEARITY ERROR MAX

- 12-BIT MONOTONICITY GUARANTEED OVER 0°C TO +70°C

- ±5V TO ±12V POWER SUPPLY

- SETTLING TIME:  $V_{out} = 1.5 \mu s$ ;  $I_{out} = 350 ns$

- SERIAL DATA INPUT: Binary Two's Complement

- 16-PIN PLASTIC DIP AND SOIC

### **APPLICATIONS**

- PROCESS CONTROL

- ATE PIN ELECTRONICS LEVEL SETTING

- CLOSED-LOOP SERVO-CONTROL

- AUTO-CALIBRATION CIRCUIT FOR A/D BOARDS

- UP-GRADE REPLACEMENT FOR MULTIPLYING D/A

- X-Y PLOTTER

- DSP PROCESSOR BOARDS

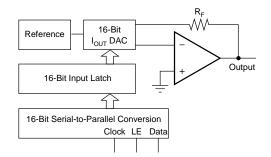

#### DESCRIPTION

The DAC56 is a complete 16-bit monolithic D/A converter. Completely self-contained with a stable, low noise, internal zener voltage reference; high-speed current switches; a resistor ladder network; and a low noise output operational amplifier all on a single monolithic chip. The DAC56 operates over a wide power supply range from ±5V to ±12V.

Differential linearity error (DLE) is guaranteed to meet specifications without external adjustment. However, provisions for an externally adjustable circuit controlling the MSB error, the differential linearity error at bipolar zero, makes the DLE at BPZ essentially zero and provides for high system performance. The I/V amplifier stage includes an output current limiting circuit to protect both amplifier and load from excessive current. This assures the user of high system reliability.

A high-speed interface is capable of clocking in data at a rate of 10MHz max, and its interface logic contains a serial data clock (input), serial data (input) and latch-enable (input). Serial data is clocked MSB first into a 16-bit register and then latched into a 16-bit parallel register.

The DAC56 is packaged in a 16-pin plastic DIP and 16-pin SOIC.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

#### **ELECTRICAL**

All specifications at  $\pm 25^{\circ}\text{C}$ , and power supply voltage of  $\pm 5\text{V}$ , unless otherwise noted.

|                                                                                                                                                                                                                             |                                                |                | DAC56                           |                                      |                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------|---------------------------------|--------------------------------------|---------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                   | CONDITIONS                                     | MIN            | TYP                             | MAX                                  | UNITS                                                   |

| DIGITAL INPUT Resolution Digital Input Level: (1) $V_{IH}$ $V_{IL}$ $I_{IH} \bullet V_{I} = +2.7V$ $I_{IL} \bullet V_{I} = +0.4V$ Input Clock Frequency                                                                     |                                                | +2.4<br>0      | 16                              | +V <sub>L</sub><br>+0.8<br>+1<br>-50 | Bits<br>V<br>V<br>μΑ<br>μΑ<br>ΜΗz                       |

| ACCURACY Integral Linearity Error Differential Linearity Error Gain Error Bipolar Zero Error Monotonicity                                                                                                                   | 0°C to +70°C                                   |                |                                 | ±0.012<br>±0.024<br>±1.5<br>±0.5     | % of FSR <sup>(3)</sup> % of FSR % of FSR % of FSR Bits |

| TEMPERATURE DRIFT  Gain Drift  Bipolar Zero Drift  Linearity Drift  Differential Linearity Drift                                                                                                                            | 0°C to +70°C                                   |                | ±60<br>±20                      | ±0.012<br>±0.024                     | ppm of FSR/°C<br>ppm of FSR/°C<br>% of FSR<br>% of FSR  |

| POWER SUPPLY SENSITIVITY Gain Bipolar Zero                                                                                                                                                                                  | $\pm V_S = \pm V_L = \pm 5VDC$                 |                | ±0.0045<br>±0.0015              |                                      | % of FSR/%V<br>% of FSR/%V                              |

| SETTLING TIME Voltage Output 6V Step 1LSB Current Output 1mA Step                                                                                                                                                           | to $\pm 0.006\%$ of FSR 10 to $100\Omega$ Load |                | 1.5<br>1<br>350                 |                                      | μs<br>μs<br>ns                                          |

| Slew Rate                                                                                                                                                                                                                   | 1kΩ Load <sup>(3)</sup>                        |                | 350<br>12                       |                                      | ns<br>V/μs                                              |

| ANALOG OUTPUT Voltage Output Configuration Bipolar Range Output Current Output Impedance Short Circuit Duration                                                                                                             |                                                | ±2.66<br>±8    | ±3.0<br>0.1<br>definite to Comm | ±3.34                                | V<br>mA<br>Ω                                            |

| Current Output Configuration<br>Bipolar Range<br>Output Impedance                                                                                                                                                           |                                                |                | ±1<br>1.2                       |                                      | mA<br>kΩ                                                |

| WARMUP TIME                                                                                                                                                                                                                 |                                                | 1              |                                 |                                      | min                                                     |

| POWER SUPPLY REQUIREMENTS <sup>(4)</sup> Supply Voltage +V <sub>S</sub> and +V <sub>L</sub> -V <sub>S</sub> and -V <sub>L</sub> Supply Drain (No Load)                                                                      |                                                | +4.75<br>-4.75 | +5.00<br>-5.00                  | +13.2<br>-13.2                       | V<br>V                                                  |

| +V (+V <sub>S</sub> and +V <sub>L</sub> = +5V)<br>-V (-V <sub>S</sub> and -V <sub>L</sub> = -5V)<br>+V (+V <sub>S</sub> and +V <sub>L</sub> = +12V)<br>-V (-V <sub>S</sub> and -V <sub>L</sub> = -12V)<br>Power Dissipation |                                                |                | +10<br>-25<br>+12<br>-27        | +17<br>-35                           | mA<br>mA<br>mA                                          |

| $V_S$ and $V_L$ = $\pm 5V$<br>$V_S$ and $V_L$ = $\pm 12V$                                                                                                                                                                   |                                                |                | 175<br>468                      | 260                                  | mW<br>mW                                                |

| TEMPERATURE RANGE Specification Storage                                                                                                                                                                                     |                                                | 0<br>-60       |                                 | 70<br>100                            | °C<br>°C                                                |

NOTES: (1) Logic input levels are TTL-/CMOS-compatible. (2) FSR means full-scale range and is equivalent to 6V ( $\pm$ 3V) for DAC56 in the V<sub>OUT</sub> mode. (3) Measured with an active clamp to provide a low impedance for approximately 200ns. (4) All specifications assume +V<sub>S</sub> connected to +V<sub>L</sub> and -V<sub>S</sub> connected to -V<sub>L</sub>. If supplies are connected separately, -V<sub>L</sub> must not be more negative than -V<sub>S</sub> to assure proper operation. No similar restriction applies to the value of +V<sub>L</sub> with respect to +V<sub>S</sub>.

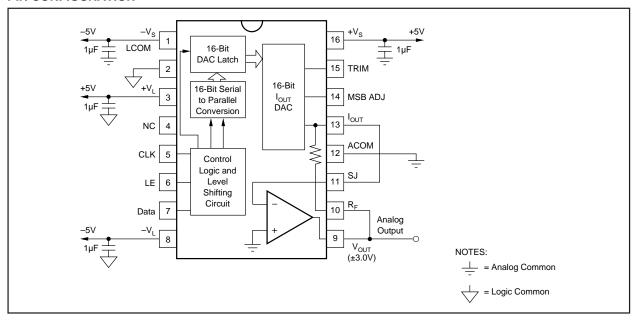

#### **PIN CONFIGURATION**

#### **PIN ASSIGNMENTS**

| PIN | NAME             | FUNCTION                |

|-----|------------------|-------------------------|

| 1   | -V <sub>S</sub>  | Analog Negative Supply  |

| 2   | LCOM             | Logic Common            |

| 3   | +V <sub>L</sub>  | Logic Positive Supply   |

| 4   | NC               | No Connection           |

| 5   | CLK              | Clock Input             |

| 6   | LE               | Latch Enable Input      |

| 7   | DATA             | Serial Data Input       |

| 8   | -V <sub>L</sub>  | Logic Negative Supply   |

| 9   | V <sub>OUT</sub> | Voltage Output          |

| 10  | R <sub>F</sub>   | Feedback Resistor       |

| 11  | SJ               | Summing Junction        |

| 12  | ACOM             | Analog Common           |

| 13  | I <sub>OUT</sub> | Current Output          |

| 14  | MSB ADJ          | MSB Adjustment Terminal |

| 15  | TRIM             | MSB Trim-pot Terminal   |

| 16  | +V <sub>S</sub>  | Analog Positive Supply  |

|     |                  |                         |

#### **PACKAGE INFORMATION**

| PRODUCT | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|---------|--------------------|------------------------------------------|

| DAC56P  | 16-Pin Plastic DIP | 180                                      |

| DAC56U  | 16-Pin SOIC        | 211                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

#### **ABSOLUTE MAXIMUM RATINGS**

| DC Supply Voltage                 | ±15VDC         |

|-----------------------------------|----------------|

| Input Logic Voltage               |                |

| Power Dissipation                 | 850mW          |

| Operating Temperature             | 25°C to +70°C  |

| Storage Temperature               | 80°C to +100°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection methods.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

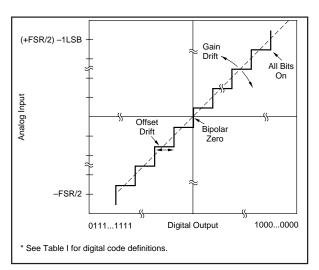

## **OPERATING INSTRUCTIONS**

The accuracy of a D/A converter is described by the transfer function as shown in Figure 1. Digital input to analog output converter relationships are shown in Table I. The errors in the D/A converter are combinations of analog errors due to the linear circuitry, matching and tracking properties of the ladder and scaling networks, power supply rejection, and reference errors. In summary, these errors consist of initial errors including gain, offset, linearity, differential linearity, and power supply sensitivity. Gain drift over temperature rotates the line (Figure 1) about the bipolar zero point and offset drift shifts the line left or right over the operating temperature range. Most of the offset and gain drift is due to the drift of the internal reference zener diode with temperature or time.

The converter is designed so that these drifts are in opposite directions. This way the bipolar zero voltage is virtually unaffected by variations in the reference voltage.

FIGURE 1. Input vs Output for an Ideal Bipolar D/A Converter.

| DIGITAL INPUT     | ANALOG OUTPUT                                     |                       |                       |  |

|-------------------|---------------------------------------------------|-----------------------|-----------------------|--|

| Binary Two's      | DAC Output                                        | Voltage (V),          | Current (mA),         |  |

| Complement (BTC)  |                                                   | V <sub>OUT</sub> Mode | I <sub>OUT</sub> Mode |  |

| 7FFF <sub>H</sub> | + Full Scale - Full Scale Bipolar Zero Zero -1LSB | +2.999908             | -0.999970             |  |

| 8000 <sub>H</sub> |                                                   | -3.000000             | +1.000000             |  |

| 0000 <sub>H</sub> |                                                   | 0.000000              | 0.000000              |  |

| FFFF <sub>H</sub> |                                                   | -0.000092             | +0.030500μA           |  |

TABLE I. Digital Input to Analog Output Relationship.

#### **DIGITAL INPUT CODES**

The DAC56 accepts serial input data (MSB first) in Binary Two's Complement form—Refer to Table I for input/output relationships.

#### POWER SUPPLY CONNECTIONS

Power supply decoupling capacitors should be added as shown in the Connection Diagram (Figure 2), for optimum performance and noise rejection.

These capacitors ( $1\mu F$  tantalum recommended) should be connected as close as possible to the converter.

FIGURE 2. Connection Diagram.

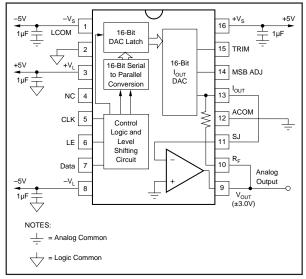

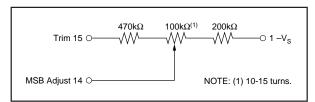

#### **MSB ERROR ADJUSTMENT (OPTIONAL)**

Differential linearity error at all codes of the DAC56 is guaranteed to meet specifications without an external adjustment. However, if adjustment of the differential linearity error at bipolar zero is desired, it can be trimmed essentially to zero using the circuit as shown in Figure 3.

FIGURE 3. MSB Adjustment Circuit.

After allowing ample warm-up time (5 to 10 minutes) to assure stable operation, select the input code FFFF<sub>H</sub>. Measure the output voltage using a 6-1/2 digit voltmeter and record the measurement. Change the digital input code to  $0000_{\rm H}$ . Adjust the  $100k\Omega$  potentiometer (TCR of 100ppm per °C or less is recommended) to make the output voltage read 1LSB more than the voltage reading of the previous code (ex. 1LSB =  $92\mu V$  at FSR = 6V).

If the MSB adjustment circuit is not used, pins 14 and 15 should be left open.

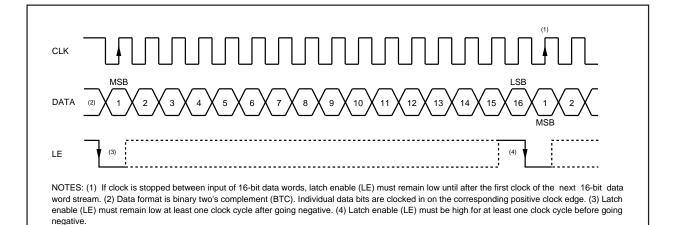

FIGURE 4. Input Timing Diagram.

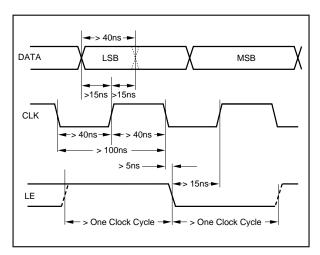

FIGURE 5. Input Timing Relationships.

#### INPUT TIMING CONSIDERATIONS

Figures 4 and 5 refer to the input timing required to interface the inputs of DAC56 to a serial input data stream. Serial data is accepted in Binary Two's Complement with the MSB being loaded first. Data is clocked in on positive going clock (CLK, pin 5) edges and is latched into the DAC input register on negative going latch enable (LE, pin 6) edges.

The latch enable input must be high for at least one clock cycle before going low, and then must be held low for at least one clock cycle. The last 16 data bits clocked into the serial input register are those that are transferred to the DAC input register when latch enable goes low. In other words, when more than 16 clock cycles occur between a latch enable, only the data present during the last 16 clocks will be transferred to the DAC input register.

Figure 4 gives the general input format required for the DAC56. Figure 5 shows the specific relationships between the various signals and their timing constraints.

BBB