# Wideband, Low Power Voltage Feedback OPERATIONAL AMPLIFIER

## **FEATURES**

- LOW POWER: 50mW

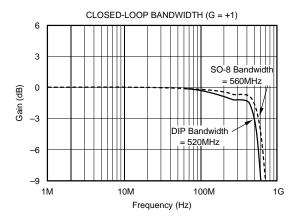

- UNITY GAIN STABLE BANDWIDTH: 560MHz

- LOW HARMONICS: -77dBc at 5MHz

- FAST SETTLING TIME: 20ns to 0.01%

- LOW INPUT BIAS CURRENT: 5µA

- DIFFERENTIAL GAIN/PHASE ERROR: 0.01%/0.03°

- HIGH OUTPUT CURRENT: 85mA

## **APPLICATIONS**

- HIGH RESOLUTION VIDEO

- BASEBAND AMPLIFIER

- CCD IMAGING AMPLIFIER

- ULTRASOUND SIGNAL PROCESSING

- ADC/DAC GAIN AMPLIFIER

- ACTIVE FILTERS

- HIGH SPEED INTEGRATORS

- DIFFERENTIAL AMPLIFIER

## DESCRIPTION

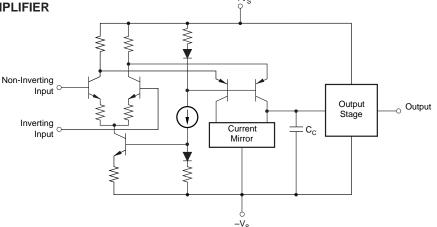

The OPA650 is a low power, wideband voltage feedback operational amplifier. It features a high bandwidth of 560MHz as well as a 12-bit settling time of only 20ns. The low distortion allows its use in communications applications, while the wide bandwidth and true differential input stage make it suitable for use in a variety of active filter applications. Its low distortion gives exceptional performance for telecommunications, medical imaging and video applications.

The OPA650 is internally compensated for unity-gain stability. This amplifier has a fully symmetrical differential input due to its "classical" operational amplifier circuit architecture. Its unusual combination of speed, accuracy and low power make it an outstanding choice for many portable, multi-channel and other high speed applications, where power is at a premium.

The OPA650 is also available in dual (OPA2650) and quad (OPA4650) configurations.

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

At  $T_A$  = +25°C,  $V_S$  = ±5V,  $R_L$  = 100 $\Omega$ , and  $R_{FB}$  = 402 $\Omega$ , unless otherwise noted.  $R_{FB}$  = 25 $\Omega$  for a gain of +1.

|                                                                                                                                                |                                                                                                                                                                                                                             | OP                   | OPA650P, U, N                 |                        |                      | OPA650UB, NB       |                      |                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------|------------------------|----------------------|--------------------|----------------------|-----------------------------------------------------------------------|

| PARAMETER                                                                                                                                      | CONDITIONS                                                                                                                                                                                                                  | MIN TYP MAX          |                               | MIN TYP MAX            |                      | UNITS              |                      |                                                                       |

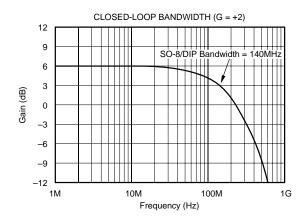

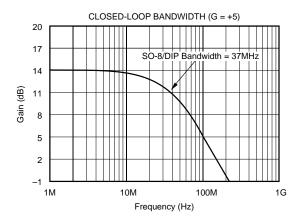

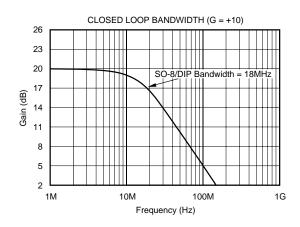

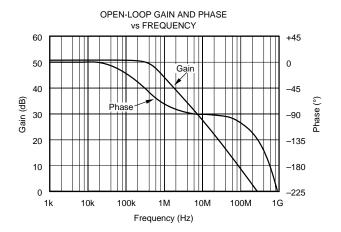

| FREQUENCY RESPONSE<br>Closed-Loop Bandwidth <sup>(2)</sup>                                                                                     | G = +1<br>G = +2<br>G = +5<br>G = +10                                                                                                                                                                                       |                      | 560<br>140<br>37<br>18        |                        |                      | *(1) * * * *       |                      | MHz<br>MHz<br>MHz<br>MHz                                              |

| Gain Bandwidth Product<br>Slew Rate<br>Over Specified Temperature                                                                              | G = +1, 2V Step                                                                                                                                                                                                             |                      | 180<br>240<br>220             |                        |                      | *<br>*<br>*        |                      | MHz<br>V/μs<br>V/μs                                                   |

| Rise Time Fall Time Settling Time 0.01% 0.1% 1%                                                                                                | 0.2V Step<br>0.2V Step<br>G = +1, 2V Step<br>G = +1, 2V Step<br>G = +1, 2V Step                                                                                                                                             |                      | 1<br>1<br>19.6<br>10.2<br>6.3 |                        |                      | *<br>*<br>*<br>*   |                      | ns<br>ns<br>ns<br>ns                                                  |

| Spurious Free Dynamic Range  Differential Gain Differential Phase                                                                              | $G = +1, f = 5.0 \text{ MHz}, V_{O} = 2\text{Vp-p}$ $R_{L} = 100\Omega$ $R_{L} = 200\Omega$ $G = +1, \text{ NTSC}, V_{O} = 1.4\text{Vp}, R_{L} = 150\Omega$ $G = +1, \text{ NTSC}, V_{O} = 1.4\text{Vp}, R_{L} = 150\Omega$ |                      | 73<br>77<br>0.01<br>0.03      |                        |                      | * * *              |                      | dBc<br>dBc<br>%<br>Degrees                                            |

| Bandwidth for 0.1dB Gain Flatness                                                                                                              | G = +2                                                                                                                                                                                                                      |                      | 25                            |                        |                      | *                  |                      | MHz                                                                   |

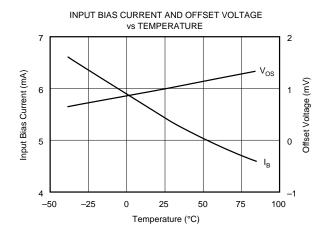

| INPUT OFFSET VOLTAGE Input Offset Voltage Average Drift Power Supply Rejection (+V <sub>S</sub> ) (-V <sub>S</sub> )                           | V <sub>S</sub>   = 4.5V to 5.5V                                                                                                                                                                                             | 60<br>47             | ±1<br>±3<br>76<br>53          | ±5                     | 70<br>50             | 0.6<br>*<br>*<br>* | ±2.5                 | mV<br>μV/°C<br>dB<br>dB                                               |

| INPUT BIAS CURRENT Input Bias Current Over Temperature Input Offset Current Over Temperature                                                   | $V_{CM} = 0V$ $V_{CM} = 0V$                                                                                                                                                                                                 |                      | 5<br>0.5                      | 20<br>30<br>1<br>3     |                      | *<br>0.2           | 10<br>20<br>0.5<br>2 | μΑ<br>μΑ<br>μΑ<br>μΑ                                                  |

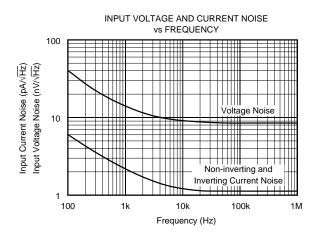

| Noise Input Voltage Noise Noise Density, f = 100Hz f = 10kHz f = 1MHz f = 1MHz to 100MHz Integrated Noise, BW = 10Hz to 100                    |                                                                                                                                                                                                                             |                      | 43<br>9.4<br>8.4<br>8.4<br>84 |                        |                      | * * * *            |                      | nV/√ <u>Hz</u><br>nV/√ <u>Hz</u><br>nV/√ <u>Hz</u><br>nV/√Hz<br>μVrms |

| Input Bias Current Noise Current Noise Density, f = 0.1MHz to Noise Figure (NF)                                                                |                                                                                                                                                                                                                             |                      | 1.2                           |                        |                      | *                  |                      | pA/√Hz                                                                |

|                                                                                                                                                | $R_S = 10k\Omega$ $R_S = 50\Omega$                                                                                                                                                                                          |                      | 4<br>19.5                     |                        |                      | *<br>*             |                      | dB<br>dB                                                              |

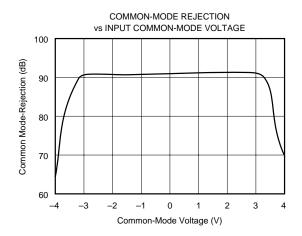

| INPUT VOLTAGE RANGE Common-Mode Input Range Over Specified Temperature Common-Mode Rejection                                                   | V <sub>CM</sub> = ±0.5∨                                                                                                                                                                                                     | ±2.2<br>65           | ±2.8                          |                        | *<br>70              | *                  |                      | V<br>V<br>dB                                                          |

| INPUT IMPEDANCE Differential Common-Mode                                                                                                       |                                                                                                                                                                                                                             |                      | 15    1<br>16    1            |                        |                      | *                  |                      | kΩ    pF<br>MΩ    pF                                                  |

| OPEN-LOOP GAIN Open-Loop Voltage Gain Over Specified Temperature                                                                               | $V_{O} = \pm 2V, R_{L} = 100\Omega$<br>$V_{O} = \pm 2V, R_{L} = 100\Omega$                                                                                                                                                  | 45<br>43             | 51                            |                        | 46<br>44             | *                  |                      | dB<br>dB                                                              |

| OUTPUT Voltage Output Over Specified Temperature                                                                                               | No Load $R_L = 250\Omega$ $R_1 = 100\Omega$                                                                                                                                                                                 | ±2.2<br>±2.2<br>±2.0 | ±3.0<br>±2.5<br>±2.3          |                        | ±2.4<br>±2.4<br>±2.2 | *<br>*<br>*        |                      | V<br>V<br>V                                                           |

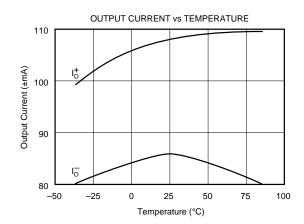

| Current Output, Sourcing Over Specified Temperature Current Output, Sinking Over Specified Temperature Short Circuit Current Output Resistance | 0.1MHz, G = +1                                                                                                                                                                                                              | 75<br>65<br>65<br>35 | 110<br>85<br>150<br>0.08      |                        | *<br>*<br>*<br>*     | * * * * *          |                      | mA<br>mA<br>mA<br>mA<br>mA                                            |

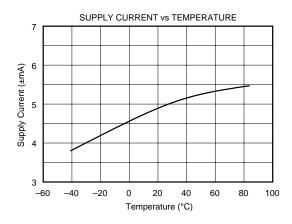

| POWER SUPPLY Specified Operating Voltage Derated Voltage Range Quiescent Current Over Specified Temperature                                    |                                                                                                                                                                                                                             | ±4.5                 | ±5<br>±5.1                    | ±5.5<br>±7.75<br>±8.75 | *                    | *<br>±5.1          | *<br>±6.5<br>±7.5    | V<br>V<br>mA<br>mA                                                    |

| <b>TEMPERATURE RANGE</b> Specification: P, U, N, UB, NB Thermal Resistance, $\theta_{\rm JA}$                                                  |                                                                                                                                                                                                                             | -40                  |                               | +85                    | *                    |                    | *                    | °C                                                                    |

| P 8-Pin DIP<br>U SO-8<br>N SOT23-5                                                                                                             |                                                                                                                                                                                                                             |                      | 100<br>125<br>150             |                        |                      | *<br>*<br>*        |                      | °C/W<br>°C/W<br>°C/W                                                  |

NOTES: (1) An asterisk (\*) specifies the same value as the grade to the left. (2) Frequency response can be strongly influenced by PC board parasitics. The OPA650 is nominally compensated assuming 2pF parasitic load. The demonstration boards show low parasitic layouts for the different package styles.

## **ABSOLUTE MAXIMUM RATINGS**

| Supply                                     |                 |

|--------------------------------------------|-----------------|

| Internal Power Dissipation                 |                 |

| Differential Input Voltage                 |                 |

| Input Voltage Range                        | ±V <sub>S</sub> |

| Storage Temperature Range: P, U, UB, N, NB | 40°C to +125°C  |

| Lead Temperature (soldering, 10s)          | +300°C          |

| (soldering, SOIC 3s)                       | +260°C          |

| Junction Temperature (T <sub>J</sub> )     | +175°C          |

# ELECTROSTATIC DISCHARGE SENSITIVITY

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection methods.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications.

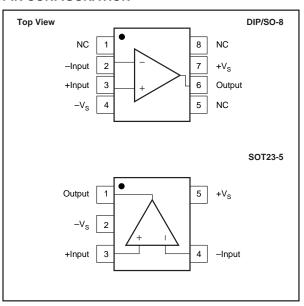

## **PIN CONFIGURATION**

#### PACKAGE/ORDERING INFORMATION

| PRODUCT             | PACKAGE            | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | TEMPERATURE<br>RANGE             | PACKAGE<br>MARKING <sup>(2)</sup> | ORDERING<br>NUMBER <sup>(3)</sup> |

|---------------------|--------------------|---------------------------------------------|----------------------------------|-----------------------------------|-----------------------------------|

| OPA650U<br>OPA650UB | SO-8 Surface Mount | 182<br>182                                  | –40°C to +85°C<br>–40°C to +85°C | OPA650U<br>OPA650UB               | OPA650U<br>OPA650UB               |

| OPA650N             | 5-pin SOT23-5      | 331                                         | -40°C to +85°C                   | A50                               | OPA650N-250<br>OPA650N-3k         |

| OPA650NB            | 5-pin SOT23-5      | 331                                         | −40°C to +85°C                   | A50B                              | OPA650NB-250<br>OPA650NB-3k       |

| OPA650P             | 8-Pin Plastic DIP  | 006                                         | -40°C to +85°C                   | OPA650P                           | OPA650P                           |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book. (2) The "B" grade of the SO-8 package will be marked with a "B" by pin 8. The "B" grade of the SOT23-5 will be marked with a "B" near pins 3 and 4. (3) The SOT23-5 is only available on a 7" tape and reel (e.g. ordering 250 pieces of "OPA650N-250" will get a single 250 piece tape and reel. Ordering 3000 pieces of "OPA650N-3k" will get a single 3000 piece tape and reel). Please refer to Appendix B of Burr-Brown IC Data Book for detailed Tape and Reel Mechanical information.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

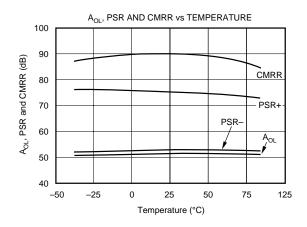

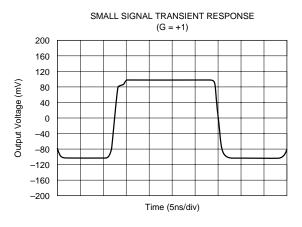

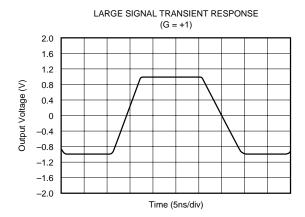

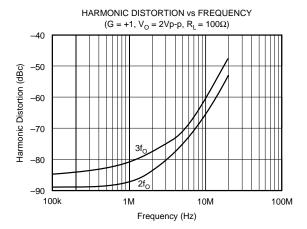

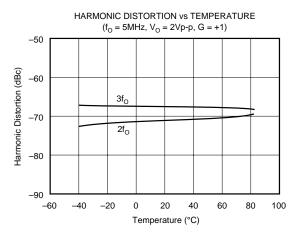

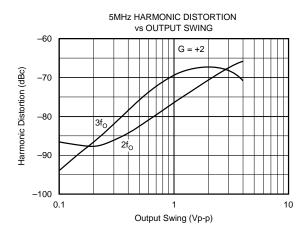

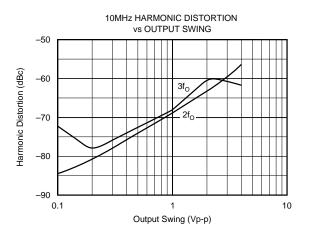

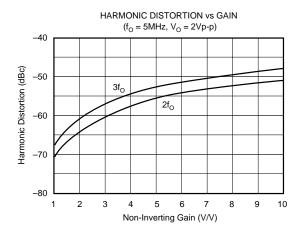

# TYPICAL PERFORMANCE CURVES

At  $T_A$  = +25°C,  $V_S$  = ±5V,  $R_L$  = 100 $\Omega$ , and  $R_{FB}$  = 402 $\Omega$ , unless otherwise noted.  $R_{FB}$  = 25 $\Omega$  for Gain of +1.

# **TYPICAL PERFORMANCE CURVES (CONT)**

At T\_A = +25°C, V\_S =  $\pm 5$ V, R\_L =  $100\Omega$ , and R\_FB =  $402\Omega$ , unless otherwise noted. R\_FB =  $25\Omega$  for Gain of +1.

# TYPICAL PERFORMANCE CURVES (CONT)

At  $T_A$  = +25°C,  $V_S$  =  $\pm 5$ V,  $R_L$  = 100 $\Omega$ , and  $R_{FB}$  = 402 $\Omega$ , unless otherwise noted.  $R_{FB}$  = 25 $\Omega$  for Gain of +1.

# TYPICAL PERFORMANCE CURVES (CONT)

At  $T_A$  = +25°C,  $V_S$  = ±5V,  $R_L$  = 100 $\Omega$ , and  $R_{FB}$  = 402 $\Omega$ , unless otherwise noted.  $R_{FB}$  = 25 $\Omega$  for Gain of +1.

# DISCUSSION OF PERFORMANCE

The OPA650 is a low power, wideband voltage feedback operational amplifier. Each channel is internally compensated to provide unity gain stability. The OPA650's voltage feedback architecture features true differential and fully symmetrical inputs. This minimizes offset errors, making the OPA650 well suited for implementing filter and instrumentation designs. The OPA650's AC performance is optimized to provide a gain bandwidth product of 180MHz and a fast 0.1% settling time of 10.2ns, which is an important consideration in high speed data conversion applications. Along with its excellent settling characteristics, the low DC input offset of  $\pm 1 \mathrm{mV}$  and drift of  $\pm 3 \mu \mathrm{V/^{\circ}C}$  support high accuracy requirements. In applications requiring a higher slew rate and wider bandwidth, such as video and high bit rate digital communications, consider the current feedback OPA658.

## CIRCUIT LAYOUT AND BASIC OPERATION

Achieving optimum performance with a high frequency amplifier like the OPA650 requires careful attention to layout parasitics and selection of external components. Recommendations for PC board layout and component selection include:

- a) Minimize parasitic capacitance to any ac ground for all of the signal I/O pins. Parasitic capacitance on the output and inverting input pins can cause instability; on the non-inverting input it can react with the source impedance to cause unintentional bandlimiting. To reduce unwanted capacitance, a window around the signal I/O pins should be opened in all of the ground and power planes. Otherwise, ground and power planes should be unbroken elsewhere on the board.

- **b)** Minimize the distance (< 0.25") from the two power pins to high frequency  $0.1\mu F$  decoupling capacitors. At the pins,

the ground and power plane layout should not be in close proximity to the signal I/O pins. Avoid narrow power and ground traces to minimize inductance between the pins and the decoupling capacitors. Larger (2.2 $\mu$ F to 6.8 $\mu$ F) decoupling capacitors, effective at lower frequencies, should also be used. These may be placed somewhat farther from the device and may be shared among several devices in the same area of the PC board.

c) Careful selection and placement of external components will preserve the high frequency performance of the OPA650. Resistors should be a very low reactance type. Surface mount resistors work best and allow a tighter overall layout. Metal film or carbon composition axially-leaded resistors can also provide good high frequency performance. Again, keep their leads as short as possible. Never use wirewound type resistors in a high frequency application. Since the output pin and the inverting input pin are most sensitive to parasitic capacitance, always position the feedback and series output resistor, if any, as close as possible to the package pins. Other network components, such as non-inverting input termination resistors, should also be placed close to the package.

Even with a low parasitic capacitance shunting external resistors, excessively high resistor values can create significant time constants and degrade performance. Good metal film or surface mount resistors have approximately 0.2pF in shunt with the resistor. For resistor values > 1.5k $\Omega$ , this adds a pole and/or zero below 500MHz that can affect circuit operation. Keep resistor values as low as possible consistent with output loading considerations. The 402 $\Omega$  feedback used for the Typical Performance Plots is a good starting point for design. Note that a 25 $\Omega$  feedback resistor, rather than a direct short, is suggested for a unity gain follower. This effectively reduces the Q of what would otherwise be a parasitic inductance (the feedback wire) into the parasitic capacitance at the inverting input.

BURR-BROWN

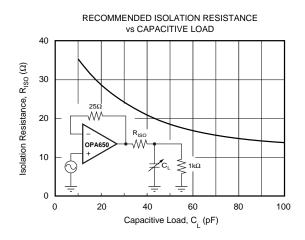

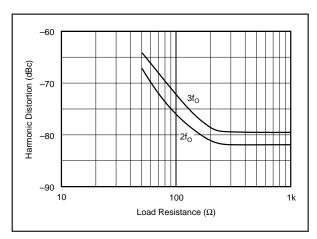

may be made with short direct traces or through on-board transmission lines. For short connections, consider the trace and the input to the next device as a lumped capacitive load. Relatively wide traces (50 to 100 mils) should be used, preferably with ground and power planes opened up around them. Estimate the total capacitive load and set R<sub>ISO</sub> from the plot of recommended R<sub>ISO</sub> vs capacitive load. Low parasitic loads may not need an R<sub>ISO</sub> since the OPA650 is nominally compensated to operate with a 2pF parasitic load. If a long trace is required and the 6dB signal loss intrinsic to doubly terminated transmission lines is acceptable, implement a matched impedance transmission line using microstrip or stripline techniques (consult an ECL design handbook for microstrip and stripline layout techniques). A  $50\Omega$  environment is not necessary on board, and in fact a higher impedance environment will improve distortion as shown in the distortion vs load plot. With a characteristic impedance defined based on board material and desired trace dimensions, a matching series resistor into the trace from the output of the amplifier is used as well as a terminating shunt resistor at the input of the destination device. Remember also that the terminating impedance will be the parallel combination of the shunt resistor and the input impedance of the destination device; the total effective impedance should match the trace impedance. Multiple destination devices are best handled as separate transmission lines, each with their own series and shunt terminations.

d) Connections to other wideband devices on the board

If the 6dB attenuation loss of a doubly terminated line is unacceptable, a long trace can be series-terminated at the source end only. This will help isolate the line capacitance from the op amp output, but will not preserve signal integrity as well as a doubly terminated line. If the shunt impedance at the destination end is finite, there will be some signal attenuation due to the voltage divider formed by the series and shunt impedances.

e) Socketing a high speed part like the OPA650 is not recommended. The additional lead length and pin-to-pin capacitance introduced by the socket creates an extremely troublesome parasitic network which can make it almost impossible to achieve a smooth, stable response. Best results are obtained by soldering the part onto the board. If socketing for the DIP package is desired, high frequency flush mount pins (e.g., McKenzie Technology #710C) can give good results.

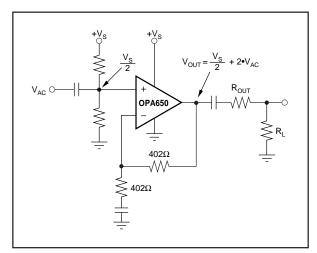

The OPA650 is nominally specified for operation using  $\pm 5V$  power supplies. A 10% tolerance on the supplies, or an ECL -5.2V for the negative supply, is within the maximum specified total supply voltage of 11V. Higher supply voltages can break down internal junctions possibly leading to catastrophic failure. Single supply operation is possible as long as common mode voltage constraints are observed. The common mode input and output voltage specifications can be interpreted as a required headroom to the supply voltage. Observing this input and output headroom requirement will allow non-standard or single supply operation. Figure 1 shows one approach to single-supply operation.

FIGURE 1. Single Supply Operation.

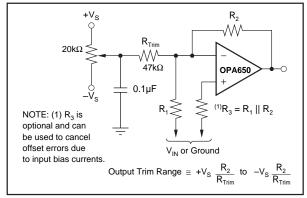

#### **OFFSET VOLTAGE ADJUSTMENT**

If additional offset adjustment is needed, the circuit in Figure 2 can be used without degrading offset drift with temperature. Avoid external adjustment whenever possible since extraneous noise, such as power supply noise, can be inadvertently coupled into the amplifier's inverting input terminal. Remember that additional offset errors can be created by the amplifier's input bias currents. Whenever possible, match the impedance seen by both inputs as is shown with  $R_3$ . This will reduce input bias current errors to the amplifier's offset current.

FIGURE 2. Offset Voltage Trim.

## **ESD PROTECTION**

ESD damage has been well recognized for MOSFET devices, but any semiconductor device is vulnerable to this potentially damaging source. This is particularly true for very high speed, fine geometry processes.

ESD damage can cause subtle changes in amplifier input characteristics without necessarily destroying the device. In precision operational amplifiers, this may cause a noticeable degradation of offset voltage and drift. Therefore, ESD handling precautions are strongly recommended when handling the OPA650.

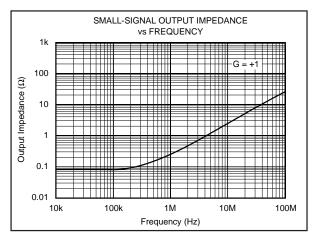

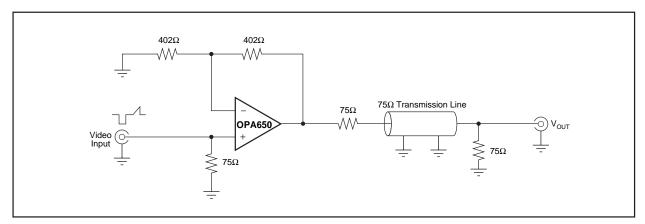

#### **OUTPUT DRIVE CAPABILITY**

The OPA650 has been optimized to drive  $75\Omega$  and  $100\Omega$  resistive loads. The device can drive a 2Vp-p into a  $75\Omega$  load. This high-output drive capability makes the OPA650 an ideal choice for a wide range of RF, IF, and video applications. In many cases, additional buffer amplifiers are unneeded.

Many demanding high-speed applications such as driving A/D converters require op amps with low wideband output impedance. For example, low output impedance is essential when driving the signal-dependent capacitances at the inputs of flash A/D converters. As shown in Figure 3, the OPA650 maintains very low-closed loop output impedance over frequency. Closed-loop output impedance increases with frequency since loop gain is decreasing.

FIGURE 3. Small-Signal Output Impedance vs Frequency.

#### THERMAL CONSIDERATIONS

The OPA650 will not require heatsinking under most operating conditions. Maximum desired junction temperature will limit the maximum allowed internal power dissipation as described below. In no case should the maximum junction temperature be allowed to exceed +175°C.

Operating junction temperature (T<sub>J</sub>) is given by T<sub>A</sub> +  $P_D\theta_{JA}$ . The total internal power dissipation  $(P_D)$  is a combination of the total quiescent power (PDQ) and the power dissipated in of the output stage (PDL) to deliver load power. Quiescent power is simply the specified no-load supply current times the total supply voltage across the part. PDL will depend on the required output signal and load but would, for a grounded resistive load, be at a maximum when the output is a fixed DC voltage equal to 1/2 of either supply voltage (assuming equal bipolar supplies). Under this condition,  $P_{DL} = V_S^2/(4 \cdot R_L)$  where  $R_L$  includes feedback network loading. Note that it is the power dissipated in the output stage and not in the load that determines internal power dissipation. As an example, compute the maximum  $T_I$  for an OPA650N at  $A_V = +2$ ,  $R_L = 100\Omega$ ,  $R_{FB}$ =  $402\Omega$ ,  $\pm V_S = \pm 5V$ , with the output at  $|V_S/2|$ , and the specified maximum  $T_A = +85^{\circ}\text{C}$ .  $P_D = 10\text{V} \cdot 8.75\text{mA} + (5^2)/(10^{\circ})$  $(4 \cdot (100\Omega || 804\Omega)) = 158 \text{mW}$ . Maximum  $T_J = +85 \text{°C} + 1000 \text{°C}$  $0.158W \cdot 150^{\circ}C/W = 109^{\circ}C.$

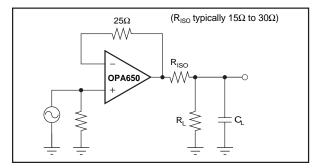

#### DRIVING CAPACITIVE LOADS

The OPA650's output stage has been optimized to drive low resistive loads. Capacitive loads, however, will decrease the amplifier's phase margin which may cause high frequency peaking or oscillations. Capacitive loads greater than 10pF should be isolated by connecting a small resistance, usually  $15\Omega$  to  $30\Omega$ , in series with the output as shown in Figure 4. This is particularly important when driving high capacitance loads such as flash A/D converters. Increasing the gain from +1 will improve the capacitive load drive due to increased phase margin.

In general, capacitive loads should be minimized for optimum high frequency performance. Coax lines can be driven if the cable is properly terminated. The capacitance of coax cable (29pF/foot for RG-58) will not load the amplifier when the coaxial cable or transmission line is terminated in its characteristic impedance.

FIGURE 4. Driving Capacitive Loads.

## FREQUENCY RESPONSE COMPENSATION

The OPA650 is internally compensated and is stable in unity gain with a phase margin of approximately  $60^{\circ}$ . However, the unity gain buffer is the most demanding circuit configuration for loop stability and oscillations are most likely to occur in this gain. If possible, use the device in a noise gain greater than one to improve phase margin and reduce the susceptibility to oscillation. (Note that, from a stability standpoint, an inverting gain of -1V/V is equivalent to a noise gain of 2.) Frequency response for other gains are shown in the Typical Performance Curves.

The high frequency response of the OPA650 in a good layout is very flat with frequency. However, some circuit configurations such as those where large feedback resistances are used, can produce high-frequency gain peaking. This peaking can be minimized by connecting a small capacitor in parallel with the feedback resistor. This capacitor compensates for the closed-loop, high-frequency, transfer function zero that results from the time constant formed by the input capacitance of the amplifier (typically 2pF after PC board mounting), and the input and feedback resistors. The selected compensation capacitor may be a trimmer, a fixed capacitor, or a planned PC board capacitance. The capacitance value is strongly dependent on circuit layout and closed-loop gain. Using small resistor values will preserve

the phase margin and avoid peaking by keeping the break frequency of this zero sufficiently high. When high closedloop gains are required, a three-resistor attenuator (teenetwork) is recommended to avoid using large value resistors with large time constants.

#### **PULSE SETTLING TIME**

High speed amplifiers like the OPA650 are capable of extremely fast settling time with a pulse input. Excellent frequency response flatness and phase linearity are required to get the best settling times. As shown in the specifications table, settling time for a ±1V step at a gain of +1 for the OPA650 is extremely fast. The specification is defined as the time required, after the input transition, for the output to settle within a specified error band around its final value. For a 2V step, 1% settling corresponds to an error band of ±20mV, 0.1% to an error band of ±2mV, and 0.01% to an error band of ±0.2mV. For the best settling times, particularly into an ADC capacitive load, little or no peaking in the frequency response can be allowed. Using the recommended  $R_{\rm ISO}$  for capacitive loads will limit this peaking and reduce the settling times. Fast, extremely fine scale settling (0.01%) requires close attention to ground return currents in the supply decoupling capacitors. For highest performance, consider the OPA642 which isolates the output stage decoupling from the rest of the amplifier.

#### **DIFFERENTIAL GAIN AND PHASE**

Differential Gain (DG) and Differential Phase (DP) are among the more important specifications for video applications. The percentage change in closed-loop gain over a specified change in output voltage level is defined as DG. DP is defined as the change in degrees of the closed-loop phase over the same output voltage change. DG and DP are both specified at the NTSC sub-carrier frequency of 3.58MHz. DG and DP increase closed-loop gain and output voltage transition. All measurements were performed using a Tektronix model VM700 Video Measurement Set.

#### **DISTORTION**

The OPA650's harmonic distortion characteristics into a  $100\Omega$  load are shown versus frequency and power output in the typical performance curves. Distortion can be significantly improved by increasing the load resistance as illustrated in Figure 5. Remember to include the contribution of the feedback network when calculating the effective load resistance seen by the amplifier.

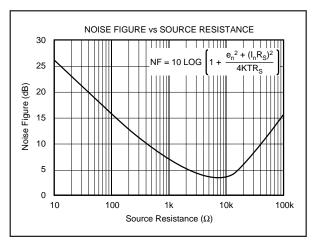

## **NOISE FIGURE**

The OPA650 voltage noise spectral density is specified in the Typical Performance Curves. For RF applications, however, Noise Figure (NF) is often the preferred noise specification since it allows system noise performance to be more easily calculated. The OPA650's Noise Figure vs Source Resistance is shown in Figure 6.

FIGURE 5. 5MHz Harmonic Distortion vs Load Resistance.

FIGURE 6. Noise Figure vs Source Resistance.

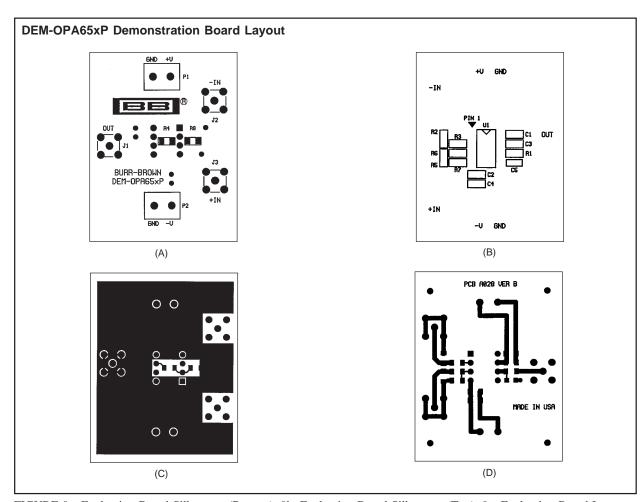

#### SPICE MODELS AND EVALUATION BOARD

Computer simulation of circuit performance using SPICE is often useful when analyzing the performance of analog circuits and systems. This is particularly true for Video and RF amplifier circuits where parasitic capacitance and inductance can have a major effect on circuit performance. SPICE models are available on a disk from the Burr-Brown Applications Department.

Demonstration boards are available for each OPA650 package style. These boards implement a very low parasitic layout that will produce the excellent frequency and pulse responses shown in the Typical Performance Curves. For each package style, the recommended demonstration board is:

| DEM-OPA65xP | 8-Pin DIP for the OPA650P |  |  |

|-------------|---------------------------|--|--|

| DEM-OPA65xU | SO-8 for the OPA650U      |  |  |

| DEM-OPA6xxN | SOT23 for the OPA650N     |  |  |

Contact your local Burr-Brown sales office or distributor to order demonstration boards.

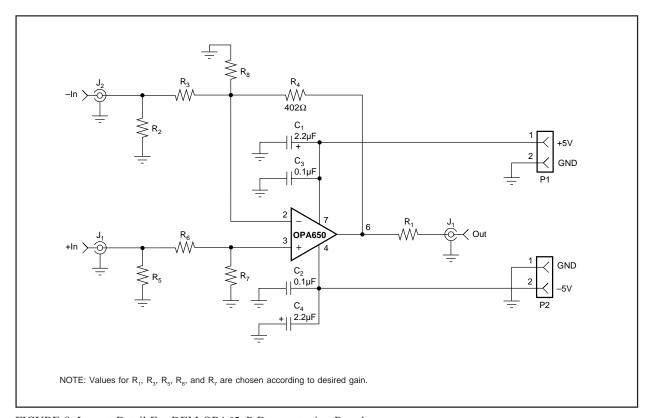

# **TYPICAL APPLICATION**

FIGURE 7. Low Distortion Video Amplifier.

FIGURE 8. Layout Detail For DEM-OPA65xP Demonstration Board.

FIGURE 9a. Evaluation Board Silkscreen (Bottom). 9b. Evaluation Board Silkscreen (Top). 9c. Evaluation Board Layout (Solder Side). 9d. Evaluation Board Layout (Layout Side).