# **CML Semiconductor Products**

**PRODUCT INFORMATION**

# FX019 Digitally Controlled Quad Amplifier Array

Publication D/019/4 December 1995

#### **Features**

- 4 Digitally Controlled Amplifiers

- 15 Gain/Attenuation Steps

- 3 Amplifiers, with a ± 3dB Range in 0.43dB Steps

- 1 'Volume' Amplifier, with a± 14dB Range in 2dB Steps

- 8-Bit Serial Data Control

- Output Mute Function

- Audio and Data Gain Control Applications

- Telecoms, Radio and Industrial Applications

**FX019**

## **Brief Description**

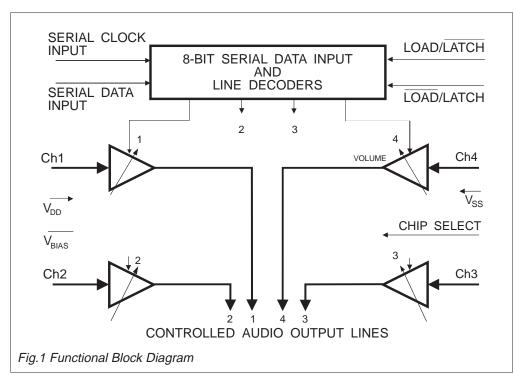

The FX019 Digitally Adjustable Amplifier Array is available to replace trimmer potentiometers and volume controls in Cellular, PMR, Telephony and Communications applications where d.c., voice or data signals need adjustment.

The FX019 is a single-chip LSI consisting of four digitally controlled amplifier stages, each with 15 distinct gain/attenuation steps. Control of each individual amplifier is by an 8-bit serial data stream. Three of the amplifier stages offer a +/-3dB range in steps of 0.43dB, whilst the remaining amplifier offers a +/-14dB range in steps of 2dB, and is suggested for volume control applications. Each amplifier includes a 16th 'Off' state which when applied, mutes the output audio from that channel. This array uses a Chip Select input to select one of two FX019s in a system.

This product replaces the need for manual trimming of audible signals by using the host microprocessor to digitally control the set-up of all audio levels during development, production/calibration and operation.

#### Applications include:

- (i) Control, adjustment and set-up of communications equipment by an Intelligent ATE without manual intervention eg. Deviation, Microphone and L/S Levels, Rx Audio Level etc.

- (ii) Automatic Dynamic Compensation of drift caused by variations in temperature, linearity, etc.

- (iii) Fully automated servicing and re-alignment. The FX019 is a low-power, single 5-volt CMOS device available in plastic DIL and Small Outline (S.O.I.C.) SMD package versions.

1

# Pin Number

# **Function**

| FX019DW |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |  |  |  |

| FX019P  | Carial Clask - This systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I alsoly pulse imput is used to "alsoly in" the Control Date Con Figure 4                                                                       |  |  |  |

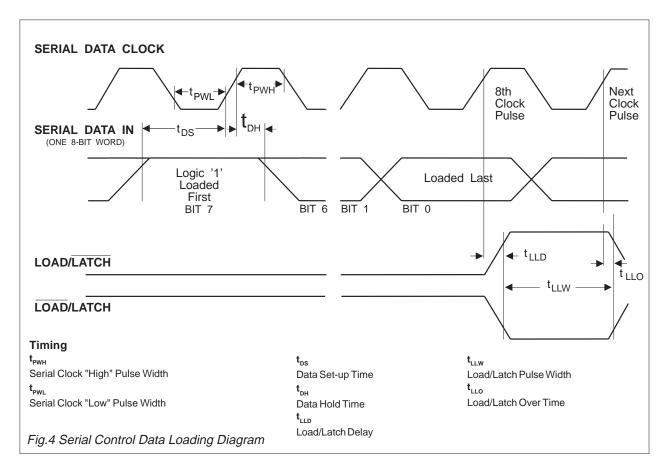

| 1       | Serial Clock: This external clock pulse input is used to "clock in" the Control Data. See Figure 4, Serial Control Data Load Timing. This input has an internal $1M\Omega$ pullup resistor.                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |  |  |  |

| 2       | <b>Load/Latch</b> : Governs the loading and execution of the control data. During serial data loading this input should be kept at a logical '0' to ensure that data rippling past the latches has no effect. When all 8 bits have been loaded, this input should be strobed '0' - '1' - '0' to latch the new data in. Data is executed on the falling edge of the strobe. If the $\overline{\text{Load}}/\text{Latch}$ input is used this pin should be left open circuit. This input has an internal $1M\Omega$ pullup resistor.             |                                                                                                                                                 |  |  |  |

| 3       | <b>Load/Latch</b> : The inverted Load/Latch input. This function governs the loading and execution of the control data. During serial data loading this input should be kept at a logical '1' to ensure that data rippling past the latches has no effect. When all 8 bits have been loaded, this input should be strobed '1' - '0' - '1' to latch the new data in. Data is executed on the rising edge of the strobe. If the Load/Latch input is used this pin should be left open circuit. This input has an internal 1MΩ pulldown resistor. |                                                                                                                                                 |  |  |  |

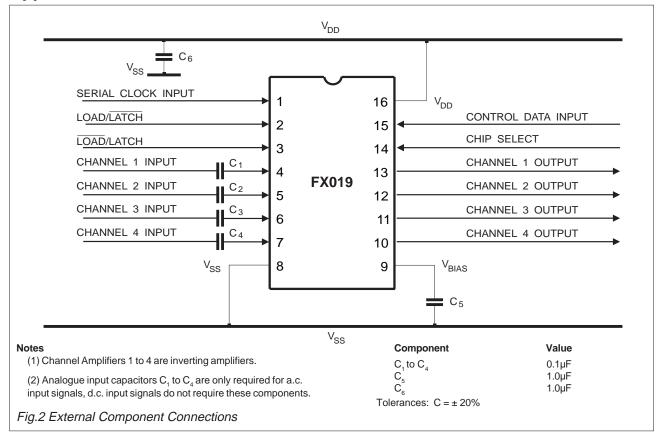

| 4       | Ch1 Input :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Analogue Inputs :                                                                                                                               |  |  |  |

| 5       | Ch2 Input :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | These individual amplifier inputs are self-biasing, a.c. input                                                                                  |  |  |  |

| 6       | Ch3 Input :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | analogue signals must be capacitively coupled to these pins, as shown in Figure 2.  Note that amplifiers Ch1 to Ch4 are 'inverting amplifiers.' |  |  |  |

| 7       | Ch4 Input :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | These that amplified our to our are inverting amplified.                                                                                        |  |  |  |

| 8       | V <sub>ss</sub> : Negative supply rail (GND).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                 |  |  |  |

| 9       | $V_{BIAS}$ : The output of the on-chip bias circuitry, held at $V_{DD}/2$ . This pin should be decoupled to $V_{SS}$ as shown in Figure 2.                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |  |  |  |

| 10      | Ch4 Output :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Controlled Analogue Outputs :                                                                                                                   |  |  |  |

| 11      | Ch3 Output :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | The individual "Gain Controlled" amplifier outputs. Ch1 to Ch3 range from -3dB to +3dB in 0.43dB steps, Ch4 could be                            |  |  |  |

| 12      | Ch2 Output :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | utilized as a volume control, ranging from -14dB to +14dB in 2.0dB steps.                                                                       |  |  |  |

| 13      | Ch1 Output :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | In the "OFF" mode there is no output from the selected amplifier.                                                                               |  |  |  |

| 14      | Chip Select : A logic input to select one of two FX019 microcircuits in a system, see Table 1. This input has an internal $1M\Omega$ pulldown resistor.                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |  |  |  |

| 15      | Control Data Input: Operation of the 4 amplifier channels (Ch1 – Ch4) is controlled by the 8 bits of data entered serially at this pin. The data is entered (bit 7 to bit 0) on the rising edge of the external Serial Clock. The data format is described in Tables 1, 2 and Figure 4. This input has an internal $1M\Omega$ pullup resistor.                                                                                                                                                                                                 |                                                                                                                                                 |  |  |  |

| 16      | V <sub>DD</sub> : Positive supply rail. A single +5-volt power supply is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |  |  |  |

## **Application Notes**

#### **Application Recommendations**

To avoid excess noise and instability in the final installation it is recommended that the following points be noted.

- (a) A noisy or badly regulated power supply can cause instability and/or variance of selected gains.

- (b) Care should be taken on the design and layout of the printed circuit board.

- (c) All external components (Figure 2) should be kept close to the FX019 package.

- (d) Inputs and outputs should be screened wherever possible.

- (e) Tracks should be kept short.

- (f) Analogue tracks should not run parallel to digital tracks.

- (g) A "Ground Plane" connected to  $\rm V_{ss}$  will assist in eliminating external pick-up on the channel input and output pins.

- (h) Do not run high-level output tracks close to low-level input tracks.

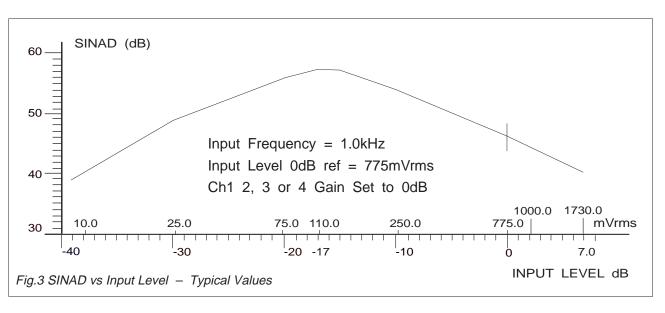

- (i) Input signal amplitudes should be applied with due regard to Figure 3.

## **Control Data and Timing**

The gain of each amplifier block (Channel 1 to Channel 4) in the FX019 is set by a separate 8-bit data word (bit 7 to bit 0). This 8-bit word, consisting of 4 Address bits (bit 7 to bit 4) and 4 Gain Control bits (bit 3 to bit 0), is loaded to the Control Data Input in serial format using the external data clock.

Data is loaded to the FX019 on the rising edge of the Serial Clock. Loaded data is executed on the falling (rising) edge of the Load/Latch (Load/Latch) pulse. Table 1 shows the format of each 4-bit Address word, Table 2 shows the format of each Gain Control word with Figure 4 describing the data loading operation and timing.

| Table 1 Address Word Format |               |       |              |                     |                                                 |                |  |

|-----------------------------|---------------|-------|--------------|---------------------|-------------------------------------------------|----------------|--|

| Bit 7<br>MSB                | Bit 6         | Bit 5 | Bit 4<br>LSB | Channel<br>Selected | Chip<br>Select                                  | Chip<br>Number |  |

| 1                           | 0             | 0     | 0            | 1                   | 0                                               |                |  |

| 1                           | 0             | 0     | 1            | 2                   | 0                                               | Chip           |  |

| 1                           | 0             | 1     | 0            | 3                   | 0                                               | 1              |  |

| 1                           | 0             | 1     | 1            | 4                   | 0                                               |                |  |

| <b>⊢</b>                    | <del></del> - |       |              |                     | <del>-                                   </del> |                |  |

|                             | 1             | 0     | 1            | 2                   | 1 1                                             | Chip           |  |

| 1                           | 1             | 1     | 0            | 3                   | 1                                               | 2              |  |

| 1                           | 1             | 1     | 1            | 4                   | 1                                               | _              |  |

The 8-bit data word is loaded bit 7 first and bit 0 last. Bit 7 must be a logic "1" to address the chip. If bit 7 in the word is a logic "0" that 8-bit word will not be executed. The Chip Select input permits the use of two devices in a system; To facilitate this, Bit 6 can be either a logic "0" or "1." Figure 4 (below) shows the timing information required to load and operate this device.

| Table 2 Gain Control Word Format |      |       |              |                           |                    |

|----------------------------------|------|-------|--------------|---------------------------|--------------------|

| Bit 3<br>MSB                     | Bit2 | Bit 1 | Bit 0<br>LSB | Stage 1, 2, 3<br>(0.43dB) | Stage 4<br>(2.0dB) |

| 0                                | 0    | 0     | 0            | OFF                       | OFF                |

| 0                                | 0    | 0     | 1            | -3.0                      | -14.0dB            |

| 0                                | 0    | 1     | 0            | -2.571                    | -12.0              |

| 0                                | 0    | 1     | 1            | -2.143                    | -10.0              |

| 0                                | 1    | 0     | 0            | -1.714                    | -8.0               |

| 0                                | 1    | 0     | 1            | -1.286                    | -6.0               |

| 0                                | 1    | 1     | 0            | -0.857                    | -4.0               |

| 0                                | 1    | 1     | 1            | -0.428                    | -2.0               |

| 1                                | 0    | 0     | 0            | 0                         | 0                  |

| 1                                | 0    | 0     | 1            | 0.428                     | 2.0                |

| 1                                | 0    | 1     | 0            | 0.857                     | 4.0                |

| 1                                | 0    | 1     | 1            | 1.286                     | 6.0                |

| 1                                | 1    | 0     | 0            | 1.714                     | 8.0                |

| 1                                | 1    | 0     | 1            | 2.143                     | 10.0               |

| 1                                | 1    | 1     | 0            | 2.571                     | 12.0               |

| 1                                | 1    | 1     | 1            | 3.0                       | 14.0               |

### **Specification**

#### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

Supply voltage -0.3 to 7.0V

Input voltage at any pin (ref  $V_{SS} = 0V$ ) -0.3 to  $(V_{DD} + 0.3V)$

Sink/source current (supply pins) +/- 30mA +/- 20mA (other pins)

Total device dissipation @ T<sub>AMB</sub> 25°C 800mW Max. 10mW/°C Derating

Operating temperature range: FX019DW/P -40°C to +85°C (plastic)

Storage temperature range: FX019DW/P -40°C to +85°C (plastic)

#### **Operating Limits**

All device characteristics are measured under the following conditions unless otherwise specified:

$V_{DD} = 5.0V$ ,  $T_{AMB} = 25$ °C. Audio Level 0dB ref: = 775mVrms. Amplifier Gain Set = 0dB.

| Characteristics                                     | See Note | Min.  | Тур.  | Max.  | Unit      |

|-----------------------------------------------------|----------|-------|-------|-------|-----------|

| Static Values                                       |          |       |       |       |           |

| Supply Voltage (V <sub>pp</sub> )                   |          | 4.5   | 5.0   | 5.5   | V         |

| Supply Current                                      |          | -     | 1.5   | -     | mA        |

| Dynamic Values                                      |          |       |       |       |           |

| Control Functions                                   |          |       |       |       |           |

| Input Logic '1'                                     |          | 3.5   | _     | _     | V         |

| Input Logic '0'                                     |          | _     | _     | 1.5   | V         |

| Digital Input Impedances                            |          | 0.5   | 1.0   | _     | $M\Omega$ |

| Amplifier Stages (General)                          |          |       |       |       |           |

| Bandwidth (-3dB)                                    |          | 20.0  | _     | _     | kHz       |

| Output Impedance                                    |          | _     | 1.0   | -     | $k\Omega$ |

| Total Harmonic Distortion                           | 1        | _     | 0.35  | 0.5   | %         |

| Output Noise Level (per stage)                      | 2        | _     | 180.0 | 400.0 | μVrms     |

| Onset of Clipping                                   | 3        | _     | 1.73  | _     | Vrms      |

| Gain Variation                                      | 4        | _     | _     | 0.1   | dB        |

| Interstage Isolation                                |          | _     | 60.0  | _     | dB        |

| "Trimmer" Stages (Ch1 - Ch3)                        |          |       |       |       |           |

| Gain                                                |          | -3.0  |       | +3.0  | dB        |

| Gain per Step (15 in No.)                           |          | _     | 0.43  | _     | dB        |

| Step Error                                          | 5        | _     | _     | ±0.2  | dB        |

| Input Impedance                                     |          | 100.0 | _     | _     | $k\Omega$ |

| "Volume" Stage (Ch4)                                |          |       |       |       |           |

| Gain                                                |          | -14.0 |       | +14.0 | dB        |

| Gain per Step (15 in No.)                           |          | _     | 2.0   | _     | dB        |

| Step Error                                          | 5        | _     | _     | ±0.4  | dB        |

| Input Impedance                                     |          | 50.0  | _     | _     | kΩ        |

| Timing (Figure 4)                                   |          |       |       |       |           |

| Serial Clock "High" Pulse Width (t <sub>PWH</sub> ) |          | 250   | _     | _     | ns        |

| Serial Clock "Low" Pulse Width (t <sub>PWL</sub> )  |          | 250   | _     | _     | ns        |

| Data Set-up Time (t <sub>DS</sub> )                 |          | 150   | _     | _     | ns        |

| Data Hold Time (t <sub>DH</sub> )                   |          | 50.0  | _     | _     | ns        |

| Load/Latch Pulse Width (t <sub>LLW</sub> )          |          | 150   | _     | _     | ns        |

| Load/Latch Delay (t <sub>lld</sub> )                |          | 200   | -     | _     | ns        |

| Load/Latch Over (t <sub>IIO</sub> )                 |          | _     | _     | 50.0  | ns        |

| Serial Data Clock Frequency                         |          | _     | _     | 2.0   | MHz       |

#### Notes

- 1. Gain Set 0dB, Input Level 1kHz -3.0dB (549mVrms).

- 2. With an a.c short-circuit input, measured in a 30kHz bandwidth.

- 3. See Figure 3.4. Over the temperature and supply voltage range.

- 5. With reference to a 1.0kHz signal.

## **Package Outlines**

The FX019 is available in the package styles outlined below. Mechanical package diagrams and specifications are detailed in Section 10 of this document. Pin 1 identification marking is shown on the relevant diagram and pins on all package styles number anti-clockwise when viewed from the top.

## **Handling Precautions**

The FX019 is a CMOS LSI circuit which includes input protection. However precautions should be taken to prevent static discharges which may cause damage.

**FX019DW** 16-pin plastic S.O.I.C. **(D4)**

Max. Body Length Max. Body Width 7.59mm O.20mm

# **Ordering Information**

FX019DW 16-pin plastic S.O.I.C. (D4)

FX019P 16-pin plastic DIL (P3)