# Spread Spectrum Frequency Timing Generator

### **Features**

- Maximized EMI suppression using Cypress's Spread Spectrum technology

- Generates a spread spectrum copy of the provided input

- · Integrated loop filter components

- . Operates with a 3.3V or 5V supply

- · Low-power CMOS design

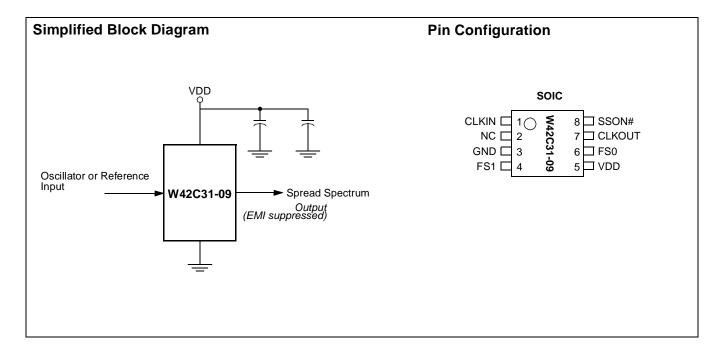

- Available in 8-pin SOIC (Small Outline Integrated Circuit)

### Overview

The W42C31-09 incorporates the latest advances in PLL spread spectrum frequency synthesizer techniques. By frequency modulating the output with a low-frequency carrier, EMI is greatly reduced. Use of this technology allows systems

to pass increasingly difficult EMI testing without resorting to costly shielding or redesign.

In a system, not only is EMI reduced in the various clock lines, but also in all signals which are synchronized to the clock. Therefore, the benefits of using this technology increase with the number of address and data lines in the system. The Simplified Block Diagram shows a simple implementation.

**Table 1. Frequency Spread Selection**

| W42C31-09 |     | Input Frequency | Output Frequency        |

|-----------|-----|-----------------|-------------------------|

| FS1       | FS0 | (MHz)           | (MHz)                   |

| 0         | 0   | 30 to 55        | f <sub>IN</sub> ±0.625% |

| 0         | 1   | 30 to 55        | f <sub>IN</sub> ±1.25%  |

| 1         | 0   | 30 to 55        | f <sub>IN</sub> ±2.5%   |

| 1         | 1   | 30 to 55        | f <sub>IN</sub> -3.75%  |

### **Pin Definitions**

| Pin Name | Pin No. | Pin<br>Type | Pin Description                                                                                                                                             |

|----------|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT   | 7       | 0           | Output Modulated Frequency: Frequency modulated copy of the unmodulated input clock.                                                                        |

| CLKIN    | 1       | I           | External Reference Frequency Input                                                                                                                          |

| NC       | 2       | I           | No Connect: This pin must be left unconnected.                                                                                                              |

| SSON#    | 8       | I           | Spread Spectrum Control (Active LOW): Pulling this input signal LOW turns the internal modulation waveform on. This pin has an internal pull-down resistor. |

| FS0:1    | 6, 4    | I           | Frequency Selection Bit 0: These pins select the frequency spreading characteristics. Refer to Table 1. These pins have internal pull-up resistors.         |

| VDD      | 5       | Р           | Power Connection: Connected to 3.3V or 5V power supply.                                                                                                     |

| GND      | 3       | G           | Ground Connection: This should be connected to the common ground plane.                                                                                     |

### **Functional Description**

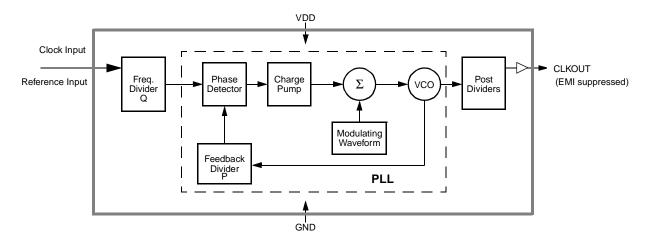

The W42C31-09 uses a phase-locked loop (PLL) to frequency modulate an input clock. The result is an output clock whose frequency is slowly swept over a narrow band near the input signal. The basic circuit topology is shown in Figure 1. The input reference signal is divided by Q and fed to the phase detector. A signal from the VCO is divided by P and fed back to the phase detector also. The PLL will force the frequency of the VCO output signal to change until the divided output signal and the divided reference signal match at the phase detector input. The output frequency is then equal to the ratio of P/Q times the reference frequency. (Note: For the W42C31-09 the output frequency is equal to the input frequency.) The unique feature of the Spread Spectrum Frequency Timing Generator is that a modulating waveform is superimposed at the input to the VCO. This causes the VCO output to be slowly swept across a predetermined frequency band.

Because the modulating frequency is typically 1000 times slower than the fundamental clock, the spread spectrum process has little impact on system performance.

### Frequency Selection With SSFTG

In Spread Spectrum Frequency Timing Generation, EMI reduction depends on the shape, modulation percentage, and frequency of the modulating waveform. While the shape and frequency of the modulating waveform are fixed, the modulation percentage may be varied.

Using frequency select bits (FS1:0 pins), various spreading percentages can be chosen (see *Table 1*).

A larger spreading percentage improves EMI reduction. However, large spread percentages may either exceed system maximum frequency ratings or lower the average frequency to a point where performance is affected. For these reasons, spreading percentages between  $\pm 0.5\%$  and  $\pm 2.5\%$  are most common.

The W42C31 features the ability to select from various spread spectrum characteristics. Selections specific to the W42C31-09 are shown in *Table 1*. Other spreading characteristics are available (see separate data sheets) or can be created with a custom mask. Also, other devices in the W42C31 family offer frequency multiplication in addition to the spread spectrum function. This will allow the use of less expensive fundamental mode crystals.

Figure 1. System Block Diagram (Concept, not actual implementation)

# Spread Spectrum Frequency Timing Generation

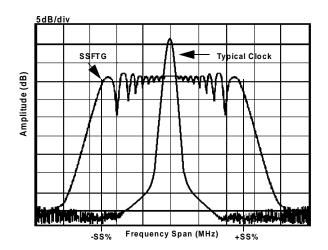

The benefits of using Spread Spectrum Frequency Timing Generation are depicted in *Figure 2*. An EMI emission profile of a clock harmonic is shown.

Contrast the typical clock EMI with the Cypress Spread Spectrum Frequency Timing Generation EMI. Notice the spike in the typical clock. This spike can make systems fail quasi-peak EMI testing. The FCC and other regulatory agencies test for peak emissions. With spread spectrum enabled, the peak energy is much lower (at least 8 dB) because the energy is spread out across a wider bandwidth.

### **Modulating Waveform**

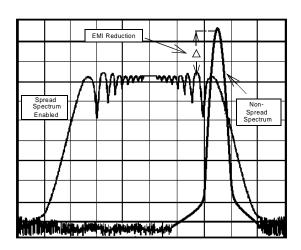

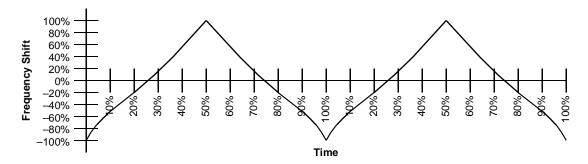

The shape of the modulating waveform is critical to EMI reduction. The modulation scheme used to accomplish the maximum reduction in EMI is shown in *Figure 3*. The period of the modulation is shown as a percentage of the period length along the X axis. The amount that the frequency is varied is shown along the Y axis, also shown as a percentage of the total frequency spread.

Cypress frequency selection tables express the modulation percentage in two ways. The first method displays the spreading frequency band as a percent of the programmed average output frequency, symmetric about the programmed average frequency. This method is always shown using the expression  $f_{Center} \pm X_{MOD}\%$  in the frequency spread selection table.

The second approach is to specify the maximum operating frequency and the spreading band as a percentage of this frequency. The output signal is swept from the lower edge of the band to the maximum frequency. The expression for this approach is  $f_{MAX}-X_{MOD}\%.$  Whenever this expression is used, Cypress has taken care to ensure that  $f_{MAX}$  will never be exceeded. This is important in applications where the clock drives components with tight maximum clock speed specifications.

#### SSON# Pin

An internal pull-down resistor defaults the chip into a spread spectrum mode. The SSON# pin enables the spreading feature when set LOW. The SSON# pin disables the spreading feature when set HIGH ( $V_{DD}$ ).

Figure 2. Typical Clock and SSFTG Comparison

Figure 3. Modulation Waveform Profile

### **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter           | Description                            | Rating       | Unit |

|---------------------|----------------------------------------|--------------|------|

| $V_{DD}$ , $V_{IN}$ | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>    | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>      | Operating Temperature                  | 0 to +70     | °C   |

| T <sub>B</sub>      | Ambient Temperature under Bias         | -55 to +125  | °C   |

| P <sub>D</sub>      | Power Dissipation                      | 0.5          | W    |

### DC Electrical Characteristics: $0^{\circ}$ C < $T_A$ < $70^{\circ}$ C, $V_{DD}$ = 3.3V $\pm 10\%$

| Parameter                      | Description            | Test Condition                               | Min | Тур | Max  | Unit |

|--------------------------------|------------------------|----------------------------------------------|-----|-----|------|------|

| I <sub>DD</sub>                | Supply Current         |                                              |     | 18  | 32   | mA   |

| t <sub>ON</sub>                | Power Up Time          | First locked clock cycle after<br>Power Good |     |     | 5    | ms   |

| V <sub>IL</sub> (Logic Inputs) | Input Low Voltage      |                                              |     |     | 0.8  | V    |

| V <sub>IL</sub> (CLKIN)        | Input Low Voltage      |                                              |     |     | .4   | V    |

| V <sub>IH</sub> (Logic Inputs) | Input High Voltage     |                                              | 2.4 |     |      | V    |

| V <sub>IH</sub> (CLKIN)        | Input High Voltage     |                                              | 2.8 |     |      | V    |

| V <sub>OL</sub>                | Output Low Voltage     | $I_{OL} = 21.6 \text{ mA}^{[1]}$             |     |     | 0.4  | V    |

| V <sub>OH</sub>                | Output High Voltage    | I <sub>OH</sub> = 31.5 mA <sup>[1]</sup>     | 2.5 |     |      | V    |

| I <sub>IL</sub>                | Input Low Current      | Note 2                                       |     |     | -100 | μΑ   |

| I <sub>IH</sub>                | Input High Current     | Note 2                                       |     |     | 10   | μΑ   |

| I <sub>OL</sub>                | Output Low Current     | @ 0.4V, V <sub>DD</sub> = 3.3V               |     | 15  |      | mA   |

| I <sub>OH</sub>                | Output High Current    | @ 2.4V, V <sub>DD</sub> = 3.3V               |     | 15  |      | mA   |

| C <sub>I</sub>                 | Input Capacitance      | All pins except CLKIN                        |     |     | 7    | pF   |

| C <sub>I</sub>                 | Input Capacitance      | CLKIN pin only                               |     | 6   | 10   | pF   |

| R <sub>P</sub>                 | Input Pull-Up Resistor |                                              |     | 500 |      | kΩ   |

| Z <sub>OUT</sub>               | Clock Output Impedance |                                              |     | 25  |      | Ω    |

### Notes:

Output driver is full CMOS.

Inputs FS1:0 have a pull-up resistor, Input SSON# has a pull-down resistor.

# DC Electrical Characteristics: $0^{\circ}\text{C} < T_A < 70^{\circ}\text{C}, \ V_{DD} = 5\text{V} \pm 10\%$

| Parameter                      | Description            | Test Condition                               | Min                | Тур | Max                 | Unit |

|--------------------------------|------------------------|----------------------------------------------|--------------------|-----|---------------------|------|

| I <sub>DD</sub>                | Supply Current         |                                              |                    | 30  | 45                  | mA   |

| t <sub>ON</sub>                | Power Up Time          | First locked clock cycle after<br>Power Good |                    |     | 5                   | ms   |

| V <sub>IL</sub> (Logic Inputs) | Input Low Voltage      |                                              |                    |     | 0.15V <sub>DD</sub> | V    |

| V <sub>IL</sub> (CLKIN)        | Input Low Voltage      |                                              |                    |     | 0.4                 | V    |

| V <sub>IH</sub> (Logic Inputs) | Input High Voltage     |                                              | 0.7V <sub>DD</sub> |     |                     | V    |

| V <sub>IH</sub> (CLKIN)        | Input High Voltage     |                                              | 4.2                |     |                     | V    |

| V <sub>OL</sub>                | Output Low Voltage     | $I_{OL} = 25.7 \text{mA}$                    |                    |     | 0.4                 | V    |

| V <sub>OH</sub>                | Output High Voltage    | I <sub>OH</sub> = 118.mA                     | 2.5                |     |                     | V    |

| I <sub>IL</sub>                | Input Low Current      | Note 2                                       |                    |     | -100                | μΑ   |

| I <sub>IH</sub>                | Input High Current     | Note 2                                       |                    |     | 10                  | μΑ   |

| I <sub>OL</sub>                | Output Low Current     | @ 0.4V, V <sub>DD</sub> = 5V                 |                    | 24  |                     | mA   |

| I <sub>OH</sub>                | Output High Current    | @ 2.4V, V <sub>DD</sub> = 5V                 |                    | 24  |                     | mA   |

| C <sub>I</sub>                 | Input Capacitance      | All pins except CLKIN                        |                    |     | 7                   | pF   |

| C <sub>I</sub>                 | Input Capacitance      | CLKIN pin only                               |                    | 6   | 10                  | pF   |

| R <sub>P</sub>                 | Input Pull-Up Resistor |                                              |                    | 500 |                     | kΩ   |

| Z <sub>OUT</sub>               | Clock Output Impedance |                                              |                    | 25  |                     | Ω    |

## AC Electrical Characteristics: $T_A = 0$ °C to +70°C, $V_{DD} = 3.3V \pm 10\%$

| Symbol            | Parameter              | Test Condition                                                                        | Min | Тур | Max | Unit |

|-------------------|------------------------|---------------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>IN</sub>   | Input Frequency        | Input Clock                                                                           | 30  | 40  | 55  | MHz  |

| f <sub>OUT</sub>  | Output Frequency       | Spread Off                                                                            | 30  | 40  | 55  | MHz  |

| t <sub>R</sub>    | Output Rise Time       | V, 15-pF load 0.8 – 2.4                                                               |     | 2   | 5   | ns   |

| t <sub>F</sub>    | Output Fall Time       | V, 15-pF load 2.4 – 0.8                                                               |     | 2   | 5   | ns   |

| t <sub>OD</sub>   | Output Duty Cycle      | 15-pF load                                                                            | 40  |     | 60  | %    |

| t <sub>ID</sub>   | Input Duty Cycle       |                                                                                       | 40  |     | 60  | %    |

| t <sub>JCYC</sub> | Jitter, Cycle-to-Cycle |                                                                                       |     | 250 | 300 | ps   |

|                   | Harmonic Reduction     | f <sub>out</sub> = 40 MHz, third harmonic<br>measured, reference board,<br>15-pF load | 8   |     |     | dB   |

## AC Electrical Characteristics: $T_A = 0$ °C to +70°C, $V_{DD} = 5V \pm 10\%$

| Symbol            | Parameter              | Test Condition                                                                        | Min | Тур | Max | Unit |

|-------------------|------------------------|---------------------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>IN</sub>   | Input Frequency        | Input Clock                                                                           | 30  | 40  | 55  | MHz  |

| f <sub>OUT</sub>  | Output Frequency       | Spread Off                                                                            | 30  | 40  | 55  | MHz  |

| t <sub>R</sub>    | Output Rise Time       | V, 15-pF load 0.8 – 2.4                                                               |     | 2   | 5   | ns   |

| t <sub>F</sub>    | Output Fall Time       | V, 15-pF load 2.4 – 0.8                                                               |     | 2   | 5   | ns   |

| t <sub>OD</sub>   | Output Duty Cycle      | 15-pF load                                                                            | 40  |     | 60  | %    |

| t <sub>ID</sub>   | Input Duty Cycle       |                                                                                       | 40  |     | 60  | %    |

| t <sub>JCYC</sub> | Jitter, Cycle-to-Cycle |                                                                                       |     | 250 | 300 | ps   |

|                   | Harmonic Reduction     | f <sub>out</sub> = 40 MHz, third harmonic<br>measured, reference board,<br>15-pF load | 8   |     |     | dB   |

### **Application Information**

### **Recommended Circuit Configuration**

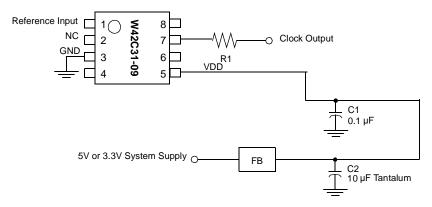

For optimum performance in system applications the power supply decoupling scheme shown in *Figure 4* should be used.

$V_{DD}$  decoupling is important to both reduce phase jitter and EMI radiation. The 0.1- $\mu F$  decoupling capacitor should be placed as close to the  $V_{DD}$  pin as possible, otherwise the in-

creased trace inductance will negate its decoupling capability. The 10- $\mu$ F decoupling capacitor shown should be a tantalum type. For further EMI protection, the V<sub>DD</sub> connection can be made via a ferrite bead, as shown.

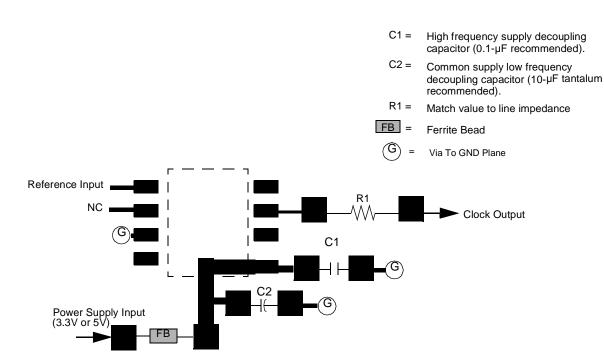

### **Recommended Board Layout**

Figure 5 shows a recommended 2-layer board layout.

Figure 4. Recommended Circuit Configuration

Figure 5. Recommended Board Layout (2-Layer Board)

### **Ordering Information**

| Ordering Code | Freq. Mask<br>Code | Package<br>Name | Package Type                 |

|---------------|--------------------|-----------------|------------------------------|

| W42C31        | 09                 | G               | 8-pin Plastic SOIC (150-mil) |

Document #: 38-00799-B

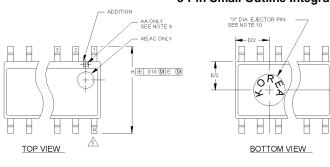

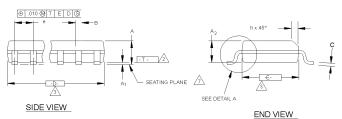

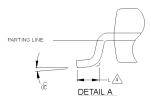

### Package Diagram

### 8-Pin Small Outline Integrated Circuit (SOIC, 150-mil)

#### NOTES:

- /1\ MAXIMUM DIE THICKNESS ALLOWABLE IS .015.

- 2 DIMENSIONING & TOLERANCES PER ANSI. Y14.5M 1982.

- ③"T" IS A REFERENCE DATUM.

- 4 "D" & "E" ARE REFERENCE DATUMS AND DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS, BUT DOES INCLUDE MOLD MISMATCH AND ARE MEASURED AT THE MOLD PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 INCHES PER SIDE.

- 5. "L" IS THE LENGTH OF TERMINAL FOR SOLDERING TO A SUBSTRATE.

- 6. "N" IS THE NUMBER OF TERMINAL POSITIONS.

- TERMINAL POSITIONS ARE SHOWN FOR

- REFERENCE ONLY.

- 8 FORMED LEADS SHALL BE PLANAR WITH RESPECT TO ONE ANOTHER WITHIN .003 INCHES AT SEATING PLANE.

- THE APPEARANCE OF PIN #1 I.D ON THE 8 LD IS OPTIONAL, ROUND TYPE ON SINGLE LEADFRAME AND RECTANGULAR TYPE ON MATRIX LEADFRAME.

- 10. COUNTRY OF ORIGIN LOCATION AND EJECTOR PIN ON PACKAGE BOTTOM IS OPTIONAL AND DEPEND ON ASSEMBLY LOCATION.

- 11, CONTROLLING DIMENSION: INCHES

### THIS TABLE IN INCHES

| S      |                | COMMON     |       |                  | NOTE   |      | 3    |      | 5  |

|--------|----------------|------------|-------|------------------|--------|------|------|------|----|

| M<br>B | D              | DIMENSIONS |       |                  | VARI-  |      | D    |      | N  |

| °L     | MIN.           | NOM.       | MAX.  | <sup>"О</sup> ТЕ | ATIONS | MIN. | NOM. | MAX. |    |

| Α      | .061           | .064       | .068  |                  | AA     | .189 | .194 | .196 | 8  |

| A,     | .004           | .006       | .0098 |                  | AB     | .337 | .342 | .344 | 14 |

| $A_2$  | .055           | .058       | .061  |                  | AC     | .386 | .391 | .393 | 16 |

| В      | .0138          | .016       | .0192 |                  |        |      |      |      |    |

| С      | .0075          | .008       | .0098 |                  |        |      |      |      |    |

| D      | SEE VARIATIONS |            |       | 3                |        |      |      |      |    |

| E      | .150           | .155       | .157  |                  |        |      |      |      |    |

| е      |                | .050 BSC   |       |                  |        |      |      |      |    |

| Н      | .230           | .236       | .244  |                  |        |      |      |      |    |

| h      | .010           | .013       | .016  |                  |        |      |      |      |    |

| L      | .016           | .025       | .035  |                  |        |      |      |      |    |

| Ŋ      | SEE VARIATIONS |            |       | 5                |        |      |      |      |    |

| oc.    | 0°             | 5°         | 8°    |                  |        |      |      |      |    |

| X      | .085           | .093       | .100  |                  |        |      |      |      |    |

### THIS TABLE IN MILLIMETERS

| S              |                | COMMON    |      |                | NOTE   |      | 3    |      | 5  |

|----------------|----------------|-----------|------|----------------|--------|------|------|------|----|

| M<br>B         | DIMENSIONS     |           |      | N O            | VARI-  |      | D    |      | N  |

| °L             | MIN.           | NOM.      | MAX. | T <sub>E</sub> | ATIONS | MIN. | NOM. | MAX. |    |

| Α              | 1.55           | 1.63      | 1.73 |                | AA     | 4.80 | 4.93 | 4.98 | 8  |

| A <sub>1</sub> | 0.127          | 0.15      | 0.25 |                | AB     | 8.58 | 8.69 | 8.74 | 14 |

| A <sub>2</sub> | 1.40           | 1.47      | 1.55 |                | AC     | 9.80 | 9.93 | 9.98 | 16 |

| В              | 0.35           | 0.41      | 0.49 |                |        |      |      |      |    |

| С              | 0.19           | 0.20      | 0.25 |                |        |      |      |      |    |

| D              | SEE            | VARIATION | IS   | 3              |        |      |      |      |    |

| E              | 3.81           | 3.94      | 3.99 |                |        |      |      |      |    |

| е              |                | 1.27 BSC  |      |                |        |      |      |      |    |

| Н              | 5.84           | 5.99      | 6.20 |                |        |      |      |      |    |

| h              | 0.25           | 0.33      | 0.41 |                |        |      |      |      |    |

| L              | 0.41           | 0.64      | 0.89 |                |        |      |      |      |    |

| Ŋ              | SEE VARIATIONS |           |      | 5              |        |      |      |      |    |

| œ              | 0°             | 5°        | 8°   |                |        |      |      |      |    |

| X              | 2.16           | 2.36      | 2.54 |                |        |      |      |      |    |

<sup>©</sup> Cypress Semiconductor Corporation, 2000. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.