# Spread Aware™, Ten/Eleven Output Zero Delay Buffer

#### **Features**

#### Spread Aware<sup>™</sup>—designed to work with SSFTG reference signals

- Well suited to both 100- and 133-MHz designs

- Ten (-09B) or Eleven (-10B) LVCMOS/LVTTL outputs

- Single output enable pin for -10 version, dual pins on -09 devices allow shutting down a portion of the outputs.

- · 3.3V power supply

- On board 25 $\Omega$  damping resistors

- Available in 24-pin TSSOP package

### **Key Specifications**

| Operating Voltage:     | 3.3V±10%                            |

|------------------------|-------------------------------------|

| Operating Range:       | 25 MHz < f <sub>OUT</sub> < 140 MHz |

| Cycle-to-Cycle Jitter: | <150 ps                             |

| Output to Output Skew: | <100 ps                             |

| Phase Error Jitter:    | <125 ps                             |

#### **Block Diagram Pin Configurations FBIN** - FBOUT □ CLK AGND I 24 □ AVDD VDD 2 23 IJ VDD Q0 3 22 Q1 4 21 Q9 Q2 II 20 **□** Q8 OE0:4 GND I 6 19 □ GND GND I 7 □ GND 18 OE 17 Q3 II 8 ■ Q7 Q4 II 9 ☐ Q6 16 **□** Q5 VDD II 10 15 OE5:8 OE II 11 14 FBOUT I 12 □ FBIN 13 □ CLK **AGND** 24 configuration of these blocks dependent upon specific option being used VDD 2 23 oxdot AVDD Q0 II 3 22 □ VDD Q1 4 21 Q8 Q2 Ш 5 20 Ⅱ Q7 GND 6 19 GND GND □ 7 18 $\square$ GND Q3 II П Q6 8 17 П Q4 II 9 16 Q5 VDD □ □ VDD 10 15 OE0:4 □ 14 □ OE5:8 □ FBIN FBOUT I 13

Spread Aware is a trademark of Cypress Semiconductor Corporation.

#### **Pin Definitions**

| Pin<br>Name | Pin No.<br>(-09B)                   | Pin No.<br>(-10B)                   | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------------------------------|-------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK         | 24                                  | 24                                  | I           | Reference Input: Output signals Q0:9 will be synchronized to this signal.                                                                                                                                                                                                                                                        |

| FBIN        | 13                                  | 13                                  | I           | Feedback Input: This input must be fed by one of the outputs (typically FBOUT) to ensure proper functionality. If the trace between FBIN and FBOUT is equal in length to the traces between the outputs and the signal destinations, then the signals received at the destinations will be synchronized to the CLK signal input. |

| Q0:8        | 3, 4, 5, 8,<br>9, 16, 17,<br>20, 21 | 3, 4, 5, 8,<br>9, 15, 16,<br>17, 20 | 0           | <b>Integrated Series Resistor Outputs:</b> The frequency and phase of the signals provided by these pins will be equal to the reference signal if properly laid out. Each output has a $25\Omega$ series damping resistor integrated.                                                                                            |

| Q9          | n/a                                 | 21                                  | 0           | Integrated Series Resistor Output: The frequency and phase of the signal provided by this pin will be equal to the reference signal if properly laid out. This output has a $25\Omega$ series damping resistor integrated.                                                                                                       |

| FBOUT       | 12                                  | 12                                  | 0           | <b>Feedback Output:</b> This output has a 25 $\Omega$ series resistor integrated on chip. Typically it is connected directly to the FBIN input with a trace equal in length to the traces between outputs Q0:9 and the destination points of these output signals.                                                               |

| AVDD        | 23                                  | 23                                  | Р           | <b>Analog Power Connection:</b> Connect to 3.3V. Use ferrite beads to help reduce noise for optimal jitter performance.                                                                                                                                                                                                          |

| AGND        | 1                                   | 1                                   | G           | Analog Ground Connection: Connect to common system ground plane.                                                                                                                                                                                                                                                                 |

| VDD         | 2, 10, 15,<br>22                    | 2, 10, 14,<br>22                    | Р           | <b>Power Connections:</b> Connect to 3.3V. Use ferrite beads to help reduce noise for optimal jitter performance.                                                                                                                                                                                                                |

| GND         | 6, 7, 18,<br>19                     | 6, 7, 18,<br>19                     | G           | Ground Connections: Connect to common system ground plane.                                                                                                                                                                                                                                                                       |

| OE          | n/a                                 | 11                                  | I           | <b>Output Enable Input:</b> Tie to $V_{DD}$ (HIGH, 1) for normal operation. when brought to GND (LOW, 0) all outputs are disabled to a LOW state.                                                                                                                                                                                |

| OE0:4       | 11                                  | n/a                                 | I           | <b>Output Enable Input:</b> Tie to $V_{DD}$ (HIGH, 1) for normal operation. when brought to GND (LOW, 0) outputs Q0:4 are disabled to a LOW state.                                                                                                                                                                               |

| OE5:8       | 14                                  | n/a                                 | I           | <b>Output Enable Input:</b> Tie to $V_{DD}$ (HIGH, 1) for normal operation. when brought to GND (LOW, 0) outputs Q5:8 are disabled to a LOW state.                                                                                                                                                                               |

#### Overview

The W132 is a PLL-based clock driver designed for use in dual inline memory modules. The clock driver has output frequencies of up to 133 MHz and output to output skews of less than 250 ps. The W132 provides minimum cycle-to-cycle and long term jitter, which is of significant importance to meet the tight input-to-input skew budget in DIMM applications.

The current generation of 256 and 512 megabyte memory modules needs to support 100-MHz clocking speeds. Especially for cards configured in 16x4 or 8x8 format, the clock signal provided from the motherboard is generally not strong enough to meet all the requirements of the memory and logic

on the DIMM. The W132 takes in the signal from the mother-board and buffers out clock signals with enough drive to support all the DIMM board clocking needs. The W132 is also designed to meet the needs of new PC133 SDRAM designs, operating to 133 MHz.

The W132 was specifically designed to accept SSFTG signals currently being used in motherboard designs to reduce EMI. Zero delay buffers which are not designed to pass this feature through may cause skewing failures.

Output enable pins allow for shutdown of output when they are not being used. This reduces EMI and power consumption.

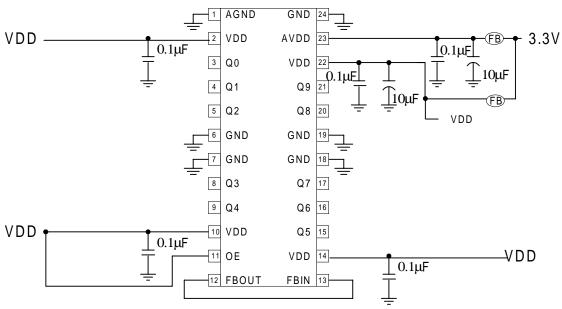

Figure 1. Schematic

## **Spread Aware**

Many systems being designed now utilize a technology called Spread Spectrum Frequency Timing Generation. Cypress has been one of the pioneers of SSFTG development, and we designed this product so as not to filter off the Spread Spectrum feature of the Reference input, assuming it exists. When a zero delay buffer is not designed to pass the SS feature through, the result is a significant amount of tracking skew which may cause problems in systems requiring synchronization.

For more details on Spread Spectrum timing technology, please see the Cypress application note titled, "EMI Suppression Techniques with Spread Spectrum Frequency Timing Generator (SSFTG) ICs."

#### **How to Implement Zero Delay**

Typically, zero delay buffers (ZDBs) are used because a designer wants to provide multiple copies of a clock signal in phase with each other. The whole concept behind ZDBs is that the signals at the destination chips are all going HIGH at the same time as the input to the ZDB. In order to achieve this, layout must compensate for trace length between the ZDB and the target devices. The method of compensation is described below.

External feedback is the trait that allows for this compensation. The PLL on the ZDB will cause the feedback signal to be in phase with the reference signal. When laying out the board, match the trace lengths between the output being used for feed back and the FBIN input to the PLL.

If it is desirable to either add a little delay, or slightly precede the input signal, this may also be affected by either making the trace to the FBIN pin a little shorter or a little longer than the traces to the devices being clocked.

### **Inserting Other Devices in Feedback Path**

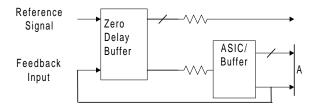

Another nice feature available due to the external feedback is the ability to synchronize signals up to the signal coming from some other device. This implementation can be applied to any device (ASIC, multiple output clock buffer/driver, etc.) which is put into the feedback path.

Referring to Figure 2, if the traces between the ASIC/buffer and the destination of the clock signal(s) (A) are equal in length to the trace between the buffer and the FBIN pin, the signals at the destination(s) device will be driven high at the same time the Reference clock provided to the ZDB goes high. Synchronizing the other outputs of the ZDB to the outputs form the ASIC/Buffer is more complex however, as any propagation delay in the ASIC/Buffer must be accounted for.

Figure 2. 6 Output Buffer in the Feedback Path

# **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter                         | Description                            | Rating       | Unit |

|-----------------------------------|----------------------------------------|--------------|------|

| V <sub>DD</sub> , V <sub>IN</sub> | Voltage on any pin with respect to GND | -0.5 to +7.0 | V    |

| T <sub>STG</sub>                  | Storage Temperature                    | -65 to +150  | °C   |

| T <sub>A</sub>                    | Operating Temperature                  | 0 to +70     | °C   |

| T <sub>B</sub>                    | Ambient Temperature under Bias         | -55 to +125  | °C   |

| P <sub>D</sub>                    | Power Dissipation                      | 0.5          | W    |

# **DC Electrical Characteristics**: $T_A = 0$ °C to 70°C, $V_{DD} = 3.3$ V $\pm 10$ %

| Parameter       | Description         | Test Condition           | Min | Тур | Max | Unit |

|-----------------|---------------------|--------------------------|-----|-----|-----|------|

| I <sub>DD</sub> | Supply Current      | Unloaded, 100 MHz        |     |     | 200 | mA   |

| V <sub>IL</sub> | Input Low Voltage   |                          |     |     | 0.8 | V    |

| V <sub>IH</sub> | Input High Voltage  |                          | 2.0 |     |     | V    |

| V <sub>OL</sub> | Output Low Voltage  | I <sub>OL</sub> = 12 mA  |     |     | 0.8 | V    |

| V <sub>OH</sub> | Output High Voltage | I <sub>OH</sub> = −12 mA | 2.1 |     |     | V    |

| I <sub>IL</sub> | Input Low Current   | V <sub>IN</sub> = 0V     |     |     | 50  | μΑ   |

| I <sub>IH</sub> | Input High Current  | $V_{IN} = V_{DD}$        |     |     | 50  | μΑ   |

# AC Electrical Characteristics: $T_A = 0$ °C to +70°C, $V_{DD} = 3.3$ V ±10%

| Parameter          | Description                                  | Test Condition                 | Min  | Тур | Max | Unit |

|--------------------|----------------------------------------------|--------------------------------|------|-----|-----|------|

| f <sub>OUT</sub>   | Output Frequency                             | 30-pF load <sup>[4]</sup>      | 25   |     | 140 | MHz  |

| t <sub>R</sub>     | Output Rise Time                             | 0.8V to 2.0V, 30-pF load       |      |     | 2.1 | ns   |

| t <sub>F</sub>     | Output Fall Time                             | 2.0V to 0.8V, 30-pF load       |      |     | 2.5 | ns   |

| t <sub>ICLKR</sub> | Input Clock Rise Time <sup>[1]</sup>         |                                |      |     | 4.5 | ns   |

| t <sub>ICLKF</sub> | Input Clock Fall Time <sup>[1]</sup>         |                                |      |     | 4.5 | ns   |

| t <sub>PEJ</sub>   | CLK to FBIN Skew Variation <sup>[2, 3]</sup> | Measured at V <sub>DD</sub> /2 | -350 | 0   | 350 | ps   |

| t <sub>SK</sub>    | Output to Output Skew                        | All outputs loaded equally     | -100 | 0   | 100 | ps   |

| t <sub>D</sub>     | Duty Cycle                                   | 30-pF load                     | 43   | 50  | 58  | %    |

| t <sub>LOCK</sub>  | PLL Lock Time                                | Power supply stable            |      |     | 1.0 | ms   |

| t <sub>JC</sub>    | Jitter, Cycle-to-Cycle                       |                                |      |     | 150 | ps   |

#### Notes:

- Longer input rise and fall time will degrade skew and jitter performance.

Skew is measured at V<sub>DD</sub>/2 on rising edges.

Duty cycle is measured at V<sub>DD</sub>/2.

- 4. Production tests are run at 133 MHz.

# **Ordering Information**

| Ordering Code | Option     | Package Type     |  |  |

|---------------|------------|------------------|--|--|

| W132          | -09B, -10B | X = 24-pin TSSOP |  |  |

Document #: 38-00792

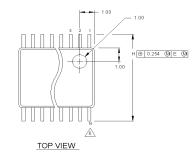

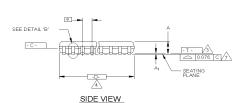

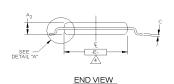

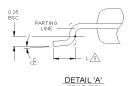

### **Package Diagram**

#### 24-Pin Thin Shrink Small Outline Package (TSSOP)

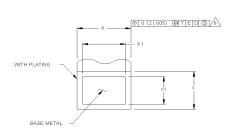

DETAIL "C" (SEE NOTE 9)

- TO A UP ARE REFERENCE ON TUNE AND DO NOT

TO A UP ARE REFERENCE ON THE AND TO NOT

TO A UP AND THE AND

- EDICATED VITHE LOWER PAULOS ON THE POUT. MINIMAM SPACE BETWEEN PROTRUSIONS ON THE POUT. MINIMAM DE DE 14 MINIMAM SEE DETAIL SE AND C. 10 DE LOTE MAND DO .0.10 DE LOTE MAND DE .0.10 DE .

# THIS TABLE IN MILLIMETERS

| S              | COMMON           |           |       |                   | NOTE   |      | 4    |      | 6  |

|----------------|------------------|-----------|-------|-------------------|--------|------|------|------|----|

| M<br>B         | DIMENSIONS       |           |       | N <sub>O</sub>    | VARI-  |      | D    |      | N  |

| 2              | MIN.             | NOM.      | MAX.  | NO <sub>T</sub> E | ATIONS | MIN. | NOM. | MAX. |    |

| Α              |                  |           | 1.10  |                   | AA     | 2.90 | 3.00 | 3.10 | 8  |

| A <sub>1</sub> | 0.05             | 0.10      | 0.15  |                   | AB     | 4.90 | 5.00 | 5.10 | 14 |

| A <sub>2</sub> | 0.85             | 0.90      | 0.95  |                   | AC     | 4.90 | 5.00 | 5.10 | 16 |

| b              | 0.19             | -         | 0.30  | 8                 | AD     | 6.40 | 6.50 | 6.60 | 20 |

| b1             | 0.19             | 0.22      | 0.25  |                   | AE     | 7.70 | 7.80 | 7.90 | 24 |

| С              | 0.090            | -         | 0.20  |                   | AF     | 9.60 | 9.70 | 9.80 | 28 |

| c1             | 0.090            | 0.127     | 0.135 |                   |        |      |      |      |    |

| D              | SEE              | VARIATION | IS    | 4                 |        |      |      |      |    |

| E              | 4.30             | 4.40      | 4.50  | 4                 |        |      |      |      |    |

| е              |                  | 0.65 BSC  |       |                   |        |      |      |      |    |

| Н              | 6.25             | 6.40      | 6.50  |                   |        |      |      |      |    |

| L              | 0.50             | 0.60      | 0.70  | 5                 |        |      |      |      |    |

| Ň              | N SEE VARIATIONS |           |       | 6                 |        |      |      |      |    |

| oc oc          | 0°               | 4°        | 8°    |                   |        |      |      |      |    |

#### THIS TABLE IN INCHES

| S              |           | COMMO     | VI.   |                               | NOTE   |              | 4    |       | 6  |

|----------------|-----------|-----------|-------|-------------------------------|--------|--------------|------|-------|----|

| Y M            |           |           |       | N                             |        | <del>4</del> |      |       | N  |

| B              |           |           |       | N <sub>O</sub> T <sub>E</sub> | VARI-  | NAINI        |      | BAAV. | IN |

| L              | MIN.      | NOM.      | MAX.  | E                             | ATIONS | MIN.         | NOM. | MAX.  |    |

| Α              |           |           | .0433 |                               | AA     | .114         | .118 | .122  | 8  |

| A <sub>1</sub> | .002      | .004      | .006  |                               | AB     | .193         | .197 | .201  | 14 |

| A2             | .0335     | .0354     | .0374 |                               | AC     | .193         | .197 | .201  | 16 |

| b              | .0075     | -         | .0118 | 8                             | AD     | .252         | .256 | .260  | 20 |

| b1             | .0075     | .0087     | .0098 |                               | AE     | .303         | .307 | .311  | 24 |

| С              | .0035     | -         | .0079 |                               | AF     | .378         | .382 | .386  | 28 |

| c1             | .0035     | .0050     | .0053 |                               |        |              |      |       |    |

| D              | SEE       | VARIATION | IS    | 4                             |        |              |      |       |    |

| E              | .169      | .173      | .177  | 4                             |        |              |      |       |    |

| е              | .0256 BSC |           |       |                               |        |              |      |       |    |

| H              | .246      | .252      | .256  |                               |        |              |      |       |    |

| L              | .020      | .024      | .028  | 5                             |        |              |      |       |    |

| Ŋ              |           |           |       | 6                             |        |              |      |       |    |

| οč             | 0° 4° 8°  |           |       |                               |        |              |      |       |    |

\*VARIATION AF IS DESIGNED BUT NOT TOOLED\*