# Spread Spectrum Desktop/Notebook System Frequency Generator

#### **Features**

- Maximized EMI suppression using Cypress's Spread Spectrum Technology

- Reduces measured EMI by as much as 10 dB

- I<sup>2</sup>C programmable to 133 MHz

- · Two skew-controlled copies of CPU output

- SEL100/66# selects CPU frequency (100 or 66.8 MHz)

- Seven copies of PCI output (synchronous w/CPU output)

- One copy of 14.31818-MHz IOAPIC output

- One copy of 48-MHz USB output

- Selectable 24-/48-MHz clock is determined by resistor straps on power-up

- One high-drive output buffer that produces a copy of the 14.318-MHz reference

- Isolated core VDD pin for noise reduction

## **Key Specifications**

| Supply Voltages:             | $V_{DDQ3} = 3.3V \pm 5\%$<br>$V_{DDQ2} = 2.5V \pm 5\%$ |

|------------------------------|--------------------------------------------------------|

| CPU Cycle to Cycle Jitter:   | 200 ps                                                 |

| CPU, PCI Output Edge Rate:   | ≥1 V/ns                                                |

| CPU0:1 Output Skew:          | 175 ps                                                 |

| PCI_F, PCI1:6 Output Skew:   | 500 ps                                                 |

| CPU to PCI Skew: 1.5 to 4    | I.0 ns (CPU Leads)                                     |

| REF2X/SEL48#, SCLOCK, SDATA: | 250-k $\Omega$ pull-up                                 |

**Note:** Internal pull-up resistors should not be relied upon for setting I/O pins HIGH.

Table 1. Pin Selectable Frequency

| SEL100/66# | CPU(0:1) | PCI      |  |  |

|------------|----------|----------|--|--|

| 1          | 100 MHz  | 33.3 MHz |  |  |

| 0          | 66.8 MHz | 33.4 MHz |  |  |

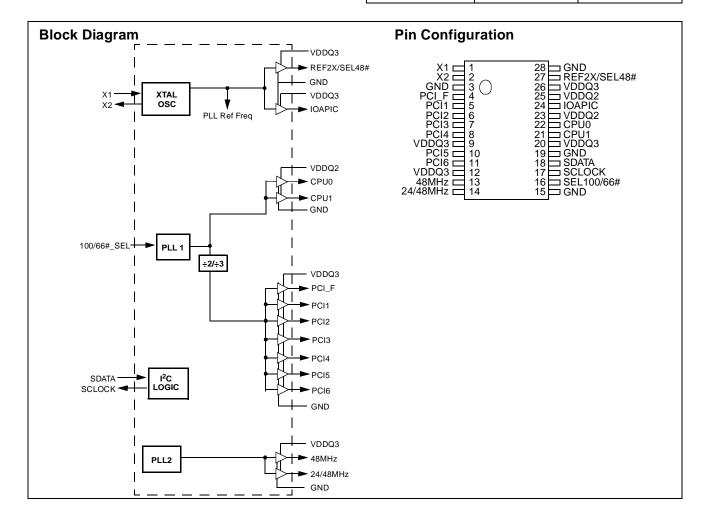

## **Pin Definitions**

| Pin Name        | Pin<br>No.               | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|--------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU0:1          | 22, 21                   | 0           | CPU Clock Outputs 0 through 1: These two CPU clocks run at a frequency set by SEL100/66#. Output voltage swing is set by the voltage applied to VDDQ2.                                                                                                                                                                                                                                        |

| PCI1:6<br>PCI_F | 5, 6, 7, 8, 10,<br>11, 4 | 0           | <b>PCI Bus Clock Outputs 1 through 6 and PCI_F:</b> These seven PCI clock outputs run synchronously to the CPU clock. Voltage swing is set by the power connection to VDDQ3.                                                                                                                                                                                                                  |

| IOAPIC          | 24                       | 0           | I/O APIC Clock Output: Provides 14.318-MHz fixed frequency. The output voltage swing is set by the power connection to VDDQ2.                                                                                                                                                                                                                                                                 |

| 48MHz           | 13                       | 0           | <b>48-MHz Output:</b> Fixed 48-MHz USB clock. Output voltage swing is controlled by voltage applied to VDDQ3.                                                                                                                                                                                                                                                                                 |

| 24/48MHz        | 14                       | 0           | 24-MHz or 48-MHz Output: Frequency is set by the state of pin 27 on power-up.                                                                                                                                                                                                                                                                                                                 |

| REF2X/SEL48#    | 27                       | I/O         | <b>I/O Dual-Function REF2X and SEL48# pin:</b> Upon power-up, the state of SEL48# is latched. The initial state is set by either a 10K resistor to GND or to V <sub>DD</sub> . A 10K resistor to GND causes pin 14 to output 48 MHz. If the pin is strapped to V <sub>DD</sub> pin 14 will output 24 MHz. After 2 ms, the pin becomes a high-drive output that produces a copy of 14.318 MHz. |

| SEL100/66#      | 16                       | I           | Frequency Selection Input: Selects CPU clock frequency as shown in Table 1 on page 1.                                                                                                                                                                                                                                                                                                         |

| SDATA           | 18                       | I/O         | $\it P^2C$ Data Pin: Data should be presented to this input as described in the $\it I^2C$ section of this data sheet. Internal 250-kΩ pull-up resistor.                                                                                                                                                                                                                                      |

| SCLOCK          | 17                       | I           | <b>I</b> <sup>2</sup> C clock Pin: The I <sup>2</sup> C data clock should be presented to this input as described in the I <sup>2</sup> C section of this data sheet.                                                                                                                                                                                                                         |

| X1              | 1                        | I           | Crystal Connection or External Reference Frequency Input: Connect to either a 14.318-MHz crystal or other reference signal.                                                                                                                                                                                                                                                                   |

| X2              | 2                        | I           | <b>Crystal Connection:</b> An input connection for an external 14.318-MHz crystal. If using an external reference, this pin must be left unconnected.                                                                                                                                                                                                                                         |

| VDDQ3           | 9, 12, 20, 26            | Р           | <b>Power Connection:</b> Power supply for core logic and PLL circuitry, PCI, 48/24MHz, and Reference output buffers. Connect to 3.3V supply.                                                                                                                                                                                                                                                  |

| VDDQ2           | 23, 25                   | Р           | <b>Power Connection:</b> Power supply for IOAPIC and CPU output buffers. Connect to 2.5V supply.                                                                                                                                                                                                                                                                                              |

| GND             | 3, 15, 19, 28            | G           | <b>Ground Connections:</b> Connect all ground pins to the common system ground plane.                                                                                                                                                                                                                                                                                                         |

### **Functional Description**

#### I/O Pin Operation

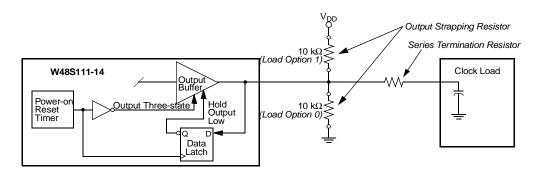

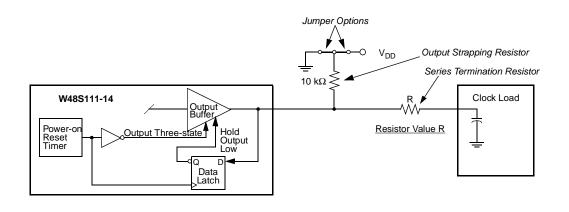

Pin 27 is a dual-purpose I/O pin. Upon power-up this pin acts as a logic input, allowing the determination of assigned device functions. A short time after power-up, the logic state of the pin is latched and the pin becomes a clock output. This feature reduces device pin count by combining clock outputs with input select pins.

An external 10-k $\Omega$  "strapping" resistor is connected between the I/O pin and ground or V<sub>DD</sub>. Connection to ground sets a latch to "0," connection to V<sub>DD</sub> sets a latch to "1." *Figure 1* and *Figure 2* show two suggested methods for strapping resistor connections.

Upon W48S111-14 power-up, the first 2 ms of operation is used for input logic selection. During this period, the Reference clock output buffer is three-stated, allowing the output strapping resistor on the I/O pin to pull the pin and its associated capacitive clock load to either a logic HIGH or LOW state. At the end of the 2-ms period, the established logic "0" or "1" condition of the I/O pin is then latched. Next the output buffer

is enabled, which converts the I/O pin into an operating clock output. The 2-ms timer is started when  $V_{DD}$  reaches 2.0V. The input bit can only be reset by turning  $V_{DD}$  off and then back on again.

It should be noted that the strapping resistor has no significant effect on clock output signal integrity. The drive impedance of clock output is  $40\Omega$  (nominal) which is minimally affected by the  $10\text{-}k\Omega$  strap to ground or  $V_{DD}$ . As with the series termination resistor, the output strapping resistor should be placed as close to the I/O pin as possible in order to keep the interconnecting trace short. The trace from the resistor to ground or  $V_{DD}$  should be kept less than two inches in length to prevent system noise coupling during input logic sampling.

When the clock output is enabled following the 2-ms input period, a 14.318-MHz output frequency is delivered on the pin, assuming that  $\mathsf{V}_{DD}$  has stabilized. If  $\mathsf{V}_{DD}$  has not yet reached full value, output frequency initially may be below target but will increase to target once  $\mathsf{V}_{DD}$  voltage has stabilized. In either case, a short output clock cycle may be produced from the CPU clock outputs when the outputs are enabled.

Figure 1. Input Logic Selection Through Resistor Load Option

Figure 2. Input Logic Selection Through Jumper Option

#### **Serial Data Interface**

The W48S111-14 features a two-pin, serial data interface that can be used to configure internal register settings that control particular device functions. Upon power-up, the W48S111-14 initializes with default register settings. Therefore, the use of this serial data interface is optional. The serial interface is write-only (to the clock chip) and is the dedicated function of device pins SDATA and SCLOCK. In motherboard applications, SDATA and SCLOCK are typically driven by two logic

outputs of the chipset. Clock device register changes are normally made upon system initialization, if required. The interface can also be used during system operation for power management functions. *Table 2* summarizes the control functions of the serial data interface.

#### Operation

Data is written to the W48S111-14 in ten bytes of eight bits each. Bytes are written in the order shown in *Table 3*.

Table 2. Serial Data Interface Control Functions Summary

| Control Function                 | Description                                                                                                                                                                     | Common Application                                                                                                                                 |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Output Disable             | Any individual clock output(s) can be disabled. Disabled outputs are actively held LOW.                                                                                         | Unused outputs are disabled to reduce EMI and system power. Examples are clock outputs to unused PCI slots.                                        |

| CPU Clock Frequency<br>Selection | Provides CPU/PCI frequency selections beyond the 100- and 66.8-MHz selections that are provided by the SEL100/66# pin. Frequency is changed in a smooth and controlled fashion. | For alternate microprocessors and power management options. Smooth frequency transition allows CPU frequency change under normal system operation. |

| Output Three-state               | Puts all clock outputs into a high-impedance state.                                                                                                                             | Production PCB testing.                                                                                                                            |

| Test Mode                        | All clock outputs toggle in relation to X1 input, internal PLL is bypassed. Refer to <i>Table 4</i> .                                                                           | Production PCB testing.                                                                                                                            |

| (Reserved)                       | Reserved function for future device revision or production device testing.                                                                                                      | No user application. Register bit must be written as 0.                                                                                            |

Table 3. Byte Writing Sequence

| Byte<br>Sequence | Byte Name       | Bit Sequence     | Byte Description                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | Slave Address   | 11010010         | Commands the W48S111-14 to accept the bits in Data Bytes 3–6 for internal register configuration. Since other devices may exist on the same common serial data bus, it is necessary to have a specific slave address for each potential receiver. The slave receiver address for the W48S111-14 is 11010010. Register setting will not be made if the Slave Address is not correct (or is for an alternate slave receiver). |

| 2                | Command<br>Code | Don't Care       | Unused by the W48S111-14, therefore bit values are ignored ("don't care"). This byte must be included in the data write sequence to maintain proper byte allocation. The Command Code Byte is part of the standard serial communication protocol and may be used when writing to another addressed slave receiver on the serial data bus.                                                                                   |

| 3                | Byte Count      | Don't Care       | Unused by the W48S111-14, therefore bit values are ignored ("don't care"). This byte must be included in the data write sequence to maintain proper byte allocation. The Byte Count Byte is part of the standard serial communication protocol and may be used when writing to another addressed slave receiver on the serial data bus.                                                                                     |

| 4                | Data Byte 0     | Don't Care       | Refer to Cypress SDRAM drivers.                                                                                                                                                                                                                                                                                                                                                                                             |

| 5                | Data Byte 1     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6                | Data Byte 2     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7                | Data Byte 3     | Refer to Table 4 | The data bits in these bytes set internal W48S111-14 registers that con-                                                                                                                                                                                                                                                                                                                                                    |

| 8                | Data Byte 4     |                  | trol device operation. The data bits are only accepted when the Address Byte bit sequence is 11010010, as noted above. For description of bit                                                                                                                                                                                                                                                                               |

| 9                | Data Byte 5     |                  | control functions, refer to <i>Table 4</i> , Data Byte Serial Configuration Map.                                                                                                                                                                                                                                                                                                                                            |

| 10               | Data Byte 6     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                             |

## **Writing Data Bytes**

Each bit in the data bytes control a particular device function except for the "reserved" bits which must be written as a logic 0. Bits are written MSB (most significant bit) first, which is bit 7. *Table 4* gives the bit formats for registers located in Data Bytes 3–6.

Table 5 details additional frequency selections that are available through the serial data interface.

Table 6 details the select functions for Byte 3, bits 1 and 0.

Table 4. Data Bytes 3-6 Serial Configuration Map

| Selection   Best   Selection   Selection | Refer to Refer to Refer to Frequency Controlled by external SEL100/ 66# pin (Table 1) (See Table 6 for function Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Frequency Controlled by BYT3 SEL_(2:0) (Table 5)  on details)  Active Active Active Active                         | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Refer to Ref         | Table 5 Table 5 Table 5 Table 5 Trequency Controlled by BYT3 SEL_(2:0) (Table 5) on details)  Active Active Active | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>00                                   |

| 6           SEL_2           5           SEL_1           4           SEL_0           3           Frequency Table Selection         Frequency Table Selection           2           (Reserved)           1-0           Bit 1 Bit 0 Function On Normal On On Spread Selection           1         0         Spread Selection         1 On Spread Selection           2         14         24/48MHz         Clock output disable           3          (Reserved)         1 On Spread Selection           4           (Reserved)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Refer to Ref         | Table 5 Table 5 Table 5 Table 5 Trequency Controlled by BYT3 SEL_(2:0) (Table 5) on details)  Active Active Active | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>00                                   |

| SEL_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Refer to Refer to Refer to Refer to Frequency Controlled by external SEL100/ 66# pin (Table 1) (See Table 6 for function Deparation e pectrum on ts Three-stated Low Low Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Table 5 Table 5 Frequency Controlled by BYT3 SEL_(2:0) (Table 5) on details)  Active Active Active                 | 0<br>0<br>0<br>0<br>0<br>00<br>1                                        |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Refer to Frequency Controlled by external SEL100/ 66# pin (Table 1)  (See Table 6 for function Deperation e Expectrum on ts Three-stated  Low Low Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Frequency Controlled by BYT3 SEL_(2:0) (Table 5)  on details)  Active Active Active Active                         | 0<br>0<br>0<br>00<br>00<br>1<br>0<br>0                                  |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Frequency Controlled by external SEL100/66# pin (Table 1)  (See Table 6 for function of the control of the c            | Frequency Controlled by BYT3 SEL_(2:0) (Table 5)  on details)  Active Active Active                                | 0<br>0<br>00<br>0<br>1<br>0<br>0<br>0                                   |

| Selection   Sele | by external SEL100/ 66# pin ( <i>Table 1</i> )  (See <i>Table 6</i> for function of the sector | by BYT3 SEL_(2:0) (Table 5)  on details)  Active Active Active                                                     | 0<br>00<br>1<br>0<br>0<br>0                                             |

| 1-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | peration e spectrum on ts Three-stated  Low Low Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <br>Active<br><br><br><br>Active                                                                                   | 0<br>1<br>0<br>0<br>0<br>0                                              |

| Data Byte 4   Test Mode   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | peration e spectrum on ts Three-stated  Low Low Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <br>Active<br><br><br><br>Active                                                                                   | 0<br>1<br>0<br>0<br>0                                                   |

| 7           (Reserved)           6         14         24/48MHz         Clock output disable           5           (Reserved)           4           (Reserved)           3           (Reserved)           2         21         CPU1         Clock Output Disable           1           (Reserved)           0         22         CPU0         Clock Output Disable           Data Byte 5         7         4         PCI_F         Clock Output Disable           6         11         PCI6         Clock Output Disable           5         10         PCI5         Clock Output Disable           4         -          (Reserved)           3         8         PCI4         Clock Output Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <br><br>Low<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <br><br><br>Active                                                                                                 | 1<br>0<br>0<br>0                                                        |

| 6         14         24/48MHz         Clock output disable           5           (Reserved)           4           (Reserved)           3           (Reserved)           2         21         CPU1         Clock Output Disable           1           (Reserved)           0         22         CPU0         Clock Output Disable           Data Byte 5           7         4         PCI_F         Clock Output Disable           6         11         PCI6         Clock Output Disable           5         10         PCI5         Clock Output Disable           4         -         -         (Reserved)           3         8         PCI4         Clock Output Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <br><br>Low<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <br><br><br>Active                                                                                                 | 1<br>0<br>0<br>0                                                        |

| 5           (Reserved)           4           (Reserved)           3           (Reserved)           2         21         CPU1         Clock Output Disable           1           (Reserved)           0         22         CPU0         Clock Output Disable           Data Byte 5           7         4         PCI_F         Clock Output Disable           6         11         PCI6         Clock Output Disable           5         10         PCI5         Clock Output Disable           4         -         -         (Reserved)           3         8         PCI4         Clock Output Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <br><br>Low<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <br><br><br>Active                                                                                                 | 0<br>0<br>0<br>1                                                        |

| 4           (Reserved)           3           (Reserved)           2         21         CPU1         Clock Output Disable           1           (Reserved)           0         22         CPU0         Clock Output Disable           Data Byte 5           7         4         PCI_F         Clock Output Disable           6         11         PCI6         Clock Output Disable           5         10         PCI5         Clock Output Disable           4         -         -         (Reserved)           3         8         PCI4         Clock Output Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <br><br>Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <br><br>Active                                                                                                     | 0 0 1                                                                   |

| 3           (Reserved)           2         21         CPU1         Clock Output Disable           1           (Reserved)           0         22         CPU0         Clock Output Disable           Data Byte 5           7         4         PCI_F         Clock Output Disable           6         11         PCI6         Clock Output Disable           5         10         PCI5         Clock Output Disable           4         -          (Reserved)           3         8         PCI4         Clock Output Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <br>Active                                                                                                         | 0<br>1                                                                  |

| 2         21         CPU1         Clock Output Disable           1           (Reserved)           0         22         CPU0         Clock Output Disable           Data Byte 5           7         4         PCI_F         Clock Output Disable           6         11         PCI6         Clock Output Disable           5         10         PCI5         Clock Output Disable           4         -         -         (Reserved)           3         8         PCI4         Clock Output Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Low<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Active                                                                                                             | 1                                                                       |