## DMC73C168

# Table of Contents

| 1. INTRODUCTION                                             | 3   |

|-------------------------------------------------------------|-----|

| 1.1 Key Features                                            |     |

| 2. DMC73C168 BLOCK DIAGRAM                                  | 5   |

| 3. PIN ASSIGNMENT AND DESCRIPTION                           |     |

| 3.1 DMC73C168 Pin Assignment                                |     |

| 3.2 Description                                             |     |

| 4. ARCHITECTURE                                             |     |

| 4.1 Register File (RF)                                      |     |

| 4.2 Peripheral File (PF)                                    |     |

| 4.3 Peripheral RAM File (PRF)                               | 12  |

| 4.4 Stack Pointer (SP)                                      | 15  |

| 4.5 Status Register (ST)                                    |     |

| 4.6 Program Counter (PC)                                    |     |

| 4.7 Peripheral File Map                                     |     |

| 4.8 Interrupt and Reset Priorities                          | 33  |

| 5. DESCRIPTION OF EACH FUNCTION                             | 34  |

| 5.1 Input / Output Ports                                    | 34  |

| 5.2 Device Initialization                                   | 36  |

| 5.3 I/O Control Register                                    | 36  |

| 5.4 Interrupt Logic and External Interrupt                  |     |

| 5.5 Programmable Timer / Event Counter                      |     |

| 5.6 A/D Converter                                           |     |

| 5.7 PLL                                                     | • • |

| 5.8 IF Counter                                              | 59  |

| 5.9 Serial Communication I/O Ports : SIO1, SIO2             | 63  |

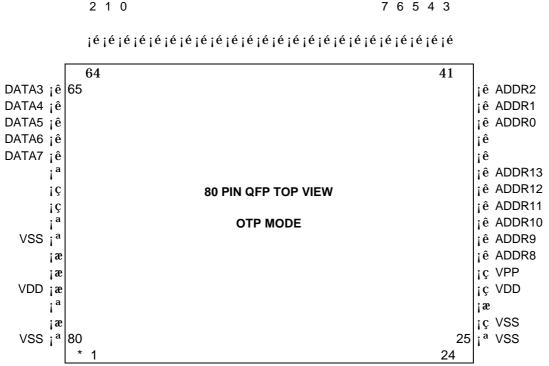

| 6. OTP DEVICE SPECIFICATION                                 | 66  |

| 6.1 Pin Assignment of OTP and OTP Programming Adapter Board | 66  |

### DMC73C168

| 7. ELECTRICAL SPECIFICATION                                            | 67 |

|------------------------------------------------------------------------|----|

| 7.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range | 67 |

| 7.2 Recommended Operating Conditions                                   | 68 |

| 7.3 Electrical Characteristics Over Full Range of Operation            | 69 |

| 7.4 AC Characteristics for Input/Output Ports                          | 70 |

| 7.5 A/D Converter Characteristics                                      | 71 |

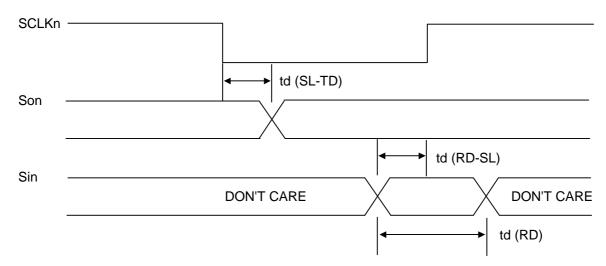

| 7.6 AC Characteristics for Serial I/O Ports                            | 71 |

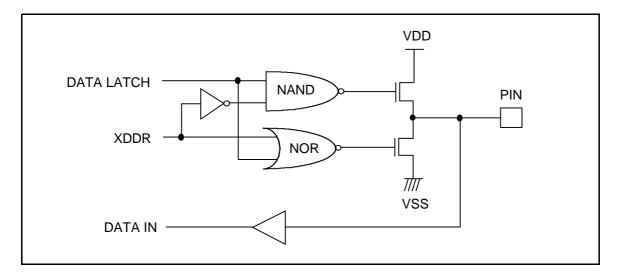

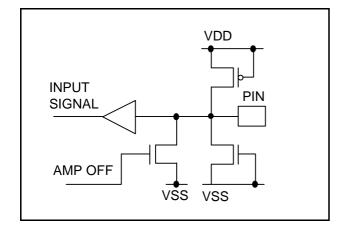

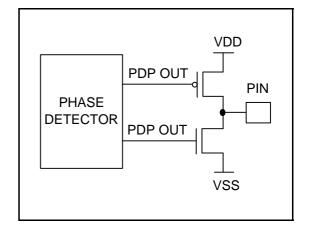

| 7.7 Schematic of Input/Outputs                                         | 72 |

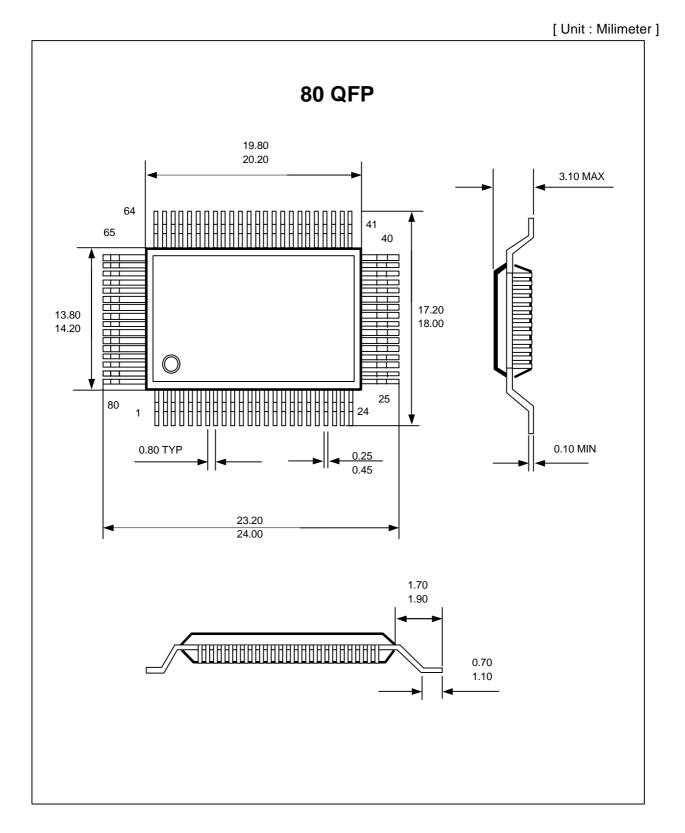

| 7.8 80 Pin Quad Flat Package (Mechanical Data)                         | 73 |

| * APPENDICES                                                           |    |

| A. DMC73C168 Table                                                     | 75 |

| B. Development Support                                                 | 75 |

| C. OTP Programming                                                     | 79 |

## 1. INTRODUCTION

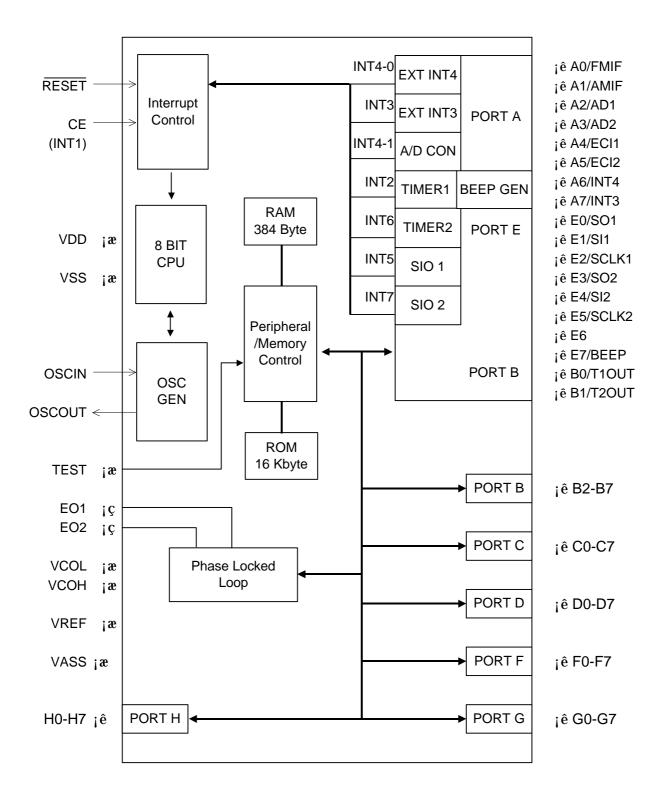

The DMC73C168 is an 8-Bit microcontroller that contains Prescaler, PLL Frequency Synthesizer and 2 channel A/D converter for Digital Tuning System.

The device is provided with abundant I/O ports and 2 channel serial interface ports (SI/O) controlled by powerful instruction. The package is 80-pin QFP and high performance CPU and internal peripheral allow flexible and easy system design in car-stereo, radio tuner and Hi-Fi audio system.

- 1.1 Key Features

- CMOS Technology

- Memory Configuration

- 256 Byte On-Chip RAM Register file plus 128 Byte Peripheral Free RAM

- Memory-Mapped Ports for Easy Addressing

- 16K-Byte On-Chip ROM

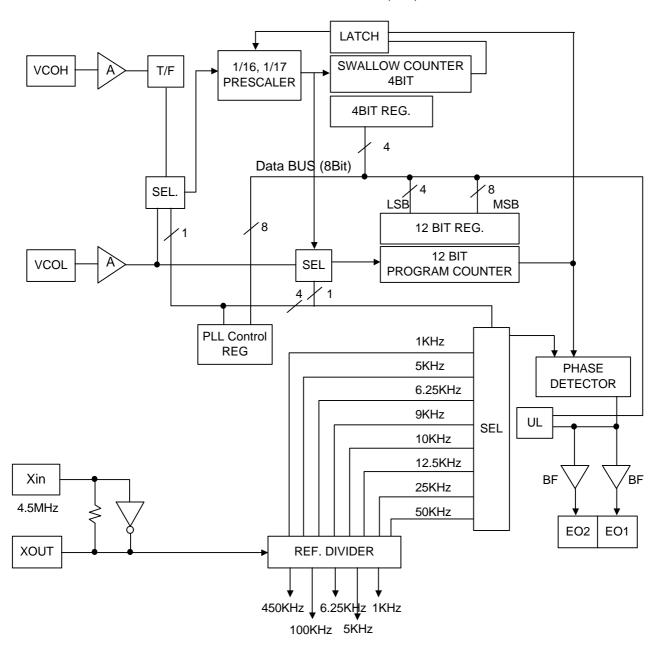

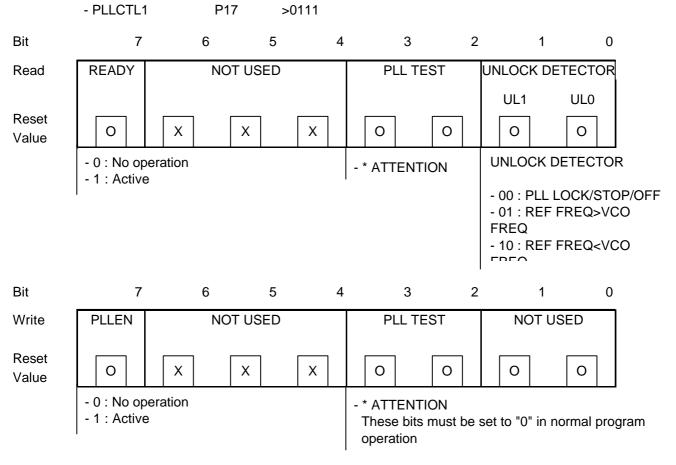

- On-Chip PLL Frequency Synthesizer with Dual Modules Prescaler

- Independant Frequency input ports : Max 150MHz at FM, 40MHz at AM

- Two Types of Frequency Dividing Method : Pulse Swallow and Direct

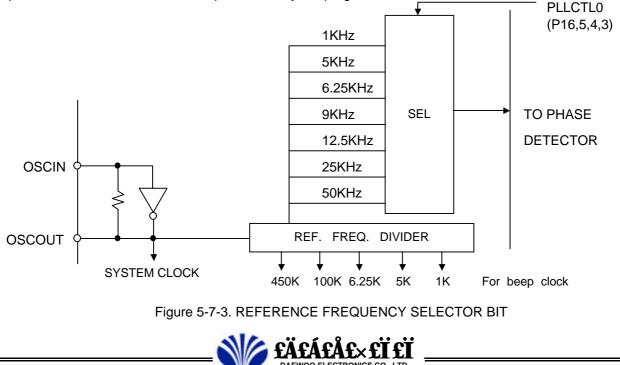

- 8 Kinds of reference Frequencies : 1, 5, 6.25, 9, 10, 12.5, 25 and 50KHz

- 2 Channel SIO port

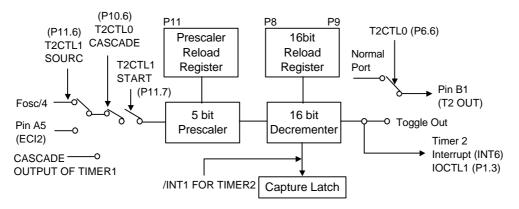

- 2 Channel On-Chip Timer

- 16-Bit with 5-Bit Prescaler and 16-Bit capture latch, timer outputs

- Internal interrupt with Automatic timer Reload

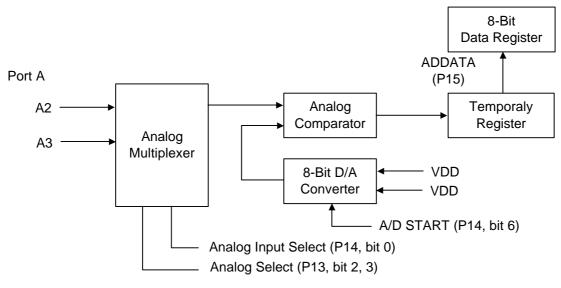

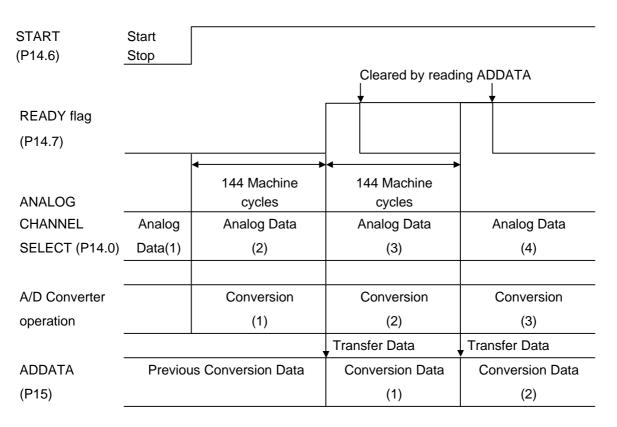

- On-Chip A/D Converter

- 2-channels with 8 bit resolution

- Ratiometric Conversion

- 144 Machine-Cycles Conversion time (64us)

- On-Chip IF Counter

- 17-Bit, Gate Time : Program can select from 1ms to 15ms

- maximum Input Frequency : FM IF = 20MHz, AM IF = 5MHz

- Easy Interrupt Handling

- External Interrupts with Schmitt-Trigger Input

- Software Calls through Interrupt Vectors

- Software Monitoring of Interrupt Status

- Precise Interrupt Timing through Capture Latch

- Selectable Beep clock : 417Hz, 1KHz, 1.25KHz, 2.5KHz

- 64 I/O Pins

- 64 Bidirectional Pins

- Wide Operating Range

- Voltage(VDD) : 5V ; %0%

3

- Clock : 4.5MHz

- Temperature : -40 deg to 85 deg

- One Machine Execution Time : 0.44us (with 4.5MHz Crystal Oscillator)

- Low operating Current

- Halt Mode for Power Savings (Typical : 1uA at OSC stop)

- Warm-up mode for avoid unstable osc operation at the wake time from Halt mode. The warm-up time can be adjustable by S/W.

- Package

- 80 QFP (Quad Flat Package)

- Development Support

- Evaluation Module : EVM73C00A & ADP73C168

- Assembler/Linker Cross Support for Popular Hosts

### DMC73C168

# 2. DMC73C168 BLOCK DIAGRAM

3. PIN ASSIGNMENT AND DESCRIPTION

3.1 DMC73C168 Pin Assignment

#### ΒВ 1 0 1 1 ΤТ 2 1 00 СССDDDDDDBBBBBBUUHHHH 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 T T 7 6 5 4 3 64 41 C3 jê 65 jê H2 C4 jê jê H1 C5 jê ;ê HO C6 jê ;ê G7 C7 jê jê G6 NC i<sup>a</sup> jê G5 EO1 jç jê G4 **80 PIN QFP TOP VIEW** EO2 įç jê G3 jê G2 VSS ;<sup>a</sup> DMC73C168 VASS ; a jê G1 VCOH jæ ;ê G0 VCOL jæ ;ç TEST VREF ; æ iç VDD iæ OSCOUT NC i<sup>a</sup> CE/INT1 ; æ ;ç OSCIN 25 ja VSS RESET ; æ 80 \* 24 1 AAAAAAEEEEEEEFFFFFFF 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 / FAAAEEIISSSSS В MMDDCCNNOICOIC Е I I 1 2 I I T T 1 1 L 2 2 L Е FF 1 2 4 3 Ρ Κ Κ 1 2

X X X E E P C O P P G E E T T M E E S S T T H V

| DDD   | ΑΑΑΑ  |

|-------|-------|

| ΑΑΑ   | D     |

| ТТТ   | D     |

| ΑΑΑ   | RRRR  |

| 2 1 0 | 765/3 |

#### 8Bit Single Chip Microcontroller

DMC73C168

### DMC73C168

### 3.2 Description

| NAME                                         | Pin No.                                      | I/O                                           | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                    | PORT TYPE                                               |

|----------------------------------------------|----------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| A0/FM IF<br>A1/AM IF                         | 1<br>2                                       | I/O<br>I/O                                    | Port A is a bidirectional data port.<br>These Ports can be selected as universal Counter<br>input. A0 and A1 work as the FM IF and AM IF pin,<br>independently. The maximum input frequency is 5MHz<br>for AM IF (0.1Vp-p) and 20MHz (0.1Vp-p) for FM IF. | Analog-IN or<br>Logic-IN/<br>Push-Pull OUT              |

| A2/AD1<br>A3/AD2                             | 3<br>4                                       | I/O<br>I/O                                    | These Posts can be selected for an A/D Converter Input.<br>2 Channel/8-Bit Analog-to-Digital Converter are used for<br>the Sequential Comparison method by program.<br>Reference Voltage of the A/D Converter is the same<br>level of VDD (5V ; \$40%)    | Analog-IN or<br>Logic-IN/<br>Push-Pull OUT              |

| A4/ECI1<br>A5/ECI2                           | 5<br>6                                       | I/O<br>I/O                                    | The A4,A5 Port can be used as event counter input 1,2.                                                                                                                                                                                                    |                                                         |

| A6/INT4<br>A7/INT3                           | 7<br>8                                       | I/O<br>I/O                                    | These Ports can be used as external interrupt pin.                                                                                                                                                                                                        | Logic-IN or<br>Schmitt-<br>Trigger-IN/<br>Push-Pull OUT |

| E0/SO1<br>E1/SI1<br>E2/SCLK1                 | 9<br>10<br>11                                | I/O<br>I/O<br>I/O                             | Port E is a bidirectional data port.<br>These Ports can be selected as serial interface (SIO) 1.<br>E0, E1 and E2 work as the serial output, serial input and<br>serial clock pin, respectively.                                                          | Logic-IN/<br>Push-Pull OUT                              |

| E3/SO2<br>E4/SI2<br>E5/SCLK2                 | 12<br>13<br>14                               | I/O<br>I/O<br>I/O                             | These Ports can be selected as serial interface (SIO) 2.<br>E3, E4 and E5 work as the serial output, serial input and<br>serial clock pin, respectively.                                                                                                  | Logic-IN/<br>Push-Pull OUT                              |

| E6<br>E7/BEEP                                | 15<br>16                                     | I/O<br>I/O                                    | The E7 Port can be used as BEEP output pin.                                                                                                                                                                                                               |                                                         |

| F0<br>F1<br>F2<br>F3<br>F4<br>F5<br>F6<br>F7 | 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Port F is a bidirectional data port.                                                                                                                                                                                                                      | Logic-IN/<br>Push-Pull OUT                              |

## DMC73C168

| N   | IAME  | PIN NO. | I/O | FUNCTION DESCRIPTION                                     | PORT TYPE     |

|-----|-------|---------|-----|----------------------------------------------------------|---------------|

|     | G0    | 30      | I/O | Port G is a bidirectional data port.                     | Logic-IN/     |

|     | G1    | 31      | I/O |                                                          | Push-Pull OUT |

|     | G2    | 32      | I/O |                                                          |               |

|     | G3    | 33      | I/O |                                                          |               |

|     | G4    | 34      | I/O |                                                          |               |

|     | G5    | 35      | I/O |                                                          |               |

|     | G6    | 36      | I/O |                                                          |               |

|     | G7    | 37      | I/O |                                                          |               |

|     | HO    | 38      | I/O | Port H is a bidirectional data port.                     | Logic-IN/     |

|     | H1    | 39      | I/O |                                                          | Push-Pull OUT |

|     | H2    | 40      | I/O |                                                          |               |

|     | H3    | 41      | I/O |                                                          |               |

|     | H4    | 42      | I/O |                                                          |               |

|     | H5    | 43      | I/O |                                                          |               |

|     | H6    | 44      | I/O |                                                          |               |

|     | H7    | 45      | I/O |                                                          |               |

| B0/ | T1OUT | 46      | I/O | Port B is a bidirectional data port.                     | Logic-IN/     |

| B1/ | T2OUT | 47      | I/O | Port B0, B1 can be selected as Timer 1 & 2 output ports. | Push-Pull OUT |

|     | B2    | 48      | I/O |                                                          |               |

|     | B3    | 49      | I/O |                                                          |               |

|     | B4    | 50      | I/O |                                                          |               |

|     | B5    | 51      | I/O |                                                          |               |

|     | B6    | 52      | I/O |                                                          |               |

|     | B7    | 53      | I/O |                                                          |               |

|     | D0    | 54      | I/O | Port D is a bidirectional data port.                     | Logic-IN/     |

|     | D1    | 55      | I/O |                                                          | Push-Pull OUT |

|     | D2    | 56      | I/O |                                                          |               |

|     | D3    | 57      | I/O |                                                          |               |

|     | D4    | 58      | I/O |                                                          |               |

|     | D5    | 59      | I/O |                                                          |               |

|     | D6    | 60      | I/O |                                                          |               |

|     | D7    | 61      | I/O |                                                          |               |

|     | C0    | 62      | I/O | Port C is a bidirectional data port.                     | Logic-IN/     |

|     | C1    | 63      | I/O |                                                          | Push-Pull OUT |

|     | C2    | 64      | I/O |                                                          |               |

|     | C3    | 65      | I/O |                                                          |               |

|     | C4    | 66      | I/O |                                                          |               |

|     | C5    | 67      | I/O |                                                          |               |

|     | C6    | 68      | I/O |                                                          |               |

|     | C7    | 69      | I/O |                                                          |               |

## DMC73C168

| NAME            | Pin No.      | I/O    | FUNCTION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                   | PORT TYPE   |

|-----------------|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| VCOH            | 75           | Ι      | FM VCO input port.<br>Only Pulse swallow method is used for this port.<br>The range of local oscillator output is 10MHz to 150MHz<br>with 0.3Vp-p minimum.<br>The output is required by capacitor coupling because an<br>AC amplifier is contained.                                                                                                                                                                                                    | Analog-IN   |

| VCOL            | 76           | I      | AM VCO input port.<br>This terminal can be selected by direct-dividing method<br>or pulse-swallow method.<br>In direct-dividing method, the range of local oscillator<br>output is 0.5MHz to 10MHz with 0.3Vp-p minimum, and<br>in pulse-swallow method, the range of local oscillator<br>output is 5MHz to 40MHz with 0.3Vp-p minimum.<br>Input to this port should be coupled by capacitor coupling<br>because and AC amplifier is contained.        | Analog-IN   |

| VDD<br>VREF     | 28<br>77     |        | Power source port.<br>The terminal supplies 5V ; $\frac{40}{5}$ for normal operation.<br>VDD and VREF must be connected to the same electric<br>potential. VDD is a power for logic circuit and V <sub>REF</sub> is a<br>power for analog circuit in the device.                                                                                                                                                                                       |             |

| NC              | 70           |        | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

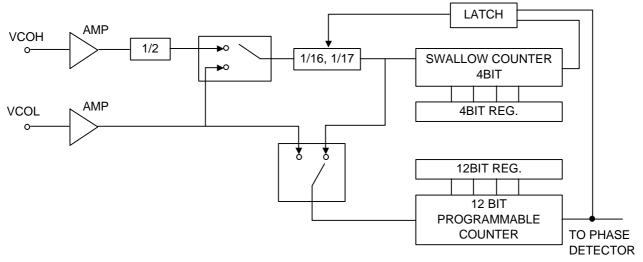

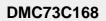

| EO1<br>EO2      | 71<br>72     | 0      | Phase comparison error output ports.<br>The divided frequency of VCO output and the reference<br>frequency are compared in their phase.<br>If divided frequency is higher than the reference frequency,<br>output signal is logic high level. If divided frequency is<br>lower than the reference frequency, output signal is vice<br>versa. When two frequencies are matched, port become a<br>floating state.<br>EO1 and EO2 have the same waveform. | 3-State-OUT |

| TEST            | 29           | I      | Internal Chip Test port.<br>It should be connected to VSS.                                                                                                                                                                                                                                                                                                                                                                                             |             |

| VSS<br>VASS     | 73, 25<br>74 |        | Ground reference<br>VSS is a ground for logic circuit and VASS is a ground for<br>Analog circuit in the device                                                                                                                                                                                                                                                                                                                                         |             |

| OSCOUT<br>OSCIN | 27<br>26     | 0<br>I | Crystal oscillator input and output ports.<br>Connect 4.5MHz Crystal.                                                                                                                                                                                                                                                                                                                                                                                  |             |

### DMC73C168

| NAME    | PIN NO. | I/O | FUNCTION DESCRIPTION                                                                                                                                                                                          | PORT TYPE               |

|---------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| NC      | 78      |     | No connection                                                                                                                                                                                                 |                         |

| RESET   | 80      | I   | System reset request input port.<br>The reset pin must be held low for minimum of 5 internal<br>clock cycles to guarantee recognition by the device.<br>The device initialization requires 15 machine cycles. |                         |

| CE/INT1 | 79      | I   | Device selection Signal input port.<br>External interrupt input port.<br>This port can be used as a Chip Enable input.<br>When activated, CPU resumes its operation from HALT<br>mode                         | Schimitt-<br>Trigger-IN |

### **4. ARCHITECTURE**

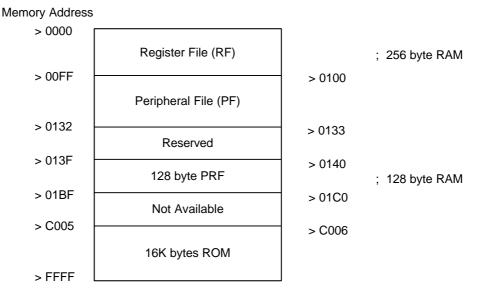

The DMC73C168 has a maximum memory address space of 64K bytes and only the Single-Chip mode. On-Chip memory spaces are configured as shown in Table 4.1.

In the sections that follow, the Register File (RF) and the Peripheral File (PF) are described along with three important registers in the CPU : the Stack Pointer (SP), the Status Register (ST), and the Program Counter (PC)

Table 4-1. DMC73C168 Memory Map

#### DMC73C168

#### 4.1 Register File (RF)

The 256-byte on chip RAM resides in location >0000 to >00FF ('>' means hex) of the DMC73C168's address space and is called the Register File (RF). The RAM is treated as registers by much of the instruction set and numbered R0-R255. The first two registers, R0 and R1, are also called the A and B registers respectively. Several instructions specify A or B as either the source or destination register ; e.g., STSP stores the contents of the Stack Pointer (SP) in the B register. Except where stated otherwise, any register in the Register File can be addressed as an 8-bit source or destination register. The stack is also located in the Register File. Refer to section 4.3 for information regarding the initialization of the Stack Pointer (SP) and stack definition in the Register File.

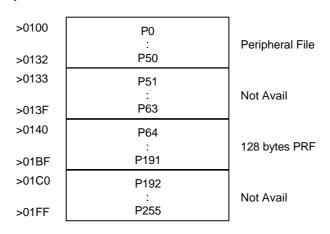

#### 4.2 Peripheral File (PF)

The Peripheral File (PF) resides in location >0100 to >0132 of the DMC73C168's address space. Peripheral File locations are numbered P0-P50. The PF registers are used for interrupt control, parallel I/O, timer control, PLL, IF counter, BEEP, SIO and A/D converter control.

#### 4.3 Peripheral RAM File (PRF)

The Peripheral RAM file (PRF) resides in location >0140 to >01BF of DMC73C168's address space. PRF will act a role P64-P191. Useage is for additional RAM, but addressing method is same as Peripheral File's.

#### Memory address

#### 4.4 Stack Pointer (SP)

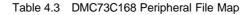

The Stack Pointer(SP) is an 8-bit register in the CPU that is typically used to hold a pointer in RAM (the Register File). However, the SP can also be used as temporary data storage if a stack is not implemented, or if the SP contents are not needed. When a stack is implemented just before data is pushed onto the stack and automatically decremented immediately after data is poped from the stack. Upon assertion if the RESET function (see Section 4.7) >01 is loaded into the SP. The size of the stack can be changed from the 254-level stack at RESET to a smaller stack by executing a stack initialization program as illustrated in Figure 4.4. The This feature allows the stack to be located anywhere in the Register File. The SP is initialized through the B register (R1).

Figure 4.4 Example of Stack Initialization in the Register File

#### 4.5 Status Register (ST)

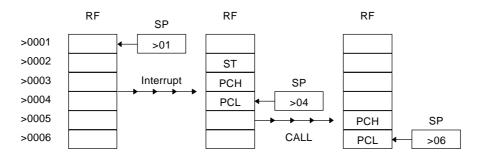

The Status Register (ST) is an 8-bit register in the CPU that contains three conditional status bits ; Carry (C), Sign (N), Zero (Z), and a global Interrupt Enable bit (I) as shown in Figure 4-5.

Figure 4-5. Status Register (ST)

The C, N and Z bits are used mostly for arithmetic operations, bit rotating, and conditional branching. The Carry(C) bits is used as the carry-in and carry-out for most of lotate and arithmetic instructions. The Sign(N) bit contains the most significant bit of the destination operand contents after instruction execution. The Zero(Z) bit contains a one when all bits of the destination operand are equal to zero after instruction execution. The C, N and Z status bits also have jump-on-condition instructions associated them. The global Interrupt Enable (I) bit must be set to one by the EINT instruction in

#### DMC73C168

order for any of the individual interrupts (INTn) to be recognized by the CPU. The Interrupt Enable (I) bit can cleared by DINT instruction of by executing a device RESET (see Section 4.7).

#### 4.6 Program Counter (PC)

The DMC73C168's 16-bit Program Counter (PC) consists of two 8-bit registers in the CPU which contain the MSB and the LSB respectively of a 16-bit address ; the Program Counter High (PCH) and Low (PCL). The PC acts as the 16-bit address pointer of the opcodes and operands in memory of the currently executing instruction. Upon assertion of the RESET function, the MSB and the LSB of the PC are loaded into the A and B registers of the Register File (see Section 4.7).

#### 4.7 Peripheral File Map

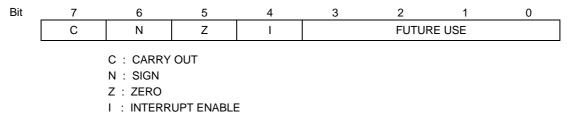

The Peripheral File (PF) resides in locations >0100 to >01BF of the DMC73C168's address space as shown in Table 4.7

| <b></b>  |         |          |      |                                      | RESET    |

|----------|---------|----------|------|--------------------------------------|----------|

| REGISTER | ADDRESS | NAME     | NOTE | FUNCTION                             | VALUE    |

| P0       | >0100   | IOCTL0   | 1    | Interrupt 1,2 and 3 control register | 00000000 |

| P1       | >0101   | IOCTL1   | 1    | Ext-INT 1,3 and 4 input edge select  | 0000x000 |

| P2       | >0102   | IOCTL2   | 1    | Interrupt 4,5,6,7 control register   | 00000000 |

| P4       | >0104   | T1MSDATA | 1    | Timer 1 MSB reload register          | xxxxxxxx |

|          |         |          |      | / MSB readout latch                  |          |

| P5       | >0105   | T1LSDATA | 1    | Timer 1 LSB reload register          | xxxxxxxx |

|          |         |          |      | / LSB decrementer value              |          |

| P6       | >0106   | T1CTL0   | 1    | Timer 1 control register 0           | x0xxxxxx |

|          |         |          |      | / MSB readout latch                  |          |

| P7       | >0117   | T1CTL1   | 1    | Timer 1 control register 1           | 0x0xxxxx |

|          |         |          |      | / LSB capture latch value            |          |

| P8       | >0118   | T2MSDATA | 1    | Timer 2 MSB reload register          | xxxxxxxx |

|          |         |          |      | / MSB readout latch                  |          |

| P9       | >0109   | T2LSDATA | 1    | Timer 2 LSB reload register          | xxxxxxxx |

|          |         |          |      | / LSB decrementer value              |          |

| P10      | >010A   | T2CTL0   | 1    | Timer 2 control register 0           | 00xxxxxx |

|          |         |          |      | / MSB readout latch                  |          |

| P11      | >010B   | T2CTL1   | 1    | Timer 2 control register 1           | 0x0xxxxx |

|          |         |          |      | / LSB capture latch value            |          |

| P13      | >010D   | APSLCT   |      | A port select control register       | 00000000 |

| P14      | >010E   | ADCTL    | 1    | A/D converter control register       | 00xxxxx0 |

| P15      | >010F   | ADDATA   | 1    | A/D converter data value             | 00000000 |

| P16      | >0110   | PLLCTL0  |      | PLL control register 0               | 00000000 |

Table 4.7 Peripheral File Map

### DMC73C168

| REGISTER | ADDRESS | NAME     | NOTE | FUNCTION                              | RESET<br>VALUE |

|----------|---------|----------|------|---------------------------------------|----------------|

| P17      | >0111   | PLLCTL1  | 1    | PLL control register 1                | 0xx x0000      |

| P18      | >0112   | PLLDATAH |      | PLL program counter MSB data register | 00000000       |

| P19      | >0113   | PLLDATAL |      | PLL program counter LSB data register | 00000000       |

| P22      | >0116   | IFCCTL   | 1    | IF counter data register              | 00000000       |

| P23      | >0117   | IFCLSD   | 1    | IF counter data register (LSB)        | 00000000       |

| P24      | >0118   | IFCMSD   | 1    | IF counter data register              | 00000000       |

| P25      | >0119   | IFCHSD   | 1    | IF counter data register (MSB)        | xxxxxx0        |

| P27      | >011B   | SIO1CTL  |      | SIO 1 control register                | 000000x        |

| P28      | >011C   | SIO1BUF  |      | SIO 1 data register                   | xxxxxxx        |

| P29      | >011D   | SIO2CTL  |      | SIO 2 control register                | 000000x        |

| P30      | >011E   | SIO2BUF  |      | SIO 2 data register                   | xxxxxxx        |

| P32      | >0120   | ADATA    |      | Port A data value                     | xxxxxxx        |

| P33      | >0121   | ADDR     |      | Port A direction register             | 00000000       |

| P34      | >0122   | BDATA    |      | Port B data value                     | xxxxxxx        |

| P35      | >0123   | BDDR     |      | Port B direction                      | 00000000       |

| P36      | >0124   | CDATA    |      | Port C data value                     | xxxxxxx        |

| P37      | >0125   | CDDR     |      | Port C direction register             | 00000000       |

| P38      | >0126   | DDATA    |      | Port D data value                     | xxxxxxx        |

| P39      | >0127   | DDDR     |      | Port D direction register             | 00000000       |

| P40      | >0128   | EDATA    |      | Port E data value                     | xxxxxxx        |

| P41      | >0129   | EDDR     |      | Port E direction register             | 00000000       |

| P42      | >012A   | FDATA    |      | Port F data value                     | xxxxxxx        |

| P43      | >012B   | FDDR     |      | Port F direction register             | 00000000       |

| P44      | >012C   | GDATA    |      | Port G data value                     | xxxxxxx        |

| P45      | >012D   | GDDR     |      | Port G direction register             | 00000000       |

| P46      | >012E   | HDATA    |      | Port H data value                     | xxxxxxx        |

| P47      | >012F   | HDDR     |      | Port H direction register             | 00000000       |

| P50      | >0132   | BEEP     |      | BEEP control register                 | 00000000       |

| P64      | >0140   |          |      | Peripheral RAM                        | xxxxxxx        |

| :        | :       |          |      | 128 bytes                             |                |

| :        | :       |          |      |                                       |                |

| P191     | >01BF   |          |      |                                       | xxxxxxx        |

Notes 1: Be careful when using logical instructions (e.g., ANDP, ORP, XORP) on these registers because of different read/write functions.

2: 'x' means indeterminate

3: P3, P12, P20, P21, P26, P31, P48, P49, P51-63 are not implemented.

#### DMC73C168

#### 4.7.1 Peripheral Files detail Description

#### 1) I/O CONTROL REGISTERS

| PF NAME : IOCTL0 : I/O CONTROL REGISTER 0 |       |       |       |       |       |       |       |       |       |

|-------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                                           | R/W   | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

| P0                                        | READ  |       |       | INT3F | INT3E | INT2F | INT2E | INT1F | INT1E |

| >0100                                     | WRITE | NOT   | USED  | INT3C | INT3E | INT2C | INT2E | INT1C | INT1E |

| RESET VALUE                               |       | Х     | Х     | 0     | 0     | 0     | 0     | 0     | 0     |

X = Indeterminate

Read : INTnF: 0 = INTn inactive 1 = INTn pending

Write : INTnE : 0 = INTn disable 1 = INTn enable

INTnC : 0 = No Effect

1 = Clear INTn flag

: I/O CONTROL REGISTER 1 PF NAME : IOCTL1

|       | R/W   | BIT 7  | BIT 6  | BIT 5  | BIT 4  | BIT 3 | BIT 2  | BIT 1 | BIT 0 |

|-------|-------|--------|--------|--------|--------|-------|--------|-------|-------|

| P1    | READ  | INT41F | INT41E | INT40F | INT40E | NOT   | INT40S | INT3S | INT1S |

| >0101 | WRITE | INT41C | INT41E | INT40C | INT40E | USED  | INT40S | INT3S | INT1S |

| RESET | VALUE | 0      | 0      | 0      | 0      | х     | 0      | 0     | 0     |

X = Indeterminate

INT41 = INT4-1

INT40 = INT4-0

Read : INTnF: 0 = INTn inactive

1 = INTn pending INTnS : 0 = Falling edge sensing 1 = Rising edgi sensing

Write : INTnE : 0 = INTn disable 1 = INTn enable INTnC :0 = No Effect 1 = Clear INTn flag

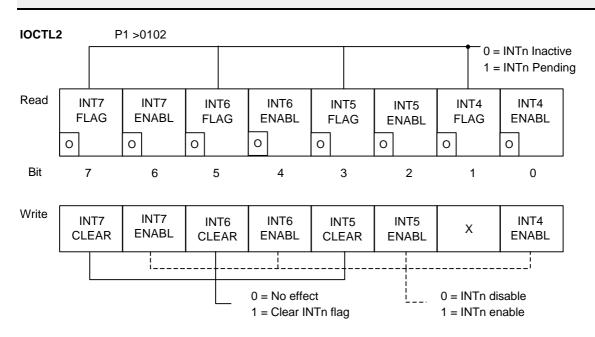

| PF NAME | : | IOCTL2 | : | 1/0 CC | DNTR | DL I | REGISTE | R 2 |

|---------|---|--------|---|--------|------|------|---------|-----|

|         |   |        |   |        |      |      |         |     |

|       | R/W   | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| P2    | READ  | INT7F | INT7E | INT6F | INT6E | INT5F | INT5E | INT4F | INT4E |

| >0102 | WRITE | INT7C | INT7E | INT6C | INT6E | INT5C | INT5E | х     | INT4E |

| RESET |       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Read : INTnF: 0 = INTn inactive 1 = INTn pending This bit is automatically cleared

Write : INTnE : 0 = INTn disable 1 = INTn enable INTnC :0 = No Effect

1 = Clear INTn flag

When CPU fetch its vector address. << INT4F is not automatically cleared

When CPU fetch vector address>>

#### DMC73C168

#### 2) TIMER 1 & 2 CONTROL REGISTERS

| PF NAME : T1MSDATA : TIMER 1 MS BYTE DATA REGISTER |       |       |                   |       |       |         |       |       |       |  |  |  |

|----------------------------------------------------|-------|-------|-------------------|-------|-------|---------|-------|-------|-------|--|--|--|

|                                                    | R/W   | BIT 7 | BIT 6             | BIT 5 | BIT 4 | BIT 3   | BIT 2 | BIT 1 | BIT 0 |  |  |  |

| P4                                                 | READ  |       | MSB READOUT LATCH |       |       |         |       |       |       |  |  |  |

| >0104                                              | WRITE |       |                   | MS    |       | OUT LAT | СН    |       |       |  |  |  |

| RESET                                              | VALUE | Х     | Х                 | Х     | Х     | Х       | Х     | Х     | Х     |  |  |  |

| PF NAME | : | T1LSDATA | : | TIMEF | R 1 LS BY | TE DATA | REGISTI | ER |

|---------|---|----------|---|-------|-----------|---------|---------|----|

|         |   |          |   |       |           |         |         |    |

|             | R/W   | BIT 7 | BIT 6                 | BIT 5 | BIT 4    | BIT 3    | BIT 2 | BIT 1 | BIT 0 |  |  |  |

|-------------|-------|-------|-----------------------|-------|----------|----------|-------|-------|-------|--|--|--|

| P5          | READ  |       | LSB DECREMENTER VALUE |       |          |          |       |       |       |  |  |  |

| >0105       | WRITE |       |                       | LSE   | B RELOAI | D REGIST | ER    |       |       |  |  |  |

| RESET VALUE |       | Х     | Х                     | Х     | Х        | Х        | Х     | Х     | х     |  |  |  |

| PF NAME : | T1CTL0 | : TIMER 1 CONTROL REGISTER 0 |

|-----------|--------|------------------------------|

|           |        |                              |

|             | R/W   | BIT 7 | BIT 6             | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |  |  |

|-------------|-------|-------|-------------------|-------|-------|-------|-------|-------|-------|--|--|--|

| P6          | READ  |       | MSB READOUT LATCH |       |       |       |       |       |       |  |  |  |

| >0106       | WRITE | Х     | T1OUT             | х     | х     | х     | х     | х     | х     |  |  |  |

| RESET VALUE |       | Х     | 0                 | Х     | Х     | Х     | Х     | Х     | Х     |  |  |  |

T1OUT : Timer 1 toggle output enable bit.

> This write bit determines PORT B0 is timer 1 toggle output pin or normal I/O pin. 0 = PORT B0 is normal I/O pin.

1 = PORT B0 is timer 1 toggle output in, and B0 is toggle when Timer 1 decrements through zero value.

| PF NAM | <u>1E : T10</u> | CTL1   | : TIMER 1 CONTROL REGISTER 1 |        |        |          |         |           |       |  |  |

|--------|-----------------|--------|------------------------------|--------|--------|----------|---------|-----------|-------|--|--|

|        | R/W             | BIT 7  | BIT 6                        | BIT 5  | BIT 4  | BIT 3    | BIT 2   | BIT 1     | BIT 0 |  |  |

| P7     | READ            |        | LSB CAPTURE LATCH            |        |        |          |         |           |       |  |  |

| >0107  | WRITE           | START1 | SOURC1                       | T1HALT | PRESCA | ALER REL | OAD REC | GISTER (F | PL)   |  |  |

| RESET  | RESET VALUE     |        | Х                            | 0      | Х      | Х        | Х       | Х         | Х     |  |  |

Write : SOURC1 : 0 = Internal clock source Fosc/4

1 = External clock source from A4/ECI1

START1 : 0 = Timer 1 is stop, hold current count value and clear INT2 flag.

1 = Timer 1 reloads prescaler and decrementer, begins decrementing.

T1HALT : 0 = Timer 1 remains active when execute IDLE instruction. (WAKE-UP)

1 = Timer 1 will halt when execute IDLE instruction. (HALT)

#### DMC73C168

| PF NAM | E : T2M | ISDATA | A : TIMER 2 MS BYTE DATA REGISTER |       |        |          |       |       |       |  |  |  |  |

|--------|---------|--------|-----------------------------------|-------|--------|----------|-------|-------|-------|--|--|--|--|

|        | R/W     | BIT 7  | BIT 6                             | BIT 5 | BIT 4  | BIT 3    | BIT 2 | BIT 1 | BIT 0 |  |  |  |  |

| P8     | READ    |        | MSB READOUT LATCH                 |       |        |          |       |       |       |  |  |  |  |

| >0108  | WRITE   |        |                                   | MSB   | READOL | JT REGIS | TER   |       |       |  |  |  |  |

| RESET  | VALUE   | Х      | Х                                 | х     | Х      | Х        | Х     | Х     | Х     |  |  |  |  |

PF NAME : T2LSDATA : TIMER 2 LS BYTE DATA REGISTER

|             | R/W   | BIT 7 | BIT 6 | BIT 5 | BIT 4    | BIT 3    | BIT 2 | BIT 1 | BIT 0 |

|-------------|-------|-------|-------|-------|----------|----------|-------|-------|-------|

| P9          | READ  |       |       | LSB [ | DECREM   | ENTER V  | ALUE  |       |       |

| >0109       | WRITE |       |       | LSE   | 3 RELOAI | D REGIST | ER    |       |       |

| RESET VALUE |       | Х     | Х     | Х     | Х        | Х        | Х     | Х     | Х     |

| PF NA       | ME : T | 2CTL0      | : TIMER 2 CONTROL REGISTER 0 |           |         |         |       |       |       |  |

|-------------|--------|------------|------------------------------|-----------|---------|---------|-------|-------|-------|--|

|             | R/W    | BIT 7      | BIT 6                        | BIT 5     | BIT 4   | BIT 3   | BIT 2 | BIT 1 | BIT 0 |  |

| P10         | READ   |            |                              | MSE       | B READO | UT LATC | Н     |       |       |  |

| >010A       | WRITE  | CASCADE    | T2OUT                        | Х         | х       | х       | х     | х     | х     |  |

| RESET VALUE |        | 0          | 0                            | Х         | х       | х       | х     | х     | х     |  |

| T2OU        | Т:     | Timer 2 to | oggle outp                   | ut enable | bit.    |         |       |       |       |  |

This write bit determines PORT B1 is timer 2 toggle output pin or normal I/O pin. 0 = PORT B1 is normal I/O pin.

1 = PORT B1 is timer 1 toggle output pin, and B1 is toggle when Timer 2 decrements through zero value.

#### CASCADE : Timer 2 cascade control bit

- 0 = Timer 2 is not cascaded with Timer 1, Timer 2 clock is determined by source bit.

- 1 = Timer 1 and 2 are cascaded, clock source is generated by Timer 1 reload pulse, overrides source bit.

#### DMC73C168

| PF                         | NAM         | E : T20 | CTL1   | :      | : TIMER 2 CONTROL REGISTER 1 |       |          |          |          |        |  |  |

|----------------------------|-------------|---------|--------|--------|------------------------------|-------|----------|----------|----------|--------|--|--|

|                            |             | R/W     | BIT 7  | BIT 6  | BIT 5                        | BIT 4 | BIT 3    | BIT 2    | BIT 1    | BIT 0  |  |  |

| P11 READ LSB CAPTURE LATCH |             |         |        |        |                              |       |          |          |          |        |  |  |

| >010                       | )B          | WRITE   | START2 | SOURC2 | T2HALT                       | PRES  | SCALER F | RELOAD F | REGISTER | R (PL) |  |  |

| RE                         | RESET VALUE |         | 0      | Х      | 0                            | Х     | Х        | Х        | Х        | Х      |  |  |

|                            |             |         |        |        |                              |       |          |          |          |        |  |  |

Write : SOURC2 : 0 = Internal clock source Fosc/4

1 = External clock source from A5/ECI2

START2 : 0 = Timer 2 is stop, hold current count value and clear INT6 flag.

1 = Timer 2 reloads prescaler and decrementer, begins decrementing.

T2HALT : 0 = Timer 2 remains active when execute IDLE instruction. (WAKE-UP)

1 = Timer 2 will halt when execute IDLE instruction. (HALT)

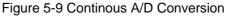

#### 3) A/D CONVERTER REGISTERS

PF NAME : APSLCT

: PORT A SELECT CONTROL REGISTER

|                                                                                                                                                                                    | R/W        | BIT 7                                   | BIT 6                          | BIT 5    | BIT 4     | BIT 3     | BIT 2        | BIT 1        | BIT 0   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------|--------------------------------|----------|-----------|-----------|--------------|--------------|---------|--|--|--|--|

| P13                                                                                                                                                                                | READ       | INT3SEL                                 | INT40SEL                       | NOT      | USED      | AD2SEL    | AD1SEL       | AMIFSEL      | FMIFSEL |  |  |  |  |

| >010C                                                                                                                                                                              | WRITE      | INT3SEL                                 | INT40SEL                       | NOT      | USED      | AD2SEL    | AD1SEL       | AMIFSEL      | FMIFSEL |  |  |  |  |

| RESET                                                                                                                                                                              | VALUE      | 0                                       | 0                              | 0        | 0         | 0         | 0            | 0            | 0       |  |  |  |  |

| FMIFSE                                                                                                                                                                             | L          |                                         |                                |          |           |           |              |              |         |  |  |  |  |

| AMIFSE                                                                                                                                                                             |            | FM and A                                | M IF input e                   | nahle hi | ts This r | ead/write | hits disahlı | e dinital in | nuts    |  |  |  |  |

|                                                                                                                                                                                    | <b>_</b> . |                                         | •                              |          |           |           |              | o aigitai in | 5010    |  |  |  |  |

|                                                                                                                                                                                    |            | when FM and AM IF inputs are enabled.   |                                |          |           |           |              |              |         |  |  |  |  |

|                                                                                                                                                                                    |            | 0 = PORT A0 and A1 are normal I/O pins. |                                |          |           |           |              |              |         |  |  |  |  |

|                                                                                                                                                                                    |            | 1 = PORT A0 and A1 are disabled.        |                                |          |           |           |              |              |         |  |  |  |  |

| AD1SEL                                                                                                                                                                             |            |                                         |                                |          |           |           |              |              |         |  |  |  |  |

| AD2SEL                                                                                                                                                                             | .:         |                                         | erter input er<br>converter ir |          |           |           |              | <b>o</b> .   | outs    |  |  |  |  |

|                                                                                                                                                                                    |            |                                         | A2 and A3                      | •        |           |           |              |              |         |  |  |  |  |

|                                                                                                                                                                                    |            |                                         | A2 and A3                      |          |           | 11.0.     |              |              |         |  |  |  |  |

|                                                                                                                                                                                    | ч          | I = FURI                                | AZ anu AS                      | ale ulsa | ibleu.    |           |              |              |         |  |  |  |  |

| INT40SE                                                                                                                                                                            |            |                                         |                                |          |           |           | , .          |              |         |  |  |  |  |

| INT3SEL : External interrupt 3 and 4-0 input enable bits. This read/write disable Digital inputs when A/D converter inputs are enabled.<br>0 = PORT A7 and A6 are normal I/O pins. |            |                                         |                                |          |           |           |              |              | Digital |  |  |  |  |

|                                                                                                                                                                                    |            | 1 = PORT                                | A7 and A6                      | are disa | bled      |           |              |              |         |  |  |  |  |

### DMC73C168

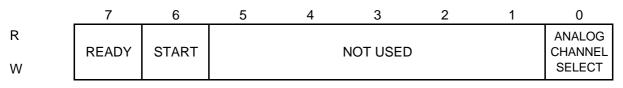

| PF NAME | E : ADCT | Ľ | : A/D CC | NTROL F | REGISTER | २ |

|---------|----------|---|----------|---------|----------|---|

|         |          |   |          |         |          |   |

|             | R/W   | BIT 7  | BIT 6 | BIT 5 | BIT 4    | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |

|-------------|-------|--------|-------|-------|----------|-------|-------|-------|-------|--|

| P14         | READ  | READY  | START |       | NOT USED |       |       |       |       |  |

| >010E       | WRITE | READYC | START |       | NOT USED |       |       |       |       |  |

| RESET VALUE |       | 0      | 0     | Х     | Х        | Х     | Х     | Х     | 0     |  |

#### READ :

READY : 0 = No Operation or Incomplete Conversion 1 = Complete Conversion

#### WRITE

ADCHS : 0 = A/D Converter Input Channel is PORT A2

1 = A/D Converter Input Channel is PORT A3

START : 0 = Conversion Stop 1 = Conversion Start

READYC: 0 = Ineffect

1 = Clear Ready Flag

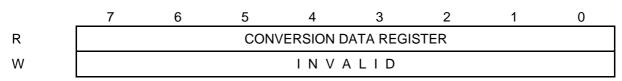

#### PF NAME : ADDATA : A/D CONVERTER DATA REGISTER

| PF NAME . ADDATA |       |                          | . AD CC            | INVERIE |       | CEGISTER | ς     |       |       |

|------------------|-------|--------------------------|--------------------|---------|-------|----------|-------|-------|-------|

|                  | R/W   | BIT 7                    | BIT 6              | BIT 5   | BIT 4 | BIT 3    | BIT 2 | BIT 1 | BIT 0 |

| P15              | READ  | CONVERSION DATA REGISTER |                    |         |       |          |       |       |       |

| >010F            | WRITE |                          | NOT USED (INVALID) |         |       |          |       |       |       |

| RESET VALUE      |       | 0                        | 0                  | 0       | 0     | 0        | 0     | 0     | 0     |

#### 4) PLL (PHASE LOCKED LOOP) REGISTER

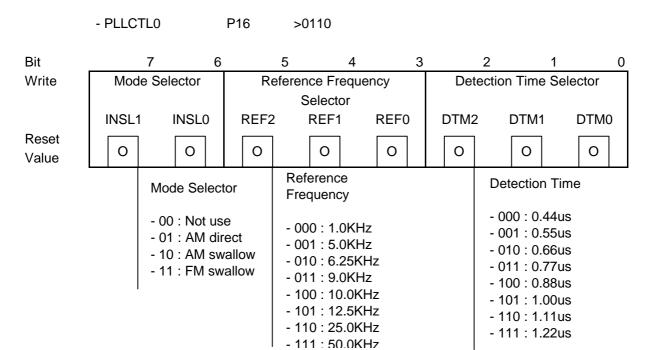

PF NAME : PLLCTL0 : PLL CONTROL REGISTER 0

|                   | R/W   | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| P16 READ NOT USED |       |       |       |       |       | 5     |       |       |       |

| >0110             | WRITE | INSL1 | INSL0 | REF2  | REF1  | REF0  | DTM2  | DTM1  | DTM0  |

| RESET VALUE       |       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

### DMC73C168

### WRITE :

PHASE DETECT TIME SELECT

| DTM2 | DTM1 | DTM0 | DETECT TIME |

|------|------|------|-------------|

| 0    | 0    | 0    | 0.44 us     |

| 0    | 0    | 1    | 0.55 us     |

| 0    | 1    | 0    | 0.66 us     |

| 0    | 1    | 1    | 0.77 us     |

| 1    | 0    | 0    | 0.88 us     |

| 1    | 0    | 1    | 1.00 us     |

| 1    | 1    | 0    | 1.11 us     |

| 1    | 1    | 1    | 1.22 us     |

#### PHASE DETECT TIME SELECT

| REF2 | REF1 | REF0 | REF. FREQ |

|------|------|------|-----------|

| 0    | 0    | 0    | 1.0 KHz   |

| 0    | 0    | 1    | 5.0 KHz   |

| 0    | 1    | 0    | 6.25 KHz  |

| 0    | 1    | 1    | 9.0 KHz   |

| 1    | 0    | 0    | 10.0 KHz  |

| 1    | 0    | 1    | 12.5 KHz  |

| 1    | 1    | 0    | 25.0 KHz  |

| 1    | 1    | 1    | 50.0 KHz  |

#### MODE SELECT

| INSL1 | INSL0 | INPUT MODE |  |  |  |  |

|-------|-------|------------|--|--|--|--|

| 0     | 0     | NOT USED   |  |  |  |  |

| 0     | 1     | AM DIRECT  |  |  |  |  |

| 1     | 0     | AM SWALLOW |  |  |  |  |

| 1     | 1     | FM SWALLOW |  |  |  |  |

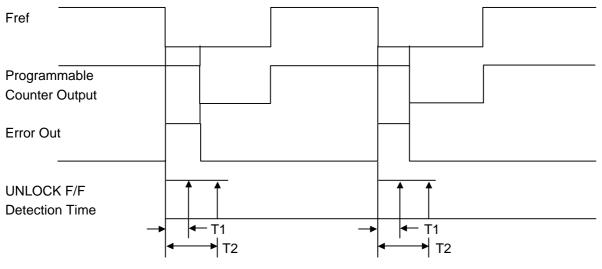

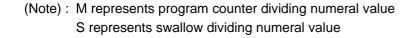

PF NAME : PLLCTL1 : PLL START/STOP CONTROL REGISTER 1

|             | R/W   | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3  | BIT 2  | BIT 1 | BIT 0 |

|-------------|-------|-------|-------|-------|-------|--------|--------|-------|-------|

| P17         | READ  | READY | х     | х     | х     | REFTST | PLLTST | UL1   | ULO   |

| >0111       | WRITE | PLLEN | х     | х     | х     | REFTST | PLLTST | NOT   | USED  |

| RESET VALUE |       | 0     | Х     | Х     | х     | 0      | 0      | 0     | 0     |

### DMC73C168

READ :

PLL UNLOCK STATUS DETECT :

| UL1 | UL0 | STATUS              |

|-----|-----|---------------------|

| 0   | 0   | PLL LOCK/STOP/OFF   |

| 0   | 1   | REF FREQ > VCO FREQ |

| 1   | 0   | REF FREQ < VCO FREQ |

| 1   | 1   | NOT USED            |

READY : 0 = NO OPERATION 1 = ACTIVE

WRITE :

- PLLTST : PLL TEST BIT (ATTENTION : SHOULD BE SET "0" IN NORMAL OPERATION) 0 = ACTIVE NORMAL

- 1 = TEST MODE

- REFTST : REFERENCE DIVIDER TEST BIT(SHOULD BE SET "0" IN NORMAL OPERATION) 0 = ACTIVE NORMAL OPERATION

- 1 = REFERENCE TEST MODE

- PLLEN : 0 = PLL OFF, PLL STOP 1 = PLL ON, PLL START

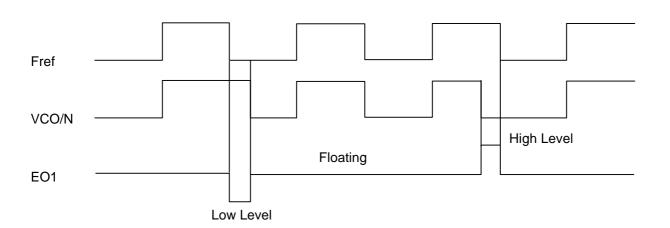

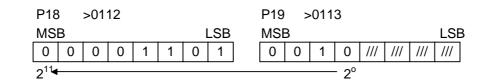

PF NAME : PLLDATAH : PLL PC MSB DATA REGISTER

|             | R/W   | BIT 7 | BIT 6           | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |

|-------------|-------|-------|-----------------|-------|-------|-------|-------|-------|-------|--|

| P18         | READ  |       | PLL PC MSB DATA |       |       |       |       |       |       |  |

| >0112       | WRITE |       |                 |       |       |       |       |       |       |  |

| RESET VALUE |       | 0     | 0               | 0     | 0     | 0     | 0     | 0     | 0     |  |

PF NAME : PLLDATAL : PLL PC LSB DATA REGISTER

|                          | R/W         | BIT 7 | BIT 6 | BIT 5                 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|--------------------------|-------------|-------|-------|-----------------------|-------|-------|-------|-------|-------|

| P19 READ PLL PC LSB DATA |             |       |       | SWALLOW COUNTER VALUE |       |       |       |       |       |

| >0113                    | >0113 WRITE |       |       |                       |       |       |       |       |       |

| RESET VALUE              |             | 0     | 0     | 0                     | 0     | 0     | 0     | 0     | 0     |

### DMC73C168

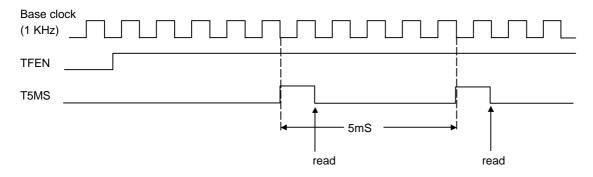

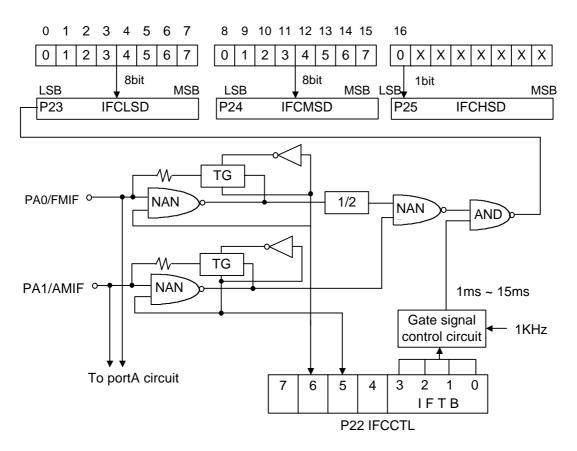

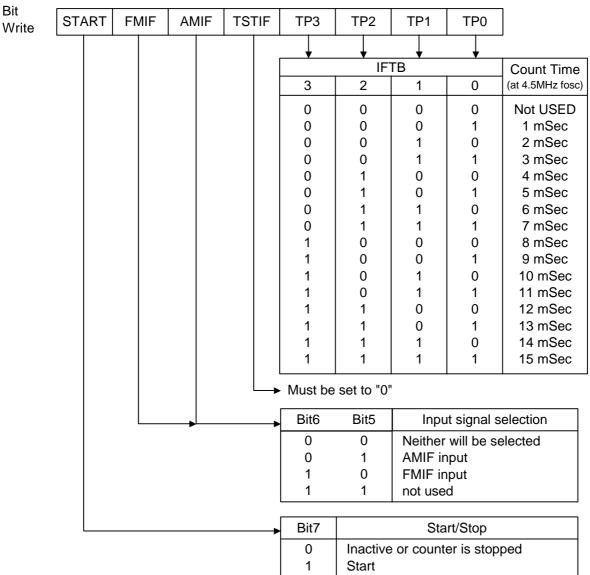

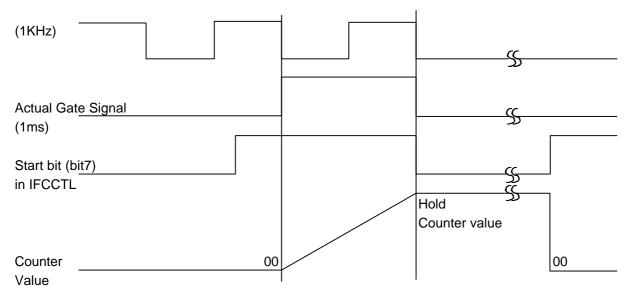

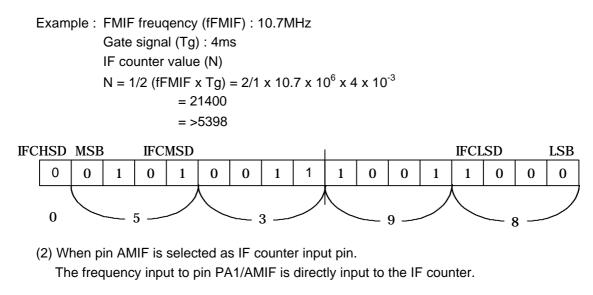

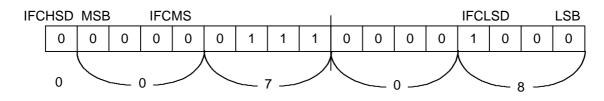

5) IF COUNTER REGISTER

|       | R/W   | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| P22   | READ  | READY | FMIF  | AMIF  | TSTIF | TP3   | TP2   | TP1   | TP0   |

| >0116 | WRITE | START |       |       |       |       |       |       |       |

| RESET | VALUE | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

READ :

WRITE :

IF FREQ. COUNTING PERIOD SELECT (TP0, TP1, TP2, TP3)

| TP3 | TP2 | TP1 | TP0 | COUNT TIME |

|-----|-----|-----|-----|------------|

| 0   | 0   | 0   | 0   | Х          |

| 0   | 0   | 0   | 1   | 1 ms       |

| 0   | 0   | 1   | 0   | 2 ms       |

| 0   | 0   | 1   | 1   | 3 ms       |

| 0   | 1   | 0   | 0   | 4 ms       |

| 0   | 1   | 0   | 1   | 5 ms       |

| 0   | 1   | 1   | 0   | 6 ms       |

| 0   | 1   | 1   | 1   | 7 ms       |

| 1   | 0   | 0   | 0   | 8 ms       |

| 1   | 0   | 0   | 1   | 9 ms       |

| 1   | 0   | 1   | 0   | 10 ms      |

| 1   | 0   | 1   | 1   | 11 ms      |

| 1   | 1   | 0   | 0   | 12 ms      |

| 1   | 1   | 0   | 1   | 13 ms      |

| 1   | 1   | 1   | 0   | 14 ms      |

| 1   | 1   | 1   | 1   | 15 ms      |

TSTIF : IF COUNTER TEST BIT

(ATTENTION : SHOULD BE SET TO "0" IN NORMAL OPERATION) 0 = NORMAL ACTIVE MODE

1 = TEST MODE

AMIF, FMIF : IF COUNTER INPUT SELECT

| - |      |      | -              |

|---|------|------|----------------|

|   | FMIF | AMIF | COUNTING INPUT |

|   | 0    | 0    | NOT INPUT      |

|   | 0    | 1    | AMIF           |

|   | 1    | 0    | FMIF           |

|   | 1    | 1    | Х              |

READY : 0 = INACTIVE OR COMPLETE COUNTER 1 = INCOMPLETE OR ACTIVE COUNTER

### DMC73C168

#### START : IF COUNTER START/STOP 0 = STOP (DISABLE) 1 = START (ENABLE)

#### PF NAME : IFCLSD : IF COUNTER LSB VALUE

|       | R/W   | BIT 7           | BIT 6                | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-----------------|----------------------|-------|-------|-------|-------|-------|-------|

| P23   | READ  |                 | IF COUNTER LSB VALUE |       |       |       |       |       |       |

| >0117 |       |                 |                      |       |       |       |       |       |       |

| RESET | VALUE | 0 0 0 0 0 0 0 0 |                      |       |       |       |       | 0     |       |

IF Counter LSB data bits

This read bits are LSB 8 bits of 17 bits IF Counter.

#### PF NAME : IFCMSD : IF COUNTER VALUE

|       | R/W   | BIT 7 | BIT 6                  | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|------------------------|-------|-------|-------|-------|-------|-------|

| P24   | READ  |       | IF COUNTER MSB-1 VALUE |       |       |       |       |       |       |

| >0118 |       |       |                        |       |       |       |       |       |       |

| RESET | VALUE | 0     | 0                      | 0     | 0     | 0     | 0     | 0     | 0     |

IF Counter MSB data bits

This read bits are MSB 8 bits (from bit-15 to bit-8) of 17 bits IF Counter.

#### PF NAME : IFCHSD : IF COUNTER MSB VALUE

|       |              |       | . 11 000                                  |   |   | - |   |   |   |

|-------|--------------|-------|-------------------------------------------|---|---|---|---|---|---|

|       | R/W          | BIT 7 | BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 |   |   |   |   |   |   |

| P25   | READ         |       | NOT USED                                  |   |   |   |   |   |   |

| >0119 |              |       |                                           |   |   |   |   |   |   |

| RESET | ESET VALUE X |       | х                                         | х | х | х | х | х | 0 |

IF Counter MSB data bits

This read bits are MSB 1 bits (bit-16) of 17 bits IF Counter.

## DMC73C168

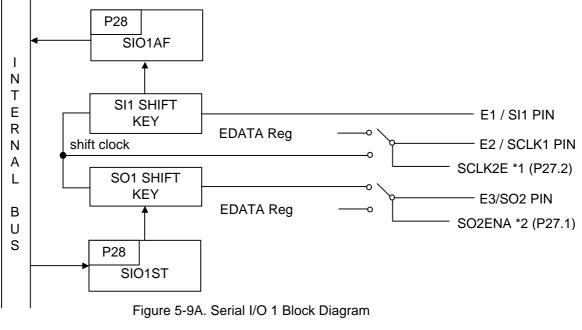

6) SERIAL I/O REGISTERS

| PF NAME : SIO1CTL |       | : SERIAL                           | _ I/O 1 CC                                                                                                                                                                                                                                                 |                            | REGISTER                 | ۲          |            |        |       |  |

|-------------------|-------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------|------------|------------|--------|-------|--|

|                   | R/W   | BIT 7                              | BIT 6                                                                                                                                                                                                                                                      | BIT 5                      | BIT 4                    | BIT 3      | BIT 2      | BIT 1  | BIT 0 |  |

| P27               | READ  | SIO1AF                             | CKSRC1                                                                                                                                                                                                                                                     | BAU11                      | BAU10                    | SIO1EF     | SCLK1E     | SO1ENA | Х     |  |

| >011B             | WRITE | SIO1ST                             | CKSRC1                                                                                                                                                                                                                                                     |                            |                          | SIO1EC     | SCLK1E     | SO1ENA | Х     |  |

| RESET V           | ALUE  | 0                                  | 0                                                                                                                                                                                                                                                          | 0                          | 0                        | 0          | 0          | 0      | х     |  |

| SIO1AF            | :     | This read<br>0 = SIO1              | HO1 operation flag bit.<br>his read bit determines SIO1 is enabled or not.<br>= SIO1 is stop state<br>= SIO1 is processing state                                                                                                                           |                            |                          |            |            |        |       |  |

| SIO1ST            | :     | This write<br>0 = SIO1<br>1 = SIO1 | <ul> <li>SIO1 start enable bit</li> <li>This write bit determines SIO1 is start or not.</li> <li>= SIO1 is stop</li> <li>= SIO1 is started</li> <li>Caution : This bit should be reset to "0" before 8bit transmition for proper SIO operation.</li> </ul> |                            |                          |            |            |        |       |  |

| CKSRC1            | :     | This read<br>0 = SIO1              | SIO1 clock source selection bit<br>This read/write bit determines SIO1 clock source in from external or internal.<br>0 = SIO1 clock is from internal<br>1 = SIO1 clock is from external                                                                    |                            |                          |            |            |        |       |  |

| BAU1n             | :     |                                    | nsmission<br>//write bits                                                                                                                                                                                                                                  | -                          |                          | ansmissior | n speed.   |        |       |  |

|                   |       | BAU11                              | BAU10                                                                                                                                                                                                                                                      | SCLK                       | FREQ. (F                 | osc = 4.5  | MKHz)      |        |       |  |

|                   |       | 0                                  | 0                                                                                                                                                                                                                                                          | Fos                        | c/8 =                    | = 563      | KHz        |        |       |  |

|                   |       | 0                                  | 1                                                                                                                                                                                                                                                          | Fos                        | c/16 =                   | = 281      | KHz        |        |       |  |

|                   |       | 1                                  | 0                                                                                                                                                                                                                                                          |                            |                          |            | KHz        |        |       |  |

| SIO1EF            | :     | Transmis<br>This read<br>0 = Overr | 11Fosc/64=70 KHzTransmission error flag bit<br>This read bit shows overrun error was occured or not<br>0 = Overrun error is not occured<br>1 = Overrun error is occured                                                                                    |                            |                          |            |            |        |       |  |

| SIO1EC            | :     | This write<br>0 = Trans            |                                                                                                                                                                                                                                                            | nines trar<br>rror flag is | nsmission<br>s not affec | •          | is cleared | or not |       |  |

### DMC73C168

| SCLK1E : | <ul> <li>SIO1 clock enable bit</li> <li>This read/write bit determines PORT E2 bit is SIO1 clock output pin or not</li> <li>0 = PORT E2 is normal I/O port</li> <li>1 = PORT E2 is assigned SIO1 clock output pin when "CKSRC1" is set.<br/>(Then, PORT E2 direction should be output)</li> </ul> |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SO1ENA : | Serial output enable bit<br>This read/write bit determines PORT E0 is SO1 pin or not<br>0 = PORT E0 is normal I/O port                                                                                                                                                                            |

PF NAME : SIO1BUF : SERIAL I/O 1 DATA REGISTER

|       | R/W   | BIT 7 | BIT 6                  | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|------------------------|-------|-------|-------|-------|-------|-------|

| P28   | READ  |       | SIO1 RECEIVING DATA    |       |       |       |       |       |       |

| >011C | WRITE |       | SIO1 TRANSMITTING DATA |       |       |       |       |       |       |

| RESET | VALUE | Х     | х                      | Х     | Х     | Х     | Х     | х     | х     |

#### X : INDETERMINATOR

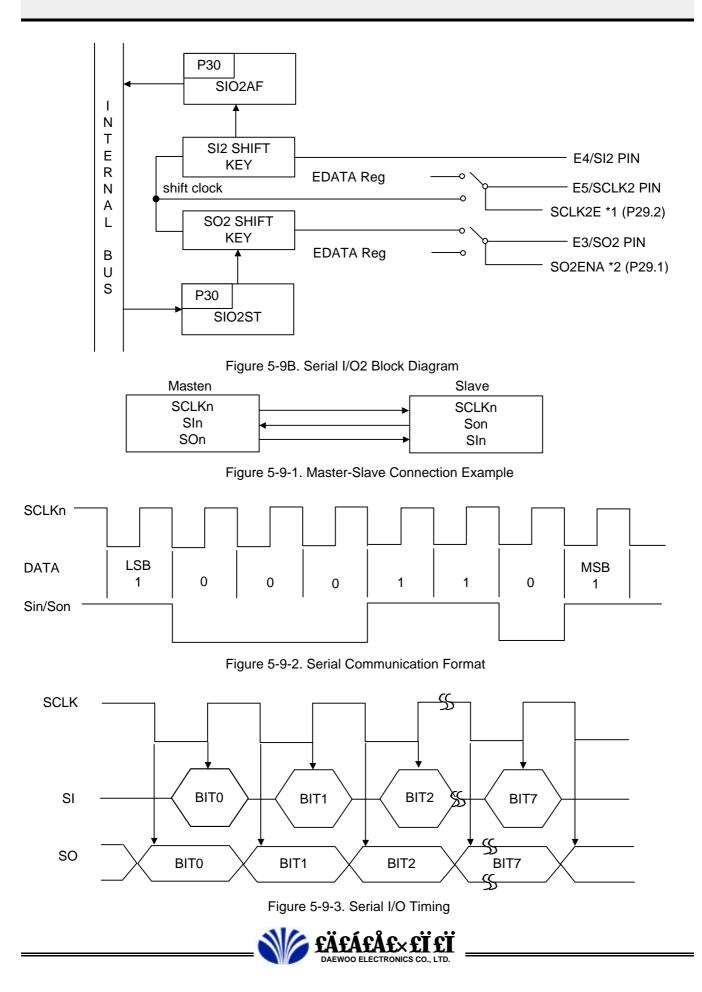

| PF NAME : SIO2CTL | : SERIAL I/O 2 CONTROL REGISTER |

|-------------------|---------------------------------|

|                   |                                 |

|        |                                                                                                                                                                                                                              | · <b></b>                                                                                                                                                                                                                                                      |        |       |       |        | · · · · · · · · · · · · · · · · · · · |        |       |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|--------|---------------------------------------|--------|-------|

|        | R/W                                                                                                                                                                                                                          | BIT 7                                                                                                                                                                                                                                                          | BIT 6  | BIT 5 | BIT 4 | BIT 3  | BIT 2                                 | BIT 1  | BIT 0 |

| P29    | READ                                                                                                                                                                                                                         | SIO2AF                                                                                                                                                                                                                                                         | CKSRC2 | BAU21 | BAU20 | SIO2EF | SCLK2E                                | SO2ENA | х     |

| >011D  | WRITE                                                                                                                                                                                                                        | SIO2ST                                                                                                                                                                                                                                                         | CKSRC2 |       |       | SIO2EC | SCLK2E                                | SO2ENA | х     |

| RESET  | VALUE                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                              | 0      | 0     | 0     | 0      | 0                                     | 0      | Х     |

| SIO2AF | :                                                                                                                                                                                                                            | <ul><li>SIO2 Operation flag bit.</li><li>This read bit determines SIO2 is enabled or not.</li><li>0 = SIO2 is stop state</li><li>1 = SIO2 is processing state</li></ul>                                                                                        |        |       |       |        |                                       |        |       |

| SIO2ST | :                                                                                                                                                                                                                            | <ul> <li>SIO2 start enable bit.</li> <li>This write bit determines SIO2 is start or not</li> <li>0 = SIO2 is stop</li> <li>1 = SIO2 is start</li> <li>* Caution : This bit should be reset to "0" before 8bit transmition for proper SIO operation.</li> </ul> |        |       |       |        |                                       |        |       |

| CKSRC2 | <ul> <li>SIO2 clock source selection bit</li> <li>This read/write bit determines SIO2 clock source in from external or internal</li> <li>0 = SIO2 clock is from internal</li> <li>1 = SIO2 clock is from external</li> </ul> |                                                                                                                                                                                                                                                                |        |       |       |        | internal                              |        |       |

|        |                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                |        |       |       |        |                                       |        |       |

<sup>1 =</sup> PORT E0 is assigned SO1 pin (Then, PORT E0 direction should be output state)

### DMC73C168

| BAU2n :  | SIO2 transmission speed select bits.<br>This read/write bits determine SIO2 transmission speed.                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|          | BAU21 BAU20 SCLK FREQ. (Fosc=4.5KHz)                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|          | 0 	 0 	 Fosc/8 = 563 	 KHz                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|          | 0 1 Fosc/16 = 281 KHz                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|          | 1 0 Fosc/32 = 141 KHz                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|          | 1 1 Fosc/64 = 70 KHz                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

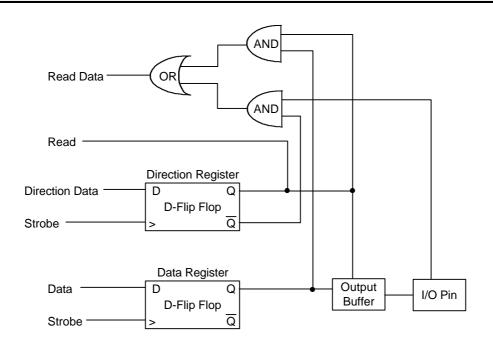

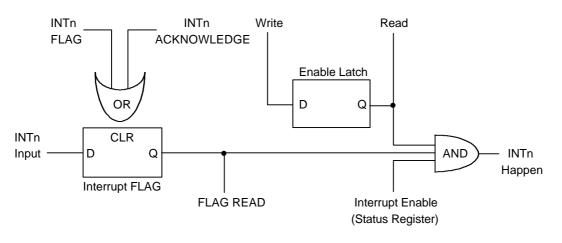

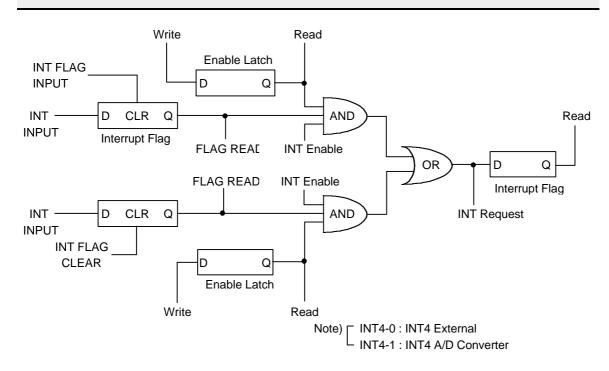

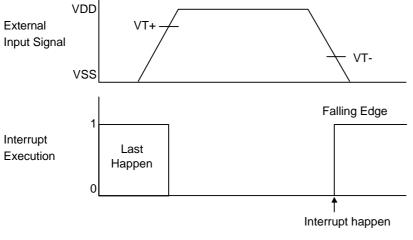

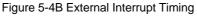

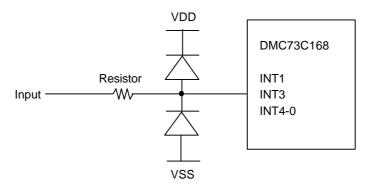

| SIO2EF : | Transmission error flag bit<br>This read bit shows overrun error was occured or not<br>0 = Overrun error is not occured<br>1 = Overrun error is occured                                                                                                                                           |  |  |  |  |  |  |  |  |  |