# **General Description**

The DM9301 is a physical-layer, single-chip, lowpower media converter for 100BASE-TX/FX full duplex repeater applications. On the TX media side, it provides a direct interface to Unshielded Twisted Pair Cable 5 (UTP5) for 100BASE-TX Fast Ethernet. On the FX media side, it provides a direct interface to a Pseudo Emitter Coupled Logic level interface (PECL).

The DM9301 uses a low power and high performance CMOS process. It contains the entire physical layer functions of 100BASE-TX as defined by IEEE802.3u, including the Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA), Twisted Pair Physical Medium Dependent Sublayer (TP-PMD) and a PECL compliant interface for a fiber optic module, compliant with ANSI X3.166. The DM9301 provides two independent clock recovery circuits to minimize bit delay through the converter (no FIFO are used to buffer data between the FX and TX interfaces). Furthermore, due to the excellent rise/fall time control by a built-in wave-shaping filter, the DM9301 needs no external filter to transport signals to the media on the 100Base-TX interface.

### **Patent-Pending Circuits**

- Smart adaptive receiver equalizer

- Digital algorithm for high frequency clock/data recovery circuit

- High speed wave-shaping circuit

# **Table of Contents**

| General Description1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block Diagram1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table of contents2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Features3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pin Configuration: DM9301 QFP4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin Description5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Functional Description10100Base-FX to TX Operation10FX PECL Receiver10FX Receiver Clock Recovery Module10FX NRZI to NRZ Converter10FX Serial to Parallel Converter11FX Code Group Alignment Monitor11TX Scrambler11TX Parallel to Serial Converter11TX NRZ to NRZI Converter11TX NRZ to NRZI Converter11TX NRZI to MLT-3 Converter11TX MLT-3 Driver11100Base-TX to FX Operation12TX Signal Detect12TX Digital Adaptive Equalization12TX NRZI to NRZI Decoder13TX NRZI to NRZ Decoder13TX Serial to Parallel Converter13TX Serial to Parallel Converter13TX NRZI to NRZ Decoder13TX Serial to Parallel Converter13TX Clock Recovery Module13TX Serial to Parallel Converter13TX Code Group Monitor13TX Descrambler13 |

| <ul> <li>FX Parallel to Serial Converter</li> <li>FX NRZ to NRZI Encoder</li> <li>Link Monitor and LED Driver</li> </ul>                                                                                                                                        | 13             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Absolute Maximum Ratings                                                                                                                                                                                                                                        | 14             |

| DC Electrical Characteristics                                                                                                                                                                                                                                   | 15             |

| AC Electrical Characteristics                                                                                                                                                                                                                                   | 16             |

| <ul> <li>Timing Waveforms</li> <li>100BASE-TX to FX Transmit Timing Diagram</li> <li>100BASE-FX to TX Transmit Timing Diagram</li> <li>5-Bit Symbol 100Base-TX/FX Transmit Timing Diagram</li> <li>5-Bit Symbol 100Base-TX/FX Receive Timing Diagram</li> </ul> | 17<br>17<br>17 |

| Application Circuit (For Reference Only)                                                                                                                                                                                                                        | 19             |

| Package Information                                                                                                                                                                                                                                             | 21             |

| Ordering Information                                                                                                                                                                                                                                            | 22             |

| Disclaimer                                                                                                                                                                                                                                                      | 22             |

| Company Overview                                                                                                                                                                                                                                                | 22             |

| Products                                                                                                                                                                                                                                                        | 22             |

| Contact Windows                                                                                                                                                                                                                                                 | 22             |

| Warning                                                                                                                                                                                                                                                         | 22             |

# Features

- 100BASE-TX/FX single-chip media converter

- Total bit delay from FX to TX interface is 20 bit times (10 bit times each direction).

- Optional propagate HALT on no Link condition

- Compliant with IEEE802.3u 100BASE-TX standard

- Compliant with ANSI X3T12 TP-PMD 1995 standard

- Compliant with ANSI X3.166 FDDI-PMD

- Supports Half and Full Duplex operation 100Mbps, the DM9301 operates in Full Duplex mode at all times

- High performance 100Mbps clock generator and data recovery circuit

- Controlled output edge rates in the 100Base-TX transmitter without the need for an external filter

- LED support for FX Link, TX link, FX receive data, TX receive data, FX code group error and TX code group error.

- Built in LED test, all LED will light during a reset condition on the DM9301

- Digital clock recovery and regeneration circuit using an advanced digital algorithm to minimize jitter

- Supports diagnostic TX to TX analog loopback and FX to FX analog loopback (Loopback at the NRZI interface)

- Supports diagnostic TX to TX digital loopback and FX to FX digital loopback (Loopback at the 5B symbol interface)

- Low-power, high-performance CMOS process

- Available in a 100 QFP package

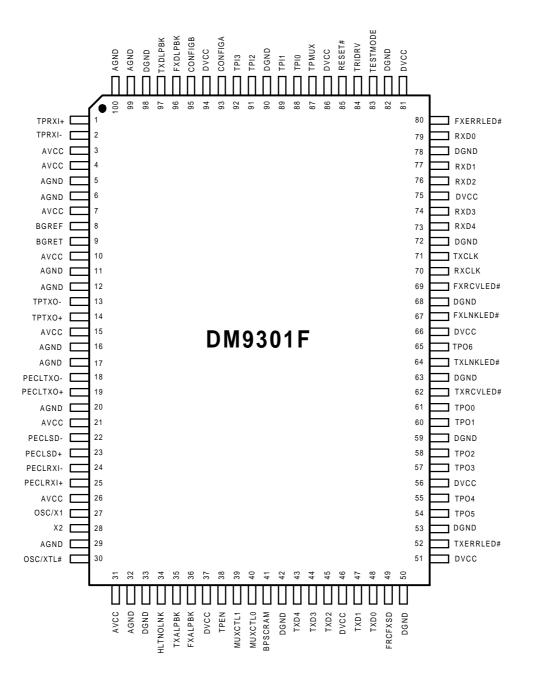

# Pin Configuration: DM9301F QFP

# **Pin Description**

| Pin No.         | Pin Name              | I/O | Description                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-----------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Media Interface |                       |     | ·                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 1, 2            | TPRXI+,<br>TPRXI-     | I   | <b>100Mbps-TX Differential Input Pair:</b><br>These pins are differential receive input for 100BASE-<br>TX. They are capable of receiving 100BASE-TX MLT-3<br>data.                                                                               |  |  |  |  |  |  |

| 13, 14          | TPTXO-,<br>TPTXO+     | 0   | <b>100BASE-TX Differential Output Pair:</b><br>These outputs drive MLT-3 encoded data over 100Mbps<br>twisted pair cable and provide controlled rise and fall<br>times designed to filter the transmitter output,<br>reducing any associated EMI. |  |  |  |  |  |  |

| 24, 25          | PECLRXI-,<br>PECLRXI+ | 1   | <b>100BASE-FX PECL Receive Data Differential Pair:</b><br>These pins are differential receive input for 100BASE-<br>FX PECL. They are capable of receiving PECL<br>100BASE-FX NRZI data.                                                          |  |  |  |  |  |  |

| 18, 19          | PECLTXO-,<br>PECLTXO+ | 0   | <b>100BASE-FX Transmit Differential Output Pair:</b><br>These outputs drive NRZI encoded data for PECL FX interface.                                                                                                                              |  |  |  |  |  |  |

| 22, 23          | PECLSD-,<br>PECLSD+   | I   | <b>100BASE-FX PECL Signal detect:</b><br>These pins are differential signals that indicate to the DM9301 that the Optical Module interface is detecting valid optical energy.                                                                     |  |  |  |  |  |  |

| Clock and Misc. | . Interface           |     |                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 27              | OSCI/X1               | I   | <b>Crystal or Oscillator Input:</b><br>This pin should connect to one side of a 25MHz, 50ppm<br>crystal if OSC/XTL#=0. This pin is the 25MHz, 50ppm<br>external TTL oscillator input, if OSC/XTLB=1.                                              |  |  |  |  |  |  |

| 28              | X2                    | 0   | <b>Crystal Oscillator Output:</b><br>The other side of a 25MHz, 50ppm crystal should<br>connect to this pin if OSC/XTL#=0. Leave this pin open<br>if OSC/XTL#=1.                                                                                  |  |  |  |  |  |  |

| 30              | OSC/XTL#              | 1   | Crystal or Oscillator Selector Pin:<br>OSC/XTL#=0: An external 25MHz, 50ppm crystal<br>should connect to X1 and X2 pins.<br>OSC/XTL#=1: An external 25MHz, 50ppm oscillator<br>should connect to X1 and left X2 pin<br>open.                      |  |  |  |  |  |  |

| 8               | BGREF                 | 1   | <b>Bandgap Voltage Reference Resistor:</b><br>It connects to a $6.49K\Omega$ , 1% error tolerance resistor<br>between this pin and BGRET pin 9 to provide an<br>accurate current reference for the chip.                                          |  |  |  |  |  |  |

| 9               | BGRET                 | I   | Bandgap Return<br>Return pin for 6.49KΩ resistor connection, DO NOT<br>CONNECT TO GROUND.                                                                                                                                                         |  |  |  |  |  |  |

| Clock and Misc | . Interface (Continued | )  |                                                                                                                   |  |  |  |  |  |

|----------------|------------------------|----|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 84             | TRIDRV                 | I  | Tristate Digital Output Pins:<br>When set high, all digital output pins are set to high                           |  |  |  |  |  |

|                |                        |    | impedance.                                                                                                        |  |  |  |  |  |

| 85             | RESET#                 | I  | <b>Reset:</b> Active Low input that initializes the DM9301, must be asserted low for 30msecs after VCC is stable. |  |  |  |  |  |

| 34             | HLTNOLNK               | 1  | Send Halt on no Link Condition:                                                                                   |  |  |  |  |  |

| 54             | HEINOENK               |    | Causes the DM9301 to Send out a Halt symbol to the                                                                |  |  |  |  |  |

|                |                        |    | TX interface if no FX link active or send out a Halt                                                              |  |  |  |  |  |

|                |                        |    | symbol to the FX interface if no TX link active.                                                                  |  |  |  |  |  |

|                |                        |    | Propagates a no-link condition to the Link Partner if 1,                                                          |  |  |  |  |  |

|                |                        |    | Idle symbol if 0. Active high                                                                                     |  |  |  |  |  |

| 93             | CONFIGA                |    | Config A: Must be connected to GND                                                                                |  |  |  |  |  |

| 95             | CONFIGB                |    | Config B: Must be connected to GND                                                                                |  |  |  |  |  |

| LED Interface  |                        |    |                                                                                                                   |  |  |  |  |  |

| 67             | FXLNKLED#              | OD | FX Link LED:                                                                                                      |  |  |  |  |  |

|                |                        |    | Indicates Good Link status for 100Mbps FX operation.                                                              |  |  |  |  |  |

|                |                        |    | Active low (Open Drain Output)                                                                                    |  |  |  |  |  |

| 64             | TXLNKLED#              | OD | TX Link LED:                                                                                                      |  |  |  |  |  |

|                |                        |    | Indicates Good Link status for 100Mbps TX operation.                                                              |  |  |  |  |  |

| 60             | FXRCVLED#              | OD | Active low (Open Drain Output)  FX Receive LED:                                                                   |  |  |  |  |  |

| 69             | FARGVLED#              | UD | Indicates the presence of receive activity for 100Mbps                                                            |  |  |  |  |  |

|                |                        |    | FX operation. Active low (Open Drain Output)                                                                      |  |  |  |  |  |

|                |                        |    | The DM9301 incorporates a "monostable" function on                                                                |  |  |  |  |  |

|                |                        |    | the FXRCVLED output. This ensures that even                                                                       |  |  |  |  |  |

|                |                        |    | minimum size packets generate adequate LED ON to                                                                  |  |  |  |  |  |

|                |                        |    | insure visibility.                                                                                                |  |  |  |  |  |

| 62             | TXRCVLED#              | OD | TX Receive LED:                                                                                                   |  |  |  |  |  |

|                |                        |    | Indicates the presence of receive activity for 100Mbps                                                            |  |  |  |  |  |

|                |                        |    | TX operation. Active low (Open Drain Output)                                                                      |  |  |  |  |  |

|                |                        |    | The DM9301 incorporates a "monostable" function on                                                                |  |  |  |  |  |

|                |                        |    | the TXRCVLED output. This ensures that even                                                                       |  |  |  |  |  |

|                |                        |    | minimum size packets generate adequate LED ON to insure visibility.                                               |  |  |  |  |  |

| 80             | FXERRLED#              | OD | FX Error LED:                                                                                                     |  |  |  |  |  |

| 00             |                        | 02 | Indicates an error was detected by the FX Code Group                                                              |  |  |  |  |  |

|                |                        |    | Alignment Monitor function on the FX receiver. Active                                                             |  |  |  |  |  |

|                |                        |    | low (Open Drain Output)                                                                                           |  |  |  |  |  |

|                |                        |    | The DM9301 incorporates a "monostable" function on                                                                |  |  |  |  |  |

|                |                        |    | the FXERRLED output. This ensures that even                                                                       |  |  |  |  |  |

|                |                        |    | minimum size errors generate adequate LED ON to                                                                   |  |  |  |  |  |

|                |                        |    | insure visibility.                                                                                                |  |  |  |  |  |

| LED Interface(C          | Continued)                         |    |                                                                                                                                                                                                                                                                                                             |

|--------------------------|------------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52                       | TXERRLED#                          | OD | TX Error LED:Indicates an error was detected by the TX Code GroupAlignment Monitor function on the TX receiver. ActiveIow (Open Drain Output)The DM9301 incorporates a "monostable" function onthe TXERRLED output. This ensures that evenminimum size errors generate adequate LED ON toinsure visibility. |

| <b>Diagnostic Por</b>    | t Interface                        |    |                                                                                                                                                                                                                                                                                                             |

| 36                       | FXALPBK                            | I  | <b>FX Interface Analog Loop Back:</b><br>Loops the FX NRZI analog transmit data path to the FX NRZI analog receive path.<br>Initiated at a H/W reset. Active high.                                                                                                                                          |

| 35                       | TXALPBK                            | I  | TX Interface Analog Loop Back:Loops the TX NRZI analog transmit data path to the TXNRZI analog receive path.Initiated at a H/W reset. Active high.                                                                                                                                                          |

| 96                       | FXDLPBK                            | I  | <b>FX Interface Digital Loop Back:</b><br>Loops the FX 5-bit symbol digital transmit data path to<br>the FX 5-bit symbol digital receive path.<br>Initiated at a H/W reset. Active high.                                                                                                                    |

| 97                       | TXDLPBK                            | I  | <b>TX Interface Digital Loop Back:</b><br>Loops the TX 5-bit symbol digital transmit data path to<br>the TX 5-bit symbol digital receive path.<br>Initiated at a H/W reset. Active high.                                                                                                                    |

| 79, 77,<br>76, 74,<br>73 | RXD0, RXD1,<br>RXD2, RXD3,<br>RXD4 | 0  | Receive Data 4 through 0:<br>The receive data 5-bit symbol interface. Data is clocked<br>out on the falling edge of RXCLK.                                                                                                                                                                                  |

| 70                       | RXCLK                              | 0  | Receive Clock:25 Mhz recovered clock, clock source is selected by theMUXCTL1 and MUXCTL0.                                                                                                                                                                                                                   |

| 48, 47,<br>45, 44,<br>43 | TXD0, TXD1,<br>TXD2, TXD3,<br>TXD4 | Ι  | <b>Transmit Data 4 through 0:</b><br>The transmit data 5-bit symbol interface. Data is clocked in on the rising edge of TXCLK.                                                                                                                                                                              |

| 71                       | TXCLK                              | 0  | Transmit Clock:<br>25 Mhz recovered clock, clock source is selected by the<br>MUXCTL1 and MUXCTL0.                                                                                                                                                                                                          |

| Diagnostic Port                     | Interface (Continued                              | ) |                                                                                                                                                                                                                         |                       |                                                                                                         |  |  |  |  |

|-------------------------------------|---------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| 39, 40                              | MUXCTL1,<br>MUXCTL0                               | Ι | Mux. Control 1 and 0:Used for testing the DM9301 Data Paths. Set to zero for<br>normal operation.Initiated at a H/W reset. Active high.                                                                                 |                       |                                                                                                         |  |  |  |  |

|                                     |                                                   |   | MUXCTL1<br>0                                                                                                                                                                                                            | MUXCTI<br>0           | L0 DATA PATH<br>Normal, FX to TX and TX to FX                                                           |  |  |  |  |

|                                     |                                                   |   | 1                                                                                                                                                                                                                       | 0                     | TX Transmit from TXD[4:0]<br>TXCLK from TX PLL<br>TX Receive to RXD[4:0]<br>RXCLK from TX receive clock |  |  |  |  |

|                                     |                                                   |   | 0                                                                                                                                                                                                                       | 1                     | FX Transmit from TXD[4:0]<br>TXCLK from FX PLL<br>FX Receive to RXD[4:0]<br>RXCLK from FX receive clock |  |  |  |  |

|                                     |                                                   |   | 1                                                                                                                                                                                                                       | 1                     | TX Transmit from TXD[4:0]<br>TXCLK from TX PLL<br>FX Receive to RXD[4:0]<br>RXCLK from FX receive clock |  |  |  |  |

| 65, 54,<br>55, 57,<br>58, 60,<br>61 | TPO6, TPO5,<br>TPO4, TPO3,<br>TPO2, TPO1,<br>TPO0 | 0 | indicators is                                                                                                                                                                                                           | e DM9301<br>s made by | internal status. Selection of status<br>using TPEN and TPMUX.<br>et. Active high.                       |  |  |  |  |

| 92, 91, 89,<br>88                   | TPI3, TPI2, TPI1,<br>TPI0,                        | Ι | Test Port Input:Controls the DM9301 internal test features. Selection of<br>input control is made by using TPEN and TPMUX.TPEN must be true (one) for this signal to take effect.Initiated at a H/W reset. Active high. |                       |                                                                                                         |  |  |  |  |

| Diagnostic Port                          | Interface (Continue   | d)  |                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|-----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49                                       | FRCFXSD               |     | Force FX Signal Detect<br>Forces the DM9301 FX interface Signal Detect true<br>Initiated at a H/W reset. Active high.                                                                                                                                                                                                             |

| 38                                       | TPEN                  | 1   | <b>Test Port Enable:</b><br>Enables the DM9301 Test Port features.<br>Initiated at a H/W reset. Active high.                                                                                                                                                                                                                      |

| 87                                       | TPMUX                 | I   | Test Port Mux:Controls the DM9301Test Port Input and Output bits.A value of zero indicates the TX interface and a value ofone indicates the FX interface. TPEN must be true (one)for this signal to take effect.Initiated at a H/W reset. Active high.                                                                            |

| 41                                       | BPSCRAM               | I   | Bypass Scrambler:<br>Controls the DM9301 TX interface Scrambler/De-<br>scrambler function. A value of zero indicates to<br>scramble and de-scramble the TX interface 5-bit<br>symbol data to and from the FX interface. A value of one<br>bypasses the scrambler/de-scrambler function.<br>Initiated at a H/W reset. Active high. |

|                                          |                       |     | 19301 are grouped in pairs of two categories - Digital<br>Power/Ground Pair.                                                                                                                                                                                                                                                      |

| Group A - Digita                         | al Supply Pairs       |     |                                                                                                                                                                                                                                                                                                                                   |

| 33, 42, 50, 53,<br>63, 68, 82, 90,<br>98 | DGND                  | Р   | Digital Logic Ground.                                                                                                                                                                                                                                                                                                             |

| 37, 46, 51, 66,<br>81, 94                | DVCC                  | Р   | Digital Logic power supply                                                                                                                                                                                                                                                                                                        |

| Group B - Analo                          | og Circuit Supply Pai | irs |                                                                                                                                                                                                                                                                                                                                   |

| 5, 6, 11, 12, 20,<br>29, 32, 99, 100,    | AGND                  | Р   | Analog circuit ground                                                                                                                                                                                                                                                                                                             |

| 3, 4, 7, 15, 21,<br>26, 31               | AVCC                  | Р   | Analog circuit power supply                                                                                                                                                                                                                                                                                                       |

# **Functional Description**

The DM9301 Fast Ethernet single-chip TX/FX media converter, provides the functionality as specified in IEEE802.3, integrates the complete 100BASE-TX and a PECL optic module interface for 100Base-FX. The DM9301 implements the PCS, PMA, and TP-PMD sublayer functions, as defined by specification. The term "X" will be used to describe the sections used in the fiber PHY layer interface. The term "X" will be used to describe the sections used in the twisted-pair PMD layer interface.

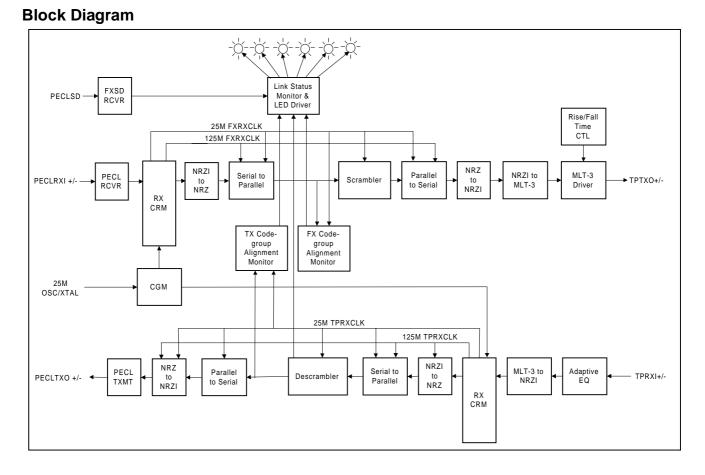

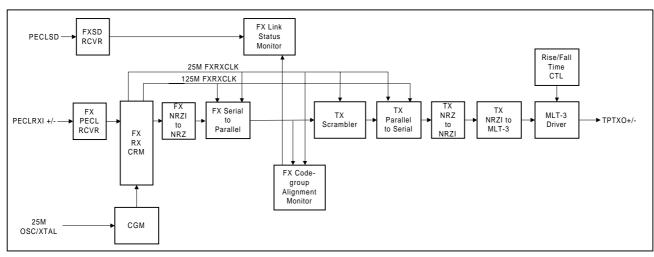

### **100BASE-FX to TX Operation**

The block diagram in figure 1 provides an overview of the functional blocks contained in the FX to TX media converter interface.

The FX to TX interface includes the following functional blocks:

- FX PECL Receiver

- FX Receiver Clock Recovery Module

- FX NRZI to NRZ Converter

- FX Serial to Parallel Converter

- FX Code Group Alignment Monitor

- TX Scrambler

- TX Parallel to Serial Converter

- TX NRZ to NRZI Converter

- TX NRZI to MLT-3 Converter

- TX MLT-3 Driver

### **FX PECL Receiver**

The PECL receiver receives NRZI encoded, differential Pseudo Emitter Coupled Logic level signal. The receiver converts the receive signal into a single-ended NRZI signal and presents this signal to the FX Clock Recovery Module.

#### FX Receiver Clock Recovery Module

The FX Clock Recovery Module accepts NRZI data from the PECL receiver. The FX Clock Recovery Module locks onto the data stream, using a Phase Lock Loop (PLL) and extracts the 125Mhz reference clock. The extracted and synchronized clock and data are presented to the FX NRZI to NRZ Decoder.

#### FX NRZI to NRZ Converter

The receive data stream is required to be NRZI encoded for compatibility with the standards for 100Base- FX. This conversion process must be reversed on the transmit end. The FX NRZI to NRZ decoder, receives the NRZI data stream from the FX Clock Recovery Module and converts it to a NRZ data stream to be presented to the FX Serial to Parallel conversion block.

#### FX to TX Block Diagram

#### FX Serial to Parallel Converter

The Serial to Parallel converter receives a serial data stream from the NRZI to NRZ converter, and converts the data stream to parallel data to be presented to the scrambler. The parallel data format presented to the TX scrambler is 5B coded.

### FX Code Group Alignment Monitor

The FX Code Group Alignment block receives nonaligned 5B data from the FX Serial to Parallel converter and monitors it for 5B code group violations. FX Code Group Alignment occurs after the J/K is detected, and subsequent data is monitored on a fixed boundary. If a violation is detected, the FX Code Group Alignment Monitor block signals the error to the Link Status Monitor block. In turn, the Link Status Monitor block flashes the FX error LED (FXERRLED#).

### **TX Scrambler**

The scrambler also receives data from the FX Serial to Parallel converter. Data from the serial to parallel conversion block is 5B symbol encoded. The scrambler is required to control the radiated emissions (EMI) by spreading the transmit energy across the frequency spectrum at the media connector and on the twisted pair cable in 100Base-TX transmit operation.

By scrambling the data, the total energy presented to the cable is randomly distributed over a wide frequency range. Without the scrambler, energy levels on the cable could peak beyond FCC limitations at frequencies related to repeated 5B sequences like continuous transmission of IDLE symbols. The scrambler output is combined with the NRZ 5B data from the FX Serial to Parallel converter via an XOR logic function. The result is a scrambled data stream with sufficient randomization to decrease radiated emissions at critical frequencies.

### **TX Parallel to Serial Converter**

The TX Parallel to Serial converter receives parallel 5B scrambled data from the scrambler and serializes it (converts it from a parallel to a serial data stream). The serialized data stream is then presented to the NRZ to NRZI converter block

### TX NRZ to NRZI Converter

After the transmit data stream has been scrambled and serialized, the data must be NRZI encoded for compatibility with the TP-PMD standard for 100Base-TX transmission over Category-5 unshielded twisted pair cable.

### **TX MLT-3 Converter**

The MLT-3 conversion is accomplished by converting the data stream output from the NRZI encoder into two binary data streams with alternately phased logic one events.

### TX MLT-3 Driver

The two binary data streams created at the MLT-3 converter are fed to the twisted pair output driver which converts these streams to current sources and alternately drives either side of the transmit transformer primary winding resulting in a minimal current MLT-3 signal.

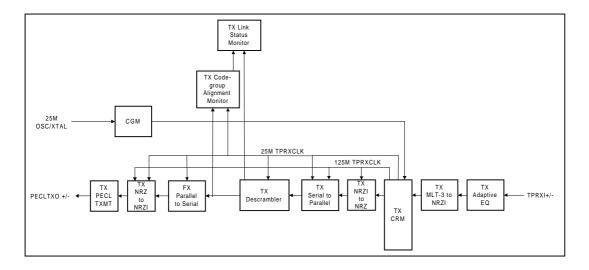

### 100Base-TX to FX Operation

The block diagram in figure 2 provides an overview of the functional blocks contained in the TX to FX media converter interface.

The TX to FX interface contains the following functional blocks:

- TX Digital Adaptive Equalization

- TX MLT-3 to NRZI

- TX Clock Recovery Module

- TX NRZI to NRZ Decoder

- TX Serial to Parallel Conversion

- TX Descrambler

- TX Code Group Alignment Monitor

- FX Parallel to Serial Conversion

- FX NRZ to NRZI

- FX PECL Transmitter

#### **TX Signal Detect**

The signal detect function meets the specifications mandated by the ANSI XT12 TP-PMD100Base-TX standards for both voltage thresholds and timing parameters.

#### **TX Digital Adaptive Equalization**

When transmitting data at high speeds over copper twisted pair cable, attenuation based on frequency becomes a concern. In high speed twisted pair signaling, the frequency content of the transmitted signal can vary areatly during normal operation based on the randomness of the scrambled data stream. This variation in signal attenuation caused by frequency variations must be compensated for to ensure the integrity of the received data. In order to ensure quality transmission when employing MLT-3 encoding, the compensation must be able to adapt to various cable lengths and cable types depending on the installed environment. The selection of long cable lengths for a given implementation, requires significant compensation which will be over-kill in a situation that includes shorter, less attenuating cable lengths. Conversely, the selection of short or intermediate cable lengths requiring less compensation will cause serious under-compensation for longer length cables.

TX to FX Block Diagram

Figure 2

Therefore, the compensation or equalization must be adaptive to ensure proper conditioning of the received signal independent of the cable length.

#### TX MLT-3 to NRZI Decoder

The DM9301 decodes the MLT-3 information from the TX Digital Adaptive Equalizer into NRZI data.

#### **TX Clock Recovery Module**

The TX Clock Recovery Module accepts NRZI data from the MLT-3 to NRZI decoder. The TX Clock Recovery Module locks onto the data stream and extracts the 125Mhz reference clock. The extracted and synchronized clock and data are presented to the NRZI to NRZ Decoder.

#### TX NRZI to NRZ Decoder

The TX transmit data stream is required to be NRZI encoded in for compatibility with the TP-PMD standard for 100Base-TX transmission over Category-5 unshielded twisted pair cable. This conversion process must be reversed on the receive end. The NRZI to NRZ decoder, receives the NRZI data stream from the TX Clock Recovery Module and converts it to a NRZ data stream to be presented to the TX Serial to Parallel conversion block.

#### **TX Serial to Parallel Converter**

The TX Serial to Parallel converter receives a serial data stream from the TX NRZI to NRZ decoder, and converts the data stream to parallel data to be presented to the TX descrambler. The parallel data format presented to the TX descrambler is 5B coded.

#### **TX Code Group Monitor**

The TX Code Group Alignment block receives nonaligned 5B data from the TX descrambler and monitors it for 5B code group violations. TX Code Group Alignment occurs after the J/K is detected, and subsequent data is monitored on a fixed boundary. If a violation is detected, the TX Code Group Monitor block signals the error to the Link Status Monitor block. In turn, the Link Status Monitor block flashes the TX error LED (TXERRLED#).

### TX Descrambler

Because of the scrambling process required to control the radiated emissions of transmit data streams, the receiver must descramble the receive data streams. The TX Descrambler receives scrambled parallel data streams from the Serial to Parallel converter, descrambles the data streams, and presents the data streams to the Code Group alignment block.

### **FX Parallel to Serial Converter**

The FX Parallel to Serial Converter receives parallel 5B data from the TX de-scrambler and serializes it (converts it from a parallel to a serial data stream). The serialized data stream is then presented to the FX NRZ to NRZI Encoder block

### FX NRZ to NRZI Encoder

After the transmit data stream has been serialized, the data must be NRZI encoded for compatibility with the standard for 100Base-FX.

#### Link Monitor and LED Driver

The Link Monitor block monitors both the TX and FX interfaces for link active, receive data and erring 5-bit stream.

The Link Monitor has the ability to detect each interfaces link status. The TX will transmit either an Idle symbol or a Halt symbol if the FX link is not established. Conversely the FX will transmit either an Idle symbol or a Halt symbol if the TX link is not established. When an o Link" condition exists, the interface pin called LTNOLNK" will cause Halt symbols to be transmitted instead of Idle symbols.

The link active LED is a static indication of the TX and FX links. It will be true to indicate the presence of a link. The receive data and error LED are generated through a ne-Shot" so that even the smallest receive or error condition will be indicated.

# Absolute Maximum Ratings\*

### Absolute Maximum Ratings (25°C)

| Symbol | Parameter                           | Min. | Max. | Unit | Conditions    |

|--------|-------------------------------------|------|------|------|---------------|

| Vcc    | Max. Supply Voltage                 |      | 7.0  | V    | Non-operating |

| Vin    | DC Input Voltage (VIN)              | -0.5 | 5.5  | V    |               |

| Vout   | DC Output Voltage(Vout)             | -0.5 | 5.5  | V    |               |

| Tstg   | Storage Temperature Rang (Tstg)     | -65  | +150 | °C   |               |

| PD     | Power Dissipation (PD)              |      | 1    | W    |               |

| LT     | Lead Temp. (TL, Soldering, 10 sec.) |      | 240  | °C   |               |

| ESD    | ESD rating (Rzap=1.5K,Czap=100pF)   |      | 4000 | V    |               |

#### **Operating Conditions**

| Symbol              | Parameter        | Min. | Max. | Unit | Conditions |

|---------------------|------------------|------|------|------|------------|

| DVcc,AVcc           | Supply Voltage   | 4.75 |      | 5.25 |            |

| Тс                  | Case Temperature | 0    | 85   | Ŝ    |            |

| PD                  | 100BASE-TX       |      | 200  | mA   | 5V         |

| (Power Dissipation) |                  |      |      |      |            |

#### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **DC Electrical Characteristics** (Vcc = 5V)

| Symbol   | Parameter                                                | Min.         | Тур. | Max.         | Unit | Conditions                  |

|----------|----------------------------------------------------------|--------------|------|--------------|------|-----------------------------|

| TTL Inpu | ts                                                       |              |      |              |      |                             |

| (DPLXSE  | L, RESET# )                                              |              |      |              |      |                             |

| VIL      | Input Low Voltage                                        |              |      | 0.8          | V    | IIL = -400uA                |

| Vін      | Input High Voltage                                       | 2.0          |      |              | V    | IIH = 100uA                 |

| lı∟      | Input Low Current                                        | -200         |      |              | uA   | VIN = 0.4V                  |

| Ін       | Input High Current                                       |              |      | 100          | uA   | VIN = 2.7V                  |

| LED Driv | er Outputs                                               | -            | -    |              | -    |                             |

| (FXLINKL | ED#, TXLINKLED#, FXRXD#,RXRX                             | D#)          |      |              |      |                             |

| Vol      | Output Low Voltage                                       |              |      | 0.4          | V    | IOL = 8mA                   |

| Vон      | Output High Voltage                                      | 2.4          |      |              | V    | Іон = -0.1mA                |

| TPTX Re  | ceiver                                                   |              |      |              |      |                             |

| VICM     | RXI+/RXI- Input Common-Mode<br>Voltage                   | 1.5          | 2.0  | 2.5          | V    | 100 Ω Termination<br>Across |

| TPTX Tra |                                                          |              |      |              |      |                             |

| ITD100   | 100TXO+/- 100BASE-TX Mode<br>Differential Output Current | 19           | 20   | 21           | mA   |                             |

| PECL FX  | Transmitter                                              |              |      |              |      |                             |

| IFD100   | PECLTX+/- 100BASE-FX Mode<br>Differential Output Current | 19           | 20   | 21           | mA   |                             |

| Vон      | PECL Output Voltage – High                               | VCC-<br>1.05 |      | VCC-<br>0.88 | V    |                             |

| Vol      | PECL Output Voltage – Low                                | VCC-<br>1.81 |      | VCC-<br>1.62 | V    |                             |

# AC Electrical Characteristics (Over full range of operating condition unless specified otherwise)

| Symbol        | Parameter                                 | Min. | Тур. | Max. | Unit | Conditions      |

|---------------|-------------------------------------------|------|------|------|------|-----------------|

| Transmit      | ter                                       |      |      |      |      |                 |

| ttr/f         | 100TXO+/- Differential Rise/Fall Time     | 3.0  |      | 5.0  | ns   |                 |

| tтм           | 100TXO+/- Differential Rise/Fall Time     | -0.5 |      | 0.5  | ns   |                 |

|               | Mismatch                                  |      |      |      |      |                 |

| <b>t</b> TDC  | 100TXO+/- Differential Output Duty Cycle  | -0.5 |      | 0.5  | ns   |                 |

|               | Distortion                                |      |      |      |      |                 |

| tt/t          | 100TXO+/- Differential Output Peak-to-    |      | 300  |      | ps   |                 |

|               | Peak Jitter                               |      |      |      |      |                 |

| Xost          | 100TXO+/- Differential Voltage Overshoot  |      |      | 5    | %    |                 |

| PECL Tra      | Insmitter (FX Transmit Interface)         |      |      |      |      |                 |

| ptTR/F        | 100FXTD+/- Differential Rise/Fall Time    | 1.0  |      | 2.0  | ns   |                 |

| ptтм          | 100FXTD+/- Differential Rise/Fall Time    | -0.5 |      | 0.5  | ns   |                 |

|               | Mismatch                                  |      |      |      |      |                 |

| ptTDC         | 100FXTD+/- Differential Output Duty Cycle | -0.5 |      | 0.5  | ns   |                 |

|               | Distortion                                |      |      |      |      |                 |

| ptppj         | 100FXTD+/- Differential Output Peak-to-   |      |      | 300  | ps   |                 |

|               | Peak Jitter                               |      |      |      |      |                 |

| ptddj         | 100FXTD+/- Differential Output Data       |      |      | 2.0  | ns   |                 |

|               | Dependent Jitter                          |      |      |      |      |                 |

| Clock Sp      | ecifications                              |      |      |      |      |                 |

| Xntol         | TX Input Clock Frequency Tolerance        | -50  |      | +50  | ppm  | 25MHz Frequency |

|               | (Oscillator or Crystal input frequency)   |      |      |      |      |                 |

| Xbtol         | TX Output Clock Frequency Tolerance       | -100 |      | +100 | ppm  | 25MHz Frequency |

| <b>t</b> PWH  | OSC Pulse Width High                      | 14   |      |      | ns   |                 |

| <b>t</b> PWL  | OSC Pulse Width Low                       | 14   |      |      | ns   |                 |

| <b>t</b> RPWH | RX_CLK Pulse Width High                   | 14   |      |      | ns   |                 |

| <b>t</b> RPWL | RX_CLK Pulse Width Low                    | 14   |      |      | ns   |                 |

# **Timing Waveforms**

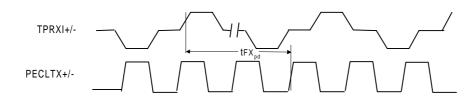

### 100BASE-TX to FX Transmit Timing Diagram

### **100BASE-TX to FX Transmit Timing Parameters**

| Symbol            | Parameter                              | Min. | Typ <sup>1</sup> . | Max. | Unit | Conditions |

|-------------------|----------------------------------------|------|--------------------|------|------|------------|

| tFX <sub>pd</sub> | TPRXI+/- to PECLTX+/- Out (FX Latency) | -    | -                  | 10   | ΒT   |            |

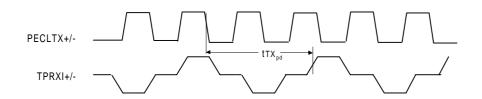

### 100BASE-FX to TX Transmit Timing Diagram

### **100BASE-FX to TX Transmit Timing Parameters**

| Symbol            | Parameter                                 | Min. | Typ <sup>1</sup> . | Max. | Unit | Conditions |

|-------------------|-------------------------------------------|------|--------------------|------|------|------------|

| t⊤x <sub>pd</sub> | PECLRX+/- to TPTXo+/- Out (TX<br>Latency) | -    | -                  | 10   | BT   |            |

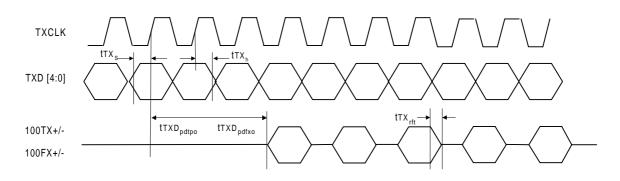

### 5-Bit Symbol 100Base-TX/FX Transmit Timing Diagram

### 5-Bit Symbol 100Base-TX/FX Transmit Timing Parameters

| Symbol                 | Parameter                                          | Min.       | Typ.1        | Max.     | Unit    | Conditions                              |

|------------------------|----------------------------------------------------|------------|--------------|----------|---------|-----------------------------------------|

| t⊤x <sub>s</sub>       | TXD[4:0] Setup To TX_CLK High                      | 11         | -            | -        | ns      |                                         |

| t⊤x <sub>h</sub>       | TXD[4:0] Hold From TX_CLK<br>High                  | 0          | -            | -        | ns      |                                         |

| tTXD <sub>pdtpo</sub>  | TXD[4:0] Sampled To TPTXO<br>(TXD to TP Latency)   | -          | -            | 6        | BT      |                                         |

| tTXD <sub>pdfxo</sub>  | TXD[4:0] Sampled To PECLTXO<br>(TXD to FX Latency) | -          | -            | 4        | BT      |                                         |

| t⊤x <sub>r/f</sub>     | 100TX Driver Rise/Fall Time                        | 3          | 4            | 5        | ns      | 90% To 10%, Into<br>100ohm Differential |

| <sup>1</sup> . Typical | values are at 25and are for design a               | id only; r | not guarante | ed and r | not sub | ject to production testing.             |

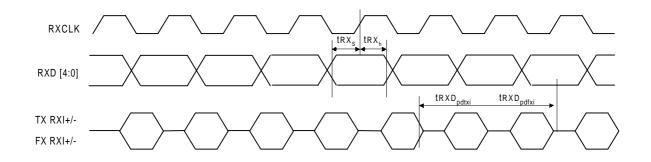

# 5-Bit Symbol 100Base-TX/FX Receive Timing Diagram

### 5-Bit Symbol 100Base-TX/FX Receive Timing Parameter

| Symbol                | Parameter                                  | Min. | Typ <sup>1</sup> . | Max. | Unit | Conditions |

|-----------------------|--------------------------------------------|------|--------------------|------|------|------------|

| tRX <sub>s</sub>      | RXD[4:0) Setup To RX_CLK<br>High           | 10   | -                  | -    | ns   |            |

| tRX <sub>h</sub>      | RXD[4:0]Hold From RX_CLK<br>High           | 10   | -                  | -    | ns   |            |

| tRXD <sub>pdtxi</sub> | TXRXI In To RXD[0:3] Out (Rx<br>Latency)   | -    | -                  | 6    | BT   |            |

| tRXD <sub>pdfxi</sub> | PECLRDI In To RXD[4:0] Out<br>(Rx Latency) | -    | -                  | 4    | BT   |            |

# MII Application Circuit: DM9301 QFP (For Reference Only)

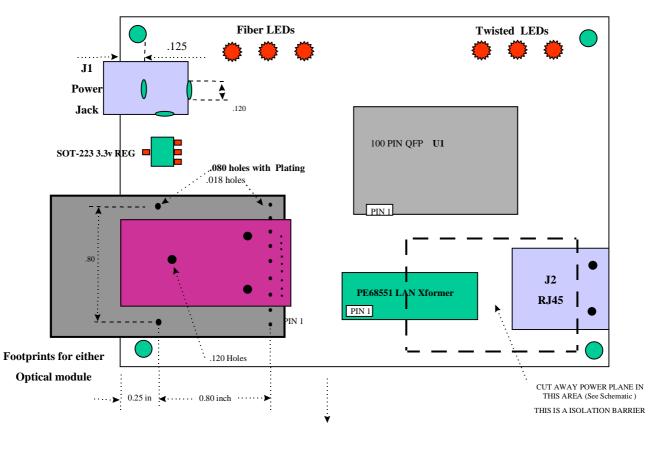

# DM9301 Sample, suggested placement

.350

MII Application Circuit: DM9301 QFP (Continued, For Reference Only)

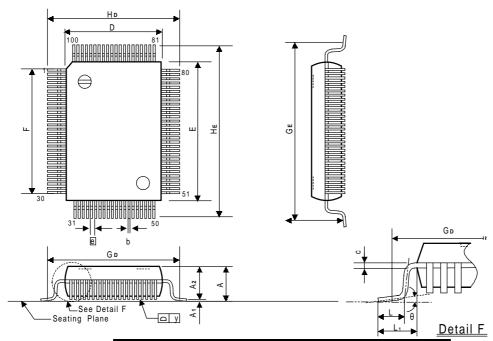

# Package Information

### **QFP 100L Outline Dimensions**

Unit: Inches/mm

| Symbol | Dimensions In Inches | <b>Dimensions In mm</b> |

|--------|----------------------|-------------------------|

| А      | 0.130 Max.           | 3.30 Max.               |

| A1     | 0.004 Min.           | 0.10 Min.               |

| A2     | 0.1120.005           | 2.850.13                |

| b      | 0.012 +0.004         | 0.31 +0.10              |

|        | -0.002               | -0.05                   |

| С      | 0.006 +0.004         | 0.15 +0.10              |

|        | -0.002               | -0.05                   |

| D      | 0.5510.005           | 14.00+/-0.13            |

| E      | 0.7870.005           | 20.00+/-0.13            |

| е      | 0.026 0.006          | 0.650.15                |

| F      | 0.742 NOM.           | 18.85 NOM.              |

| Gd     | 0.693 NOM.           | 17.60 NOM.              |

| Ge     | 0.929 NOM.           | 23.60 NOM.              |

| Ho     | 0.7400.012           | 18.800.31               |

| HE     | 0.9760.012           | 24.790.31               |

| L      | 0.0470.008           | 1.190.20                |

| Ц      | 0.0950.008           | 2.410.20                |

| у      | 0.006 Max.           | 0.15 Max.               |

| θ      | 0° ~ 12°             | 0° ~ 12°                |

#### Note:

1. Dimension D & E do not include resin fins.

2. Dimension GD & GE are for PC Board surface mount pad pitch design reference only.

3. All dimensions are based on metric system.

# **Ordering Information**

| Part Number | Pin Count | Package |

|-------------|-----------|---------|

| DM9301F     | 100       | QFP     |

# Disclaimer

The information appearing in this publication is believed to be accurate. Integrated circuits sold by DAVICOM Semiconductor are covered by the warranty and patent indemnification provisions stipulated in the terms of sale only. DAVICOM makes no warranty, express, statutory, implied or by description regarding the information in this publication or regarding the information in this publication or regarding the freedom of the described chip(s) from patent infringement. FURTHER, DAVICOM MAKES NO WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PURPOSE. DAVICOM reserves the right to halt production or alter the specifications and prices at any time without notice. Accordingly, the reader is cautioned to verify that the data sheets and other information in this publication are current before placing orders. Products described herein are intended for use in normal commercial applications. Applications involving unusual environmental or reliability requirements, e.g. military equipment or medical life support equipment, are specifically not recommended without additional processing by DAVICOM for such applications. Please note that application circuits illustrated in this document are for reference purposes only.

DAVICOM 's terms and conditions printed on the order acknowledgment govern all sales by DAVICOM. DAVICOM will not be bound by any terms inconsistent with these unless DAVICOM agrees otherwise in writing. Acceptance of the buyer's orders shall be based on these terms.

# **Company Overview**

DAVICOM Semiconductor, Inc. develops and manufactures integrated circuits for integration into data communication products. Our mission is to design and produce IC products that are the industry's best value for Data, Audio, Video, and Internet/Intranet applications. To achieve this goal, we have built an organization that is able to develop chipsets in response to the evolving technology requirements of our customers while still delivering products that meet their cost requirements.

# Products

We offer only products that satisfy high performance requirements and which are compatible with major hardware and software standards. Our currently available and soon to be released products are based on our proprietary designs and deliver high quality, high performance chipsets that comply with modem communication standards and Ethernet networking standards.

# **Contact Windows**

For additional information about DAVICOM products, contact the sales department at:

#### Headquarters

Hsin-chu Office: 3F, No. 7-2, Industry E. Rd., IX, Science-based Park, Hsin-chu City, Taiwan, R.O.C. TEL: 886-3-5798797 FAX: 886-3-5798858 Taipei Sales & Marketing Office: 8F, No. 3, Lane 235, Bao-chiao Rd., Hsin-tien City, Taipei, Taiwan, R.O.C. TEL: 02-29153030 FAX: 02-29157575 Email: sales@davicom.com.tw

### Davicom USA

**Sunnyvale, California** 1135 Kern Ave., Sunnyvale, CA94086, U.S.A. TEL: 1-408-7368600 FAX: 1-408-7368688 Email: <u>sales@davicom8.com</u>

#### WARNING

Conditions beyond those listed for the absolute maximum may destroy or damage the products. In addition, conditions for sustained periods at near the limits of the operating ranges will stress and may temporarily (and permanently) affect and damage structure, performance and/or function.