# Radiation Hard Programmable Peripheral Interface

DS3575-5.0 January 2000

Replaces June 1999 version, DS3575-4.0

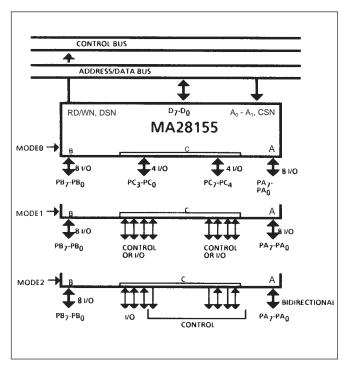

The MA28155 is a general purpose programmable Input/ Output device designed for use with the MAS281 microprocessor. It has 24 I/O pins which may be individually programmed in 2 groups of 12 and used in 3 major modes of operation.

In the first mode (MODE 0), each group of 12 I/O pins may be programmed in sets of 4 to be inputs or outputs. In the second mode (MODE 1), each group may be programmed to have 8 lines of input or output. Of the remaining 4 pins, 3 are used for hand-shaking and interrupt control signals. The third mode of operation (MODE 2) is the bidirectional bus mode, which uses 8 lines for a bidirectional bus and 5 lines, borrowing one from the other group, for hand-shaking.

#### **FEATURES**

- Radiation Hard to 1MRad (Si)

- High SEU Immunity, Latch Up Free

- Silicon-on-Sapphire Technology

- 24 Programmable I/O Pins

- All Inputs and Outputs are TTL Compatible

- Direct Bit Set/Reset Capability Easing Control Application Interface

- Replaces Several MSI Packages

- Compatible with MAS281 (Mil-Std-1750A) Microprocessor

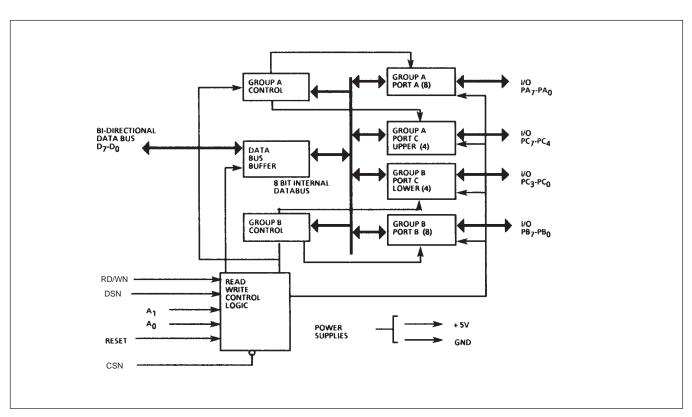

Figure 1: Block Diagram

#### **FUNCTIONAL DESCRIPTION**

The MA28155 is a programmable peripheral interface (PPI) device designed for use with MAS281. Its function is that of a general purpose I/O component to interface peripheral equipment to the microcomputer system bus. The functional configuration of the MA28155 is programmed by the system software so that, normally, no external logic is necessary to interface peripheral devices or structures.

#### **Data Bus Buffer**

This 3-state, bidirectional, 8-bit buffer is used to interface the MA28155 to the system data bus. Data is transmitted or received by the buffer upon execution of input or output instructions by the CPU. Control words and status information are also transferred through the data bus buffer.

#### Read/Write and Control Logic

The function of this block is to manage all of the internal and external transfers of both Data and Control Status words. It accepts inputs from the CPU Address and Control busses and in turn, issues commands to both of the Control Groups.

#### Reset (RESET)

A high on this input clears the control register and all ports (A,B,C) are set to the input mode.

#### Chip Select (CSN)

A low on this input pin enables the communication between the MA28155 and the CPU.

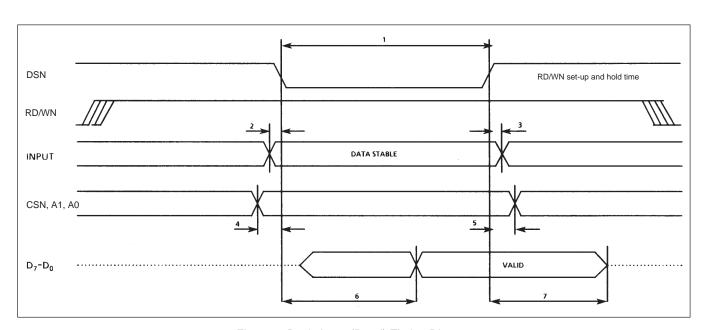

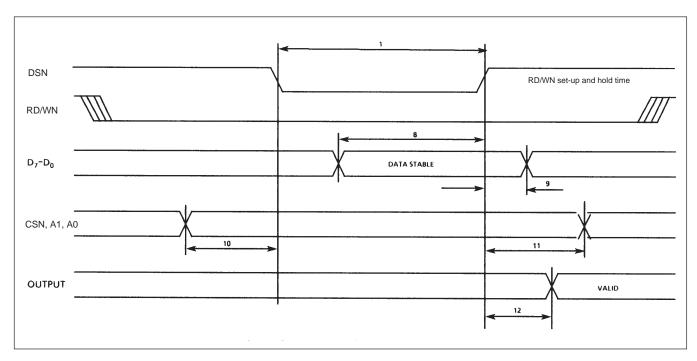

# Read/Write Select (RD/WN)

A high on RD/WN indicates a CPU read from the MA28155 and a low indicates a CPU data or control word write to the MA28155. The RD/WN line is active only when DSN is low.

# Data Strobe (DSN)

This input indicates that a data transfer is taking place. During a CPU write operation the MA28155 reads data from the bus on the rising edge of DSN. During a read operation the MA28155 outputs data to the bus while DSN is low. Data is valid on the rising edge of DSN.

#### Port Select O and Port Select 1 (AO and A1)

These input signals, in conjunction with the DSN and RD/WN inputs, control the selection of one of the three ports of the control word registers. They are normally connected to the least significant bits of the address bus.

#### **Basic Operation**

| A1 | Α0 | DSN | RD/WN | CSN | READ                           |

|----|----|-----|-------|-----|--------------------------------|

| 0  | 0  | 0   | 1     | 0   | PORT A $\rightarrow$ DATA BUS  |

| 0  | 1  | 0   | 1     | 0   | PORT B → DATA BUS              |

| 1  | 0  | 0   | 1     | 0   | PORT C → DATA BUS              |

|    |    |     |       |     | WRITE                          |

| 0  | 0  | 0   | 0     | 0   | DATA BUS → PORT A              |

| 0  | 1  | 0   | 0     | 0   | DATA BUS $\rightarrow$ PORT B  |

| 1  | 0  | 0   | 0     | 1   | $DATA\;BUS\toPORT\;C$          |

| 1  | 1  | 0   | 0     | 1   | DATA BUS $\rightarrow$ CONTROL |

|    |    |     |       |     | DISABLE                        |

| Х  | Х  | х   | х     | 1   | DATA BUS → TRI-STATE           |

| 1  | 1  | 0   | 1     | 0   | ILLEGAL CONDITION              |

| Х  | х  | 1   | х     | 0   | $DATA\;BUS\toTRI\text{-}STATE$ |

Table 1: Basic Operation

#### **OPERATIONAL DESCRIPTION**

#### **Mode Selection**

There are three basic modes of operation, which can be selected by the system software:

Mode 0. Basic Input/Output Mode 1. Strobed Input/Output

Mode 2 Bi-directional Bus

When the reset input goes high all ports will be set to the input mode (i.e. all 24 lines will be in the high impedance state) After the reset is removed the MA28155 can remain in the input mode with no additional initialisation required.

During the execution of the system program any of the other modes may be selected using a single output instruction. This allows a single MA28155 to service a variety of peripheral devices with a single software maintenance routine.

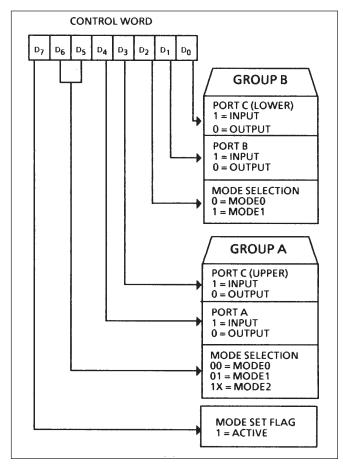

The modes for Port A and Port B can be separately defined, while Port C is divided into two portions as required by the Port A and Port B definitions. All of the output registers, including the status register, will be reset whenever the mode is changed.

Modes may be combined so that their functional definition can be tailored to almost any I/O structure. For instance; Group B can be programmed in Mode 0 whilst Group A could be simultaneously programmed in Mode 1.

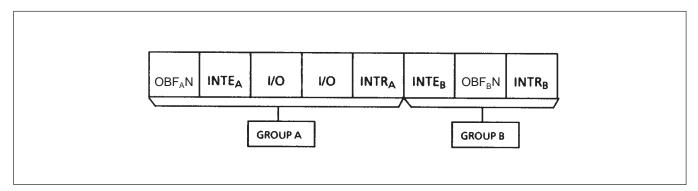

Figure 2: Basic Mode Definitions and Bus Interface

#### Mode Definition Format ( $D_7 = 1$ )

Figure 3: Mode Definition Format ( $D_7 = 1$ )

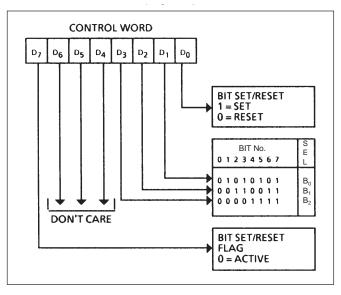

#### Single Bit Set/Reset Feature

Any of the eight bits of Port C can be Set or Reset using a single output instruction. This feature reduces software requirements in control-based applications.

When Port C is being used as Status/Control for Port A or B, these bits can be set or reset by using the Bit Set/Reset operation just as if they were data output ports.

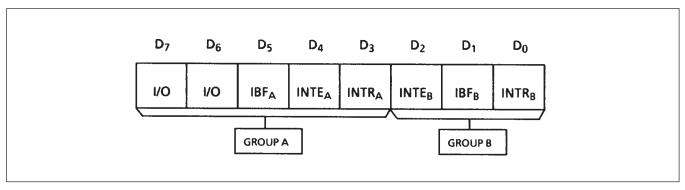

#### **Interrupt Control Functions**

When the MA28155 is programmed to operate in Mode 1 or 2, control signals are provided that can be used as interrupt request inputs to the CPU (figure 4). The interrupt request signals, generated from Port C, can be inhibited or enabled by setting or resetting the associated INTE register bit, using the Bit Set/Reset function of Port C.

This function allows the programmer to disallow or allow a specific I/O device to interrupt the CPU, without affecting any other device in the interrupt structure.

INTE register bit definitions:

(BIT-SET): INTE is SET -Interrupt enable

(BIT-RESET): INTE is RESET -Interrupt disable

Note: All mask register bits are automatically reset during mode selection and device reset.

# Bit Set/Reset Format ( $D_7 = 0$ )

Figure 4: Bit Set/Reset Format ( $D_7 = 0$ )

### **Group A and Group B Controls**

The functional configuration of each port is programmed by the system software. In essence, the CPU outputs a control word to the MA28155. The control word contains information such as mode, bit set, bit reset, etc., this initializes the functional configuration of the MA28155.

Each of the Control blocks (Group A and Group B) accept commands from the Read/Write Control Logic, receive control words from the internal data bus and issue the proper commands to its associated ports:

Control Group A - Port A and Port C upper (C7-C4) Control Group B - Port B and Port C lower (C3-C0)

The Control Word Register can only be written into. Therefore reading of the Control Word Register is not allowed . Ports A, B and C

The MA28155 contains three 8-bit ports (A, B, and C). All can be configured in a wide variety of functional characteristics by the system software but each has its own special features to further enhance the power and flexibility of the MA28155.

#### Port A.

One 8-bit data output latch/buffer and one 8-bit data input latch.

#### Port B.

One 8-bit data input/output latch/buffer and one 8-bit input buffer

# Port C.

One 8-bit data output latch/buffer and one 8-bit data input buffer (no latch for input) This port can be divided into two 4-bit ports under the mode control. Each 4-bit port contains a 4-bit latch and it can be used for the control signal outputs and status signal inputs in conjunction with ports A and B

# OPERATING MODE 0 (Basic Input/Output)

This functional configuration provides simple input and output operation for each of the three ports. No handshaking is required; data is simply written to or read from a specified port.

- Two 8-bit ports and 4-bit ports

- Any port can be input or output

- Outputs are latched

- Inputs are not latched.

- 16 different Input/Output configurations are possible in this Mode.

Figure 5: Basic Input (Read) Timing Diagram

Figure 6: Basic Input (Write) Timing Diagram

# **Port Definition Mode 0**

| D <sub>4</sub> | D <sub>3</sub> | D <sub>1</sub> | D <sub>0</sub> | PORT A<br>(UPPER) | PORT C | PORT B | PORT C<br>(LOWER) |

|----------------|----------------|----------------|----------------|-------------------|--------|--------|-------------------|

| 0              | 0              | 0              | 0              | OUTPUT            | OUTPUT | OUTPUT | OUTPUT            |

| 0              | 0              | 0              | 1              | OUTPUT            | OUTPUT | OUTPUT | INPUT             |

| 0              | 0              | 1              | 0              | OUTPUT            | OUTPUT | INPUT  | OUTPUT            |

| 0              | 0              | 1              | 1              | OUTPUT            | OUTPUT | INPUT  | INPUT             |

| 0              | 1              | 0              | 0              | OUTPUT            | INPUT  | OUTPUT | OUTPUT            |

| 0              | 1              | 0              | 1              | OUTPUT            | INPUT  | OUTPUT | INPUT             |

| 0              | 1              | 1              | 0              | OUTPUT            | INPUT  | INPUT  | OUTPUT            |

| 0              | 1              | 1              | 1              | OUTPUT            | INPUT  | INPUT  | INPUT             |

| 1              | 0              | 0              | 0              | INPUT             | OUTPUT | OUTPUT | OUTPUT            |

| 1              | 0              | 0              | 1              | INPUT             | OUTPUT | OUTPUT | INPUT             |

| 1              | 0              | 1              | 0              | INPUT             | OUTPUT | INPUT  | OUTPUT            |

| 1              | 0              | 1              | 1              | INPUT             | OUTPUT | INPUT  | INPUT             |

| 1              | 1              | 0              | 0              | INPUT             | INPUT  | OUTPUT | OUTPUT            |

| 1              | 1              | 0              | 1              | INPUT             | INPUT  | OUTPUT | INPUT             |

| 1              | 1              | 1              | 0              | INPUT             | INPUT  | INPUT  | OUTPUT            |

| 1              | 1              | 1              | 1              | INPUT             | INPUT  | INPUT  | INPUT             |

Table 2: Port Definition Mode 0 (See Also Figure 3)

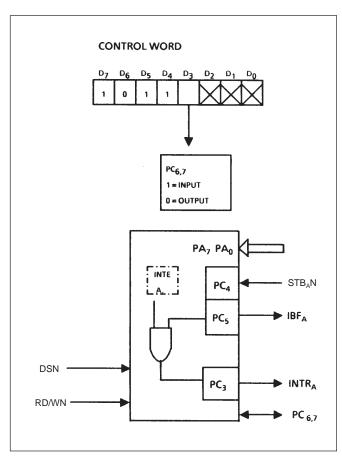

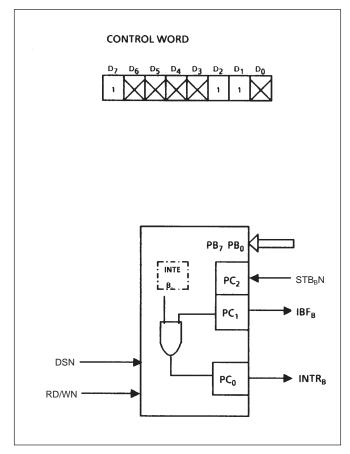

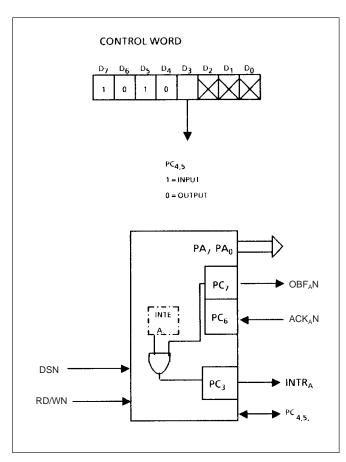

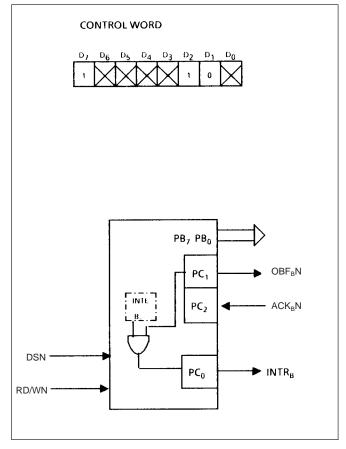

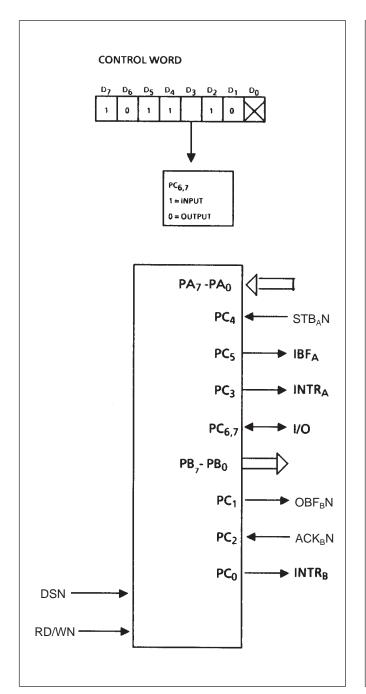

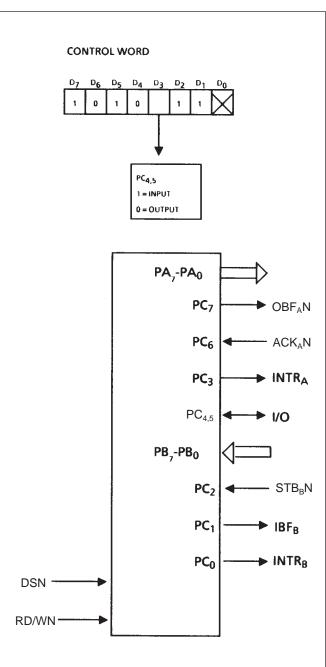

# OPERATING MODE 1 (Strobed Input/Output)

This functional configuration provides a means for transferring I/O data to or from a specified port in conjunction with strobes or handshaking signals. In mode 1, port A and port B use the lines on port C to generate or accept these handshaking signals

- Two Groups (Group A and Group B) .

- Each Group contains one 8-bit data port and one 4-bit control/data port,

- The 8-bit data port can be either input or output, Both inputs and outputs are latched,

- The 4-bit port is used for control and status of the 8-bit data port.

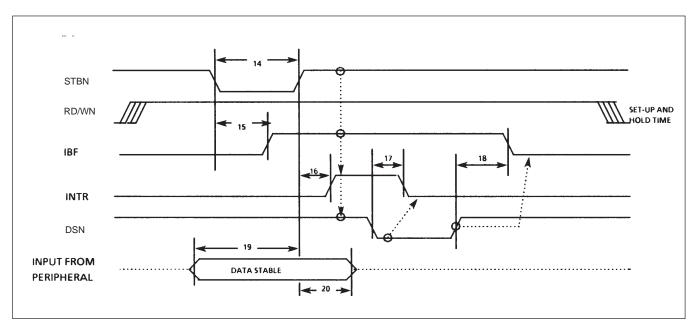

Figure 7: Strobed Input Timing Diagram

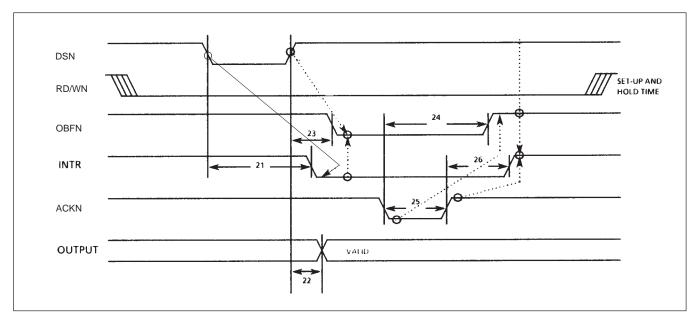

Figure 8: Strobed Output Timing Diagram

# **Input Control Signal Definition (Mode 1)**

# STBN (Strobe Input).

A low on this input loads data into the input latch.

# IBF (Input Buffer Full Register Bit).

A high on this output indicates that the data has been loaded into the input latch; in essence, an acknowledgement.

IBF is set by a STBN active pulse (which strobes data into the device), and is reset by the rising edge of DSN (which reads the latched data out of the device).

Figure 9: Strobed Input (PORT A)

# INTR (Interrupt Request).

A high on this output can be used to interrupt the CPU when an input device is requesting service, INTR is set by the STBN being high and IBF being high and INTE being enabled, It is reset by the falling edge of DSN, This procedure allows an input device to request service from the CPU by simply strobing its data into the port,

INTE A: Controlled by bit set/reset of PC<sub>4</sub>

INTE B: Controlled by bit set/reset of PC2

Figure 10: Strobed Input (PORT B)

# **Output Control Signal Definition (Mode 1)**

# **OBFN** (Output Buffer Full Register Bit).

The OBFN output will go low to indicate that the CPU has written data out to the specified port. The OBF register bit will be set by the rising edge of the DSN input and reset by ACKN input being low.

#### ACKN (Acknowledge Input).

A low on this input informs the 28155 that the data from port A or port B has been accepted; in essence, a response from the peripheral device indicating that it has received the data output by the CPU.

# INTR (Interrupt Request).

A high on this output can be used to interrupt the CPU when an output device has accepted data transmitted by the CPU. INTR is set when ACKN is high, OBFN is high and INTE is high. It is reset by the falling edge of DSN.

INTE A: Controlled by bit set/reset of PC<sub>6</sub> INTE B: Controlled by bit set/reset of PC<sub>2</sub>

Figure 11: Strobed Output (PORT A)

Figure 12: Strobed Output (PORT B)

#### **Combinations of Mode 1**

Port A and Port B can be individually defined as input or output in Mode 1 to support a wide variety of strobed I/O applications.

Figure 13: PORT A (STROBED INPUT) PORT B (STROBED OUTPUT)

Figure 14: PORT A (STROBED OUTPUT)

PORT B (STROBED INPUT)

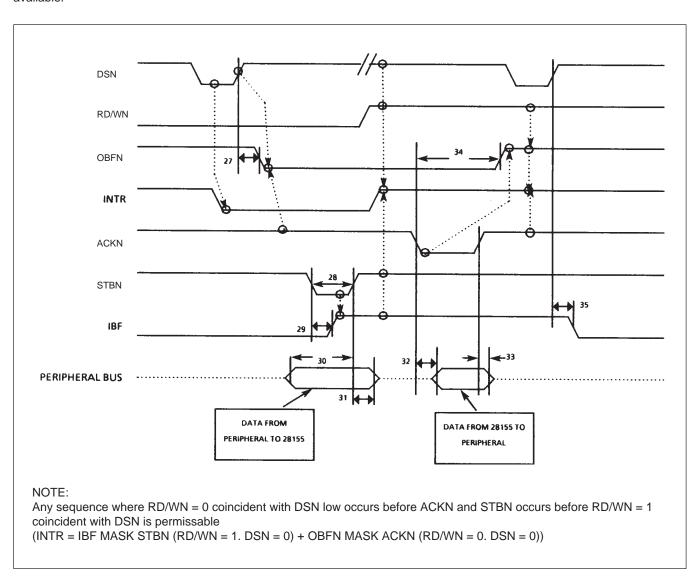

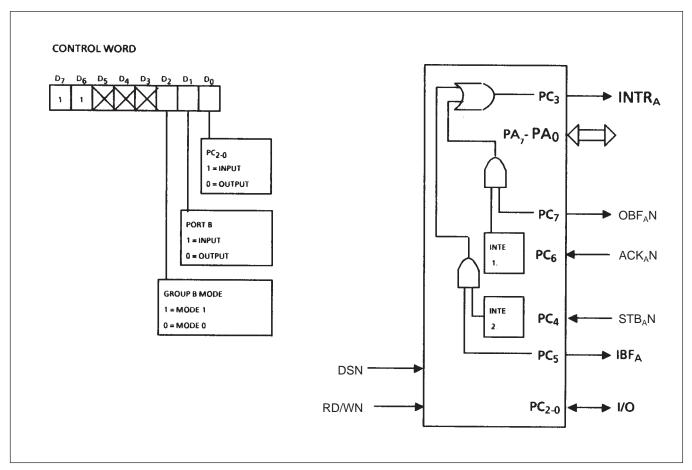

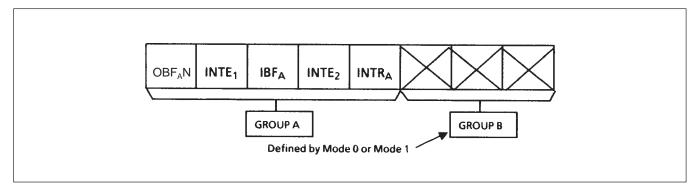

# OPERATING MODE 2 (Strobed Bidirectional Bus I/0)

This functional configuration provides a means for communicating with a peripheral device or structure on a single 8-bit bus for both transmitting and receiving data (bidirectional bus I/O) . Handshaking signals are provided to maintain proper bus flow discipline in a similar manner to Mode 1, Interrupt generation and enable/disable functions are also available.

- Used in group A only.

- One 8-bit bidirectional bus port (port A) and 5-bit control port (port C).

- Both inputs and outputs are latched,

- The 5-bit control port (port C) is used for control and status of the 8-bit bidirectional bus port (port A).

Figure 15: Bidirectional Timing Diagram

# BIDIRECTIONAL BUS L/O CONTROL Signal Definition (Mode 2)

# INTR (Interrupt Request):

A high on this output can be used to interrupt the CPU for both input or output operations.

# **Output Operations**

# OBFN (Output Buffer Full):

The OBF output will go low to indicate that the CPU has written data out to port A.

#### ACKN (Acknowledge):

A low on this input enables the tri-state output buffer of port A to send out the data. Otherwise, the output buffer will be in the high impedance state,

# INTE 1 (INTE register bit associated with OBFN):

Controlled by Bit Set/Reset of PC<sub>6</sub>.

# **Input Operations**

STBN (Strobe input):

A low on this input loads data in to the input latch,

# IBF (Input Buffer Full Register Bit):

A high on this output indicates data has been loaded in to the input latch,

INTE 2 (The INTE register bit associated with IBF). Controlled by Bit Set/Reset of PC<sub>4</sub>.

Figure 16: Mode 2 Bidirectional

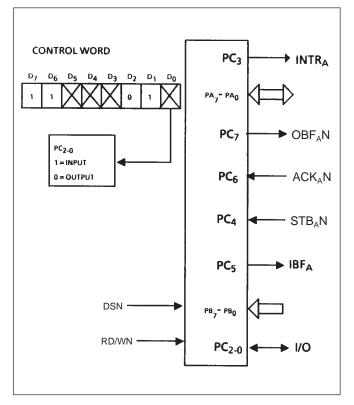

CONTROL WORD PC<sub>3</sub> → INTR<sub>A</sub> 0 PA7 - PA0 ▶ OBF<sub>A</sub>N PC<sub>7</sub> PC2-0 1 = INPUT ACK<sub>A</sub>N 0 = OUTPUT PC<sub>6</sub> PC<sub>4</sub> - STB<sub>A</sub>N ► IBF<sub>A</sub> PC<sub>5</sub> DSN · PB7- PB0 RD/WN PC<sub>2-0</sub> 1/0

Figure 17a: Mode 2 and Mode 0 (Input)

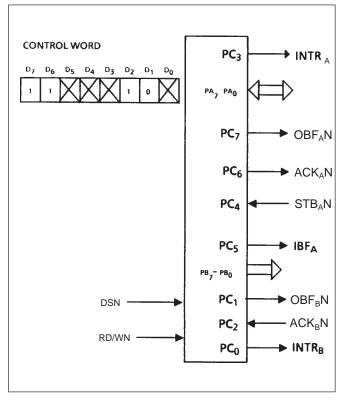

Figure 17b: Mode 2 and Mode 0 (Output)

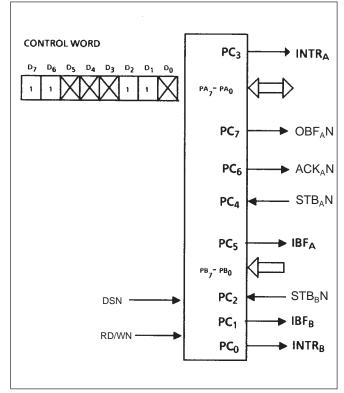

Figure 17c: Mode 2 and Mode 1 (Output)

Figure 17d: Mode 2 and Mode 1 (Input)

# **Mode Definition Summary**

|                 | MODE 0 |     | MOD                | DE 1               | MODE 2                   |

|-----------------|--------|-----|--------------------|--------------------|--------------------------|

|                 | IN     | OUT | IN                 | OUT                | _                        |

| $PA_0$          | IN     | OUT | IN                 | OUT                | $\Leftarrow \Rightarrow$ |

| PA <sub>1</sub> | IN     | OUT | IN                 | OUT                | ⇐⇒                       |

| PA <sub>2</sub> | IN     | OUT | IN                 | OUT                | ⇐⇒                       |

| PA <sub>3</sub> | IN     | OUT | IN                 | OUT                | ⇐⇒                       |

| PA <sub>4</sub> | IN     | OUT | IN                 | OUT                | ⇐⇒                       |

| PA <sub>5</sub> | IN     | OUT | IN                 | OUT                | ⇐⇒                       |

| PA <sub>6</sub> | IN     | OUT | IN                 | OUT                | ⇐⇒                       |

| PA <sub>7</sub> | IN     | OUT | IN                 | OUT                | $\Leftarrow \Rightarrow$ |

| PB <sub>0</sub> | IN     | OUT | IN                 | OUT                | PORT B MODE 0 or 1       |

| PB <sub>1</sub> | IN     | OUT | IN                 | OUT                | PORT B MODE 0 or 1       |

| PB <sub>2</sub> | IN     | OUT | IN                 | OUT                | PORT B MODE 0 or 1       |

| PB <sub>3</sub> | IN     | OUT | IN                 | OUT                | PORT B MODE 0 or 1       |

| PB <sub>4</sub> | IN     | OUT | IN                 | OUT                | PORT B MODE 0 or 1       |

| PB <sub>5</sub> | IN     | OUT | IN                 | OUT                | PORT B MODE 0 or 1       |

| PB <sub>6</sub> | IN     | OUT | IN                 | OUT                | PORT B MODE 0 or 1       |

| PB <sub>7</sub> | IN     | OUT | IN                 | OUT                | PORT B MODE 0 or 1       |

| PC <sub>0</sub> | IN     | OUT | INTR <sub>B</sub>  | INTR <sub>B</sub>  | I/O                      |

| PC <sub>1</sub> | IN     | OUT | IBF <sub>B</sub>   | OBF <sub>B</sub> N | I/O                      |

| PC <sub>2</sub> | IN     | OUT | STB <sub>B</sub> N | ACK <sub>B</sub> N | I/O                      |

| PC <sub>3</sub> | IN     | OUT | INTR <sub>A</sub>  | INTR <sub>A</sub>  | INTR <sub>A</sub>        |

| PC <sub>4</sub> | IN     | OUT | STB <sub>A</sub> N | I/O                | STB <sub>A</sub> N       |

| PC <sub>5</sub> | IN     | OUT | IBF <sub>A</sub>   | I/O                | IBF <sub>A</sub>         |

| PC <sub>6</sub> | IN     | OUT | I/O                | ACK <sub>A</sub> N | ACK <sub>A</sub> N       |

| PC <sub>7</sub> | IN     | OUT | I/O                | OBF <sub>A</sub> N | OBF <sub>A</sub> N       |

Table 3: Mode Definition Summary

### **Special Mode Combination Considerations.**

There are several combinations of modes when not all of the bits in port C are used for control or status. The remaining bits can be used as follows:

If programmmed as inputs-

All input lines can be accessed during normal port C read.

If programmed as outputs

Bits in C upper (PC7-PC4) must be individually accessed using a bit set/reset function.

Bits in C lower (PC3-PC0) can be accessed using the bit set/reset function or bits PC2-PC0 may also be accessed as a trio by writing into port C.

#### Reading Port C Status.

In Mode 0 Port C transfers data from or to the peripheral device, When the MA28155 is programmed to function in Modes 1 or 2 Port C generates or accepts handshaking signals with the peripheral device, Reading the contents of Port C allows the programmer to test or verify the status of each peripheral device and change the program flow accordingly.

There is no special instruction to read the Status Information from Port C. A normal read operation of Port C is executed to perform this function.

Figure 18a: Mode 1 Input Configuration

Figure 18b: Mode 1 Output Configuration

Figure 18c: Mode 2

# **DEFINITION OF SUBGROUPS**

| Subgroup | Definition                                               |  |  |  |  |  |

|----------|----------------------------------------------------------|--|--|--|--|--|

| 1        | Static characteristics specified in Table 5 at +25°C     |  |  |  |  |  |

| 2        | Static characteristics specified in Table 5 at +125°C    |  |  |  |  |  |

| 3        | Static characteristics specified in Table 5 at -55°C     |  |  |  |  |  |

| 7        | Functional characteristics specified at +25°C            |  |  |  |  |  |

| 8A       | Functional characteristics specified at +125°C           |  |  |  |  |  |

| 8B       | Functional characteristics specified at -55°C            |  |  |  |  |  |

| 9        | Switching characteristics specified in Table 6 at +25°C  |  |  |  |  |  |

| 10       | Switching characteristics specified in Table 6 at +125°C |  |  |  |  |  |

| 11       | Switching characteristics specified in Table 6 at -55°C  |  |  |  |  |  |

# DC CHARACTERISTICS AND RATINGS

| Parameter               | Min  | Max                  | Units |

|-------------------------|------|----------------------|-------|

| Supply Voltage          | -0.5 | 7                    | V     |

| Input Voltage           | -0.3 | V <sub>DD</sub> +0.3 | V     |

| Current Through Any Pin | -20  | +20                  | mA    |

| Operating Temperature   | -55  | 125                  | °C    |

| Storage Temperature     | -65  | 150                  | °C    |

damage to the device. This is a stress rating only and functional operation of the device at these conditions, or at any other condition above those indicated in the operations section of this specification, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Stresses above those listed may cause permanent

Table 4: Absolute Maximum Ratings

|                 |                                   |                                                    | 1   | ose radia<br>ng 3x10⁵ |     |       |

|-----------------|-----------------------------------|----------------------------------------------------|-----|-----------------------|-----|-------|

| Symbol          | Parameter                         | Conditions                                         | Min | Тур                   | Max | Units |

| $V_{DD}$        | Supply Voltage                    | -                                                  | 4.5 | 5.0                   | 5.5 | V     |

| $V_{IH}$        | Input High Voltage                | -                                                  | 2.2 | -                     | -   | V     |

| $V_{IL}$        | Input Low Voltage                 | -                                                  | -   | -                     | 0.8 | V     |

| $V_{OH}$        | Output High Voltage               | $I_{OH} = -6mA$                                    | 3.5 | -                     | -   | V     |

| $V_{OL}$        | Output Low Voltage                | $I_{OL} = 12mA$                                    | -   | -                     | 0.5 | V     |

| I <sub>IN</sub> | Input Leakage Current (Note 1)    | $V_{DD} = 5.5V$ ,<br>$V_{IN} = V_{SS}$ or $V_{DD}$ | -   | -                     | ±10 | μΑ    |

| I <sub>OZ</sub> | Tristate Leakage Current (Note 1) | $V_{DD} = 5.5V$ ,<br>$V_{IN} = V_{SS}$ or $V_{DD}$ | -   | -                     | ±50 | μΑ    |

| $I_{DD}$        | Power Supply Current              | Static,                                            | -   | 0.1                   | 10  | mA    |

Note 1: Guaranteed but not tested at -55°C Mil-Std-883, method 5005, subgroups 1, 2, 3.

$V_{DD} = 5V\pm10\%$ , over full operating temperature range.

Table 5: Electrical Characteristics

# **AC ELECTRICAL CHARACTERISTICS**

|    | Parameter                      | Min. | Max. | Units |    | Parameter                         | Min. | Max        | Units |

|----|--------------------------------|------|------|-------|----|-----------------------------------|------|------------|-------|

|    |                                |      |      |       | 18 | DSN Î to IBF Î                    | -    | 65         | ns    |

|    |                                |      |      |       | 19 | Peripheral Data set up to STBN ↑  | 0    |            | ns    |

| 1  | DSN width                      | 65   | -    | ns    | 20 | Peripheral Data hold after STBN Î | 100  |            | ns    |

| 2  | Peripheral Data set up to DSN  | 0    | -    | ns    | 21 | DSN                               | -    | DS+<br>100 | ns    |

| 3  | Peripheral Data hold after DSN | 10   | -    | ns    | 22 | Output valid from DSN ↑           | -    | 100        | ns    |

| 4  | CSN, A1, A0 setup to DSN ↓     | 0    | -    | ns    | 23 | DSN îto OBFN ↓                    | -    | 105        | ns    |

| 5  | CSN, A1, A0 hold after DSN ↑   | 0    | -    | ns    | 24 | ACKN ↑ to OBFN ↓                  | -    | 50         | ns    |

| 6  | Data valid from DSN ↓          | -    | 60   | ns    | 25 | ACKN pulse width                  | 100  | -          | ns    |

| 7  | Data float from DSN ↑ (note 5) | 10   | 100  | ns    | 26 | ACKN Î INTR Î                     | -    | 80         | ns    |

| 8  | Data set up to DSN ↓           | 20   | -    | ns    | 27 | DSN Î to OBFN ↓                   | -    | 105        | ns    |

| 9  | Data hold after DSN ↑          | 30   | -    | ns    | 28 | STBN pulse width                  | 100  | -          | ns    |

| 10 | CSN, A1, A0 setup to DSN ↓     | 0    | -    | ns    | 29 | STBN ∜ to IBF ↑                   | -    | 65         | ns    |

| 11 | CSN, A1, A0 hold after DSN ↑   | 20   | -    | ns    | 30 | Peripheral Data set up to STBN ↑  | 0    | -          | ns    |

| 12 | Output valid from DSN ↑        | -    | 100  | ns    | 31 | Perlpheral Data hold after STBN 1 | 100  | -          | ns    |

| 14 | STBN pulse width               | 100  | -    | ns    | 32 | Output valid from ACKN ↓          | -    | 45         | ns    |

| 15 | STBN ∜ to IBF ↑                | -    | 65   | ns    | 33 | Output float from ACKN ↑ (Note 5) | 10   | 100        | ns    |

| 16 | STBN î to INTR î               | -    | 65   | ns    | 34 | ACKN ∜ to OBFN ↑                  | -    | 50         | ns    |

| 17 | DSN ∜, to INTR ∜               | -    | 65   | ns    | 35 | DSN ↑ to IBF ↓                    | -    | 65         | ns    |

- Mil-Std-883, method 5005, subgroup 9, 10, 11. 1.  $V_{DD} = 5V\pm10\%$  and  $C_{CL} = 50pF$ , over full operating temperature range. 2. Input Pulse  $V_{SS}$  to 3.0 Volts.

- 3. Times Measurement Reference Level 1.5 Volts.

- 4. DSN = Data Strobe Pulse Width.

- 5. Measured by a 1.0 Volt change in output voltage. Outputs tied to  $V_{SS}$  via  $680\Omega$ .

Table 6: AC Electrical Characteristics

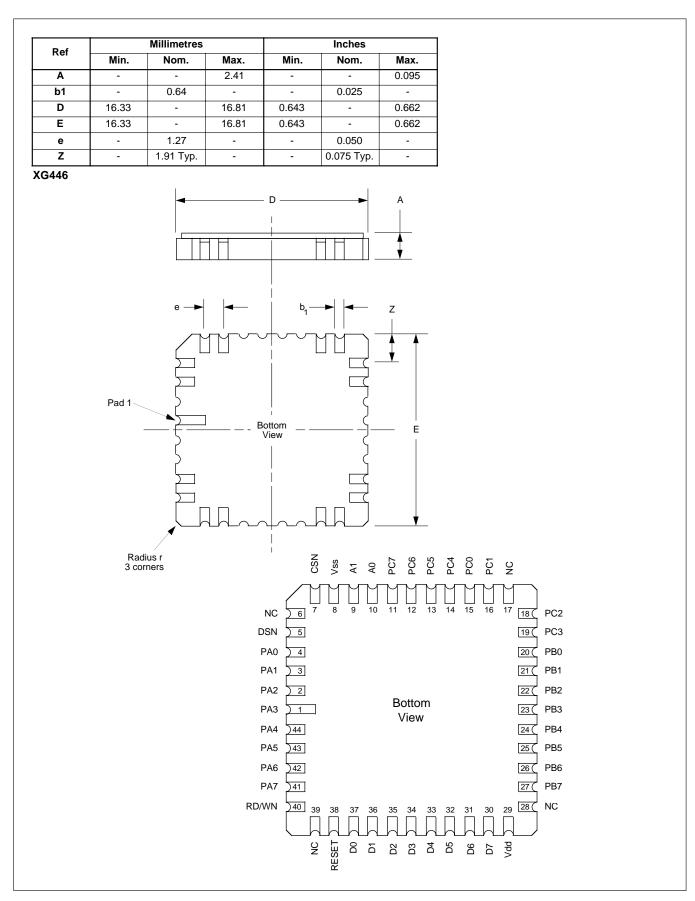

# **PACKAGE OUTLINES & PIN ASSIGNMENTS**

| Ref         |      |             |       |                |            |                |               |                    |          |

|-------------|------|-------------|-------|----------------|------------|----------------|---------------|--------------------|----------|

|             |      | Millimetres |       |                | Inches     |                |               |                    |          |

|             | Min. | Nom.        | Max.  | Min.           | Nom.       | Max.           |               |                    |          |

| Α           | -    | -           | 5.715 | -              | -          | 0.225          | PA3 1         | 0                  | 40 PA4   |

| A1          | 0.38 | -           | 1.53  | 0.015          | -          | 0.060          | PA2 2         |                    | 39 PA5   |

| b           | 0.35 | -           | 0.59  | 0.014          | -          | 0.023          | PA1 3         |                    | 38 PA6   |

| С           | 0.20 | -           | 0.36  | 0.008          | -          | 0.014          | PA0 4         |                    | 37 PA7   |

| D           | -    | -           | 51.31 | -              | -          | 2.020          | DSN 5         |                    | 36 RD/WN |

| е           | -    | 2.54 Typ.   | -     | -              | 0.100 Typ. | -              | CSN 6         |                    | 35 RESET |

| e1          | -    | 15.24 Typ.  | -     | -              | 0.600 Typ. | -              |               |                    |          |

| Н           | 4.71 | -           | 5.38  | 0.185          | -          | 0.212          | Vss 7         |                    | 34 D0    |

| Me          | -    | -           | 15.90 | -              | -          | 0.626          | A1 8          |                    | 33 D1    |

| Z           | -    | -           | 1.27  | _              | -          | 0.050          | A0 9          | Ton                | 32 D2    |

| W           | -    | -           | 1.53  | -              | -          | 0.060          | PC7 10        | Top<br>View        | 31 D3    |

| (G405       |      | -           | 1.55  |                |            | 0.000          | PC6 11        |                    | 30 D4    |

|             | 21   |             |       | <i>y</i><br>w− | 40         |                | PB2 <u>20</u> |                    | 21 PB3   |

| <del></del> |      |             |       |                | Sea        | ating Plane    | <b>_</b>      | — M <sub>E</sub> — | <b></b>  |

| ↑<br>A<br>↓ |      |             |       |                |            | A <sub>1</sub> |               |                    |          |

Figure 19: 40-Lead Ceramic DIL (Solder Seal) - Package Style C

Figure 20: 44-Pad Leadless Chip Carrier (Package Style L)

#### RADIATION TOLERANCE

#### **Total Dose Radiation Testing**

For product procured to guaranteed total dose radiation levels, each wafer lot will be approved when all sample devices from each lot pass the total dose radiation test.

The sample devices will be subjected to the total dose radiation level (Cobalt-60 Source), defined by the ordering code, and must continue to meet the electrical parameters specified in the data sheet. Electrical tests, pre and post irradiation, will be read and recorded.

Dynex Semiconductor can provide radiation testing compliant with Mil-Std-883 test method 1019, Ionizing Radiation (Total Dose).

| Total Dose (Function to specification)*      | 3x10 <sup>5</sup> Rad(Si)             |

|----------------------------------------------|---------------------------------------|

| Transient Upset (Stored data loss)           | 5x10 <sup>10</sup> Rad(Si)/sec        |

| Transient Upset (Survivability)              | >1x10 <sup>12</sup> Rad(Si)/sec       |

| Neutron Hardness (Function to specification) | >1x10 <sup>15</sup> n/cm <sup>2</sup> |

| Single Event Upset**                         | <1x10 <sup>-10</sup> Errors/bit day   |

| Latch Up                                     | Not possible                          |

<sup>\*</sup> Other total dose radiation levels available on request

Figure 21: Radiation Hardness Parameters

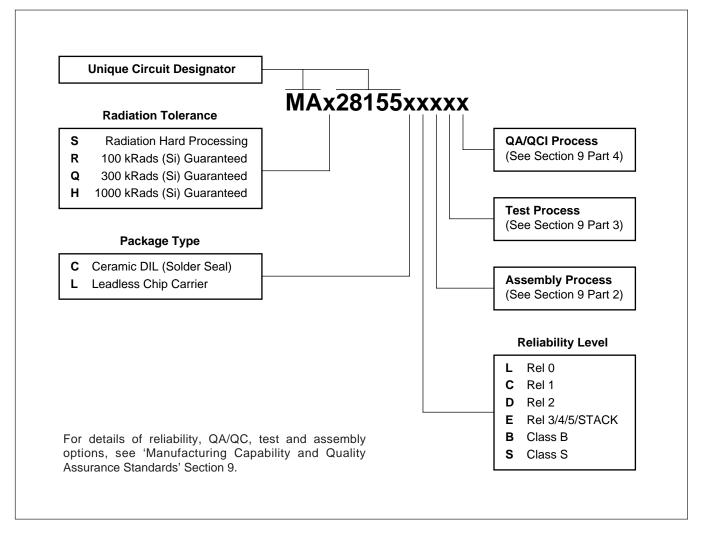

#### ORDERING INFORMATION

<sup>\*\*</sup> Worst case galactic cosmic ray upset - interplanetary/high altitude orbit

#### http://www.dynexsemi.com

e-mail: power\_solutions@dynexsemi.com

HEADQUARTERS OPERATIONS

DYNEX SEMICONDUCTOR LTD

Doddington Road, Lincoln. Lincolnshire. LN6 3LF. United Kingdom. Tel: 00-44-(0)1522-500500 Fax: 00-44-(0)1522-500550

DYNEX POWER INC.

Unit 7 - 58 Antares Drive, Nepean, Ontario, Canada K2E 7W6.

Tel: 613.723.7035 Fax: 613.723.1518

Toll Free: 1.888.33.DYNEX (39639)

CUSTOMER SERVICE CENTRES

France, Benelux, Italy and Spain Tel: +33 (0)1 69 18 90 00. Fax: +33 (0)1 64 46 54 50

North America Tel: 011-800-5554-5554. Fax: 011-800-5444-5444

UK, Germany, Scandinavia & Rest Of World Tel: +44 (0)1522 500500. Fax: +44 (0)1522 500020

SALES OFFICES

France, Benelux, Italy and Spain Tel: +33 (0)1 69 18 90 00. Fax: +33 (0)1 64 46 54 50

Germany Tel: 07351 827723

North America Tel: (613) 723-7035. Fax: (613) 723-1518. Toll Free: 1.888.33.DYNEX (39639) /

Tel: (831) 440-1988. Fax: (831) 440-1989 / Tel: (949) 733-3005. Fax: (949) 733-2986.

**UK, Germany, Scandinavia & Rest Of World** Tel: +44 (0)1522 500500. Fax: +44 (0)1522 500020 These offices are supported by Representatives and Distributors in many countries world-wide.

© Dynex Semiconductor 2000 Publication No. DS3575-5 Issue No. 5.0 January 2000 TECHNICAL DOCUMENTATION – NOT FOR RESALE. PRINTED IN UNITED KINGDOM

#### Datasheet Annotations:

Dynex Semiconductor annotate datasheets in the top right hard corner of the front page, to indicate product status. The annotations are as follows:-

Target Information: This is the most tentative form of information and represents a very preliminary specification. No actual design work on the product has been started.

Preliminary Information: The product is in design and development. The datasheet represents the product as it is understood but details may change.

Advance Information: The product design is complete and final characterisation for volume production is well in hand.

No Annotation: The product parameters are fixed and the product is available to datasheet specification.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior notice the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

All brand names and product names used in this publication are trademarks, registered trademarks or trade names of their respective owners