# **Packet Telecommand Decoder**

Replaces June 2000 version, DS3839-6.1

DS3839-7.0 September 2001

The MA28140 Packet Telecommand Decoder (PTD) is a single-chip implementation of the core part of a telecommand decoder, manufactured using CMOS-SOS high performance, radiation hard, 1.5 $\mu$ m technology. The PTD is a full implementation of and fully compliant with the packet telecommand standard ESA PSS-04-107 and the telecommand decoder specification ESA PSS-04-151, these being derived from the corresponding CCSDS standards.

The PTD, which handles 6 NRZ TC input channels, processes the following layers:

Coding Layer

Transfer Layer

Segmentation Layer

**Authentication Layer**

Command Pulse Distribution

Some of these layers have a telemetry reporting mechanism. The processed TC segment can be transferred to the application either serially or in parallel.

## **FEATURES**

- Single Chip Implementation of all TC Decoder Core Functions

- Built-in Authentication Unit

- Built-in Command Pulse Distribution Unit Core Logic

- Radiation Hard to 1MRads (Si)

- High SEU Immunity, Latch-up Free

- CMOS-SOS Technology

- Conforms to CCSDS Standards

- 6 NRZ TC Input Channels

- 50Kbps Bit Rate

- Low Power Consumption

- Single 5V Supply

- -55 to +125°C Operation

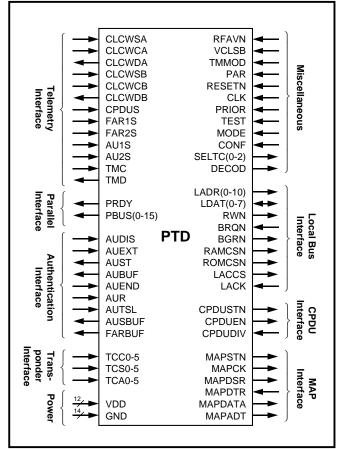

Pin connections

#### **CONTENTS**

|                                           | Page |

|-------------------------------------------|------|

| Front sheet                               | 1    |

| 1. Introduction                           | 2    |

| 2. TC Decoder Subsystem Overview          | 3    |

| 3. PTD Architectural Overview             | 4    |

| 4. PTD Functional Description             |      |

| 4.1 Coding Layer                          | 6    |

| 4.2 Transfer Layer                        | 9    |

| 4.3 Authentication Layer                  | 15   |

| 4.4 Segmentation Layer                    | 21   |

| 4.5 CPDU                                  | 22   |

| 4.6 Telemetry Reporting                   | 24   |

| 5. PTD Interfaces                         |      |

| 5.1 Physical Channel Interface            | 27   |

| 5.2 MAP Interface                         | 27   |

| 5.3 Telemetry Interface                   | 30   |

| 5.4 Parallel Interface                    | 34   |

| 5.5 CPDU Interface                        | 35   |

| 5.6 Local Bus Interface                   | 36   |

| 5.7 Memories                              | 36   |

| 5.8 External Authentication               | 41   |

| 6. State After Reset                      | 42   |

| 7. Signal Description                     | 44   |

| 8. Electrical Characteristics and Ratings |      |

| 8.1 DC Parameters                         | 47   |

| 8.2 AC Parameters                         | 48   |

| 9. Package Details                        |      |

| 9.1 Dimensions                            | 65   |

| 9.2 Pin Assignment                        | 66   |

| 10. Radiation Tolerance                   | 70   |

| 11. Ordering Information                  | 70   |

| 12 Synonyms                               | 71   |

#### **REFERENCES**

- 1. "Packet Telecommand Standard" ESA PSS-04-107, Issue 2, April 92.

- 2. "Telecommand Decoder Specification" ESA PSS-04-151, Issue 1, September 93.

## 1. INTRODUCTION

This document is the data sheet of the "Packet Telecommand Decoder", henceforth called the PTD.

The PTD is compatible with the ESA PSS-04-107 standard directly derived from the CCSDS recommendations. This standard is described in references 1 and 2. The data sheet is based on both documents for the description of the protocol. Nevertheless, it was impossible to include the whole reference documents in the data sheet, thus some specific points of the protocol or some descriptions of the recommended hardware implementation have not been included. The reader may find these points in the applicable documents.

## **CONVENTION**

In this document the two conventions described in references 1 and 2 apply:

1. The first bit in the field to be transmitted (i.e. the most left justified bit when drawing a figure) is defined to be Bit 0. When the field is used to express a binary value, the Most Significant Bit (MSB) shall be the first transmitted bit of the field (i.e. Bit 0).

| Bit 0                         | Bit N-1 |

|-------------------------------|---------|

| N Bit Data Field              |         |

| MSB                           | LSB     |

| ← First Bit transmitted = MSB |         |

Note: Some of the external interfaces have parallel busses (LADR, LDAT, PBUS, SELTC) which have the opposite bit order specified, i.e. Bit 0 is The Least Significant Bit.

2. An 8-bit word (a byte) is called an OCTET.

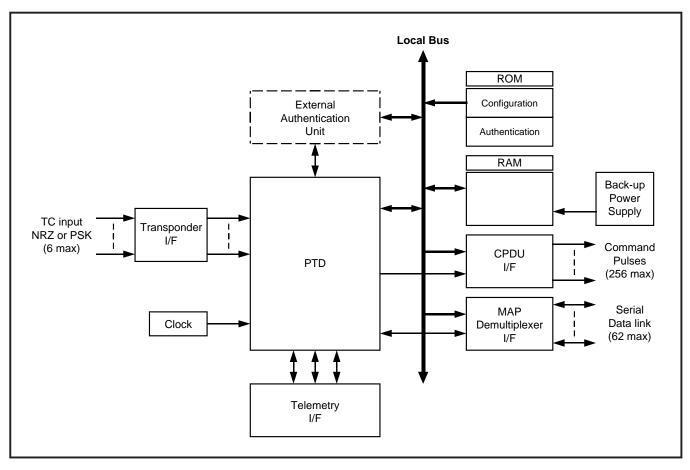

Figure 1: Block Diagram of a TC Decoder Subsystem

## 2. TC DECODER SUBSYSTEM OVERVIEW

An ESA/CCSDS Telecommand Decoder subsystem including the PTD and fulfilling the receiving-end functions established in the Packet Telecommand Standard (ref 1) is shown in Figure 1.

The PTD requires the following additional hardware to fulfil the requirements of the Telecommand Decoder Specification (ref 2):

- Transponder I/F including demodulators for PSK TC inputs.

- Telemetry I/F. The telemetry reporting signals can be directly connected to a Virtual Channel Multiplexer (ref 3).

- Command Pulse Distribution Unit I/F. This function performs decoding of commands present on the local bus and power amplification. The PTD ASIC associated with the CPDU I/F can manage 256 pulse outputs.

- MAP demultiplexer I/F. This interface is composed of a demultiplexer to provide the TC segment data to various Data Management System interfaces. The demultiplexer is controlled by the MAP data present on the Local Bus. The PTD ASIC can manage 62 different serial data interfaces (63 if AU is disabled).

- Memories. There are 2 different memories:

- RAM (2Kx8) used to store the received TC data and protocol variables (programme authentication key for instance) and eventually to store the TC segment available for further processing by the Data Management System. If this memory is used to store the recovery LAC counter (Authentication function), it must be a non-volatile memory.

- ROM (1Kx8) divided in two parts:

- Configuration part, used to provide the Mission Specific Data.

- Authentication part, used to provide the fixed Authentication key.

- External Authentication Unit (optional). Although an AU is implemented in the PTD, it is also possible to use an external AU if the mission requires a different authentication algorithm. This external unit accesses the RAM in order to authenticate a TC segment.

## 3. PTD ARCHITECTURAL OVERVIEW

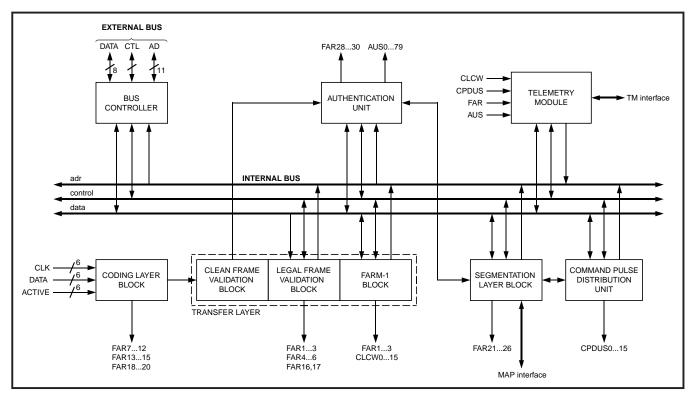

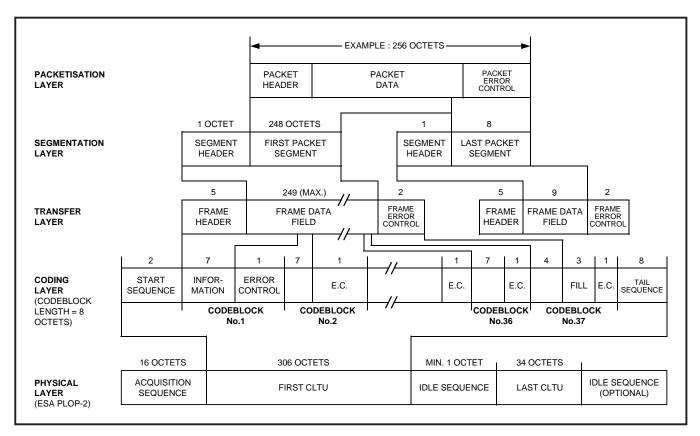

Figure 2 describes the PTD functional architecture which features 7 major blocks described below. Figure 3 shows the CCSDS protocol layer architecture. The PTD deals with the Coding Layer, the Transfer Layer, the Authentication Layer, the Segmentation Layer and a part of the Packetisation Layer of the CCSDS protocol.

## **CODING LAYER BLOCK**

The coding layer block multiplexes the 6 physical TC channel inputs and fulfils the coding layer function described in section 5 of ref.1.

The main tasks performed by the PTD at this level are:

- Start sequence detection and selection of the first active TC input.

- Codeblock error detection and correction.

- Valid codeblock transfer to the above layer.

- Generation of part of the FAR and CLCW status.

## TRANSFER LAYER BLOCK

This level is concerned with the processing of the frames received from the coding layer and fulfils the transfer layer function described in section 6 of ref.1.

At this level, the PTD performs the following tasks:

- · Clean frame validation.

- Legal frame validation.

- Frame analysis report mechanism.

- Reporting word (16 bit CLCW and part of 32 bit FAR) generation.

#### **AUTHENTICATION UNIT BLOCK**

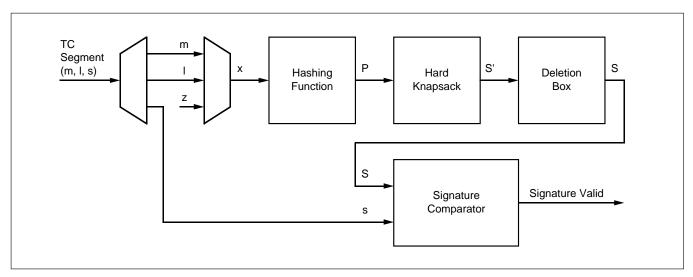

This block (which is optional and can be disabled permanently or during flight) is concerned with the segment data protection, it enables the spacecraft to authenticate the received data. The authentication concept is the "plain text with appended signature" approach, described in Section 8 of ref. 2.

In the PTD architecture this function is implemented on chip. However, a specific interface allows authentication to be performed externally - if another coding algorithm is to be used, the on-chip block can be disabled and an external authentication system can be used.

The block generates a reporting word (Authentication Status = 80 bits) and part of the 32 bit FAR.

## **SEGMENTATION LAYER BLOCK**

This block implements only some of the segmentation layer functions described in section 7 of ref.1. Its purpose is to manage the back-end buffer shared with the FARM-1 block of the transfer layer and to implement the MAP interface in order to demultiplex (with external hardware) the segments dedicated to the different spacecraft applications.

Figure 2: PTD Internal Architecture

Figure 3: CCSDS Protocol Layer Architecture

## **COMMAND PULSE DISTRIBUTION UNIT**

The CPDU is integrated into the PTD ensuring higher reliability for this critical function (direct telecommand for spacecraft reconfiguration) than if implemented in an external chip. The critical commands executed by the CPDU are received in specific packets. The CPDU responds to the MAP identifier 0, and to a mission dependent application process identifier (stored in ROM). No segmentation is accepted, the commands must be contained in an unsegmented package. The unit generates a reporting word (CPDU Status = 16 bits).

## **BUS CONTROLLER**

This block is the interface between external memories and on chip modules. Its different functions are:

- · address decoding.

- internal and external bus access arbitration.

## **TELEMETRY MODULE**

This block is the interface with the telemetry subsystem. It manages the data report storage using double buffered registers.

#### 4. PTD FUNCTIONAL DESCRIPTION

#### **4.1 CODING LAYER**

#### Overview of the Layer

The coding layer provides the forward error correction capability and synchronisation services used by the Transfer layer. Each Transfer Frame is encoded/embedded in one CLTU (Command Link Transmission Unit), which is the protocol-data unit of the coding layer. At the receiving end of the Coding Layer, a "dirty" symbol stream (plus control information on whether the physical channel is active or inactive) is received from the layer below. Searching for the Start Sequence, the coding layer finds the beginning of a CLTU and decodes the TC Codeblocks. As long as no errors are detected, or errors are detected and corrected, the coding layer passes "clean" octets of data to the Transfer layer. Should any codeblock contain an uncorrectable error, this Codeblock is abandoned and considered as Tail Sequence, no further data is passed to the layer above and the Coding Layer returns to a Start Sequence searching mode until it detects one. The coding layer also generates part of the CLCW and FAR status.

The PTD can handle up to 6 TC input interfaces, the data bit rate on these inputs should not exceed 50 Kbits per second when using the Authentication Unit. If the Authenication unit is not used the symbol rate could exceed 200kBits/sec (not guaranteed).

## Standard Data Structures Within the Layer

A CLTU is made up of three distinct protocol data elements:

- one 16-bit Start Sequence,

- one or more TC Codeblocks of a fixed length of 8 octets to encode the protocol data unit from the layer above,

- one Tail Sequence of length equal to that of the TC Codeblock, i.e. 8 octets.

| Start    | First     | •••••         | Last      | Tail     |

|----------|-----------|---------------|-----------|----------|

| Sequence | Codeblock |               | Codeblock | Sequence |

| 16 Bits  | Variabl   | e Number of C | odeblocks | 8 Octets |

The Start Sequence marks the beginning of the TC Codeblock field within a CLTU. It consists of a 16-bit synchronisation pattern represented in hexadecimal as EB90, where the first transmitted octet is EB.

The TC Codeblock field consists of one or more TC Codeblocks. The codeblock length of received data is fixed and set to 8 octets (information field: 7 octets).

|                   | P0 (MSB)                             | P6    | P7 (LSB)   |

|-------------------|--------------------------------------|-------|------------|

| Information Field | Error Control Field<br>7 parity bits |       | Filler Bit |

| 7 Octets          | 1                                    | Octet |            |

The Tail Sequence marks the end of the TC Codeblock Field within a CLTU. The length of the Tail Sequence is that of a TC Codeblock. Reference 1 specifies that its pattern should be alternating "zeros" and "ones", ending with a "one" (55 .... 55 in hexadecimal), but any double error codeblock, or single error codeblock with filler bit equal to 1 will be interpreted as Tail Sequence by the PTD.

## Synchronization and TC Input Selection

Synchronization is performed by searching for the Start Sequence simultaneously on all active TC inputs. The Start Sequence detection allows one bit error anywhere in the 16-bit pattern. Furthermore due to NRZ coding ambiguity on the incoming bit stream, it is possible to detect the inverted Start Sequence pattern in order to choose between positive or negative representation for further NRZ data processing. If an inverted Start Sequence is detected, the following bit stream is inverted until the Tail Sequence is encountered.

Two different modes to perform the TC channel selection are supported, selectable with the PRIOR configuration input:

Standard Mode (PRIOR = 0), in which all TC inputs TC0 to TC5 have the same priority, and the search for a Start Sequence is performed on all active TC channels simultaneously.

Priority Mode (PRIOR = 1), in which two inputs are assigned an absolute priority.

**Note:** This mode is not compliant with Ref. 1, and is intended for applications with specific requirements on unconditional access to the TC decoder. If this mode is used, a thorough analysis of potential failure modes and the built-in timeout mechanisms is recommended.

## **Standard Mode**

The TC input selection locks the selection multiplexer on the first TC channel where the Start Sequence is found. The selection mechanism is restarted once a Tail Sequence or a codeblock rejection has been detected. Furthermore, as a protection mechanism in case of RF receiver breakdown, a timeout mechanism is provided; if the TC channel clock is not detected during a certain time, the TC selection mechanism is reactivated in order not to remain lacked on a Channel without a clock signal.

The timeout value between two successive edges of the TC channel clock is: 3932160

tCK < TC clock timeout < 4587520 tCK, with tCK being the system clock period. With a

system clock frequency fCK of 4MHz this equals 0.98s <TC clock timeout < 1.15s.

## **Priority Mode**

In this mode two inputs have priority, according to the following rule: TC0 > TC1 > TC2 = TC3 = TC4 = TC5. When neither the TC0 input nor the TC1 input is active, the selection between the inputs TC2 to TC5 is performed as in the Standard Mode.

As soon as the TC active signal of TC0 is asserted, this TC input is selected, and the 5 other channels are inhibited. In case another input was already selected and receiving data, it is abandoned. The TC0 input remains selected until one of the following events:

- a1: its TC active signal becomes inactive, or

- b1: its bit clock has not been received for a period equal to the TC clock timeout, or

- c1: no Start Sequence has been detected for a period equal to the TC active timeout, or

- d1: a Tail Sequence or a codeblock rejection has occurred.

Upon events (a1) and (d1), the selection logic returns to the search state. Upon events (b1) and (c1), the TC0 input is ignored (i.e. considered inactive) until the event (a1) occurs.

When the TC0 input is inactive (including the case of a timeout as described above), as soon as the TC active signal of TC1 is asserted, this TC input is selected, and the lower priority inputs TC2 to TC5 are inhibited. In case any of these inputs was already selected and receiving data, it is abandoned. The TCI input remains selected until one of the following events.

- a2: its TC active signal, becomes inactive, or

- b2: its bit clock has not been received for a period equal to the TC clack timeout, or

- c2: no Start Sequence has been detected for a period equal to the TC active timeout, or

- d2: a Tail Sequence or a codeblock rejection has occurred, or

- e2: the TCO active signal is asserted.

Upon events (a2) and (d2), the selection logic returns to the search state. Upon events (b2) and (c2), the selection logic ignores the TC1 input until event (a2) occurs. Upon event (e2) the TCl input is inhibited and the TC0 input is selected as previously described.

The TC clock timeout value between two successive edges of the TC channel clock is: 3932160  $t_{\text{CK}}$  < TC clock timeout < 4587520  $t_{\text{CK}}$ . With a system clock frequency  $f_{\text{CK}}$  of 4 MHz this equals 0.98s <TC clock timeout < 1.15s.

The TC active timeout value between two successive Start Sequence patterns being detected is 334233600  $t_{\rm CK}$  < TC active timeout < 335399960  $t_{\rm CK}$ . With a system clock frequency  $f_{\rm CK}$  of 4MHz this equals 83.5s < TC active timeout < 83.9s.

#### **Codeblock Decoding**

Codeblock decoding is performed for each received codeblock. At the sending end, a systematic block coding procedure processing 56 bits per Codeblock and generating 7 parity check bits per Codeblock is used. The parity check bits are then complemented and placed into the codeblocks: P0 (MSB) through P6 are located in the first seven bits (MSBs) of the last octet of the codeblock. The last bit of the last octet, P7 (LSB), is a filler bit appended to complete the 8-bit Error Control Field. This Filler Bit should normally be a zero, except for the Tail Sequence. The code is a (63,56) modified Bose-Chaudhuri-Hocquenghem (BCH), based on the following polynomial generator:  $g(x)=x^7+x^6+x^2+1$ . A single error correction & double error detection mode is provided by using this code.

The following table describes the Decoding Strategy of the codeblocks:

| ERRORS DETECTED                                                                     | FILLER BIT<br>VALUE | DECISION                                                 |

|-------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------|

| no errors                                                                           | ignored             | codeblock<br>accepted                                    |

| even number of errors                                                               | ignored             | codeblock<br>rejected                                    |

| odd number of errors<br>with a binary syndrome<br>value equal to all zeros          | ignored             | codeblock<br>rejected                                    |

| odd number of errors<br>with a binary syndrome<br>value different from all<br>zeros | 0                   | codeblock<br>accepted<br>correction of<br>a single error |

| odd number of errors<br>with a binary syndrome<br>value different from all<br>zeros | 1                   | codeblock<br>rejected                                    |

## **CLTU Management**

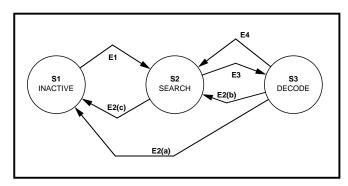

CLTU decoding consists of the states and events summarized in the following table and state diagram:

Figure 4: CLTU Decoder State Diagram

| State Number | State Name | State Definition                                                                                                                                                |

|--------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1           | INACTIVE   | All telecommand channels are inactive (no bit lock is achieved) or no bit modulation is detected.                                                               |

| S2           | SEARCH     | Incoming bit stream is searched, bit by bit, for the Start Sequence pattern.                                                                                    |

| S3           | DECODE     | Codeblocks, which are either free of error or which can be corrected, are received and decoded, and their information octets are transferred to the layer above |

| Event Number | Event Name              | Event Definition                                                                                                                                      |

|--------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1           | CHANNEL ACTIVATION      | Bit modulation is detected and bit lock is achieved:                                                                                                  |

|              |                         | telecommand bit stream is present                                                                                                                     |

| E2 (a) (c)   | CHANNEL<br>DEACTIVATION | Deactivation of the TC Active Signal                                                                                                                  |

| (b)          | CLTU ERROR              | More than 37 codeblocks accepted in the CLTU or Timeout on the TC Clock signal or Activity on a channel having higher priority in priority mode       |

| E3           | START SEQUENCE<br>FOUND | The Start Sequence pattern has been detected, signalling the beginning of the first codeblock of the CLTU                                             |

| E4           | CODEBLOCK<br>REJECTION  | A codeblock is found uncorrectable (erroneous codeblock or tail sequence). No information octet from this codeblock is transferred to the layer above |

Codeblock transfer is performed in a serial way to the above layer (Transfer layer). Two indication signals are provided to the above layer - one indicating the whole frame duration, the other asserted each time a 7 octets block is being transferred.

The following rules apply to the data transfer between the Coding Layer and the Transfer Layer:

- When the first Candidate Codeblock is affected by an event E4 or by an event E2, the CLTU is abandoned. No Candidate Frame is transferred to the Transfer Layer.

- When the first Candidate Codeblock is found to be error free, or if it contained one error which has been corrected, its information octets (i.e. 7 octets) are transferred to the Transfer Layer. The decoding of the CLTU continues until one of the following events occurs:

- 1- when an event E4 (codeblock rejection) occurs for any of the 37 possible Candidate Codeblocks the decoder returns to the search state S2 with the following actions:

- The codeblock is abandoned

- No information from that codeblock is transferred to the layer above

- The Coding Layer indicates to the Transfer Layer the end of transfer of the Candidate Frame.

- 2- when an event E2 (channel deactivation) occurs the decoder returns to the inactive state (for the channel) with the following actions:

- The CLTU is aborted,

- The CLTU is reported as abandoned,

- A signal is sent to the Transfer Layer to indicate that the entire block of octets making up the Candidate Frame must be erased.

- 3- When an event E2(b) (CLTU error) occurs, the decoder returns to the search state with the following actions:

- The CLTU is aborted,

- The CLTU is reported as abandoned,

- A signal is sent to the Transfer Layer to indicate that the entire block of octets making up the Candidate Frame must be erased.

- A CLTU error occurs in the following cases:

- More than 37 codeblocks have been accepted in the  $\operatorname{CLTU}$ ,

- A timeout on the TC clock signal occurs,

- Activity on a channel having higher priority is detected in priority mode.

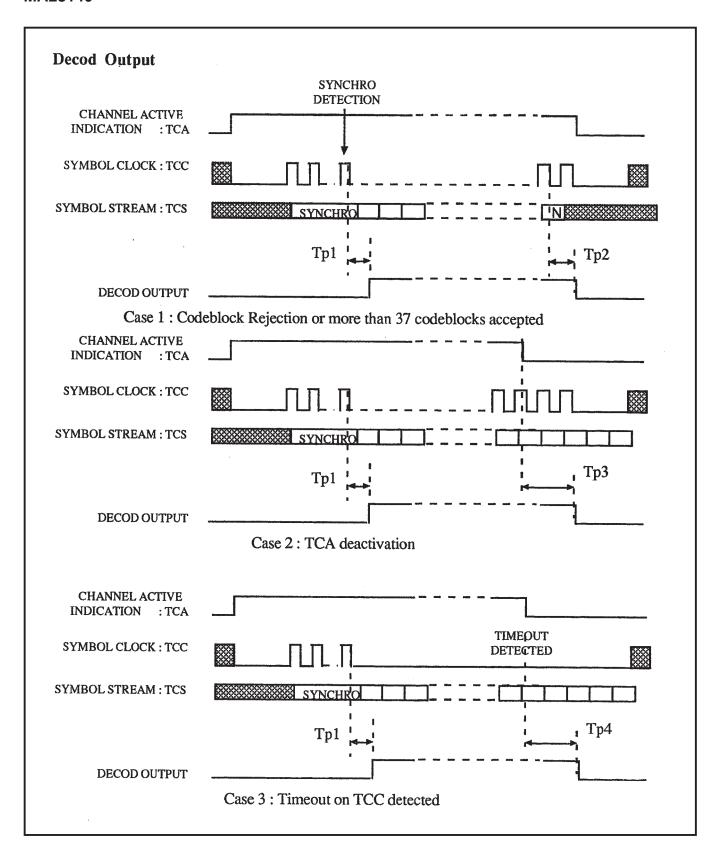

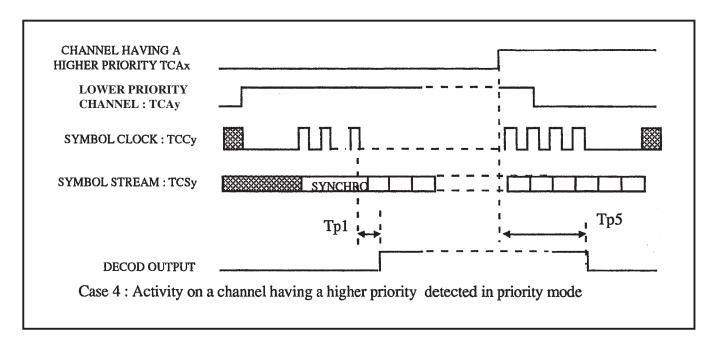

The DECOD output is activated when the CLTU decoder state is S3.

#### **4.2 TRANSFER LAYER**

## Overview of the Layer

The Transfer Layer implements the following sublayers:

- The Frame Error Control Sublayer which ensures that only "clean" frames are transferred to the sublayer above by using a CRC error syndrome verification.

- The Frame Header Sublayer verifies the conformity of the relevant frame header fields by using the Legal Frame Validation process before passing the frame to the FARM1.

- The "Frame Acceptance and Reporting Mechanism One" or FARM1 ensures that frames are processed in the correct sequence.

There are three types of TC transfer frames:

- two types for the Sequence-Controlled Service: AD and BC frames

- one type for the Expedited Service: BD frames

The Sequence-Controlled Service is used for normal spacecraft communications. It concerns essentially TC Transfer Frames carrying TC segments: the AD frames. To configure the AD machine, special control frames are used called BC frames.

The Expedited Service is used for recovery in the absence of the telemetry downlink or during unexpected situations. It is only concerned with TC transfer frames carrying TC segments: the BD frames.

## Standard Data Structures Within the Layer

The major fields of the TC Transfer Frame are shown below:

| 5 octets     | 1 to 249 octets  | 2 octets                     |

|--------------|------------------|------------------------------|

| Frame Header | Frame Data Field | Frame Error<br>Control Field |

## Frame Header

The structure of the frame header is given below:

|                   |                | 2 octets                   |                     |                  | 1                        | octet               | 1 octet         | 1 octet                     |

|-------------------|----------------|----------------------------|---------------------|------------------|--------------------------|---------------------|-----------------|-----------------------------|

| version<br>number | bypass<br>flag | control<br>command<br>flag | reserved<br>field A | spacecraft<br>ID | virtual<br>channel<br>ID | reserved<br>field B | frame<br>length | frame<br>sequence<br>number |

| 2                 | 1              | 1                          | 2                   | 10               | 6                        | 2                   | 8               | 8                           |

A description of the fields of the frame header is given below:

- Version number, Reserved field A and Reserved field B should always be 00 (ref 1).

- Bypass flag and control command flags. Their values are given in the next table:

| Bypass Flag Control Command Flag |   | Interpretation |

|----------------------------------|---|----------------|

| 0                                | 0 | AD frames      |

| 0                                | 1 | ILLEGAL        |

| 1                                | 0 | BD frames      |

| 1                                | 1 | BC frames      |

• Spacecraft identifier. This field provides the identification of the spacecraft being commanded.

- Virtual channel identifier. It is used as a spacecraft subidentifier. It can provide an identification of the spacecraft telecommand chain selected for operating the spacecraft.

- Frame length. This field specifies the number of octets contained within the entire TC transfer frame:

Field Value = (Total number of octets) - 1

- Frame sequence number. This number is denoted as N(S). It is set to different values:

- for AD frames it should be set to the Transmitter Frame Sequence Number and it is compared to the Receiver Frame Sequence Number V(R) stored in the PTD, to control the transfer of a sequence of frames (see the FARM-1 process)

- for BC and BD frames it should be set to all zeros.

Except for the bypass and control command flags, the values of the first three header octets are programmed in the external ROM.

In the abbreviations AD, BD and BC, A stands for Acceptance check of N(S), B stands for Bypass of A, C stands for Control and D stands for Data. AC is an illegal combination because Control Commands cannot reliably use a transfer service which they are meant to modify.

#### Frame Data Field

The frame data field is of variable length from a minimum of 1 octet to a maximum of 249 octets. When the frame is a data frame (type AD or BD), it contains a TC segment. When the frame is a BC frame, this field can contain 2 control commands to configure the FARM-1 process:

• the UNLOCK command. The FARM-1 has a built in mechanism which will go into a Lockout state whenever it receives a type-AD frame containing a frame sequence number N(S) outside the limits of the FARM-1 Sliding Window. The UNLOCK command provides a mechanism to reset the Lockout condition. The UNLOCK command is encoded as a single octet with the value: 00000000.

• The SET V(R) command. The SET V(R) command allows V(R) to be preset to any desired value. The SET V(R) command is encoded as three octets with the values:

10000010 00000000

XXXXXXX

The value to be set into V(R) is stored in the third octet.

## Frame Error Field

The frame error field is a mandatory 16-bit field which occupies the two trailing octets of the TC Transfer Frame. It is a cyclic redundant code (CRC) generated with the polynom  $X^{16}+X^{12}+X^5+1$  with the shift register being initialised to all ones before processing each frame (refer to ref 2 for a complete description of this field). The CRC is only used for error detection by the frame and not for error correction.

## Standard Procedures Within the Layer

#### The Clean Frame Validation Process

On receiving a new frame, the Clean Frame Validation process performs the following tasks:

- the number of octets in the frame is checked to be greater than 7 octets.

- the transfer frame is assumed to be a version 1 frame,

- the frame length field is checked to be compliant with the real number of octets of the frame.

- the number of fill octets is verified to be minimum zero and maximum six,

- the fill octets are removed,

- the CRC error syndrome verification is carried out.

All candidate frames passing all the preceding validation checks are declared clean and transferred immediately to the Legal Frame Validation process. Frames failing any of the preceding tests are declared dirty and are erased.

## The Legal Frame Validation Process

On receiving a clean frame, the Legal Frame Validation process performs the following validation checks:

- the version number is checked to be as defined in the ROM,

- the reserved fields A and B are checked to be as defined in the ROM,

- the value of the spacecraft ID is checked to be as defined in the ROM.

- the value of the Virtual Channel ID is checked to be as defined in the ROM and by the VCLSB input,

- the Bypass and Control Command flags must combine legally,

- the BC frames must contain a valid control command (either UNLOCK or SET V(R)),

- for a BC or BD frame the Frame Sequence Number field must be set to all zeros.

The LSB of the VC ID is indirectly defined from a dedicated pin VCLSB; it allows easy configuring of a pair of redundant TC decoders.

- VCLSB = 1: The VC ID LSB read from the ROM is inverted.

- VCLSB = 0: The VC ID LSB read from the ROM is not inverted.

All candidate frames passing all the preceding validation checks are declared legal and transferred immediately to the FARM-1 process. Frames failing any of the preceding tests are declared illegal and erased.

## The FARM-1 Process

#### THE FARM-1 VARIABLES

The Frame Acceptance and Reporting mechanism (FARM-1) is described by a finite state machine represented by the FARM-1 state table. The FARM-1 maintains a set of variables which are described below:

- The State. This may be one of the following:

- Open (S1)

- Wait (S2)

- Lockout (S3)

This variable represents the state of the FARM-1 automaton. In Open State, the FARM-1 accepts frames and passes them to the above layer. In Wait State, there is no buffer space available in which to place any further received data of type AD. The protocols leaves the Wait State upon receipt of a buffer release signal from the Higher Layer. Lockout is entered if the protocol machine detects an error. It is a safe state in that no user data (AD frames) will be accepted or transferred to the Higher Layer. The only accepted data frames are the BD frames, but even in this case the protocol machine remains in lockout state. The protocol machine leaves the Lockout State upon receipt of an UNLOCK control command.

- The Lockout Flag. This is set to 1 whenever the protocol is in the Lockout State.

- The Wait Flag. This is set to 1 whenever the protocol is in Wait State.

- The Retransmit Flag. This is set to 1 whenever the protocol machine knows that an AD frame has been lost in transmission or has been discarded because there was no buffer space available. This flag is reset to 0 upon the successful receipt of a frame with N(S)=V(R), the receipt of a SET V(R) control command (unless in Lockout State) or receipt of an UNLOCK control command.

- FARM B counter. This is incremented whenever a valid BD or BC frame arrives. This counter is a 2 bit wraparound counter.

- Receiver Frame Sequence Number V(R). This records the value of N(S) expected to be seen in the next AD frame.

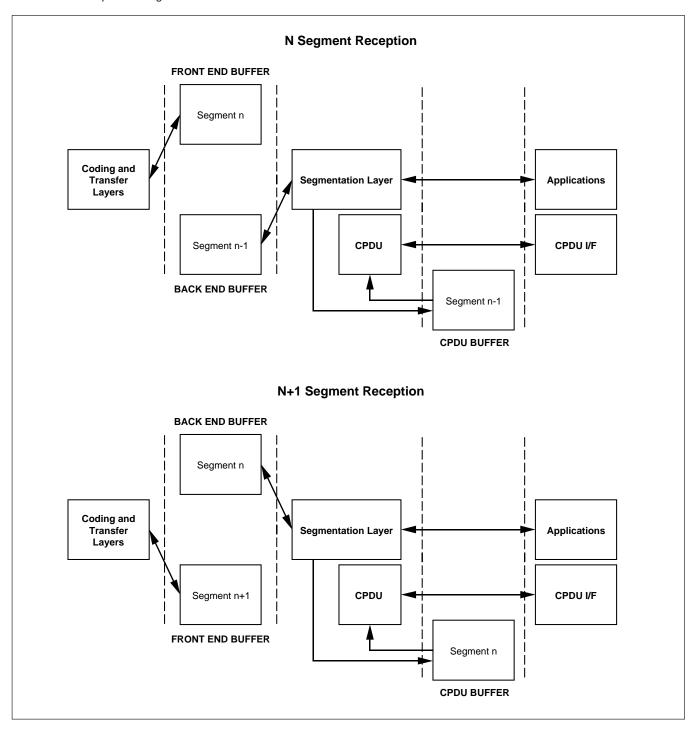

- The buffer management variable. The PTD maintains a flag indicating the number of the back end buffer. The AUBUF output pin provides the value of this flag (the back end and front end buffers are represented in Figure 6). The number of the TC channel on which the data stored in the back-end buffer has been received is provided on the output pins (SELTC2-0).

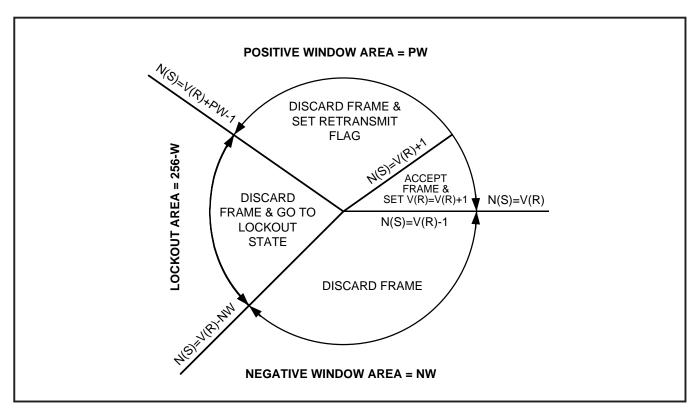

- FARM Sliding window variables. The purpose of these are to protect FARM-1 against the unauthorised transfer of a sequence of frames such that the Frame Sequence Number N(S) of one or more of these frames will exceed the current value of the V(R) counter. The FARM Sliding Window concept applies only to AD frames.

The FARM Sliding Window is defined in terms of two variables:

- the width of the positive part referred to as PW

- the width of the negative part referred to as NW

The FARM Positive window area starts with V(R) and extends PW frames in the positive direction. The FARM Negative window starts at V(R) - 1 and extends NW frames in the negative direction.

Figure 5: The FARM Sliding Window Concept

A Frame Sequence Number N(S) falls outside the FARM Sliding Window i.e. in the Lockout Area when:

N(S)>V(R)+PW-1 N(S)<V(R)-NW

In this case, the Lockout flag is set.

When N(S) falls inside the FARM Sliding Window, one of the following three cases can occur:

• First case N(S)=V(R)

The frame is accepted

Second Case

N(S)>V(R) and  $N(S)\leq V(R)+PW-1$

The frame is in the positive window and does not contain the expected Frame Sequence Number. The Frame is discarded and the retransmit Flag is set.

• Third Case

N(S)<V(R) and N(S)≥V(R)-NW

The frame is in the negative window and is discarded without any other action being taken.

#### THE FARM-1 PROCESS DESCRIPTION

At the user end of the FARM-1 process the TC segments are delivered as a buffer of accepted data. No distinction is made between a TC segment delivered by means of an AD frame and one delivered by a BD frame. However, the management of the common FARM-1 back end buffer is affected as follows:

#### • BD Frames:

When a frame of this type is accepted by the FARM-1, the TC segment it contains shall be placed in the back end buffer of the FARM-1 even if this buffer still contains data (partially read or not ) in which case this data will be erased, an abort signal sent to the Segment Layer to signal the erasure and the new data signalled as arrived. This implies an Event E10.

#### AD frames:

When a frame of this type is accepted by the FARM-1, the TC segment it contains is placed in the back end buffer of the FARM-1 only when the buffer is available (empty). If the buffer still contains data, the newly arrived frame is discarded (erased) as shown by the FARM-1 state table (Event E2 in table 1).

The definitions used in the FARM-1 State Table are listed below:

- "Valid frame arrives" means that the Legal Frame Validation Sublayer has placed a legal frame in the front-end buffer. If the frame is a data frame (AD or BD) and if the FARM-1 accepts it, the back end buffer is allocated for the data.

- "Accept" for an AD frame is subject to a buffer available signal. When no back end buffer is available (Event E2) the frame is discarded. The data is then made available for the Authentication Layer, or the Segmentation Layer if Authentication is disabled.

- "Accept" for a BD frame means that the TC segment is placed in the back end buffer even when this buffer still contains data, in which case this previous data is erased (event E10). The Wait concept does not apply to BD frames. The data is available for the Authentication Layer, or the Segmentation Layer if Authentication is disabled.

| State Name            | OPEN            | WAIT            | LOCKOUT         |

|-----------------------|-----------------|-----------------|-----------------|

|                       | Normal state to | Wait Flag is on | Lockout Flag is |

| Main Feature of State | accept frames   |                 | on              |

| State Number          | (S1)            | S(2)            | S(3)            |

| Event                     | Conditions                                               |                                              | Event<br>Number | OPEN                                                   | WAIT           | LOCKOUT |

|---------------------------|----------------------------------------------------------|----------------------------------------------|-----------------|--------------------------------------------------------|----------------|---------|

|                           | N(S)=V(R)                                                | A buffer is<br>available for this<br>frame   | E1              | Accept frame,<br>V(R):=V(R)+1R<br>etransmit<br>Flag:=0 | Not applicable | Discard |

|                           |                                                          |                                              |                 | (S1)                                                   |                | (S3)    |

| Valid AD frame<br>arrives | N(S)=V(R)                                                | No buffer is<br>available for this<br>frame  | E2              | Discard,<br>Retransmit<br>Flag:=1,<br>Wait Flag:=1     | Discard        | Discard |

|                           |                                                          |                                              |                 | (S2)                                                   | (S2)           | (S3)    |

|                           | N(S)>V(R)<br>N(S)≤V(R)<br>i.e. inside<br>part of sliding | and<br>+PW-1<br>positive<br>window and >V(R) | E3              | Discard,<br>Retransmit<br>Flag:=1                      | Discard        | Discard |

|                           | N(S)<                                                    |                                              |                 | (S1)                                                   | (S2)           | (S3)    |

Table 1: The FARM-1 State Table

| Event   Conditions   Number   OPEN   WAIT   LOCKOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cont') Valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Retransmit Flag:=0   Naid Unlock BC frame arrives   Naid Unlock BC frame arrives   Valid Unlock BC frame arrives   Naid Unlock BC frame arrives   Retransmit Flag:=0   V(R):=V*(R)   V(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*(R):=V*   |

| AD frame arrives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AD frame arrives    N(S)>V(R)+PW-1 and N(S) <u(r)-nw discard="" e5="" flag:="1" i.e.="" lockout="" outside="" s(s3)="" s<="" sliding="" td="" window=""  =""></u(r)-nw>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| arrives N(S) <v(r)-nw (s1)="" (s2)="" (s3)="" accept,="" arrives="" bc="" counter="" counter,="" e6="" e7="" farm-b="" flag:="0&lt;/td" frame="" i.e.="" increment="" lockout="" outside="" retransmit="" sliding="" unlock="" valid="" wait="" window=""></v(r)-nw>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Sliding window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Flag:=1   Flag:=1   Flag:=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (S3) (S3) (S3)  E6 Accept, Increment FARM-B Counter  (S1) (S2) (S3)  E7 Increment FARM-B Counter, Retransmit Flag:=0  Valid Unlock BC frame arrives  (S1) (S1) (S1) (S1)  E8 Increment FARM-B Counter, Retransmit Flag:=0  V(R):=V*(R)  (S3) (S3)  Accept, Increment FARM-B Accept, Increment FARM-B Counter  FARM-B Counter  FARM-B Counter  FARM-B Counter  FARM-B Counter  FARM-B Counter, Retransmit Flag:=0  (S1) (S1) (S1)  Increment FARM-B Counter  Retransmit Flag:=0  Wait Flag:=0  V(R):=V*(R)  Wait Flag:=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Valid BD frame arrives*  E6 Accept, Increment FARM-B Counter  (S1) (S2) (S3)  E7 Increment FARM-B Counter, Retransmit Flag:=0, Wait Flag:=0, Wait Flag:=0, V(S1)  (S1) (S2) (S3)  Increment FARM-B Counter, Retransmit Flag:=0, Wait Flag:=0, U(S1)  (S1) (S1) (S1) (S1)  E8 Increment FARM-B Counter, Retransmit Flag:=0, Wait Flag:=0, Wait Flag:=0, U(S1)  (S1) (S1) (S1)  (S1) Increment FARM-B Counter, Retransmit Flag:=0, Wait  |

| Valid BD frame arrives*  E7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Valid BD frame arrives*  (S1)  (S2)  (S3)  E7  Increment FARM-B Counter, Retransmit Flag:=0  Valid Unlock BC frame arrives  (S1)  (S2)  (S3)  Increment FARM-B Counter, Retransmit Flag:=0, Wait Flag:=0, Wait Flag:=0, Wait Flag:=0  (S1)  (S1)  (S1)  (S1)  (S1)  (S1)  Increment FARM-B Counter, Retransmit Flag:=0 V(R):=V*(R)  Wait Flag:=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (S1) (S2) (S3)  E7 Increment FARM-B Counter, Retransmit Flag:=0 (S1) (S1) (S1)  Valid Unlock BC frame arrives  (S1) (S2) (S3)  Increment FARM-B Counter, Retransmit Flag:=0, Wait Flag:=0, Wait Flag:=0, Wait Flag:=0 (S1) (S1) (S1)  E8 Increment FARM-B Counter, Retransmit Flag:=0 (Counter, Retransmit Flag:=0)  V(R):=V*(R) Wait Flag:=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E7 Increment FARM-B Counter, Retransmit Flag:=0 (S1) (S1) (S1) Increment FARM-B Counter, Retransmit Flag:=0 (S1) (S1) Increment FARM-B Counter, Retransmit Flag:=0 (S1) (S1) (S1) Increment FARM-B Counter, Retransmit Flag:=0 (S1) Increment FARM-B Counter, Retransmit Flag:=0 (S1) Increment FARM-B Counter, Retransmit Flag:=0 (S1) (S1) (S1) (S1) (S1) (S1) (S1) (S1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Counter, Retransmit Flag:=0  Valid Unlock BC frame arrives  (S1)  E8  Increment FARM-B Counter, Retransmit Flag:=0  (S1)  (S1)  Increment FARM-B Counter, Retransmit Flag:=0  V(R):=V*(R)  Counter, Retransmit Flag:=0  Wait Flag:=0, Wait Flag:=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Valid Unlock BC frame arrives  Retransmit Flag:=0, Wait Flag:=0, Wait Flag:=0, Wait Flag:=0, Wait Flag:=0, Wait Flag:=0  (S1) (S1) (S1)  E8 Increment FARM-B Counter, Retransmit Flag:=0 V(R):=V*(R)  Wait Flag:=0 Wait Flag:=0 Wait Flag:=0  Wait Flag:=0, Wa |

| Valid Unlock BC frame arrives  (S1)  (S1)  (S1)  (S1)  (S1)  (S1)  (S1)  (S1)  (S1)  Increment FARM-B  Counter,  Retransmit Flag:=0  V(R):=V*(R)  Wait Flag:=0  Wait Flag:=0, Lockout  Flag:=0  Wait Flag:=0, Lockout  Flag:=0  Wait Flag:=0, Lockout  Flag:=0  Wait Flag:=0  Wait Flag:=0  Wait Flag:=0  Wait Flag:=0  V(S1)  (S1)  Increment FARM-B  Counter,  Retransmit Flag:=0  Wait Flag:=0  Wait Flag:=0  Wait Flag:=0  V(S1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Valid Unlock BC frame arrives  (S1)  (S1)  (S1)  (S1)  (S1)  (S1)  (S1)  Increment FARM-B  Counter,  Retransmit Flag:=0  V(R):=V*(R)  Flag:=0  (S1)  (S1)  (S1)  Increment FARM-B  Counter,  Retransmit Flag:=0  Wait Flag:=0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E8 Increment FARM-B Counter, Counter, Retransmit Flag:=0 V(R):=V*(R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

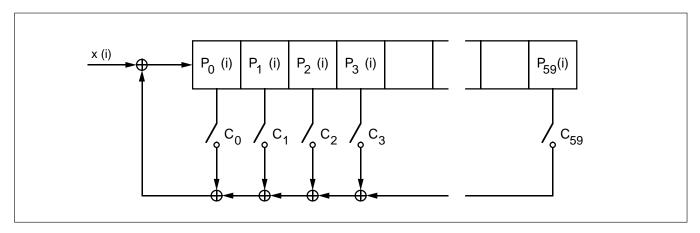

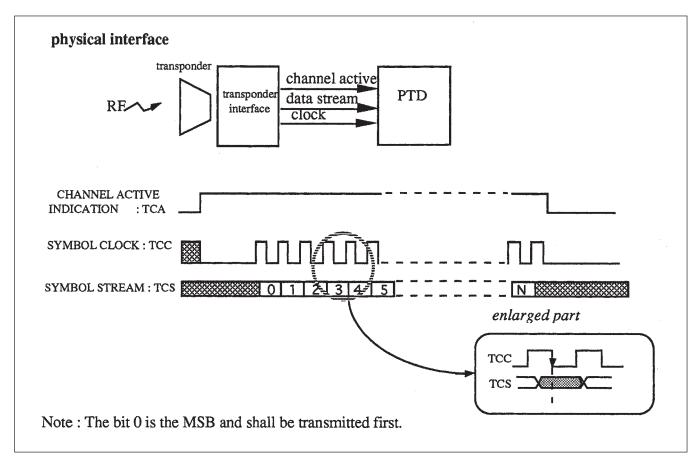

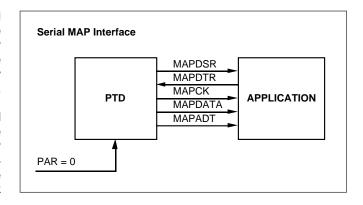

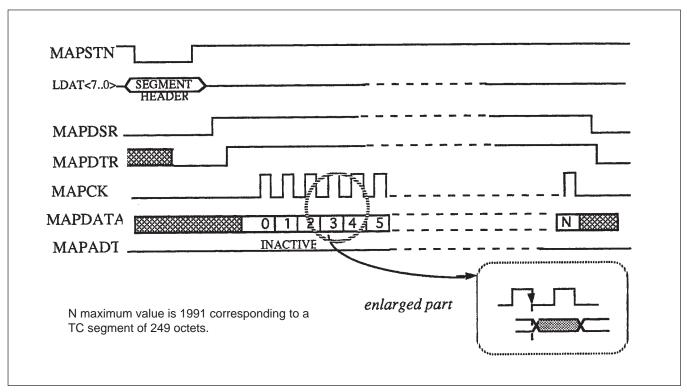

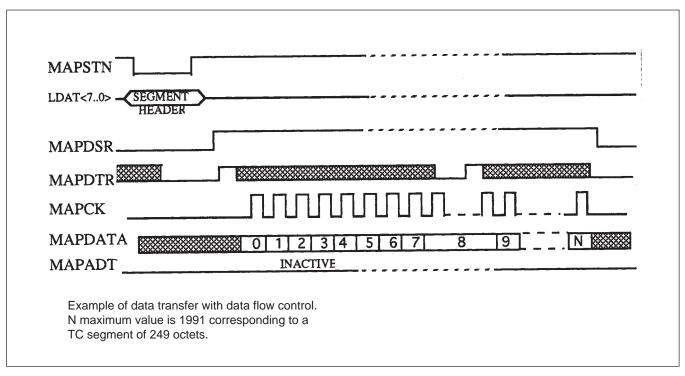

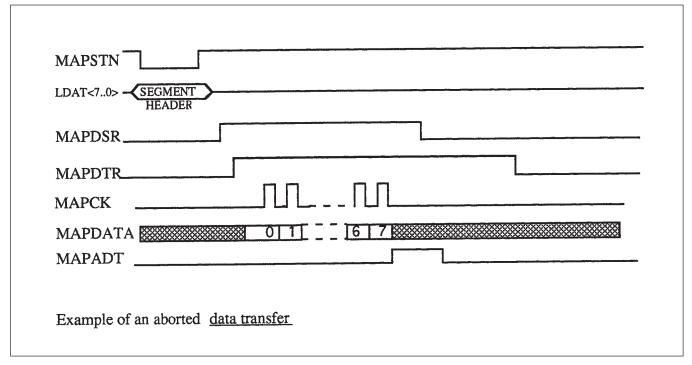

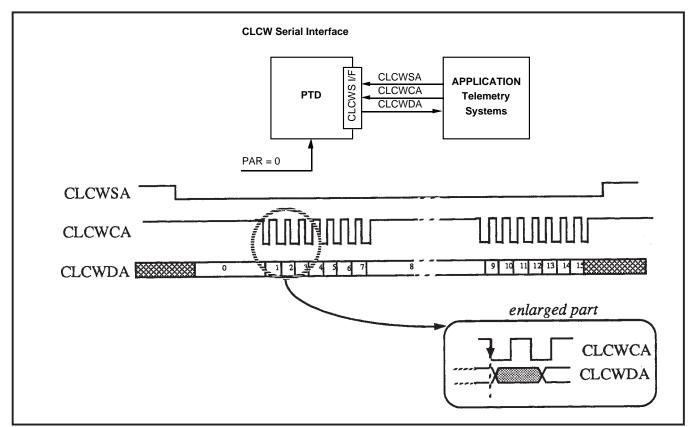

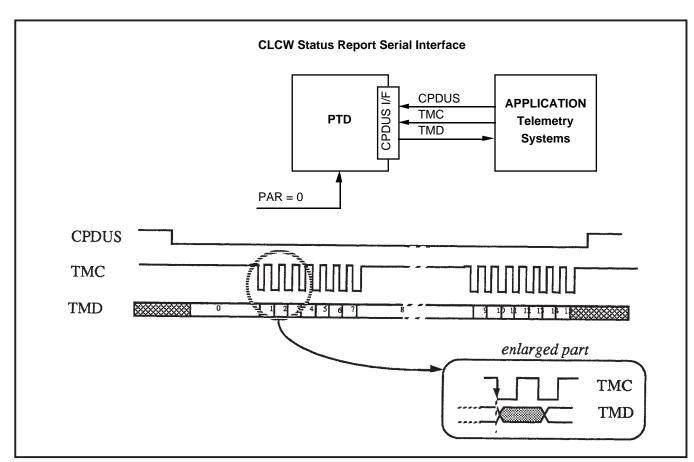

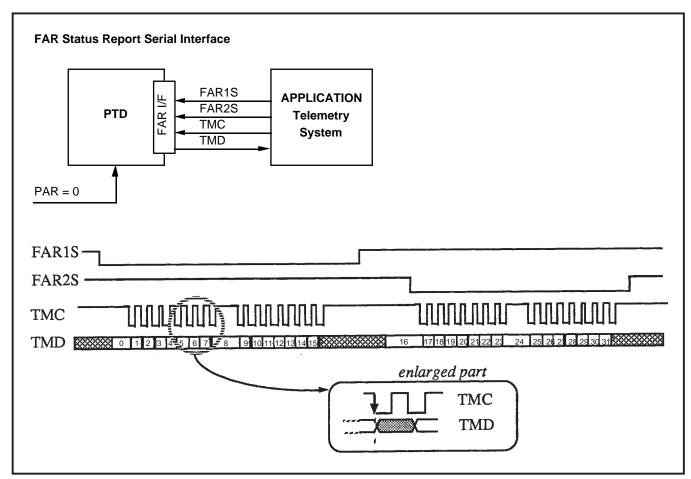

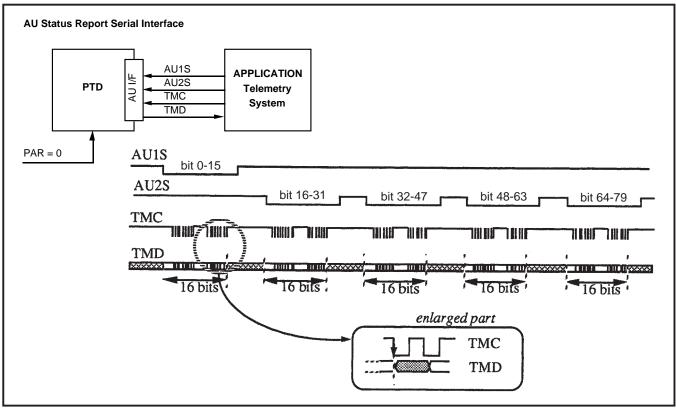

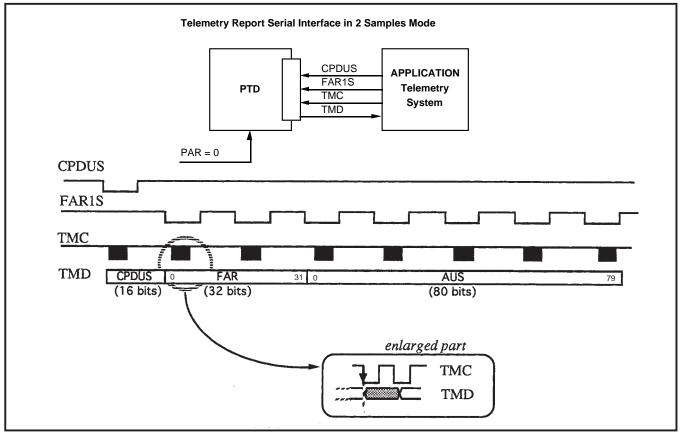

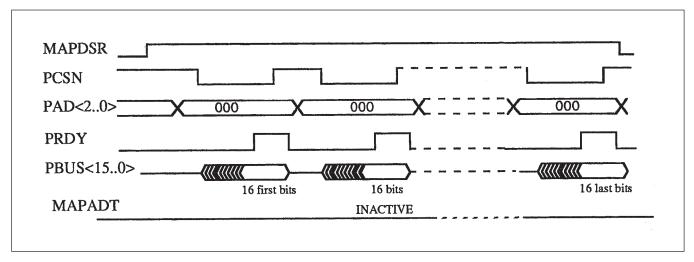

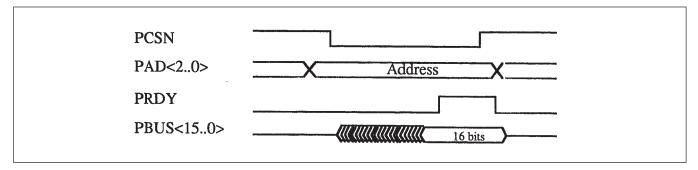

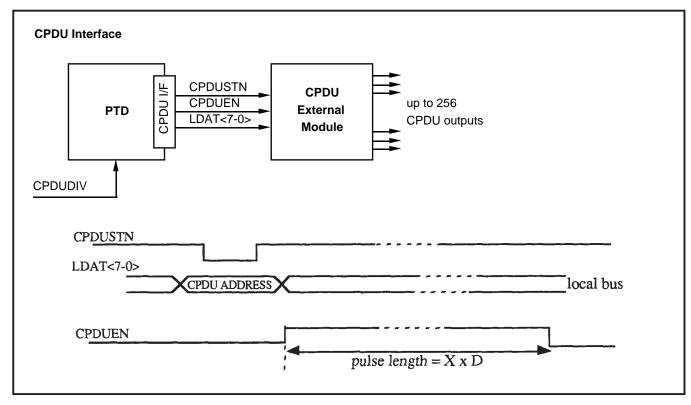

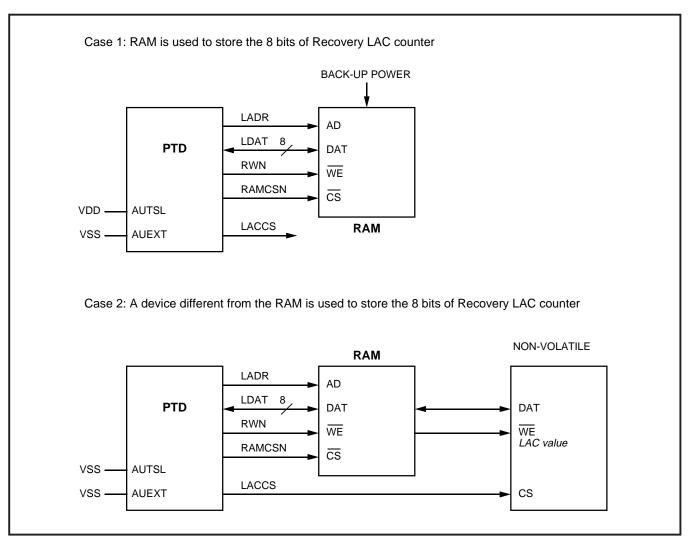

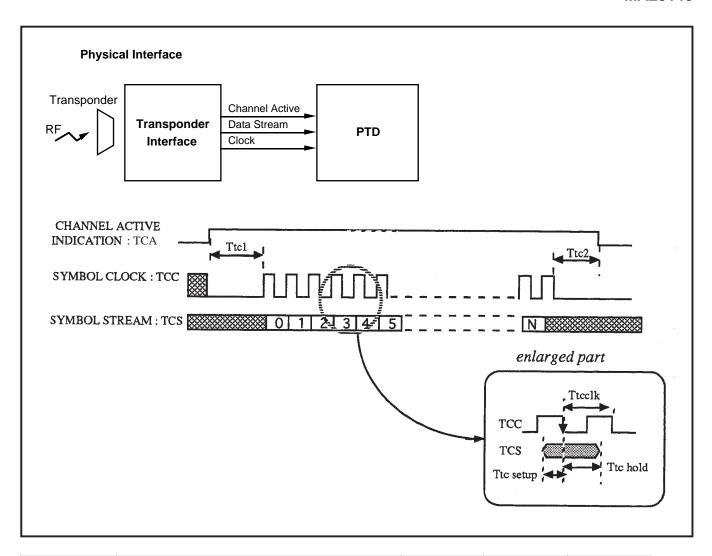

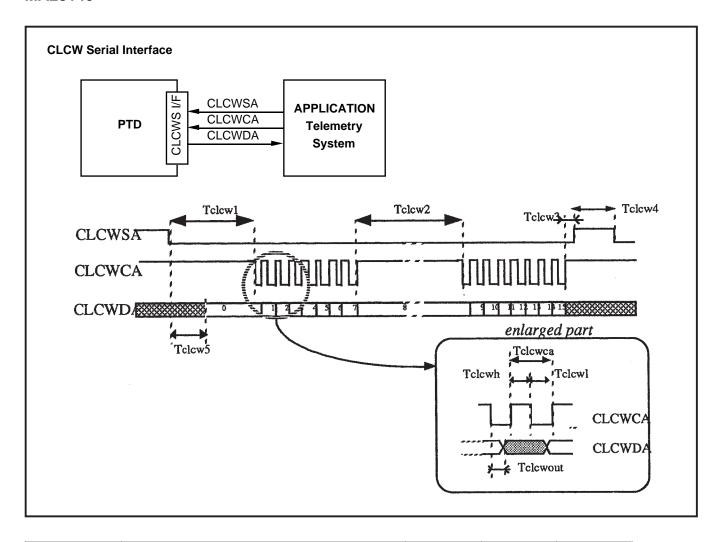

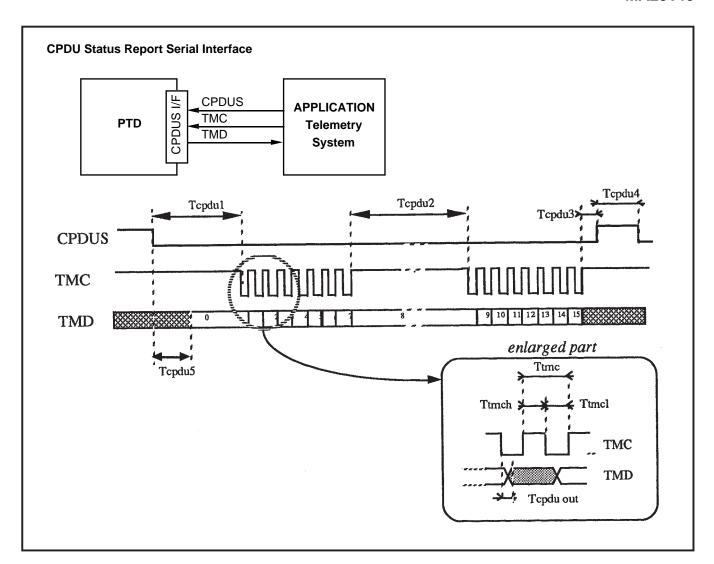

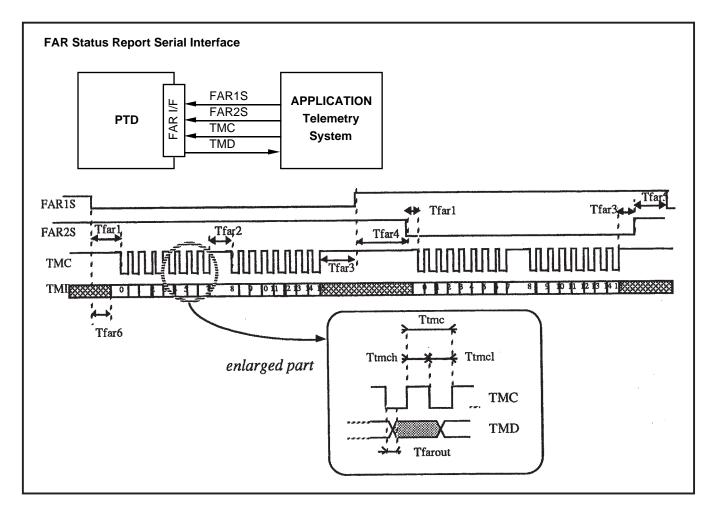

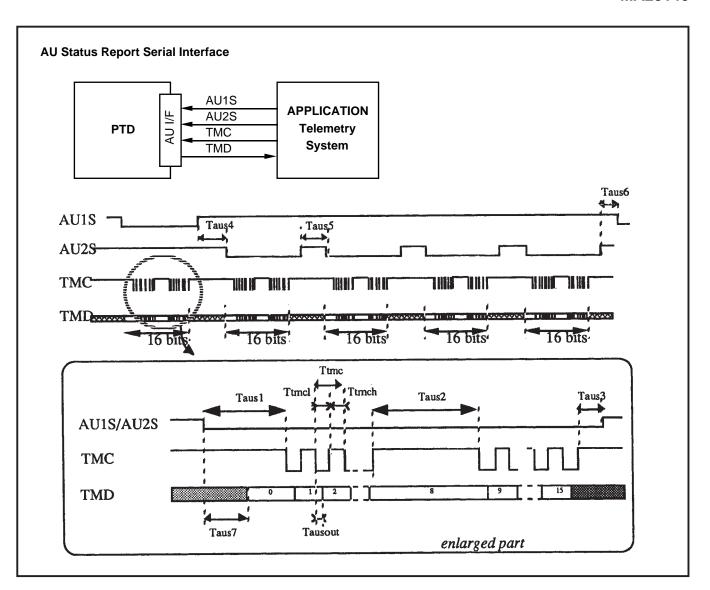

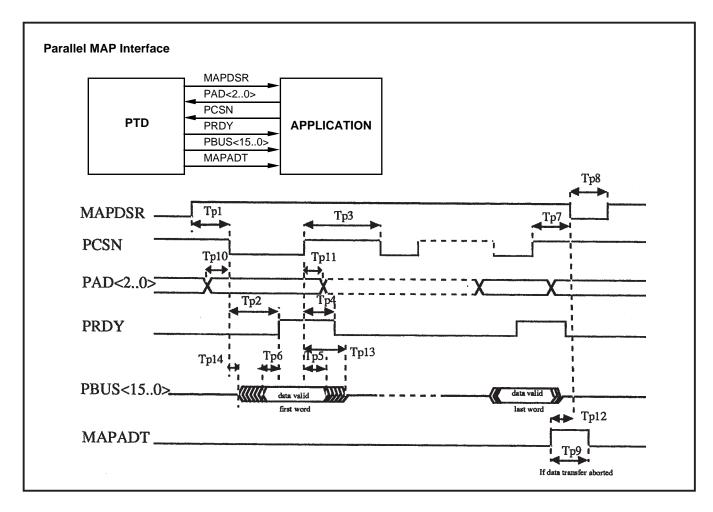

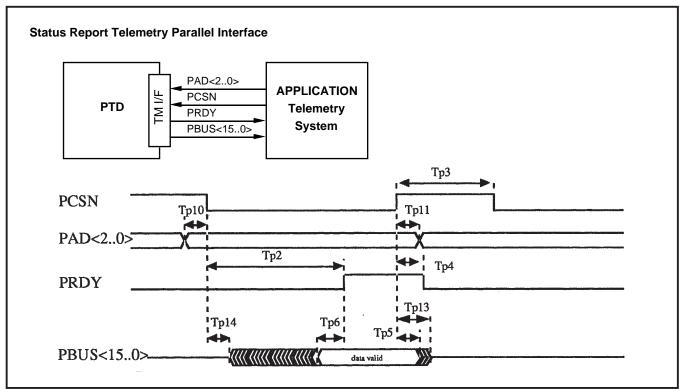

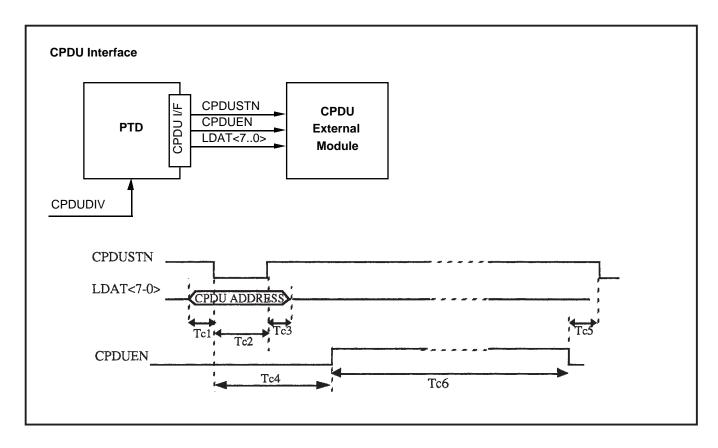

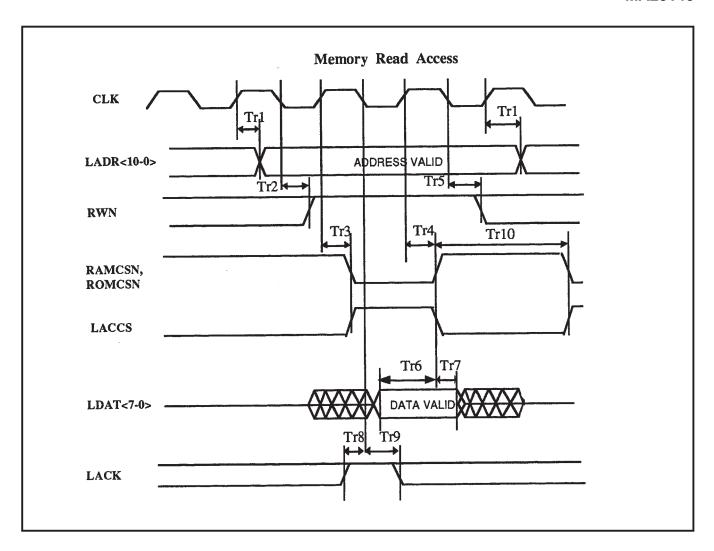

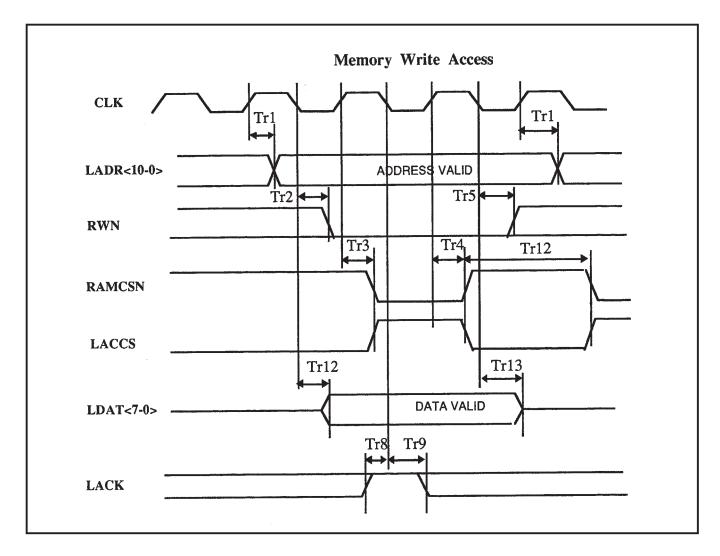

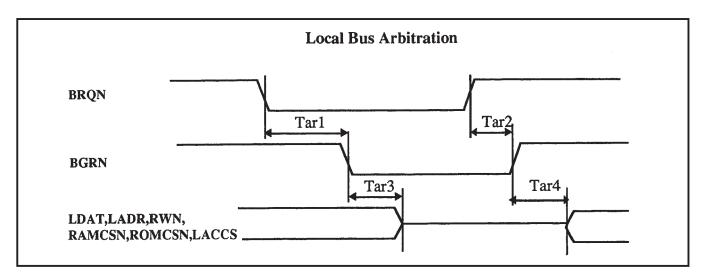

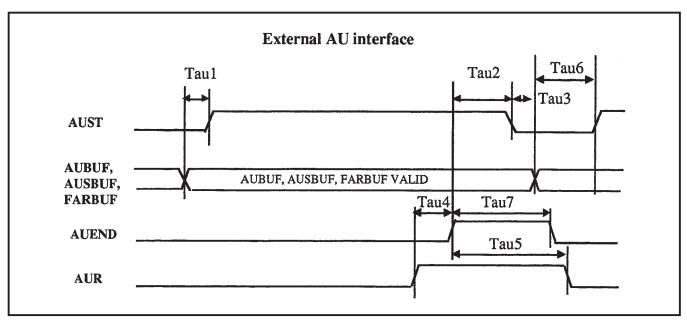

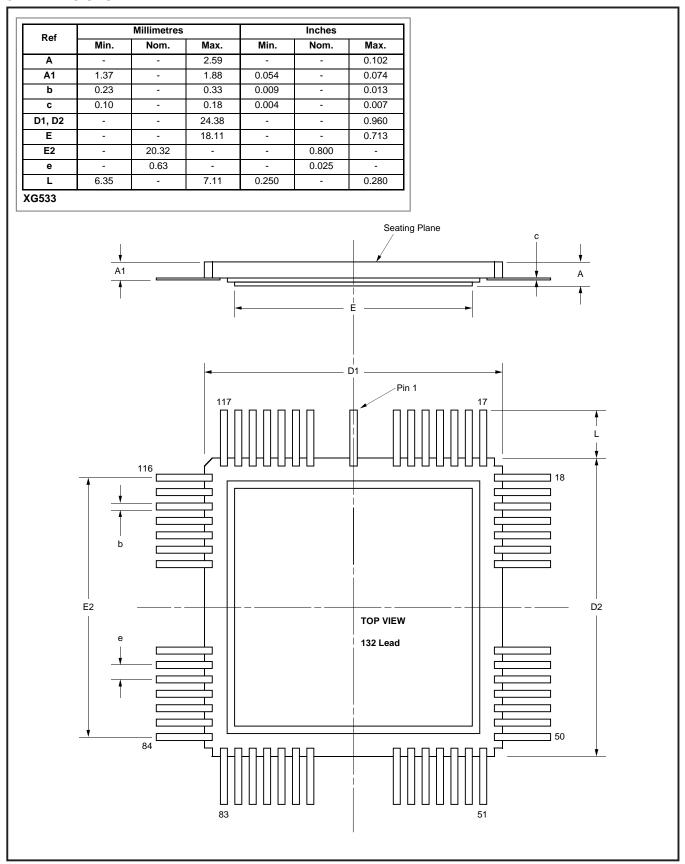

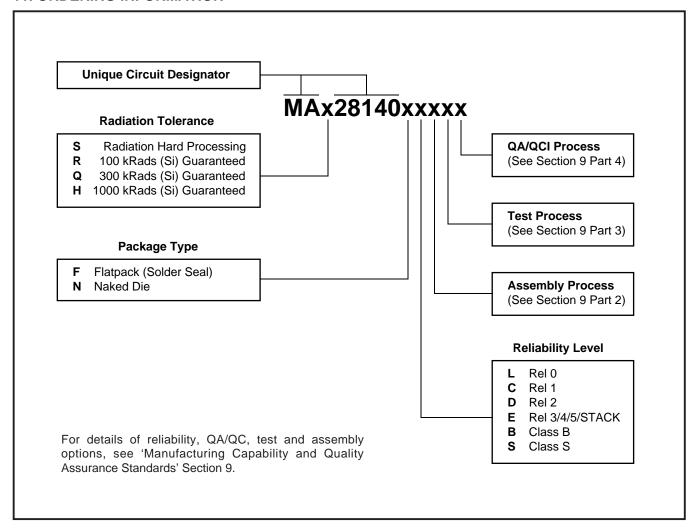

| E8 Increment FARM-B Counter, Counter, Retransmit Flag:=0 V(R):=V*(R)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |