### DESCRIPTION

The ES3986 digital-audio processor chip is ESS Technology's highly integrated, optimal-quality, and costeffective single-chip solution for the emerging digital-audio market. Its target applications include internet audio platforms, MP3 CD players in boom box and combination systems, portable MP3 CD player, etc.

Based on the programmable multimedia processor (PMP) ES3986 architecture. the integrates softwareconfigurable 32-bit reduced instruction set computing (RISC) processor and a 64-bit vector processor core. The RISC CPU can be used in place of a microcontroller to provide the functions of system management, user interface, and peripheral control. The vector processor is dedicated for audio-specific processing. In addition to MPEG audio decoding, it will generate 3D sound effects, and support karaoke features, such as key control and echo. The chip also provides the voice-activated ADPCM codec for voice recording and language learning through MIC input.

The ES3986 supports a variety of CD servos directly to provide the system solution of lower BOM cost and manufacturing flexibility. With its low system power consumption, the built-in antishock capabilities, and 16-Mbit DRAM support, the ES3986 is very suitable for portable audio applications.

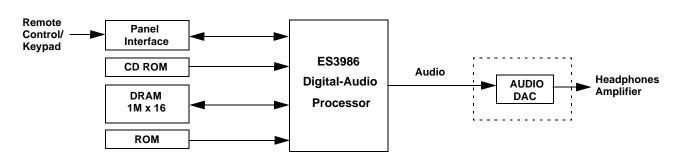

Figure 1 shows a typical standalone system using a MP3 player, where the MP3 stream from a CD-ROM is passed to the ES3986, which parses the system layer and decodes the audio layer. The decoded MPEG audio and 3D sound enhancement is then passed to the external audio DAC.

## FEATURES

- Programmable multimedia processor (PMP) architecture

- MPEG1/MPEG2 and MP3 audio decoder

- CD block decoder functions

- STC interpretation and audio phase-lock loop (PLL)

- 256/384 fs for audio system clock

- Programmable master clock for external audio DAC

- Independent bit clock for audio transmit and receive

- · Power management

- 2.5V power supply with 5V-tolerant I/Os

- 3D sound and surround sound

- Karaoke function

- Vocal reverb: simulates a theater acoustic environment

- 0.3W power dissipation

- 2-Mb DRAM support

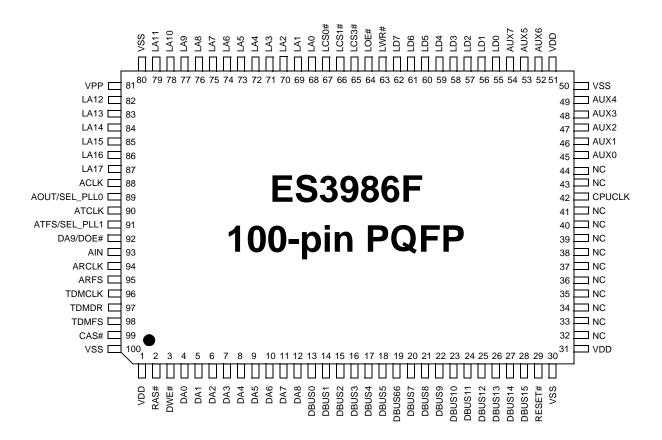

- 100-pin plastic quad flat pack (PQFP) package digitalaudio processor

Figure 1 ES3986 VCD Processor System Block Diagram

## PINOUT

The pinouts for the ES3896 are shown in Figure 2.

Figure 2 ES3986 Pinout Diagram

ES3986 PIN DESCRIPTIONS

####

# **ES3986 PIN DESCRIPTIONS**

The ES3986 pins are listed and described in Table 1.

Table 1 ES3896 Pin Descriptions

| Names             | Pin Numbers           | I/O | Definitions                                                                                                                                                             |  |

|-------------------|-----------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VDD               | 1, 31, 51             | Ι   | Voltage supply for 2.5V.                                                                                                                                                |  |

| RAS#              | 2                     | 0   | DRAM row address strobe (active low).                                                                                                                                   |  |

| DWE#              | 3                     | 0   | DRAM write enable (active low).                                                                                                                                         |  |

| DA[8:0]           | 4:12                  | 0   | DRAM multiplexed row and column address bus.                                                                                                                            |  |

| DBUS[15:0]        | 13:28                 | I/O | DRAM data bus.                                                                                                                                                          |  |

| RESET#            | 29                    | Ι   | System reset (active low).                                                                                                                                              |  |

| VSS               | 30, 50, 80, 100       | Ι   | Ground.                                                                                                                                                                 |  |

| NC                | 32:41, 43, 44         | _   | No Connect.                                                                                                                                                             |  |

| CPUCLK            | 42                    | Ι   | RISC and system clock input.<br>CPUCLK is used only if SEL_PLL[1:0] = 00.                                                                                               |  |

| AUX[7:0]          | 44:49, 54, 52,<br>53, | I/O | Auxiliary control pins (AUX0 and AUX1 are open collectors.)                                                                                                             |  |

| LD[7:0]           | 55:62                 | I/O | RISC interface data bus.                                                                                                                                                |  |

| LWR#              | 63                    | 0   | RISC interface write enable (active low).                                                                                                                               |  |

| LOE#              | 64                    | 0   | RISC interface output enable (active low).                                                                                                                              |  |

| LCS[3,1,0]#       | 65, 66, 67            | 0   | RISC interface chip select (active low).                                                                                                                                |  |

| LA[17:0]          | 68:79, 82:87          | 0   | RISC interface address bus.                                                                                                                                             |  |

| VPP               | 81                    | -   | Digital supply voltage for 5V.                                                                                                                                          |  |

| ACLK              | 88                    | I/O | Master clock for external audio DAC (8.192 MHz, 11.2896 MHz, 12.288 MHz, 16.9344 MHz, and 18.432 MHz)                                                                   |  |

| AOUT/             | 89                    | 0   | Dual-purpose pin. AOUT is the audio interface serial data output.                                                                                                       |  |

| SEL_PLL0          |                       | I   | Pins SEL_PLL[1:0] select phase-lock loop (PLL) clock frequency CPUCLK<br>for the ES3986:<br>00 = bypass PLL<br>01 = 54-MHz PLL<br>10 = 67.5-MHz PLL<br>11 = 81-MHz PLL. |  |

| ATCLK             | 90                    | I/O | Audio transmit bit clock.                                                                                                                                               |  |

| ATFS/<br>SEL_PLL1 | 91                    | 0   | Dual-purpose pin. ATFS is the audio interface transmit frame sync.                                                                                                      |  |

|                   |                       | I   | Pins SEL_PLL[1:0] select phase-lock loop clock frequency CPUCLK for the ES3986. (Refer to the SEL_PLL0 pin above for the settings.)                                     |  |

| DA9/DOE#          | 92                    | 0   | Dual-purpose pin: DRAM output enable (active low)/DRAM multiplexed row and column address bus.                                                                          |  |

| AIN               | 93                    | Ι   | Audio interface serial data input.                                                                                                                                      |  |

| ARCLK             | 94                    | Ι   | Audio receive bit clock.                                                                                                                                                |  |

| ARFS              | 95                    | Ι   | Audio interface receive frame sync.                                                                                                                                     |  |

| TDMCLK            | 96                    | Ι   | TDM interface serial clock.                                                                                                                                             |  |

| TDMDR             | 97                    | Ι   | TDM interface serial data receive.                                                                                                                                      |  |

| TDMFS             | 98                    | Ι   | TDM interface frame sync.                                                                                                                                               |  |

| CAS#              | 99                    | 0   | DRAM column address strobe bank 0 (active low).                                                                                                                         |  |

### **ORDERING INFORMATION**

| Part Number | Description             | Package      |

|-------------|-------------------------|--------------|

| ES3986F     | Digital-Audio Processor | 100-pin PQFP |

ESS Technology, Inc. 48401 Fremont Blvd. Fremont, CA 94538 Tel: (510) 492-1088 Fax: (510) 492-1898 No part of this publication may be reproduced, stored in a retrieval system, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without the prior written permission of ESS Technology, Inc.

ESS Technology, Inc. makes no representations or warranties regarding the content of this document.

All specifications are subject to change without prior notice.

ESS Technology, Inc. assumes no responsibility for any errors contained herein.

(P) U.S. patents pending.

Visba, SmartScale, SmartStream, and VideoDrive are trademarks of ESS Technology, Inc.

MPEG is the Moving Picture Experts Group of the ISO/ IEC. References to MPEG2 in this document refer to the ISO/IEC 13818-1.

All other trademarks are owned by their respective holders and are used for identification purposes only.