October 1987 Revised January 1999

## **CD4027BC**

# **Dual J-K Master/Slave Flip-Flop with Set and Reset**

## **General Description**

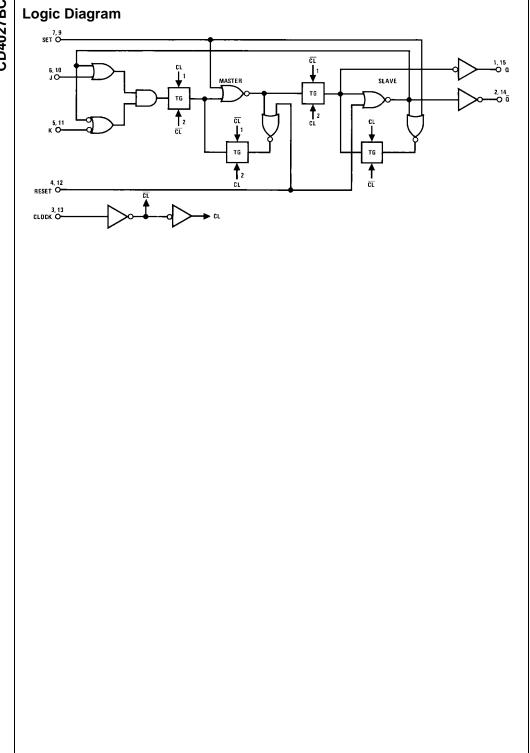

The CD4027BC dual J-K flip-flops are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. Each flip-flop has independent J, K, set, reset, and clock inputs and buffered Q and  $\overline{\mathbf{Q}}$  outputs. These flip-flops are edge sensitive to the clock input and change state on the positive-going transition of the clock pulses. Set or reset is independent of the clock and is accomplished by a high level on the respective input.

All inputs are protected against damage due to static discharge by diode clamps to  $V_{\mbox{\scriptsize DD}}$  and  $V_{\mbox{\scriptsize SS}}.$

#### **Features**

■ Wide supply voltage range: 3.0V to 15V  $\blacksquare$  High noise immunity: 0.45  $\rm V_{DD}$  (typ.)

■ Low power TTL compatibility: Fan out of 2 driving 74L or 1 driving 74LS

■ Low power: 50 nW (typ.)

■ Medium speed operation: 12 MHz (typ.) with 10V

# **Ordering Code:**

| Order Number | Package Number | Package Description                                                               |

|--------------|----------------|-----------------------------------------------------------------------------------|

| CD4027BCM    | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Body |

| CD4027BCN    | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide            |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code

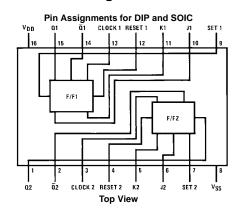

## **Connection Diagram**

#### **Truth Table**

| Inputs t <sub>n-1</sub><br>(Note 1) |   |     |     |     |     | Outputs t <sub>n</sub><br>(Note 2) |             |  |  |

|-------------------------------------|---|-----|-----|-----|-----|------------------------------------|-------------|--|--|

| CL<br>(Note 3)                      | J | K   | S   | R   | Q   | q                                  | Q           |  |  |

| ~                                   | ı | Χ   | 0   | 0   | 0   | ı                                  | 0           |  |  |

| ~                                   | Χ | 0   | 0   | 0   | - 1 | - 1                                | 0           |  |  |

|                                     | 0 | Χ   | 0   | 0   | 0   | 0                                  | 1           |  |  |

| ~                                   | Χ | - 1 | 0   | 0   | - 1 | 0                                  | 1           |  |  |

| ~                                   | Χ | Χ   | 0   | 0   | Χ   |                                    | (No Change) |  |  |

| Х                                   | Χ | Χ   | - 1 | 0   | Χ   | - 1                                | 0           |  |  |

| Х                                   | Χ | Χ   | 0   | - 1 | Χ   | 0                                  | 1           |  |  |

| Х                                   | Χ | Χ   | I   | I   | Χ   | - 1                                | 1           |  |  |

I = HIGH Level

O = LOW Level X = Don't Care

∠ = LOW-to-HIGH

~ = HIGH-to-LOW

Note 1: t<sub>n-1</sub> refers to the time interval prior to the positive clock pulse

Note 2: t<sub>n</sub> refers to the time intervals after the positive clock pulse

Note 3: Level Change

## **Absolute Maximum Ratings**(Note 4)

(Note 5)

DC Supply Voltage (V<sub>DD</sub>)  $-0.5 \text{ V}_{DC} \text{ to +18 V}_{DC}$  Input Voltage (V<sub>IN</sub>)  $-0.5 \text{V to V}_{DD} +0.5 \text{ V}_{DC}$  Storage Temperature Range (T<sub>S</sub>)  $-65^{\circ}\text{C to +150^{\circ}C}$

Power Dissipation (P<sub>D</sub>)

Dual-In-Line 700 mW Small Outline 500 mW

Lead Temperature (T<sub>L</sub>)

(Soldering, 10 seconds) 260°C

# Recommended Operating Conditions (Note 5)

DC Supply Voltage (V<sub>DD</sub>) \$3V\$ to 15  $V_{DC}$  Input Voltage (V<sub>IN</sub>) \$0V\$ to  $V_{DD}$   $V_{DC}$

Operating Temperature Range ( $T_A$ )  $-40^{\circ}$ C to  $+85^{\circ}$ C

Note 4: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Recommended Operating Conditions" and "Electrical Characteristics" provides conditions for actual device operation.

Note 5:  $V_{SS} = 0V$  unless otherwise specified.

## DC Electrical Characteristics (Note 6)

| Symbol          | Parameter                | Conditions                                     | -40°C |      | +25°C |                   |      | +85°C |      | Units |

|-----------------|--------------------------|------------------------------------------------|-------|------|-------|-------------------|------|-------|------|-------|

| Symbol          | Faranietei               | Conditions                                     | Min   | Max  | Min   | Тур               | Max  | Min   | Max  | Units |

| I <sub>DD</sub> | Quiescent Device Current | $V_{DD} = 5V$ , $V_{IN} = V_{DD}$ or $V_{SS}$  |       | 4    |       |                   | 4    |       | 30   | μΑ    |

|                 |                          | $V_{DD} = 10V$ , $V_{IN} = V_{DD}$ or $V_{SS}$ |       | 8    |       |                   | 8    |       | 60   | μΑ    |

|                 |                          | $V_{DD} = 15V$ , $V_{IN} = V_{DD}$ or $V_{SS}$ |       | 16   |       |                   | 16   |       | 120  | μΑ    |

| V <sub>OL</sub> | LOW Level                | I <sub>O</sub>   < 1 μA                        |       |      |       |                   |      |       |      |       |

|                 | Output Voltage           | $V_{DD} = 5V$                                  |       | 0.05 |       | 0                 | 0.05 |       | 0.05 | V     |

|                 |                          | $V_{DD} = 10V$                                 |       | 0.05 |       | 0                 | 0.05 |       | 0.05 | V     |

|                 |                          | $V_{DD} = 15V$                                 |       | 0.05 |       | 0                 | 0.05 |       | 0.05 | V     |

| V <sub>OH</sub> | HIGH Level               | I <sub>O</sub>   < 1 μA                        |       |      |       |                   |      |       |      |       |

|                 | Output Voltage           | $V_{DD} = 5V$                                  | 4.95  |      | 4.95  | 5                 |      | 4.95  |      | V     |

|                 |                          | $V_{DD} = 10V$                                 | 9.95  |      | 9.95  | 10                |      | 9.95  |      | V     |

|                 |                          | $V_{DD} = 15V$                                 | 14.95 |      | 14.95 | 15                |      | 14.95 |      | V     |

| V <sub>IL</sub> | LOW Level                | $V_{DD} = 5V$ , $V_{O} = 0.5V$ or 4.5V         |       | 1.5  |       |                   | 1.5  |       | 1.5  | V     |

|                 | Input Voltage            | $V_{DD} = 10V$ , $V_{O} = 1V$ or $9V$          |       | 3.0  |       |                   | 3.0  |       | 3.0  | V     |

|                 |                          | $V_{DD} = 15V$ , $V_{O} = 1.5V$ or $13.5V$     |       | 4.0  |       |                   | 4.0  |       | 4.0  | V     |

| V <sub>IH</sub> | HIGH Level               | $V_{DD} = 5V$ , $V_{O} = 0.5V$ or 4.5V         | 3.5   |      | 3.5   |                   |      | 3.5   |      | V     |

|                 | Input Voltage            | $V_{DD} = 10V, V_{O} = 1V \text{ or } 9V$      | 7.0   |      | 7.0   |                   |      | 7.0   |      | V     |

|                 |                          | $V_{DD} = 15V$ , $V_{O} = 1.5V$ or $13.5V$     | 11.0  |      | 11.0  |                   |      | 11.0  |      | V     |

| I <sub>OL</sub> | LOW Level Output         | $V_{DD} = 5V, V_{O} = 0.4V$                    | 0.52  |      | 0.44  | 0.88              |      | 0.36  |      | mA    |

|                 | Current (Note 7)         | $V_{DD} = 10V, \ V_{O} = 0.5V$                 | 1.3   |      | 1.1   | 2.25              |      | 0.9   |      | mA    |

|                 |                          | $V_{DD} = 15V, V_{O} = 1.5V$                   | 3.6   |      | 3.0   | 8.8               |      | 2.4   |      | mA    |

| I <sub>OH</sub> | HIGH Level Output        | $V_{DD} = 5V, V_{O} = 4.6V$                    | -0.52 |      | -0.44 | -0.88             |      | -0.36 |      | mA    |

|                 | Current (Note 7)         | $V_{DD} = 10V, \ V_{O} = 9.5V$                 | -1.3  |      | -1.1  | -2.25             |      | -0.9  |      | mA    |

|                 |                          | $V_{DD} = 15V, V_{O} = 13.5V$                  | -3.6  |      | -3.0  | -8.8              |      | -2.4  |      | mA    |

| I <sub>IN</sub> | Input Current            | $V_{DD} = 15V, V_{IN} = 0V$                    |       | -0.3 |       | -10 <sup>-5</sup> | -0.3 |       | -1.0 | μА    |

|                 |                          | $V_{DD} = 15V, V_{IN} = 15V$                   |       | 0.3  |       | 10 <sup>-5</sup>  | 0.3  |       | 1.0  | μΑ    |

Note 6: V<sub>SS</sub> = 0V unless otherwise specified.

Note 7:  $I_{\mbox{\scriptsize OH}}$  and  $I_{\mbox{\scriptsize OL}}$  are tested one output at a time.

# AC Electrical Characteristics (Note 8)

| Symbol                               | Parameter                   | Conditions            | Min | Тур  | Max                                 | Units |

|--------------------------------------|-----------------------------|-----------------------|-----|------|-------------------------------------|-------|

| t <sub>PHL</sub> or t <sub>PLH</sub> | Propagation Delay Time      | $V_{DD} = 5V$         |     | 200  | 400                                 | ns    |

|                                      | from Clock to Q or Q        | V <sub>DD</sub> = 10V |     | 80   | 160                                 | ns    |

|                                      |                             | V <sub>DD</sub> = 15V |     | 65   | 130                                 | ns    |

| t <sub>PHL</sub> or t <sub>PLH</sub> | Propagation Delay Time      | V <sub>DD</sub> = 5V  |     | 170  | 340                                 | ns    |

|                                      | from Set to Q or Reset to Q | V <sub>DD</sub> = 10V |     | 70   | 140                                 | ns    |

|                                      |                             | V <sub>DD</sub> = 15V |     | 55   | 110                                 | ns    |

| t <sub>PHL</sub> or t <sub>PLH</sub> | Propagation Delay Time      | V <sub>DD</sub> = 5V  |     | 110  | 220                                 | ns    |

|                                      | from Set to Q or            | V <sub>DD</sub> = 10V |     | 50   | 100                                 | ns    |

|                                      | Reset to Q                  | V <sub>DD</sub> = 15V |     | 40   | 80                                  | ns    |

| t <sub>S</sub>                       | Minimum Data Setup Time     | V <sub>DD</sub> = 5V  |     | 135  | 270                                 | ns    |

|                                      |                             | $V_{DD} = 10V$        |     | 55   | 110                                 | ns    |

|                                      |                             | V <sub>DD</sub> = 15V |     | 45   | 90                                  | ns    |

| t <sub>THL</sub> or t <sub>TLH</sub> | Transition Time             | V <sub>DD</sub> = 5V  |     | 100  | 200                                 | ns    |

|                                      |                             | V <sub>DD</sub> = 10V |     | 50   | 100                                 | ns    |

|                                      |                             | V <sub>DD</sub> = 15V |     | 40   | 80                                  | ns    |

| OL.                                  | Maximum Clock Frequency     | V <sub>DD</sub> = 5V  | 2.5 | 5    |                                     | MHz   |

|                                      | (Toggle Mode)               | V <sub>DD</sub> = 10V | 6.2 | 12.5 |                                     | MHz   |

|                                      |                             | V <sub>DD</sub> = 15V | 7.6 | 15.5 |                                     | MHz   |

| TOL TOL                              | Maximum Clock Rise          | V <sub>DD</sub> = 5V  | 15  |      |                                     | μs    |

|                                      | and Fall Time               | V <sub>DD</sub> = 10V | 10  |      |                                     | μs    |

|                                      |                             | V <sub>DD</sub> = 15V | 5   |      | 200<br>100<br>80<br>200<br>80<br>65 | μs    |

| t <sub>W</sub>                       | Minimum Clock Pulse         | V <sub>DD</sub> = 5V  |     | 100  | 200                                 | ns    |

|                                      | Width $(t_{WH} = t_{WL})$   | V <sub>DD</sub> = 10V |     | 40   | 80                                  | ns    |

|                                      |                             | V <sub>DD</sub> = 15V |     | 32   | 65                                  | ns    |

| t <sub>WH</sub>                      | Minimum Set and             | V <sub>DD</sub> = 5V  |     | 80   | 160                                 | ns    |

|                                      | Reset Pulse Width           | V <sub>DD</sub> = 10V |     | 30   | 60                                  | ns    |

|                                      |                             | V <sub>DD</sub> = 15V |     | 25   | 50                                  | ns    |

| C <sub>IN</sub>                      | Average Input Capacitance   | Any Input             |     | 5    | 7.5                                 | pF    |

| C <sub>PD</sub>                      | Power Dissipation Capacity  | Per Flip-Flop         |     | 35   |                                     | pF    |

|                                      |                             | (Note 9)              |     |      |                                     |       |

Note 8: AC Parameters are guaranteed by DC correlated testing.

Note 9: C<sub>PD</sub> determines the no load AC power consumption of any CMOS device. For complete explanation, see 74C Family Characteristics application note, AN-90.

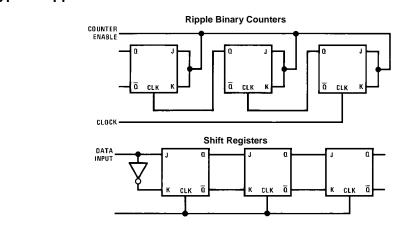

# **Typical Applications**

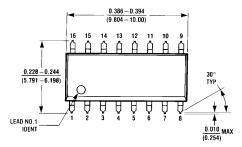

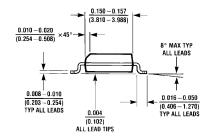

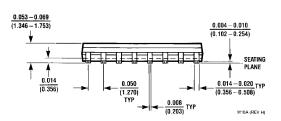

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Body Package Number M16A

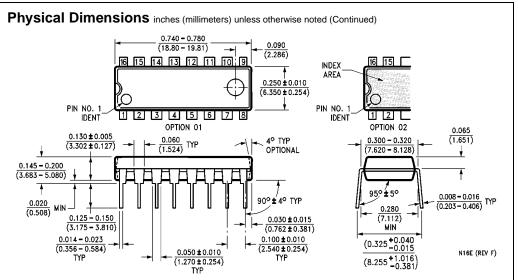

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com