# HGTD7N60C3, HGTD7N60C3S, HGTP7N60C3

January 1997

# 14A, 600V, UFS Series N-Channel IGBTs

### Features

- 14A, 600V at T<sub>C</sub> = 25<sup>o</sup>C

- 600V Switching SOA Capability

- Short Circuit Rating

- Low Conduction Loss

## Description

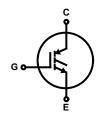

The HGTD7N60C3, HGTD7N60C3S and HGTP7N60C3 are MOS gated high voltage switching devices combining the best features of MOSFETs and bipolar transistors. These devices have the high input impedance of a MOSFET and the low on-state conduction loss of a bipolar transistor. The much lower on-state voltage drop varies only moderately between  $25^{\circ}$ C and  $150^{\circ}$ C.

The IGBT is ideal for many high voltage switching applications operating at moderate frequencies where low conduction losses are essential, such as: AC and DC motor controls, power supplies and drivers for solenoids, relays and contactors.

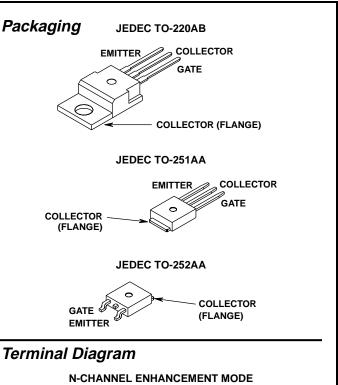

| PACKAGING AVAILABILITY                         |          |         |  |  |

|------------------------------------------------|----------|---------|--|--|

| PART NUMBER                                    | PACKAGE  | BRAND   |  |  |

| HGTD7N60C3                                     | TO-251AA | G7N60C  |  |  |

| HGTD7N60C3S                                    | TO-252AA | G7N60C  |  |  |

| HGTP7N60C3                                     | TO-220AB | G7N60C3 |  |  |

| NOTE: When ordering use the entire part number |          |         |  |  |

NOTE: When ordering, use the entire part number.

Add the suffix 9A to obtain the TO-252AA variant in tape and reel, i.e. HGTD7N60C3S9A.

Formerly Developmental Type TA49115.

Absolute Maximum Ratings  $T_C = 25^{\circ}C$ , Unless Otherwise Specified

HGTD7N60C3, HGTD7N60C3S

|                                                                                     | HGTP7N60C3  | UNITS             |

|-------------------------------------------------------------------------------------|-------------|-------------------|

| Collector-Emitter VoltageBV <sub>CES</sub>                                          | 600         | V                 |

| Collector Current Continuous                                                        |             |                   |

| At $T_{C} = 25^{\circ}C$ $I_{C25}$                                                  | 14          | А                 |

| At $T_{C} = 110^{\circ}C$ $I_{C110}$                                                | 7           | А                 |

| Collector Current Pulsed (Note 1)                                                   | 56          | А                 |

| Gate-Emitter Voltage ContinuousV <sub>GES</sub>                                     | ±20         | V                 |

| Gate-Emitter Voltage Pulsed                                                         | ±30         | V                 |

| Switching Safe Operating Area at T <sub>J</sub> = 150 <sup>o</sup> C, Figure 14SSOA | 40A at 480V |                   |

| Power Dissipation Total at $T_{C} = 25^{\circ}C$ $P_{D}$                            | 60          | W                 |

| Power Dissipation Derating $T_C > 25^{\circ}C$                                      | 0.48        | W/ <sup>o</sup> C |

| Reverse Voltage Avalanche Energy E <sub>ARV</sub>                                   | 100         | mJ                |

| Operating and Storage Junction Temperature Range                                    | -40 to 150  | oC                |

| Maximum Lead Temperature for SolderingTL                                            | 260         | oC                |

| Short Circuit Withstand Time (Note 2) at V <sub>GE</sub> = 15Vt <sub>SC</sub>       | 1           | μs                |

| Short Circuit Withstand Time (Note 2) at V <sub>GE</sub> = 10Vt <sub>SC</sub>       | 8           | μs                |

| NOTES:                                                                              |             |                   |

| 1 Papatitiva Pating: Pulsa width limited by maximum junction temporatura            |             |                   |

1. Repetitive Rating: Pulse width limited by maximum junction temperature.

2.  $V_{CE(PK)} = 360V, T_J = 125^{\circ}C, R_{GE} = 50\Omega$ .

| PARAMETER                            | SYMBOL               | TEST CONDITIONS                                                |                                     | MIN | ТҮР  | МАХ  | UNITS |

|--------------------------------------|----------------------|----------------------------------------------------------------|-------------------------------------|-----|------|------|-------|

| Collector-Emitter Breakdown Voltage  | BV <sub>CES</sub>    | $I_C = 250 \mu A, V_{GE} = 0 V$                                |                                     | 600 | -    | -    | V     |

| Emitter-Collector Breakdown Voltage  | BV <sub>ECS</sub>    | $I_{C} = 3mA, V_{GE} = 0V$                                     |                                     | 16  | 30   | -    | V     |

| Collector-Emitter Leakage Current    | ICES                 | $V_{CE} = BV_{CES}$                                            | T <sub>C</sub> = 25 <sup>o</sup> C  | -   | -    | 250  | μA    |

|                                      |                      | $V_{CE} = BV_{CES}$                                            | T <sub>C</sub> = 150 <sup>o</sup> C | -   | -    | 2.0  | mA    |

| Collector-Emitter Saturation Voltage | V <sub>CE(SAT)</sub> | $I_{\rm C} = I_{\rm C110},$                                    | T <sub>C</sub> = 25 <sup>o</sup> C  | -   | 1.6  | 2.0  | V     |

|                                      |                      | V <sub>GE</sub> = 15V                                          | T <sub>C</sub> = 150 <sup>o</sup> C | -   | 1.9  | 2.4  | V     |

| Gate-Emitter Threshold Voltage       | V <sub>GE(TH)</sub>  | $I_{C} = 250\mu A,$<br>$V_{CE} = V_{GE}$                       | T <sub>C</sub> = 25 <sup>o</sup> C  | 3.0 | 5.0  | 6.0  | V     |

| Gate-Emitter Leakage Current         | I <sub>GES</sub>     | V <sub>GE</sub> = ±25V                                         |                                     | -   | -    | ±250 | nA    |

| Switching SOA                        | SSOA                 | $T_J = 150^{\circ}C$ $R_G = 50\Omega$ $V_{GE} = 15V$ $L = 1mH$ | V <sub>CE(PK)</sub> = 480V          | 40  | -    | -    | A     |

|                                      |                      |                                                                | V <sub>CE(PK)</sub> = 600V          | 6   | -    | -    | A     |

| Gate-Emitter Plateau Voltage         | V <sub>GEP</sub>     | $I_{C} = I_{C110}, V_{CE} = 0.5 \text{ BV}_{CES}$              |                                     | -   | 8    | -    | V     |

| On-State Gate Charge                 | Q <sub>G(ON)</sub>   | $I_{C} = I_{C110},$<br>$V_{CE} = 0.5 \text{ BV}_{CES}$         | V <sub>GE</sub> = 15V               | -   | 23   | 30   | nC    |

|                                      |                      |                                                                | V <sub>GE</sub> = 20V               | -   | 30   | 38   | nC    |

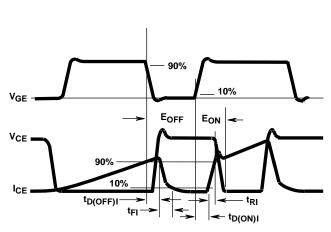

| Current Turn-On Delay Time           | <sup>t</sup> D(ON)I  | T <sub>J</sub> = 150 <sup>o</sup> C                            |                                     | -   | 8.5  | -    | ns    |

| Current Rise Time                    | t <sub>RI</sub>      | $I_{CE} = I_{C110}$<br>$V_{CE(PK)} = 0.8 \text{ BV}_{CES}$     |                                     | -   | 11.5 | -    | ns    |

| Current Turn-Off Delay Time          | <sup>t</sup> D(OFF)I | V <sub>GE</sub> = 15V<br>R <sub>G</sub> = 50Ω                  | -                                   | 350 | 400  | ns   |       |

| Current Fall Time                    | t <sub>FI</sub>      | L = 1.0mH                                                      | -                                   | 140 | 275  | ns   |       |

| Turn-On Energy                       | E <sub>ON</sub>      |                                                                | -                                   | 165 | -    | μJ   |       |

| Turn-Off Energy (Note 3)             | E <sub>OFF</sub>     |                                                                | -                                   | 600 | -    | μJ   |       |

| Thermal Resistance                   | R <sub>θJC</sub>     |                                                                |                                     | -   | -    | 2.1  | °C/W  |

### **Electrical Specifications** T<sub>C</sub> = 25<sup>o</sup>C, Unless Otherwise Specified

NOTE:

3. Turn-Off Energy Loss (E<sub>OFF</sub>) is defined as the integral of the instantaneous power loss starting at the trailing edge of the input pulse and ending at the point where the collector current equals zero (I<sub>CE</sub> = 0A). The HGTD7N60C3, HGTD7N60C3S and HGTP7N60C3 were tested per JEDEC standard No. 24-1 Method for Measurement of Power Device Turn-Off Switching Loss. This test method produces the true total Turn-Off Energy Loss. Turn-On losses include diode losses.

#### HARRIS SEMICONDUCTOR IGBT PRODUCT IS COVERED BY ONE OR MORE OF THE FOLLOWING U.S. PATENTS:

| 4,364,073 | 4,417,385 | 4,430,792 | 4,443,931 | 4,466,176 | 4,516,143 | 4,532,534 | 4,567,641 |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 4,587,713 | 4,598,461 | 4,605,948 | 4,618,872 | 4,620,211 | 4,631,564 | 4,639,754 | 4,639,762 |

| 4,641,162 | 4,644,637 | 4,682,195 | 4,684,413 | 4,694,313 | 4,717,679 | 4,743,952 | 4,783,690 |

| 4,794,432 | 4,801,986 | 4,803,533 | 4,809,045 | 4,809,047 | 4,810,665 | 4,823,176 | 4,837,606 |

| 4,860,080 | 4,883,767 | 4,888,627 | 4,890,143 | 4,901,127 | 4,904,609 | 4,933,740 | 4,963,951 |

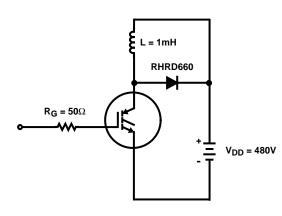

### Test Circuit and Waveform

FIGURE 18. INDUCTIVE SWITCHING TEST CIRCUIT

FIGURE 19. SWITCHING TEST WAVEFORMS

# Handling Precautions for IGBTs

Insulated Gate Bipolar Transistors are susceptible to gateinsulation damage by the electrostatic discharge of energy through the devices. When handling these devices, care should be exercised to assure that the static charge built in the handler's body capacitance is not discharged through the device. With proper handling and application procedures, however, IGBTs are currently being extensively used in production by numerous equipment manufacturers in military, industrial and consumer applications, with virtually no damage problems due to electrostatic discharge. IGBTs can be handled safely if the following basic precautions are taken:

- Prior to assembly into a circuit, all leads should be kept shorted together either by the use of metal shorting springs or by the insertion into conductive material such as "ECCOSORBD™ LD26" or equivalent.

- 2. When devices are removed by hand from their carriers, the hand being used should be grounded by any suitable means - for example, with a metallic wristband.

- 3. Tips of soldering irons should be grounded.

- 4. Devices should never be inserted into or removed from circuits with power on.

- 5. Gate Voltage Rating Never exceed the gate-voltage rating of  $V_{GEM}$ . Exceeding the rated  $V_{GE}$  can result in permanent damage to the oxide layer in the gate region.

- 6. Gate Termination The gates of these devices are essentially capacitors. Circuits that leave the gate opencircuited or floating should be avoided. These conditions can result in turn-on of the device due to voltage buildup on the input capacitor due to leakage currents or pickup.

- Gate Protection These devices do not have an internal monolithic Zener diode from gate to emitter. If gate protection is required an external Zener is recommended.

ECCOSORBD<sup>™</sup> is a Trademark of Emerson and Cumming, Inc.

# **Operating Frequency Information**

#### **Operating Frequency Information for a Typical Device**

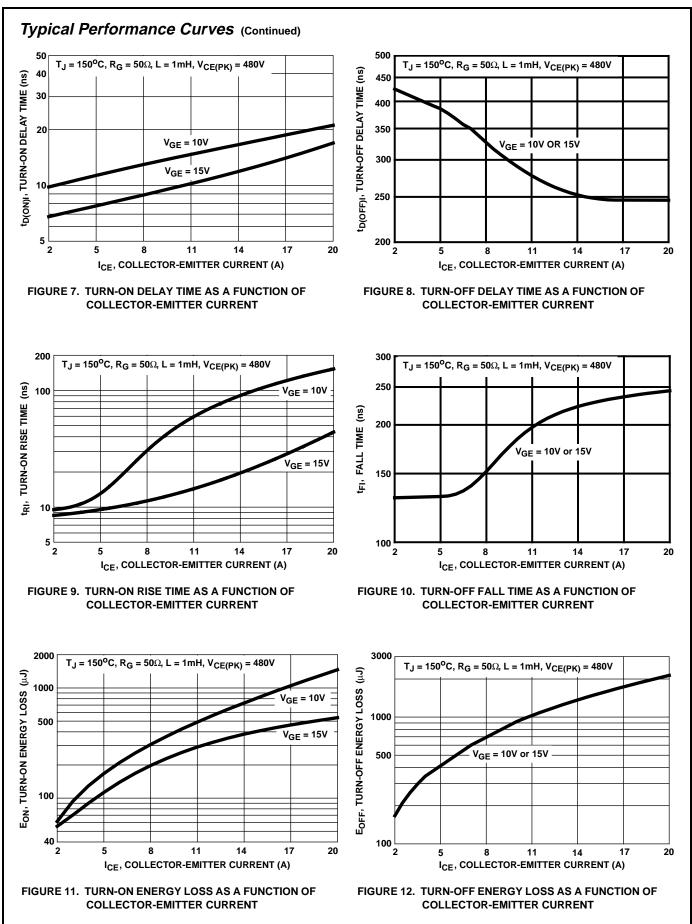

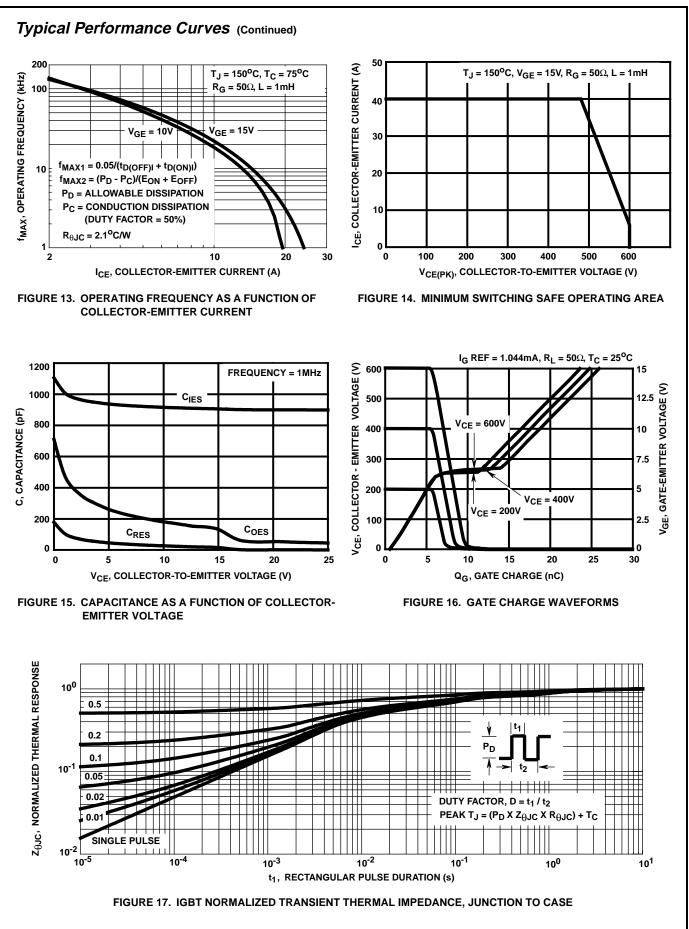

Figure 13 is presented as a guide for estimating device performance for a specific application. Other typical frequency vs collector current ( $I_{CE}$ ) plots are possible using the information shown for a typical unit in Figures 4, 7, 8, 11 and 12. The operating frequency plot (Figure 13) of a typical device shows  $f_{MAX1}$  or  $f_{MAX2}$  whichever is smaller at each point. The information is based on measurements of a typical device and is bounded by the maximum rated junction temperature.

$f_{MAX1}$  is defined by  $f_{MAX1} = 0.05/(t_{D(OFF)I} + t_{D(ON)I})$ . Deadtime (the denominator) has been arbitrarily held to 10% of the on- state time for a 50% duty factor. Other definitions are possible.  $t_{D(OFF)I}$  and  $t_{D(ON)I}$  are defined in Figure 19.

Device turn-off delay can establish an additional frequency limiting condition for an application other than  $T_{JMAX}$ .  $t_{D(OFF)I}$  is important when controlling output ripple under a lightly loaded condition.

$f_{MAX2}$  is defined by  $f_{MAX2} = (P_D - P_C)/(E_{OFF} + E_{ON})$ . The allowable dissipation  $(P_D)$  is defined by  $P_D = (T_{JMAX} - T_C)/R_{\theta JC}$ . The sum of device switching and conduction losses must not exceed  $P_D$ . A 50% duty factor was used (Figure 13) and the conduction losses  $(P_C)$  are approximated by  $P_C = (V_{CE} \times I_{CE})/2$ .  $E_{ON}$  and  $E_{OFF}$  are defined in the switching waveforms shown in Figure 19.  $E_{ON}$  is the integral of the instantaneous power loss ( $I_{CE} \times V_{CE}$ ) during turn-on and  $E_{OFF}$  is the integral of the instantaneous power loss ( $I_{CE} \times V_{CE}$ ) during turn-off. All tail losses are included in the calculation for  $E_{OFF}$ ; i.e. the collector current equals zero ( $I_{CE} = 0$ ).