# 74LCXH162373 Low Voltage 16-Bit Transparent Latch with Bushold and 26 $\Omega$ Series Resistor Outputs

#### **General Description**

#### **Features**

- 5V tolerant control inputs and outputs

- 2.3V–3.6V V<sub>CC</sub> specifications provided

- Equivalent 26Ω series resistors on outputs

- Bushold on inputs eliminates the need for external pull-up/pull-down resistors

- 6.2 ns t<sub>PD</sub> max (V<sub>CC</sub> = 3.3V), 20 μA I<sub>CC</sub> max

- Power down high impedance inputs and outputs

- $\blacksquare$  ±12 mA output drive (V<sub>CC</sub> = 3.0V)

- Implements patented noise/EMI reduction circuitry

- Latch-up performance exceeds 500 mA

- ESD performance: Human body model > 2000V

- Machine model > 200V

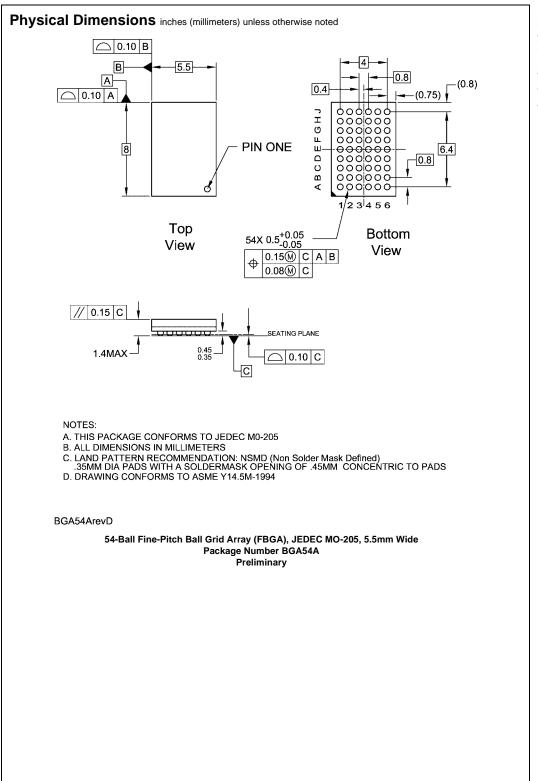

- Also packaged in plastic Fine-Pitch Ball Grid Array (FBGA) (Preliminary)

#### **Ordering Code:**

| <b>FAIRCH</b>                                                                                                                                                                                                                                                                                                                                                                                                                                              | CTORIM                                                                                                                                                                                                                                                                                                                                                                                                        | February 2001<br>Revised March 2002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ge 16-Bi                                                                                                                                                                                                                                                                                                                                                                                                      | t Transparent Latch<br>26 $\Omega$ Series Resistor Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| General Des<br>The LCXH162373 c<br>with 3-STATE output<br>applications. The de<br>appear transparent to<br>is HIGH. When LE is<br>time is latched. Data<br>Enable (OE) is LOW<br>a high impedance sta<br>The LCXH162373 is<br>3.3V) V <sub>CC</sub> application<br>signal environment.<br>output overshoot and<br>The LCXH162373 is<br>technology to achieve<br>ing CMOS low powe<br>The LCXH162373 d<br>cuitry, eliminating the<br>hold unused or floatil | ontains sixteen n<br>its and is intender<br>vice is byte contro-<br>to the data when the<br>s LOW, the data the<br>appears on the b<br>When $\overline{OE}$ is HIG<br>ate.<br>Is designed for lo<br>as with capability of<br>The 26 $\Omega$ series re-<br>d undershoot.<br>Is fabricated with a<br>e high speed oper-<br>r dissipation.<br>ata inputs include<br>a need for externa-<br>ing data inputs at a | ad for bus oriented<br>rolled. The flip-flops<br>e Latch Enable (LE)<br>hat meets the setup<br>us when the Output $2.3V-3.6V V_{CC}$ specifications provided $Equivalent 26\Omega$ series resistors on outputsBushold on inputs eliminates the need for external<br>pull-up/pull-down resistors $Bushold on inputs eliminates the need for externalpull-up/pull-down resistorsBushold orfinterfacing to a 5Vseistor helps reduceBushold orLatch-up performance exceeds 500 mABushold orLatch-up performance:Human body model > 200VBushold cir-I pull-up resistors toBushold cir-I$ |

| Order Number                                                                                                                                                                                                                                                                                                                                                                                                                                               | Package<br>Number                                                                                                                                                                                                                                                                                                                                                                                             | Package Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 74LCXH162373GX<br>(Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                 | BGA54A<br>(Preliminary)                                                                                                                                                                                                                                                                                                                                                                                       | 54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide<br>[TAPE and REEL]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

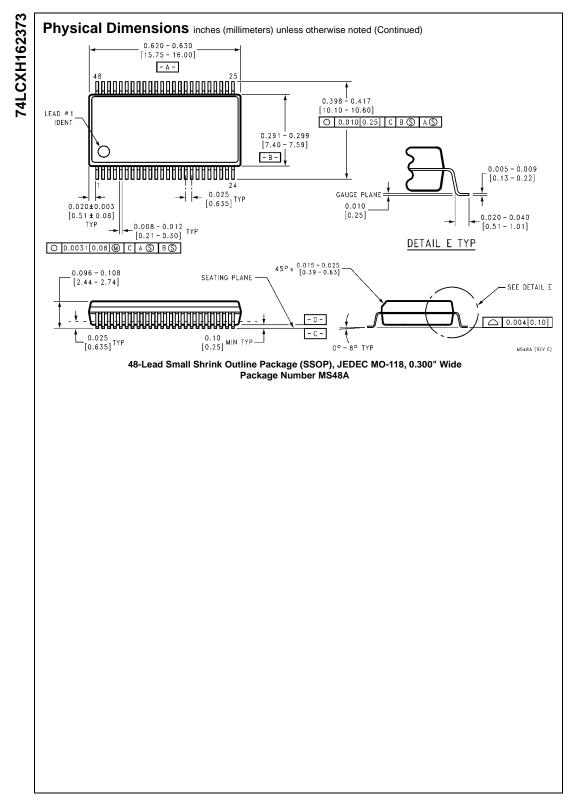

| 74LCXH162373MEA                                                                                                                                                                                                                                                                                                                                                                                                                                            | MS48A                                                                                                                                                                                                                                                                                                                                                                                                         | 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide<br>[[RAIL]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 74LCXH162373MEX                                                                                                                                                                                                                                                                                                                                                                                                                                            | MS48A                                                                                                                                                                                                                                                                                                                                                                                                         | 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide<br>[TAPE and REEL]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

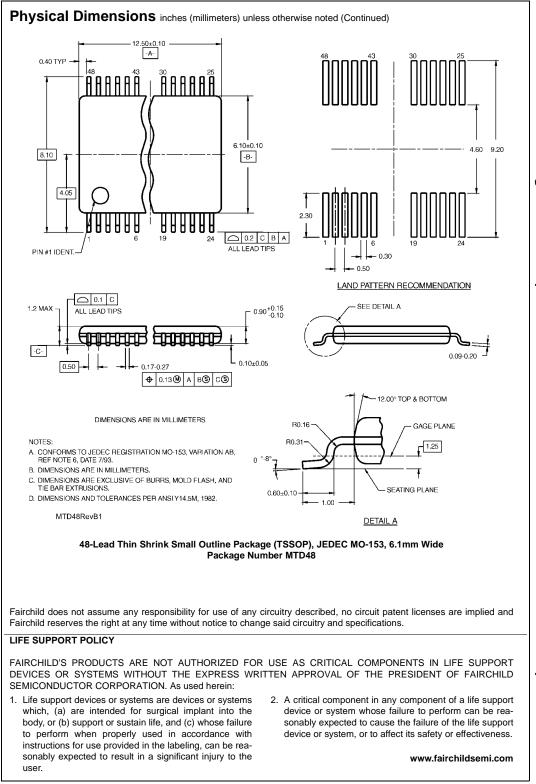

| 74LCXH162373MTD                                                                                                                                                                                                                                                                                                                                                                                                                                            | MTD48                                                                                                                                                                                                                                                                                                                                                                                                         | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide [RAIL]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 74LCXH162373MTX                                                                                                                                                                                                                                                                                                                                                                                                                                            | MTD48                                                                                                                                                                                                                                                                                                                                                                                                         | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide<br>[TAPE and REEL]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Note 1: BGA package ava                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                               | only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

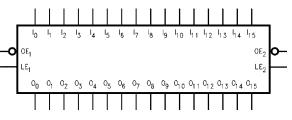

| Logic Symbo                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                               | II I2 I3 I4 I5 I6 I7 I8 I9 I10 I11 I12 I13 I14 I15<br>UE2<br>LE2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## Logic Symbol

| Connection D                                                      | Diagrams                                                               |                                                                                  |

|-------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Pin Assignn                                                       | nent for SSOP a                                                        | nd TSSOP                                                                         |

| 00<br>00<br>01                                                    | 1 48<br>2 47<br>3 46                                                   | — LE <sub>1</sub><br>— I <sub>0</sub><br>— I <sub>1</sub>                        |

| 01<br>GND —<br>0 <sub>2</sub> —<br>0 <sub>3</sub> —               | 4 45<br>5 44<br>6 43                                                   |                                                                                  |

| v <sub>cc</sub> —<br>o <sub>4</sub> —<br>o <sub>5</sub> —         | 7 42<br>8 41<br>9 40                                                   | – v <sub>cc</sub><br>– ' <sub>4</sub><br>– ' <sub>5</sub>                        |

| gnd —<br>0 <sub>5</sub> —<br>0 <sub>7</sub> —<br>0 <sub>8</sub> — | 10 39<br>11 38<br>12 37<br>13 36                                       | — GND<br>— I <sub>6</sub><br>— I <sub>7</sub><br>— I <sub>8</sub>                |

| 0 <sub>9</sub> —<br>gnd —<br>0 <sub>10</sub> —                    | 14 35   15 34   16 33                                                  | — I <sub>9</sub><br>— GND<br>— I <sub>10</sub>                                   |

| 0 <sub>11</sub>                                                   | 17 32   18 31   19 30   20 29                                          | — I <sub>11</sub><br>— V <sub>CC</sub><br>— I <sub>12</sub><br>— I <sub>13</sub> |

| GND                                                               | 21 28<br>22 27<br>23 26                                                | — GND<br>— I <sub>14</sub><br>— I <sub>15</sub>                                  |

| ਹĒ₂ —<br>Pin As                                                   | 24 25<br>signment for F                                                |                                                                                  |

| ЈН G F E D C B A                                                  | $\begin{array}{c}1&2&3&4&5\\0&0&0&0&0\\0&0&0&0&0\\0&0&0&0&0\\0&0&0&0&$ | ¢<br>000000000                                                                   |

| (                                                                 | Top Thru View)                                                         |                                                                                  |

|                                                                   |                                                                        |                                                                                  |

|                                                                   |                                                                        |                                                                                  |

### **Pin Descriptions**

| Pin Names                       | Description                      |

|---------------------------------|----------------------------------|

| <del>OE</del> n                 | Output Enable Input (Active LOW) |

| LEn                             | Latch Enable Input               |

| I <sub>0</sub> —I <sub>15</sub> | Inputs (Bushold)                 |

| O <sub>0</sub> -O <sub>15</sub> | Outputs (Bushold)                |

| NC                              | No Connect                       |

### **FBGA Pin Assignments**

|   | 1               | 2               | 3               | 4               | 5               | 6               |

|---|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Α | O <sub>0</sub>  | NC              | OE <sub>1</sub> | LE <sub>1</sub> | NC              | I <sub>0</sub>  |

| В | 0 <sub>2</sub>  | 0 <sub>1</sub>  | NC              | NC              | I <sub>1</sub>  | l <sub>2</sub>  |

| С | O <sub>4</sub>  | O <sub>3</sub>  | V <sub>CC</sub> | V <sub>CC</sub> | I <sub>3</sub>  | I <sub>4</sub>  |

| D | O <sub>6</sub>  | O <sub>5</sub>  | GND             | GND             | I <sub>5</sub>  | I <sub>6</sub>  |

| E | 0 <sub>8</sub>  | 0 <sub>7</sub>  | GND             | GND             | ۱ <sub>7</sub>  | I <sub>8</sub>  |

| F | O <sub>10</sub> | O <sub>9</sub>  | GND             | GND             | l <sub>9</sub>  | I <sub>10</sub> |

| G | O <sub>12</sub> | O <sub>11</sub> | V <sub>CC</sub> | V <sub>CC</sub> | I <sub>11</sub> | I <sub>12</sub> |

| н | 0 <sub>14</sub> | 0 <sub>13</sub> | NC              | NC              | I <sub>13</sub> | I <sub>14</sub> |

| J | O <sub>15</sub> | NC              | OE <sub>2</sub> | $LE_2$          | NC              | I <sub>15</sub> |

#### **Truth Tables**

|                 | Inputs          |                                 | Outputs                         |

|-----------------|-----------------|---------------------------------|---------------------------------|

| LE <sub>1</sub> | OE <sub>1</sub> | I <sub>0</sub> —I <sub>7</sub>  | 0 <sub>0</sub> –0 <sub>7</sub>  |

| Х               | Н               | Х                               | Z                               |

| н               | L               | L                               | L                               |

| н               | L               | Н                               | н                               |

| L               | L               | Х                               | O <sub>0</sub>                  |

| Inputs          |                 |                                 | Outputs                         |

| LE <sub>2</sub> | 0E2             | I <sub>8</sub> —I <sub>15</sub> | 0 <sub>8</sub> –0 <sub>15</sub> |

| Х               | Н               | Х                               | Z                               |

| Н               | L               | L                               | L                               |

| н               | L               | н                               | н                               |

|                 |                 | х                               | O <sub>0</sub>                  |

#### **Functional Description**

The LCXH162373 contains sixteen D-type latches with 3-STATE standard outputs. The device is byte controlled with each byte functioning identically, but independent of the other. Control pins can be shorted together to obtain full 16-bit operation. The following description applies to each byte. When the Latch Enable (LE<sub>n</sub>) input is HIGH, data on the I<sub>n</sub> enters the latches. In this condition the latches are transparent, i.e. a latch output will change state each time

its I input changes. When LE<sub>n</sub> is LOW, the latches store information that was present on the I inputs a setup time preceding the HIGH-to-LOW transition of LE<sub>n</sub>. The 3-STATE standard outputs are controlled by the Output Enable  $(\overline{OE}_n)$  input. When  $\overline{OE}_n$  is LOW, the standard outputs are in the 2-state mode. When  $\overline{OE}_n$  is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.

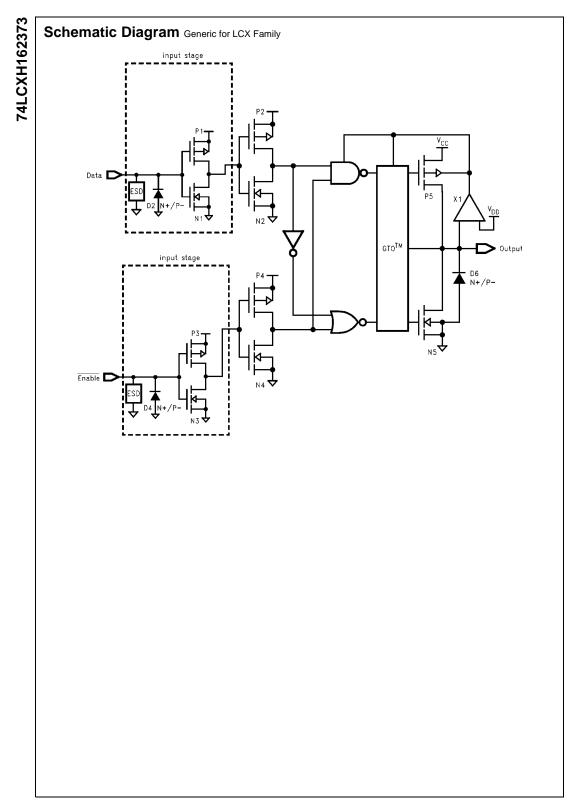

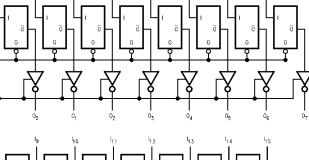

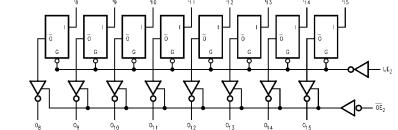

#### **Logic Diagrams**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

#### Absolute Maximum Ratings(Note 2)

| Symbol           | Parameter                                         | Value                    | Conditions                           | Units |

|------------------|---------------------------------------------------|--------------------------|--------------------------------------|-------|

| V <sub>CC</sub>  | Supply Voltage                                    | -0.5 to +7.0             |                                      | V     |

| VI               | DC Input Voltage I <sub>0</sub> - I <sub>15</sub> | $-0.5$ to $V_{CC} + 0.5$ |                                      | V     |

|                  | OE <sub>n</sub> , LE <sub>n</sub>                 | -0.5V to 7.0V            |                                      | v     |

| Vo               | DC Output Voltage                                 | -0.5 to +7.0             | Output in 3-STATE                    | V     |

|                  |                                                   | $-0.5$ to $V_{CC} + 0.5$ | Output in HIGH or LOW State (Note 3) |       |

| I <sub>IK</sub>  | DC Input Diode Current                            | -50                      | V <sub>I</sub> < GND                 | mA    |

| I <sub>OK</sub>  | DC Output Diode Current                           | -50                      | V <sub>O</sub> < GND                 | mA    |

|                  |                                                   | +50                      | V <sub>O</sub> > V <sub>CC</sub>     | mA    |

| l <sub>o</sub>   | DC Output Source/Sink Current                     | ±50                      |                                      | mA    |

| I <sub>CC</sub>  | DC Supply Current per Supply Pin                  | ±100                     |                                      | mA    |

| I <sub>GND</sub> | DC Ground Current per Ground Pin                  | ±100                     |                                      | mA    |

| T <sub>STG</sub> | Storage Temperature                               | -65 to +150              |                                      | °C    |

## Recommended Operating Conditions (Note 4)

| Symbol                           | Parameter                                                            | Min                                              | Max | Units           |      |

|----------------------------------|----------------------------------------------------------------------|--------------------------------------------------|-----|-----------------|------|

| V <sub>CC</sub>                  | Supply Voltage                                                       | Operating                                        | 2.0 | 3.6             | V    |

|                                  |                                                                      | Data Retention                                   | 1.5 | 3.6             | v    |

| VI                               | Input Voltage                                                        |                                                  | 0   | V <sub>CC</sub> | V    |

| Vo                               | Output Voltage                                                       | HIGH or LOW State                                | 0   | V <sub>CC</sub> | V    |

|                                  |                                                                      | 3-STATE                                          | 0   | 5.5             | v    |

| I <sub>OH</sub> /I <sub>OL</sub> | Output Current                                                       | $V_{CC} = 3.0V - 3.6V$                           |     | ±12             |      |

|                                  |                                                                      | $V_{CC} = 2.7V - 3.0V$<br>$V_{CC} = 2.3V - 2.7V$ |     | ±8              | mA   |

|                                  |                                                                      | $V_{CC}=2.3V-2.7V$                               |     | ±4              |      |

| T <sub>A</sub>                   | Free-Air Operating Temperature                                       |                                                  | -40 | 85              | °C   |

| $\Delta t / \Delta V$            | Input Edge Rate, V <sub>IN</sub> = 0.8V–2.0V, V <sub>CC</sub> = 3.0V |                                                  | 0   | 10              | ns/V |

Note 2: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the Absolute Maximum Ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 3:  $\mathrm{I}_{\mathrm{O}}$  Absolute Maximum Rating must be observed.

Note 4: Floating or unused control inputs must be HIGH or LOW.

## **DC Electrical Characteristics**

| Symbol          | Parameter                 | Conditions                | V <sub>cc</sub> | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      | Units |

|-----------------|---------------------------|---------------------------|-----------------|-----------------------------------------------|------|-------|

| Symbol          | Farameter                 | conditions                | (V)             | Min                                           | Max  | onits |

| V <sub>IH</sub> | HIGH Level Input Voltage  |                           | 2.3 – 2.7       | 1.7                                           |      | V     |

|                 |                           |                           | 2.7 - 3.6       | 2.0                                           |      | V     |

| VIL             | LOW Level Input Voltage   |                           | 2.3 – 2.7       |                                               | 0.7  | V     |

|                 |                           |                           | 2.7 - 3.6       |                                               | 0.8  | v     |

| V <sub>OH</sub> | HIGH Level Output Voltage | I <sub>OH</sub> = -100 μA | 2.3 - 3.6       | V <sub>CC</sub> - 0.2                         |      |       |

|                 |                           | $I_{OH} = -4 \text{ mA}$  | 2.3             | 1.8                                           |      |       |

|                 |                           | $I_{OH} = -4 \text{ mA}$  | 2.7             | 2.2                                           |      | V     |

|                 |                           | $I_{OH} = -6 \text{ mA}$  | 3.0             | 2.4                                           |      |       |

|                 |                           | $I_{OH} = -8 \text{ mA}$  | 2.7             | 2.0                                           |      |       |

|                 |                           | $I_{OH} = -12 \text{ mA}$ | 3.0             | 2.0                                           |      |       |

| V <sub>OL</sub> | LOW Level Output Voltage  | I <sub>OL</sub> = 100 μA  | 2.3 - 3.6       |                                               | 0.2  |       |

|                 |                           | I <sub>OL</sub> = 4 mA    | 2.3             |                                               | 0.6  |       |

|                 |                           | $I_{OL} = 4 \text{ mA}$   | 2.7             |                                               | 0.4  | v     |

|                 |                           | I <sub>OL</sub> = 6 mA    | 3.0             |                                               | 0.55 | v     |

|                 |                           | I <sub>OL</sub> = 8 mA    | 2.7             |                                               | 0.6  |       |

|                 |                           | I <sub>OL</sub> = 12 mA   | 3.0             |                                               | 0.8  |       |

| կ               | Input Leakage Current     | $V_I = V_{CC}$ or GND     | 2.3 - 3.6       | 1                                             | ±5.0 | μΑ    |

| Symbol               | Parameter                             | Conditions                       | V <sub>cc</sub> | T <sub>A</sub> = -40° | C to +85°C | Units |

|----------------------|---------------------------------------|----------------------------------|-----------------|-----------------------|------------|-------|

| Symbol               | Faraneter                             | conditions                       | (V)             | Min                   | Max        | onits |

| I <sub>I(HOLD)</sub> | Bushold Input Minimum                 | $V_{IN} = 0.7V$                  | 2.3             | 45                    |            |       |

|                      | Drive Hold Current                    | V <sub>IN</sub> = 1.7V           | 3.0             | -45                   |            | μA    |

|                      |                                       | $V_{IN} = 0.8V$                  |                 | 75                    |            |       |

|                      |                                       | $V_{IN} = 2.0V$                  | 3.0             | -75                   |            |       |

| I <sub>I(OD)</sub>   | Bushold Input Over-Drive              | (Note 6)                         | 2.7             | 300                   |            |       |

|                      | Current to Change State               | (Note 7)                         | 2.1             | -300                  |            |       |

|                      |                                       | (Note 6)                         | 3.6             | 450                   |            | μA    |

|                      |                                       | (Note 7)                         | 5.0             | -450                  |            |       |

| I <sub>OZ</sub>      | 3-STATE Output Leakage                | $0 \le V_O \le 5.5V$             | 2.3 - 3.6       |                       | ±5.0       |       |

|                      |                                       | $V_I = V_{IH}$ or $V_{IL}$       | 2.3 - 3.0       |                       | ±3.0       | μA    |

| I <sub>OFF</sub>     | Power-Off Leakage Current             | V <sub>O</sub> = V <sub>CC</sub> | 0               |                       | 10         | μA    |

| I <sub>CC</sub>      | Quiescent Supply Current              | $V_I = V_{CC}$ or GND            | 2.3 - 3.6       |                       | 20         |       |

|                      |                                       | $3.6V \le V_O \le 5.5V$ (Note 5) | 2.3 - 3.6       |                       | ±20        | μA    |

| $\Delta I_{CC}$      | Increase in I <sub>CC</sub> per Input | $V_{IH} = V_{CC} - 0.6V$         | 2.3 - 3.6       |                       | 500        | μA    |

Note 5: Outputs disabled or 3-STATE only.

Note 6: An external driver must source at least the specified current to switch from LOW-to-HIGH.

Note 7: An external driver must sink at least the specified current to switch from HIGH-to-LOW.

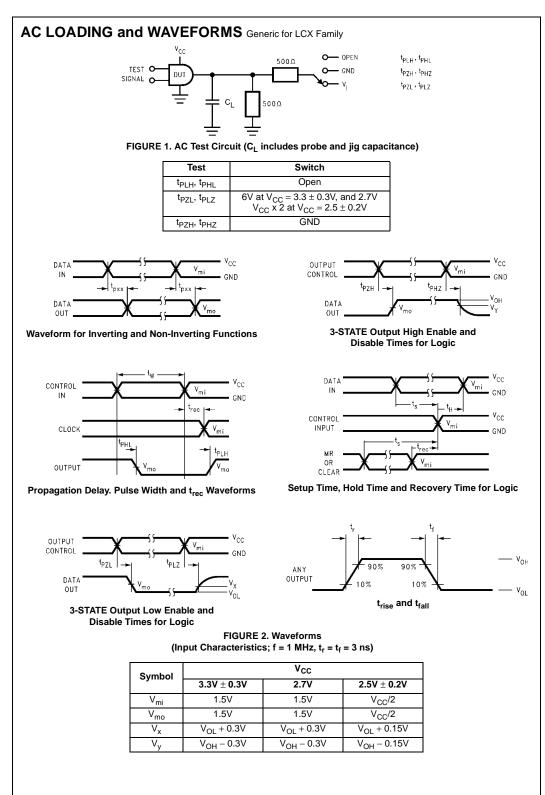

### **AC Electrical Characteristics**

|                   |                                  |                      | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ , $R_L = 500\Omega$ |                   |                                                  |     |               |       |  |

|-------------------|----------------------------------|----------------------|------------------------------------------------------------|-------------------|--------------------------------------------------|-----|---------------|-------|--|

| Symbol            | Parameter                        | $V_{CC}=3.3V\pm0.3V$ |                                                            | V <sub>CC</sub> : | V <sub>CC</sub> = 2.7V<br>C <sub>L</sub> = 50 pF |     | $5V \pm 0.2V$ | Units |  |

|                   | Farameter                        | C <sub>L</sub> =     | C <sub>L</sub> = 50 pF                                     |                   |                                                  |     | 30 pF         | Units |  |

|                   |                                  | Min                  | Max                                                        | Min               | Max                                              | Min | Max           |       |  |

| t <sub>PHL</sub>  | Propagation Delay                | 1.5                  | 6.2                                                        | 1.5               | 6.7                                              | 1.5 | 7.4           | ns    |  |

| t <sub>PLH</sub>  | I <sub>n</sub> to O <sub>n</sub> | 1.5                  | 6.2                                                        | 1.5               | 6.7                                              | 1.5 | 7.4           | ns    |  |

| t <sub>PHL</sub>  | Propagation Delay                | 1.5                  | 6.3                                                        | 1.5               | 7.2                                              | 1.5 | 7.6           | ns    |  |

| t <sub>PLH</sub>  | LE to O <sub>n</sub>             | 1.5                  | 6.3                                                        | 1.5               | 7.2                                              | 1.5 | 7.6           | 115   |  |

| t <sub>PZL</sub>  | Output Enable Time               | 1.5                  | 6.9                                                        | 1.5               | 7.3                                              | 1.5 | 9.0           | ne    |  |

| t <sub>PZH</sub>  |                                  | 1.5                  | 6.9                                                        | 1.5               | 7.3                                              | 1.5 | 9.0           | ns    |  |

| t <sub>PLZ</sub>  | Output Disable Time              | 1.5                  | 6.0                                                        | 1.5               | 6.3                                              | 1.5 | 7.2           | 20    |  |

| t <sub>PHZ</sub>  |                                  | 1.5                  | 6.0                                                        | 1.5               | 6.3                                              | 1.5 | 7.2           | ns    |  |

| ts                | Setup Time, In to LE             | 2.5                  |                                                            | 2.5               |                                                  | 3.0 |               | ns    |  |

| t <sub>H</sub>    | Hold Time, I <sub>n</sub> to LE  | 1.5                  |                                                            | 1.5               |                                                  | 2.0 |               | ns    |  |

| t <sub>W</sub>    | LE Pulse Width                   | 3.0                  |                                                            | 3.0               |                                                  | 3.5 |               | ns    |  |

| toshl             | Output to Output Skew (Note 8)   |                      | 1.0                                                        |                   |                                                  |     |               |       |  |

| t <sub>OSLH</sub> |                                  |                      | 1.0                                                        |                   |                                                  |     |               | ns    |  |

Note 8: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t<sub>OSHL</sub>) or LOW-to-HIGH (t<sub>OSLH</sub>). Parameter guaranteed by design.

# Dynamic Switching Characteristics

| Symbol           | Parameter                                   | Conditions                                                                                                                             | V <sub>CC</sub><br>(V) | T <sub>A</sub> = 25°C<br>Typical | Units |

|------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------|-------|

| V <sub>OLP</sub> | Quiet Output Dynamic Peak V <sub>OL</sub>   | $C_L = 50 \text{ pF}, V_{IH} = 3.3 \text{V}, V_{IL} = 0 \text{V}$<br>$C_L = 30 \text{ pF}, V_{IH} = 2.5 \text{V}, V_{IL} = 0 \text{V}$ | 3.3                    | 0.35                             | V     |

|                  |                                             | $C_L = 30 \text{ pF}, V_{IH} = 2.5 \text{V}, V_{IL} = 0 \text{V}$                                                                      | 2.5                    | 0.25                             | v     |

| V <sub>OLV</sub> | Quiet Output Dynamic Valley V <sub>OL</sub> | $C_L = 50 \text{ pF}, V_{IH} = 3.3 \text{V}, V_{IL} = 0 \text{V}$                                                                      | 3.3                    | -0.35                            | V     |

|                  |                                             | $C_L = 30 \text{ pF}, V_{IH} = 2.5 \text{V}, V_{IL} = 0 \text{V}$                                                                      | 2.5                    | -0.25                            | v     |

# Capacitance

| Symbol           | Parameter                     | Conditions                                            | Typical | Units |

|------------------|-------------------------------|-------------------------------------------------------|---------|-------|

| CIN              | Input Capacitance             | $V_{CC} = Open, V_I = 0V \text{ or } V_{CC}$          | 7       | pF    |

| C <sub>OUT</sub> | Output Capacitance            | $V_{CC} = 3.3V$ , $V_I = 0V$ or $V_{CC}$              | 8       | pF    |

| C <sub>PD</sub>  | Power Dissipation Capacitance | $V_{CC} = 3.3V$ , $V_I = 0V$ or $V_{CC}$ , f = 10 MHz | 20      | pF    |