# GDC21D601 32-Bit RISC MCU

### Preliminary

Ver 1.6

HDS-GDC21D601-9908 / 10

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by Hyundai for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Hyundai or others.

These Hyundai products are intended for usage in general electronic equipment (office equipment, communication equipment, measuring equipment, domestic electrification, etc.).

Please make sure that you consult with us before you use these Hyundai products in equipment which require high quality and / or reliability, and in equipment which could have major impact to the welfare of human life (atomic energy control, airplane, spaceship, traffic signal, combustion control, all types of safety devices, etc.). Hyundai cannot accept liability to any damage which may occur in case these Hyundai products were used in the mentioned equipment without prior consultation with Hyundai.

Copyright 1999 Hyundai Micro Electronics Co.,Ltd. All Rights Reserved

# TABLE OF CONTENTS

| Section 1. Overview                                                                                                                                                               | 8                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1. General Description       8         2. Feature       10         3. Package       12         4. Pin Assignment       13         5. Pin Descriptions       15                    | 0<br>2<br>3<br>5 |

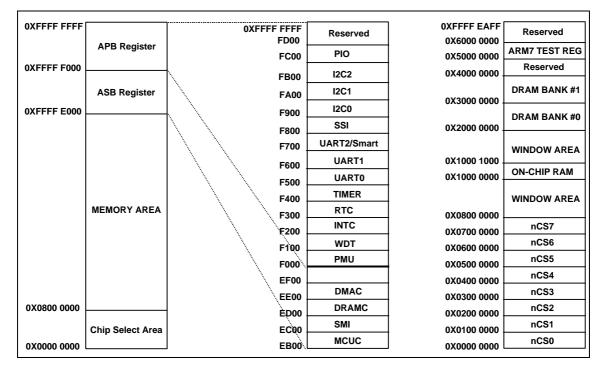

| Section 2. System Architecture                                                                                                                                                    | 0                |

| 1. Internal Bus Architecture.202. Arbiter203. System Decoder214. Memory Map215. Memory Format226. Boot Mode.227. Multi-Function Pin23                                             | 0<br>1<br>2<br>2 |

| Section 3. ARM720T Core24                                                                                                                                                         | 4                |

| 1. General Description    24      2. Feature    24      3. Core Block Diagram    26                                                                                               | 4                |

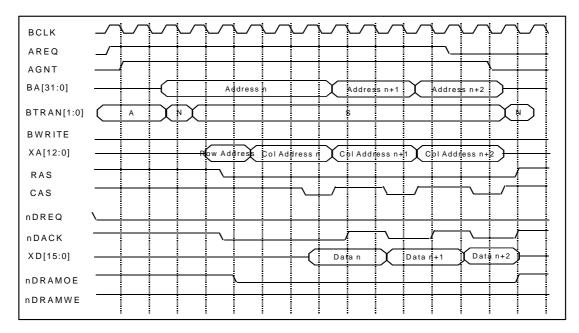

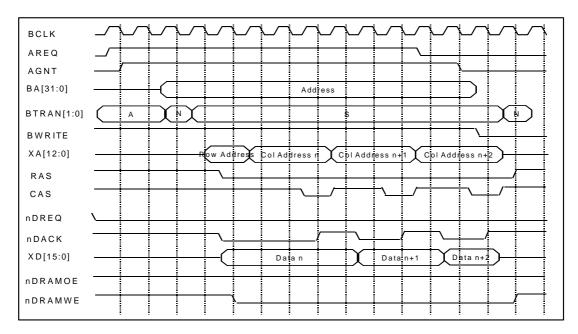

| Section 4. DRAM Controller                                                                                                                                                        | 7                |

| 1. General Description       27         2. Hardware Interface and Signal Description       28         3. Functional Description       31         4. Register Description       34 | 8<br>1           |

| Section 5. On-Chip SRAM                                                                                                                                                           | 7                |

| 1. General Description       37         2. Signal Description       37         3. Function Description       37                                                                   | 7                |

| Section 6. Static Memory Controller                                                                                                                                               | B                |

| 1. General Description       38         2. Signal Description       39         3. Functional Description       43         4. Programmer's Model       45                          | 9<br>3           |

| Section 7. MCU Controller                     | 48 |

|-----------------------------------------------|----|

| 1. General Description                        |    |

| 2. Signal Description                         |    |

| 3. Register Description                       | 49 |

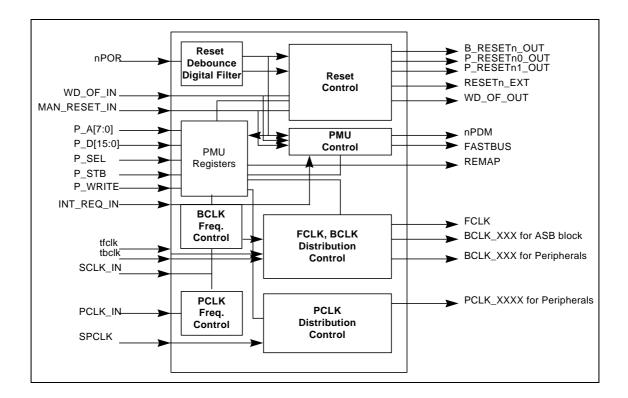

| Section 8. Power Management Unit              | 54 |

| 1. General Description                        |    |

| 2. Hardware Interface and Signal Description  | 55 |

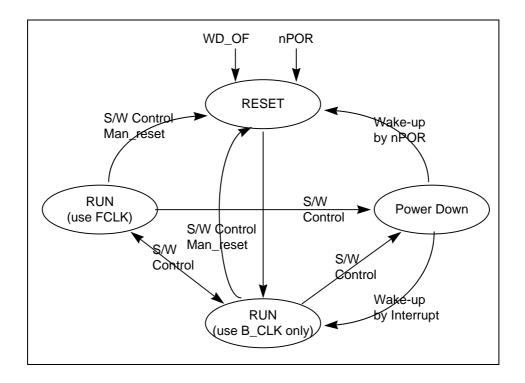

| 3. Operation Modes                            |    |

| 4. Register Description                       |    |

| 5. Power Management Unit Register Map         |    |

| 6. Test Mode Guide for MCU                    |    |

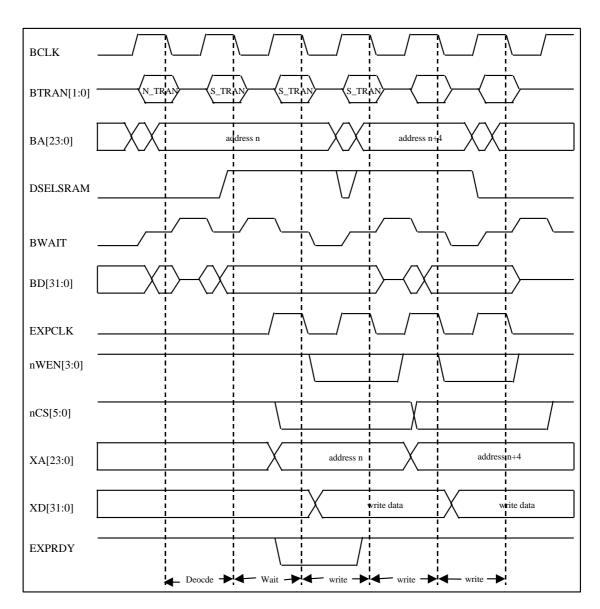

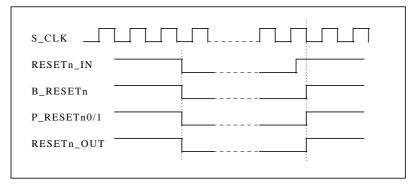

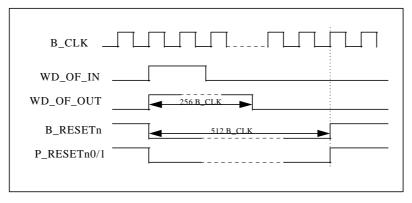

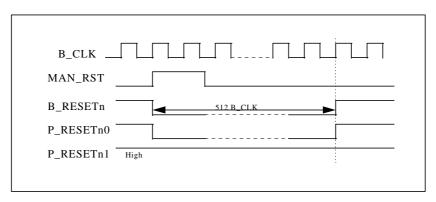

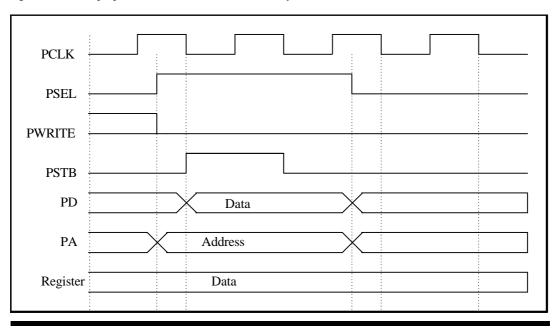

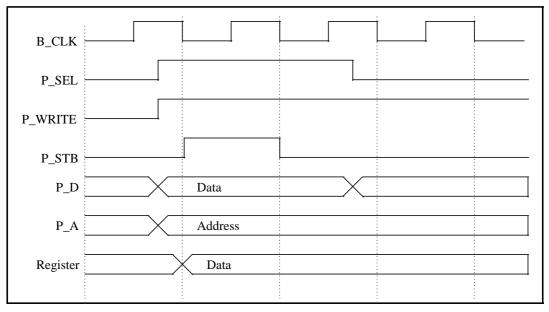

| 7. Signal Timing Diagram                      | 66 |

| Section 9. Watchdog Timer                     | 68 |

| 1. General Description                        | 68 |

| 2. Hardware Interface and Signal Description  |    |

| 3. Watchdog Timer Introduction                |    |

| 4. Watchdog Timer Operation                   |    |

| 5. Watchdog Timer Memory Map                  |    |

| 6. Watchdog Timer Register Descriptions       |    |

| 7. Examples of Register Setting               |    |

| Section 10. Interrupt Controller              | 81 |

| 1. General Description                        | 81 |

| 2. Hardware Interface and Signal Description  |    |

| 3. Interrupt Controller                       |    |

| 4. Interrupt Controller Memory Map            | 86 |

| 5. Interrupt Controller Register Descriptions |    |

| Section 11. Real Time Clock                   | 91 |

| 1. General Description                        |    |

| 2. Signal Description                         |    |

| 3. Hardware Interface                         |    |

| 4. Functional Description                     |    |

| 5. Real Time Clock Memory Map                 |    |

| 6. Real Time Clock Register Descriptions      |    |

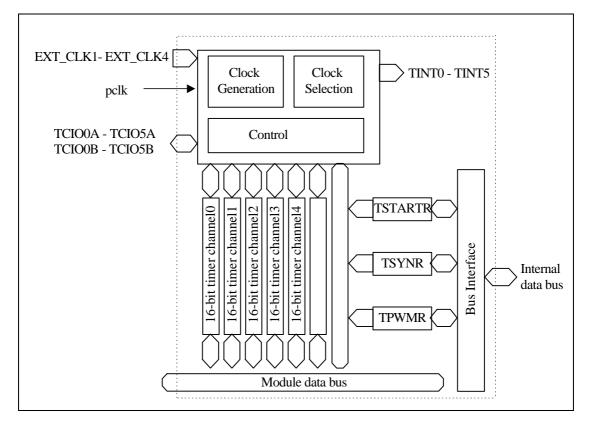

| Section 12. General Purpose Timer Unit              | 96  |

|-----------------------------------------------------|-----|

| 1. General Description                              |     |

| 2. Hardware Interface and Signal Description        |     |

| 3. General Purpose Timer Unit Introduction          |     |

| 4. General Purpose Timer Unit Operation             |     |

| 5. General Purpose Timer Unit Memory Map            |     |

| 6. General Purpose Timer Unit Register Descriptions |     |

| 7. Examples of Register Setting                     |     |

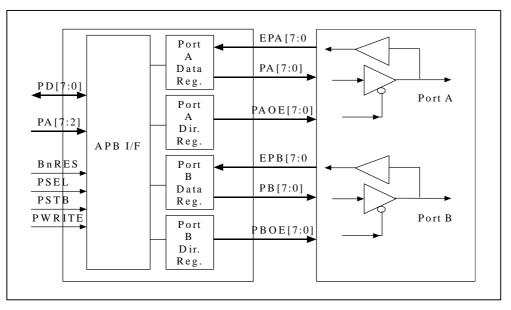

| Section 13. PIO                                     | 111 |

| 1. General Description                              |     |

| 2. Signal Description                               |     |

| 3. Hardware Interface                               |     |

| 4. Functional Description                           |     |

| 5. Programmer' s Model                              |     |

| ·                                                   |     |

| Section 14. Synchronous Serial Peripheral Interface | 118 |

| 1. General Description                              |     |

| 2. Signal Description                               |     |

| 3. Hardware Interface                               |     |

| 4. Functional Description                           |     |

| 5. Register Memory Map                              |     |

| 6. SSPI Data Clock Timing Diagram                   |     |

| Oracles 45 HADT                                     | 405 |

| Section 15. UART                                    | -   |

| 1. General Description                              |     |

| 2. Features                                         |     |

| 3. Signal Description                               |     |

| 4. Internal Block Diagram                           |     |

| 5. Registers Description                            |     |

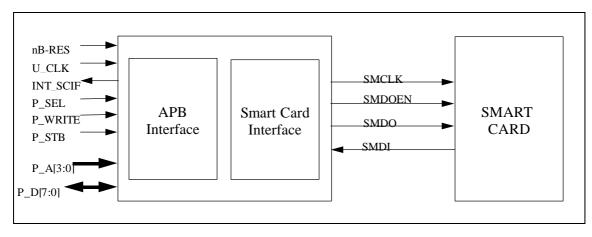

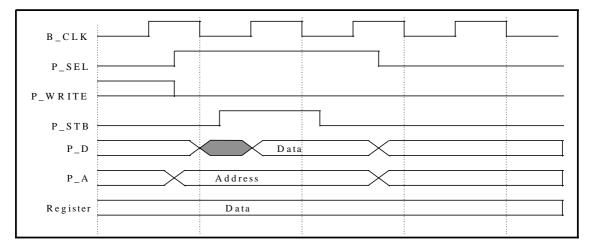

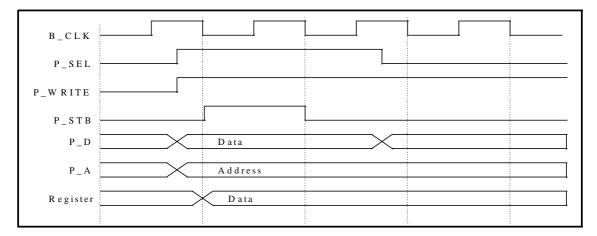

| Section 16. Smart Card Interface                    |     |

| 1. General Description                              | 142 |

| 2. Signal Description                               |     |

| 3. Hardware Interface                               |     |

| 4. Functional Description                           | 145 |

| 5. Programmer' s Model                              | 146 |

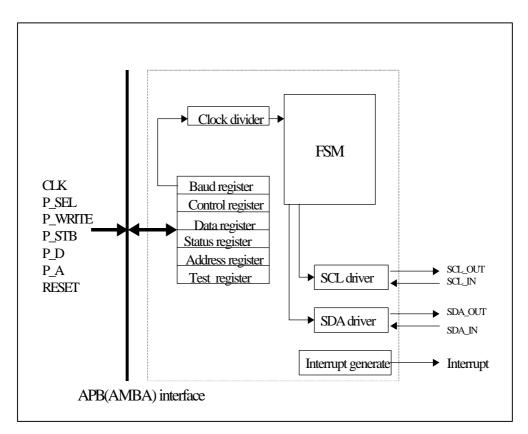

| Section 17. I <sup>2</sup> C Controller14                   | 19        |

|-------------------------------------------------------------|-----------|

| 1. General Description                                      | 19        |

| 2. I <sup>2</sup> C Controller Key Features                 | 50        |

| 3. I <sup>2</sup> C Controller Clocking and Pin Functions15 | 50        |

| 4. I <sup>2</sup> C Master Mode Transmit / Receive Process  |           |

| 5. I <sup>2</sup> C Restart Capability (Combined Mode)15    | 51        |

| 6. I <sup>2</sup> C Controller Programming Model15          | 52        |

| 7. I <sup>2</sup> C Module Signal Description15             | 54        |

| 8. Hardware Interface15                                     |           |

| 9. Register Memory Map15                                    | 56        |

| Section 18. Direct Memory Access Controller15               | 57        |

| 1. General Description                                      | 57        |

| 2. Signal Description                                       |           |

| 3. Programmer's Model15                                     |           |

| 4. Address Modes                                            |           |

| Section 19. Debug and Test Interface16                      | 37        |

| 1. General Description                                      | 37        |

| 2. Software Development Debug and Test Interface            |           |

| 3. Test Access Port and Boundary Scan16                     |           |

| Section 20. Electrical Ratings                              | <b>39</b> |

| 1. Absolute Maximum Ratings                                 | 39        |

| 2. Thermal Characteristics                                  |           |

| 3. D.C Electrical Characteristics                           |           |

| APENDIX A. Register Map17                                   | 70        |

Preliminary

GDC21D601

32-Bit RISC MCU

### Section 1. Overview

### **1. General Description**

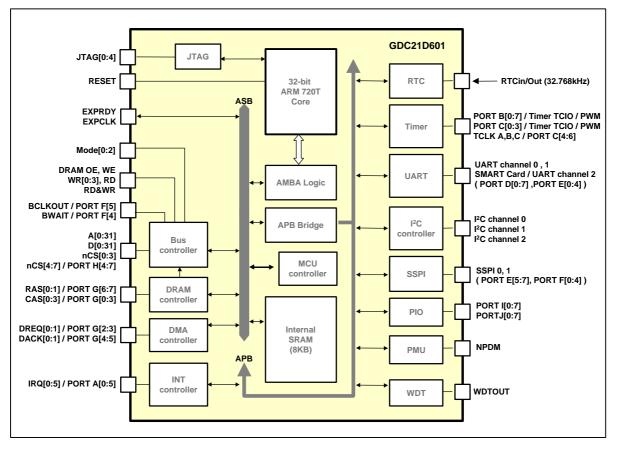

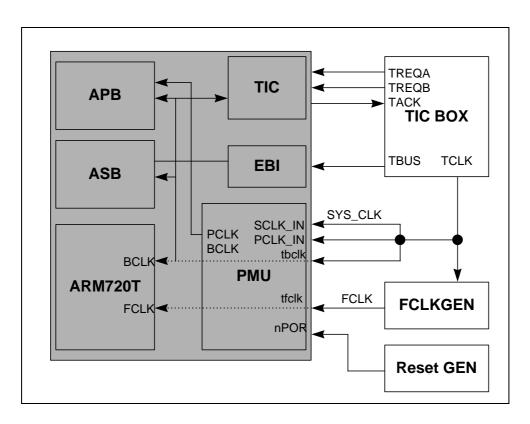

The GDC21D601 is the HME's 32bit high performance microcontroller unit (MCU). The GDC21D601 contains ARM720T, which is a general-purpose 32bit microprocessor, and extensive peripherals: 6 channel 16bit Timer, Watch Dog Timer, 2 channel UART, 2 channel SSPI, 3 channel I<sup>2</sup>C, Programmable Priority Interrupt Controller, 10 port PIO, 2 channel DMA Controller, External Memory Controller and BUS Controller including chip select logic.

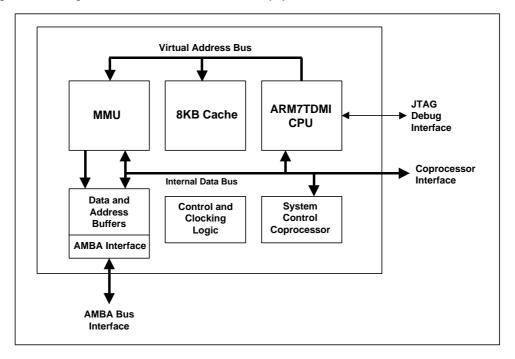

ARM720T is a 32bit Microprocessor with the CPU of the ARM7TDMI, 8KB Cache, enlarged write buffer and Memory Management Unit (MMU). The ARM720T is fully software compatible with the ARM processor family.

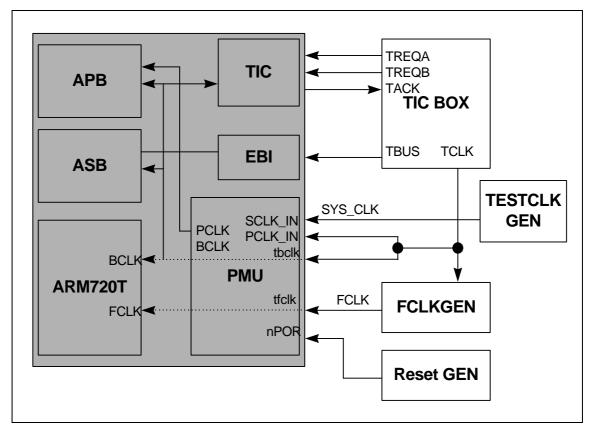

Figure. 1 GDC21D601 Block Diagram

The general descriptions of the GDC21D601 like following :

- On-Chip Modular Architecture (using AMBA)

- Utilizes the ARM720T("ARM7TDMI with 8Kbyte Cache and MMU") 32bit RISC Family

- 8Kbyte internal SRAM

- support 8bit/16bit/32bit external Data bus width

- Eight Programmable Chip Select Outputs with EXPRDY

- Support Little and Big Endian memory format

- Low Power Consumption using Power Management Unit

- Fully static operation : Max. 80MHz

- Two 32bit DMA Controllers (External request only)

- Programmable Priority Interrupt Controller (6 external sources)

- Two DRAM Banks Support

- Six 16bit Multi Function Timers / Counters for General Purpose Applications

- One 8bit Watch Dog Timer (WDT)

- Real Time Clock : 32.768 KHz

- Three UARTs (Universal Asynchronous Receiver Transmitter) compatible with 16C550 UART, one UART with Smart card interface

- Two SSPIs (Synchronous Serial Peripheral Interface) with FIFO

- Three I<sup>2</sup>C Master/Slave Controllers

- Programmable Input/Output (8bit 10 channel)

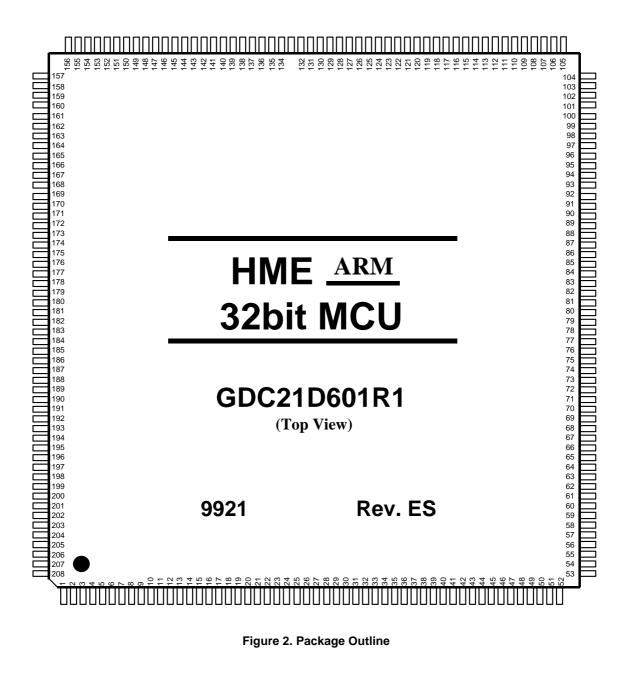

- 208 MQFP Package

### 2. Feature

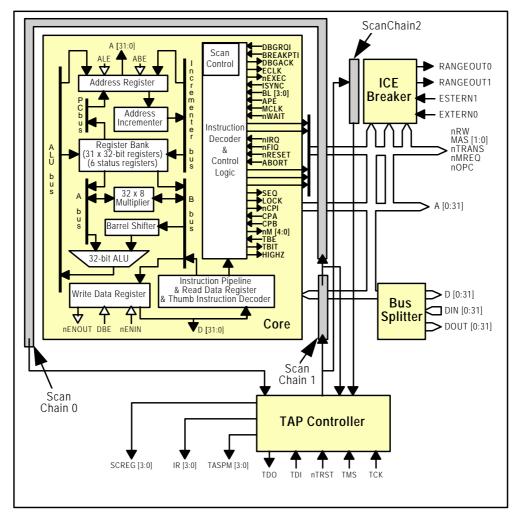

#### • ARM720T Core

- This is an ARM7TDMI CPU core with

- . 8KB cache

- . enlarged write buffer

- . MMU(Memory Management Unit)

- . On-chip ICEbreaker debug support

- . 32-bit x 8 hardware multiplier

- . Thumb decompressor

- . High-performance 32-bit RISC architecture

- . High-density 16-bit insturction set

- Enhanced ARM software toolkit

#### THUMB code is able to provide up to 65% of the code size of ARM, and 160% of the performance of an equivalent ARM processor connected to a 16-bit memory system.

The MMU supports 4G bytes Virtual address. The allocation of virtual addresses with different task ID improves performance in task switching operations with the cache enabled.

#### • DMA Controller

- Two Channels with identical function

- Four Gigabytes of address space

- 256 Kbytes transfers to the maximum

- Data Transfer unit : Byte, Half-word, Word

- Two kinds of Bus mode

- . Burst mode

- . Exception mode(Cycle steal)

- Two kinds of address mode

- . Single address mode

- . Dual address mode

- Two types of Transfer request source . External I/O request

- . Auto-request

- Two kind of fixed priority for channels

- Interrupted when the data transfers are complete

#### DRAM Controller

- DRAM access

- Support Word, Half-word, and Byte transaction

- CBR refresh in normal operation and self-refresh in power-down mode

- Support programmable refresh rate

- Support various DRAM access time by setting the wait count control register

- Static Memory Controller

- Chip Select up to 8 (Each Bank is 256 MByte) Exchangeable Chip Select Active High/Low

- (CS6 and CS7 only)

- Little-Endian and Big-Endian Memory Support

- Programmable wait-state (up to 16 wait-state)

- Support External BUS Ready Strobe

- Support various type Bus Control timing

- Support Word, Half-word, and Byte transaction

#### On-Chip SRAM

- 8k Bytes(2048x32)

- Asynchronous SRAM

- Can write 8/16/32bits data, and read 32bits data

#### MCU Controller

- The Memory Map Structure Control signals

- DRAM Power-Down Request and Powr-Down Ack signal

- Generate the Multi Function Pin control signals

- Device Code : \$GDC601

#### Power Management Unit

- Power On Reset, WD\_OF Reset, and S/W Reset

- Status : RESET, Power Down, RUN\_FAST,

- RUN\_SLOW

Provide separated clock for each modules on chip

- Provide BCLKOUT, WD\_OF, Power-Down pins for external devices

- Watch Dog Timer

- Watchdog timer mode & interval timer mode

- Eight counter clock sources

- Generate the Power Down reset or the Watch Dog Overflow

- Interrupt Controller

- Asynchronous interrupt controller

- Six external interrupt

- Twenty internal interrupt

- Level or edge triggered

- Mask for each interrupt source

- Request of IRQ, FIQ for each interrupt source

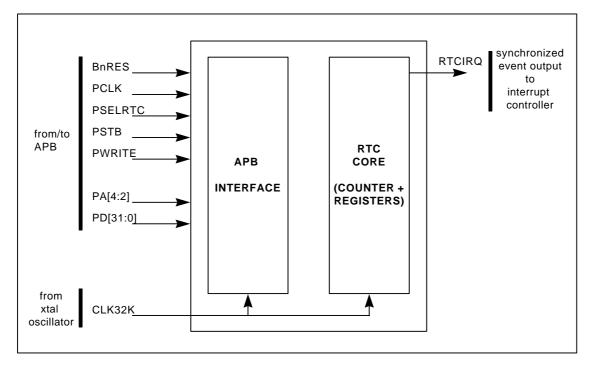

- Real Time Clock

- 32bit counter clocked by a 32.768KHz clock.

- 32bit match register

#### Programmable Input Output

- up to 80 pin (8bit 10channel)

- Each pin can be configurable as either input or output

#### • Timer

- 6 channel 16-bit up-count

- 4-internal pre-scaleable, 4-external input clock

- . 1 interrupt per 1 channel

- . 2 inout pin per 1 channel for input capture or output compare

- Basic function :

- . Compare match waveform output

- . Input capture

- . Match clear

- . Capture clear

- Synchronous mode

- . Synch. clear at two or more channel

- . Synch. write at two or more channel

- PWM waveform output mode

### Synchronous Serial Interface

- Supports full duplex communication

- Sends and receives data continuously, using 16 x 8 bit FIFOs

- Built-in baud rate generator capable of generation 4 clock rate

- Selectable clock source : either built-in buad-rate generator or external clock

- 4 independent interrupts : transmit-end, rx-full, tx-empty and tx-full

#### • UART

- 2 channel : UART only

- . Compatible with 16550

- . 16 byte each FIFO for TX / RX  $\,$

- . Start, stop and parity bit can be added or deleted from/to serial data

- . MODEM control functions (CTS, RTS, DSR, DTR, RI and DCD )

- . Fully programmable serial-interface

- characteristics : 5-, 6-, 7- or 8-bit characters

- : even, odd or no-parity bit generation and

- detection

- : 1-, 1.5- or 2-stop bit generation and detection

#### SmartCard Interface

- 1 channel : Support SmartCard Interface

- . Supports only asynchronous operation . Supports cards that have internal reset

- capability . Supports cards that have an active low reset

- input

- . Supports cards that use the internal clock

- . Generate the clock for a card expecting the external clock

- . Use the serial in/out ports for I/O

- . Use the PIO ports for other interface signals like RST, DETECT, etc

### • I<sup>2</sup>C

- 3 channels

- Master / Slave function

- Programmable clock speed

- 8bit data transfer

- Slave clock stretch support

- Maskable interrupt

- Support clock rates up to 1.84MHz Baud

### GDC21D601

GDC21D601

# **HYUNDAI**MicroElectronics

### 3. Package

### 4. Pin Assignment

| PIN | NAME      | PIN | NAME       | PIN | NAME                 | PIN | NAME      |

|-----|-----------|-----|------------|-----|----------------------|-----|-----------|

| 1   | A0        | 45  | IRQ0/PA0   | 89  | VDD                  | 133 | NRAS0/PG6 |

| 2   | A1        | 46  | VDD        | 90  | SMDI/PE2             | 134 | VSS       |

| 3   | VDD       | 47  | IRQ1/PA1   | 91  | SMDO/PE3             | 135 | NRAS1/PG7 |

| 4   | A2        | 48  | IRQ2/PA2   | 92  | SMCLK/PE4            | 136 | NCAS0/PH0 |

| 5   | A3        | 49  | IRQ3/PA3   | 93  | VSS                  | 137 | NCAS1/PH1 |

| 6   | A4        | 50  | VSS        | 94  | SIN0/ PE5            | 138 | NCAS2/PH2 |

| 7   | VSS       | 51  | IRQ4/PA4   | 95  | SOUT0/PE6            | 139 | NCAS3/PH3 |

| 8   | A5        | 52  | IRQ5/PA5   | 96  | SCLK0/PE7            | 140 | VSS       |

| 9   | A6        | 53  | PA6        | 97  | VDD                  | 141 | XOUT      |

| 10  | A7        | 54  | PA7        | 98  | SCS0/PF0/MemByte0    | 142 | XIN       |

| 11  | VDD       | 55  | TCIOA0/PB0 | 99  | SIN1/PF1/MemByte1    | 143 | VDD       |

| 12  | A8        | 56  | VDD        | 100 | SOUT1/PF2            | 144 | NDRAMOE   |

| 13  | A9        | 57  | TCIOB0/PB1 | 101 | VSS                  | 145 | NDRAMWE   |

| 14  | A10       | 58  | TCIOA1/PB2 | 102 | SCLK1/PF3            | 146 | VSS       |

| 15  | VSS       | 59  | TCIOB1/PB3 | 103 | SCS1/PF4             | 147 | NWR0      |

| 16  | A11       | 60  | VSS        | 104 | BCLKOUT/PF5          | 148 | NWR1      |

| 17  | A12       | 61  | TCIOA2/PB4 | 105 | NFIQOUT/PF6          | 149 | NWR2      |

| 18  | VDD       | 62  | TCIOB2/PB5 | 106 | NIRQOUT/PF7          | 150 | VDD       |

| 19  | A13       | 63  | TCIOA3/PB6 | 107 | VDD                  | 151 | NWR3      |

| 20  | A14       | 64  | VDD        | 108 | I <sup>2</sup> CSDA0 | 152 | NRD       |

| 21  | A15       | 65  | TCIOB3/PB7 | 109 | I <sup>2</sup> CSCL0 | 153 | RDNWR     |

| 22  | VSS       | 66  | PC0/TCIOA4 | 110 | I <sup>2</sup> CSDA1 | 154 | VSS       |

| 23  | A16       | 67  | PC1/TCIOB4 | 111 | VSS                  | 155 | NEXPRDY   |

| 24  | A17       | 68  | VSS        | 112 | I <sup>2</sup> CSCL1 | 156 | EXPCLK    |

| 25  | A18       | 69  | PC2/TCIOA5 | 113 | I <sup>2</sup> CSDA2 | 157 | NCS0      |

| 26  | VDD       | 70  | PC3/TCIOB5 | 114 | I <sup>2</sup> CSCL2 | 158 | NCS1      |

| 27  | A19       | 71  | PC4/TCLKA  | 115 | VDD                  | 159 | NCS2      |

| 28  | A20       | 72  | VDD        | 116 | Mode0/TREQA          | 160 | VDD       |

| 29  | A21       | 73  | PC5/TCLKB  | 117 | Mode1/TREQB          | 161 | NCS3      |

| 30  | VSS       | 74  | PC6/TCLKC  | 118 | Mode2/TACK           | 162 | NCS4/PH4  |

| 31  | A22       | 75  | PC7/TCLKD  | 119 | VSS                  | 163 | NCS5/PH5  |

| 32  | A23       | 76  | RXD0/PD0   | 120 | UCLKOUT              | 164 | VSS       |

| 33  | WDTOUT    | 77  | VSS        | 121 | UCLKIN               | 165 | CS6/PH6   |

| 34  | NPDN      | 78  | TXD0/PD1   | 122 | VDD                  | 166 | CS7/PH7   |

| 35  | VSS       | 79  | RXD1/PD2   | 123 | TEST                 | 167 | D31/PJ7   |

| 36  | RTCOSCIN  | 80  | TXD1/PD3   | 124 | NEXTREQ/PG0          | 168 | VDD       |

| 37  | RTCOSCOUT | 81  | VDD        | 125 | NRESET               | 169 | D30/PJ6   |

| 38  | VDD       | 82  | NCTS/ PD4  | 126 | VSS                  | 170 | D29/PJ5   |

| 39  | NTRST     | 83  | NDSR/PD5   | 127 | NEXTACK/PG1          | 171 | D28/PJ4   |

| 40  | TDI       | 84  | NDCD/ PD6  | 128 | NDREQ0/PG2           | 172 | VSS       |

| 41  | TCK       | 85  | VSS        | 129 | NDACK0/PG3           | 173 | D27/PJ3   |

| 42  | VSS       | 86  | NRI/ PD7   | 130 | VDD                  | 174 | D26/PJ2   |

| 43  | TDO       | 87  | NDTR/PE0   | 131 | NDREQ1/PG4           | 175 | D25/PJ1   |

| 44  | TMS       | 88  | NRTS/PE1   | 132 | NDACK1/PG5           | 176 | VDD       |

| PIN | NAME    | PIN | NAME    | PIN | NAME | PIN | NAME |

|-----|---------|-----|---------|-----|------|-----|------|

| 177 | D24/PJ0 | 185 | VDD     | 193 | VDD  | 201 | VDD  |

| 178 | D23/PI7 | 186 | D17/PI1 | 194 | D11  | 202 | D5   |

| 179 | D22/PI6 | 187 | D16/PI0 | 195 | D10  | 203 | D4   |

| 180 | D21/PI5 | 188 | D15     | 196 | D9   | 204 | D3   |

| 181 | VSS     | 189 | VSS     | 197 | VSS  | 205 | VSS  |

| 182 | D20/PI4 | 190 | D14     | 198 | D8   | 206 | D2   |

| 183 | D19/PI3 | 191 | D13     | 199 | D7   | 207 | D1   |

| 184 | D18/PI2 | 192 | D12     | 200 | D6   | 208 | D0   |

### GDC21D601

### 5. Pin Descriptions

| PIN NUMBER      | PIN NAME  | TYPE | DESCRIPTION                                                                                                                                                   |  |

|-----------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1~2, 4~6, 8~10, | A[31:0]   | 0    | Address Bus                                                                                                                                                   |  |

| 12~14, 16~17,   |           |      | Valid After RESET.                                                                                                                                            |  |

| 19~21, 23~25,   |           |      |                                                                                                                                                               |  |

| 27~29, 31~32    |           |      |                                                                                                                                                               |  |

| 33              | WDTOUT    | 0    | Watch Dog Timer Overflow Output                                                                                                                               |  |

| 34              | NPDN      | 0    | Power Down Signal from PMU block<br>When it is LOW, MCU entered the power down mode. When HIGH, normal                                                        |  |

| 37              | RTCOSCIN  | Ι    | Real Time Clock Oscillator Input 32.768kHz                                                                                                                    |  |

| 36              | RTCOSCOUT | 0    | Real Time Clock Oscillator Output                                                                                                                             |  |

| 39              | NRST      | Ι    | JTAG Reset                                                                                                                                                    |  |

| 40              | TDI       | Ι    | JTAG Data Input                                                                                                                                               |  |

| 41              | TCK       | Ι    | JTAG Clock Input                                                                                                                                              |  |

| 43              | TDO       | 0    | JTAG Data Output                                                                                                                                              |  |

| 44              | TMS       | Ι    | JTAG Mode Signal                                                                                                                                              |  |

| 45              | IRQ0      | I/O  | External Interrupt Input 0, when PINMUX_PA[0] = 0<br>Programmable I/O ports. Each pin can be mapped to specified<br>function pin name. (External IRQ0,IRQ1,). |  |

|                 | PA0       |      | PIO Port A[0], when PINMUX_ $PA[0] = 1$                                                                                                                       |  |

| 47              | IRQ1      | I/O  | External Interrupt Input 1, when PINMUX_PA[1] = 0                                                                                                             |  |

|                 | PA1       |      | PIO Port A[1], when PINMUX_ $PA[1] = 1$                                                                                                                       |  |

| 48              | IRQ2      | I/O  | External Interrupt Input 2, when PINMUX_PA[2] = 0                                                                                                             |  |

|                 | PA2       |      | PIO Port A[2], when PINMUX_PA[2] = 1                                                                                                                          |  |

| 49              | IRQ3      | I/O  | External Interrupt Input 3, when PINMUX_PA[3] = 0                                                                                                             |  |

|                 | PA3       |      | PIO Port A[3], when PINMUX_PA[3] = 1                                                                                                                          |  |

| 51              | IRQ4      | I/O  | External Interrupt Input 4, when PINMUX_PA[4] = 0                                                                                                             |  |

|                 | PA4       |      | PIO Port A[4], when PINMUX_PA[4] =1                                                                                                                           |  |

| 52              | IRQ5      | I/O  | External Interrupt Input 5, when PINMUX_PA[5] = 0                                                                                                             |  |

|                 | PA5       |      | PIO Port A[5], when PINMUX_PA[5] = 1                                                                                                                          |  |

| 53              | PA6       | I/O  | PIO Port A[6]<br>Tbclk Clock Input for TIC test                                                                                                               |  |

| 54              | PA7       | I/O  | PIO Port A[7]                                                                                                                                                 |  |

|                 |           |      | Tfclk Clock Input for TIC test                                                                                                                                |  |

| 55              | TCIOA0    | I/O  | Timer Channel 0 Input Capture A, when PINMUX_PB[0] = 0                                                                                                        |  |

|                 | PB0       |      | PIO Port B[0], when PINMUX_PB[0] = $1$                                                                                                                        |  |

| 57              | TCIOB0    | I/O  | Timer Channel 0 Input Capture B, when PINMUX_PB[1] = 0                                                                                                        |  |

|                 | PB1       |      | PIO Port B[1], when PINMUX_PB[1] = $1$                                                                                                                        |  |

| 58              | TCIOA1    | I/O  | Timer Channel 1 Input Capture A, when PINMUX_PB[2] = 0                                                                                                        |  |

|                 | PB2       |      | PIO Port B[2], when PINMX_PB[2] = 1                                                                                                                           |  |

| 59              | TCIOB1    | I/O  | Timer Channel 1 Input Capture B, when PINMUX_PB[3] = 0                                                                                                        |  |

|                 | PB3       |      | PIO Port B[3], when PINMUX_PB[3] = 1                                                                                                                          |  |

| 61              | TCIOA2    | I/O  | Timer Channel 2 Input Capture A, when PINMUX_PB[4] = 0                                                                                                        |  |

|                 | PB4       |      | PIO Port B[4], when PINMUX_PB[4] = $1$                                                                                                                        |  |

| 62              | TCIOB2    | I/O  | Timer Channel 2 Input Capture B, when PINMUX_PB[5] = 0                                                                                                        |  |

|                 | PB5       |      | PIO Port B[5], when PINMUX_PB[5] = $1$                                                                                                                        |  |

| PIN NUMBER | PIN NAME | TYPE | DESCRIPTION                                              |  |

|------------|----------|------|----------------------------------------------------------|--|

| 63         | TCIOA3   | I/O  | Timer Channel 3 Input Capture A, when PINMUX_PB[6] = $0$ |  |

|            | PB6      |      | PIO Port B[6], when PINMUX_PB[6] = 1                     |  |

| 65         | TCIOB3   | I/O  | Timer Channel 3 Input Capture B, when PINMUX_PB[7] = $0$ |  |

|            | PB7      |      | PIO Port B[7], when PINMUX_PB[7] = 1                     |  |

| 66         | PC0      | I/O  | PIO Port C[0], when PINMUX_PC[0] = $0$                   |  |

|            | TCIOA4   |      | Timer Channel 4 Input Capture A, when PINMUX_PC[0] = 1   |  |

| 67         | PC1      | I/O  | PIO Port C[1], when PINMUX_PC[1] = $0$                   |  |

|            | TCIOB4   |      | Timer Channel 4 Input Capture B, when PINMUX_PC[1] = 1   |  |

| 69         | PC2      | I/O  | PIO Port C[2], when PINMUX_PC[2] = $0$                   |  |

|            | TCIOA5   |      | Timer Channel 5 Input Capture A, when PINMUX_PC[2] = 1   |  |

| 70         | PC3      | I/O  | PIO Port C[3], when PINMUX_PC[3] = $0$                   |  |

|            | TCIOB5   |      | Timer Channel 5 Input Capture B, when PINMUX_PC[3] = 1   |  |

| 71         | PC4      | I/O  | PIO Port C[4], when PINMUX_PC[4] = $0$                   |  |

|            | TCLKA    |      | External Timer Clock Source A, when PINMUX_PC[4] = 1     |  |

| 73         | PC5      | I/O  | PIO Port C[5], when PINMUX_PC[5] = $0$                   |  |

|            | TCLKB    |      | External Timer Clock Source B, when PINMUX_PC[5] = 1     |  |

| 74         | PC6      | I/O  | PIO Port C[6], when PINMUX_PC[6] = $0$                   |  |

|            | TCLKC    |      | External Timer Clock Source C, when PINMUX_PC[6] = 1     |  |

| 75         | PC7      | I/O  | PIO Port C[7], when PINMUX_PC[7] = $0$                   |  |

|            | TCLKD    |      | External Timer Clock Source D, when PINMUX_PC[7] = 1     |  |

| 76         | RXD0     | I/O  | UART Channel 0 Receive Data, when $PINMUX_PD[0] = 0$     |  |

|            | PD0      |      | PIO Port $D[0]$ , when PINMUX_PD[0] = 1                  |  |

| 78         | TXD0     | I/O  | UART Channel 0 Transmit Data, when $PINMUX_PD[1] = 0$    |  |

|            | PD1      |      | PIO Port D[1], when PINMUX_PD[1] =1                      |  |

| 79         | RXD1     | I/O  | UART Channel 1 Receive Data, when PINMUX_PD[2] = 0       |  |

|            | PD2      |      | PIO Port D[2], when PINMUX_PD[2] = 1                     |  |

| 80         | TXD1     | I/O  | UART Ch 1 Transmit Data, when PINMUX_PD[3] = $0$         |  |

|            | PD3      |      | PIO Port D[3], when PINMUX_PD[3] =1                      |  |

| 82         | NCTS     | I/O  | UART Ch 1 Clear to Send, when PINMUX_PD[4] = $0$         |  |

|            | PD4      |      | PIO Port D[4], when PINMUX_PD[4] = $1$                   |  |

| 83         | NDSR     | I/O  | UART Ch 1 Data Set Ready, when $PINMUX_PD[5] = 0$        |  |

|            | PD5      |      | PIO Port D[5], when PINMUX_PD[5] = 1                     |  |

| 84         | NDCD     | I/O  | UART Ch 1 Data Carrier Detect, when $PINMUX_PD[6] = 0$   |  |

|            | PD6      |      | PIO Port D[6], when PINMUX_PD[6] = $1$                   |  |

| 86         | NRI      | I/O  | UART Ch 1 Ring Indicator, when $PINMUX_PD[7] = 0$        |  |

|            | PD7      |      | PIO Port D[7], when PINMUX_PD[7] =1                      |  |

| 87         | NDTR     | I/O  | UART C 1 Data Terminal Ready, when $PINMUX_PE[0] = 0$    |  |

|            | PE0      |      | PIO Port $E[0]$ , when PINMUX_PE[0] = 1                  |  |

| 88         | NRTS     | I/O  | UART Ch 1 Ready to Send Data, when $PINMUX_PE[1] = 0$    |  |

|            | PE1      |      | PIO Port $E[1]$ , when PINMUX_PE[1] = 1                  |  |

| 90         | SMDI     | I/O  | Smart Card Interface Data In, when PINMUX_PE[2] = 0      |  |

|            | PE2      |      | PIO Port E[2], when PINMUX_PE[2] = 1                     |  |

| 91         | SMDO     | I/O  | Smart Card Interface Data Out, when PINMUX_PE[3] = 0     |  |

|            | PE3      |      | PIO Port E[3], when PINMUX_PE[3] =1                      |  |

| 92         | SMCLK    | I/O  | Smart Card Interface Clock Out, when $PINMUX_PE[4] = 0$  |  |

|            | PE4      |      | PIO Port E[4], when PINMUX_ $PE[4] = 1$                  |  |

| PIN NUMBER | PIN NAME             | TYPE | DESCRIPT                                         | ION                                              |

|------------|----------------------|------|--------------------------------------------------|--------------------------------------------------|

| 94         | SIN0                 | I/O  | SSI Channel 0 Data In, when PINM                 |                                                  |

| -          | PE5                  |      | PIO Port E[5], when PINMUX_PE[5] =1              |                                                  |

|            | BPROT0               |      | AMNA BPROT[0] Signal, when PIN                   |                                                  |

| 95         | SOUT0                | I/O  | SSI Channel 0 Data Out, when PINMUX_ $PE[6] = 0$ |                                                  |

|            | PE6                  |      | PIO Port E[6], when PINMUX_PE[6]                 |                                                  |

|            | BPROT1               |      | AMBA BPROT[1] Signal, when PIN                   | -                                                |

| 96         | SCLK0                | I/O  | SSI Channel 0 Clock Out, when PIN                |                                                  |

|            | PE7                  |      | PIO Port E[7], when PINMUX_PE[7]                 |                                                  |

|            | BLOK                 |      | AMBA BLOK Signal Out, when PIN                   |                                                  |

| 98         | SCS0                 | I/O  | SSI Channel 0 Channel Control, whe               |                                                  |

|            | PF0                  |      | PIO Port F[0], when PINMUX_PF[0]                 |                                                  |

|            | MemByte0             |      | MemByte[0] Signal from EBI Block                 |                                                  |

| 99         | SIN1                 | I/O  | SSI Channel 1 Data In, when PINM                 |                                                  |

|            | PF1                  |      | PIO Port F[1], when PINMUX_PF[1]                 |                                                  |

|            | MemByte1             |      | MemByte[1] Signal from EBI Block                 |                                                  |

| 100        | SOUT1                | I/O  | SSI Channel 1 Data Out, when PINN                |                                                  |

| 100        | PF2                  | 10   | PIO Port F[2], when PINMUX_PF[2]                 |                                                  |

|            | BTRANSO              |      | AMBA BTRANS[0] Signal, when P                    |                                                  |

| 102        | SCLK1                | I/O  | SSI Channel 1 Clock Out, when PIN                |                                                  |

| 102        | PF3                  | 10   | PIO Port F[3], when PINMUX_PF[3]                 |                                                  |

|            | BTRANS[1]            |      | AMBA BTRANS[1] Signal, when P                    |                                                  |

| 103        | SCS1                 | I/O  | SSI Channel 1 Channel Control, whe               |                                                  |

|            | PF4                  |      | PIO Port F[4], when PINMUX_PF[4]                 |                                                  |

|            | BWAIT                |      | AMBA BWAIT Signal, when PINM                     |                                                  |

| 104        | BCLKOUT              | I/O  | AMBA BCLK Signal, when PINMU                     |                                                  |

|            | PF5                  |      | PIO Port F[5], when PINMUX_PF[5]                 |                                                  |

| 105        | NFIQOUT              | I/O  | AMBA NFIQ Signal, when PINMU                     | -                                                |

|            | PF6                  |      | PIO Port F[6], when PINMUX_PF[6]                 |                                                  |

| 106        | NIRQOUT              | I/O  | AMBA NIRQ Signal, when PINMUX_PF[7] = 0          |                                                  |

|            | PF7                  |      | PIO Port F[7], when PINMUX_PF[7]                 |                                                  |

| 108        | I <sup>2</sup> CSDA0 | I/O  | Data Signal for I <sup>2</sup> C Channel 0       | -                                                |

|            |                      |      | Pins (108~110,112~114) are require               | ed to be pull-up externally.                     |

|            |                      |      | When bus is free, this pin goes logical "H       | IIGH″                                            |

|            |                      |      | After reset, SDA pins enter Idle state           |                                                  |

| 109        | I <sup>2</sup> CSCL0 | I/O  | Clock Signal for I <sup>2</sup> C Channel 0      |                                                  |

| 110        | I <sup>2</sup> CSDA1 | I/O  | Data Signal for I <sup>2</sup> C Channel 1       |                                                  |

| 112        | I <sup>2</sup> CSCL1 | I/O  | Clock Signal for I <sup>2</sup> C Channel 1      |                                                  |

| 113        | I <sup>2</sup> CSDA2 | I/O  | Data Signal for I <sup>2</sup> C Channel 2       |                                                  |

| 114        | I <sup>2</sup> CSCL2 | I/O  | Clock Signal for I <sup>2</sup> C Channel 2      |                                                  |

| 116        | Mode0                | Ι    | Boot Mode0, when TEST $pin = 0$                  |                                                  |

|            |                      |      | By default, 32-bit access                        | Mode[0:1] = 00 32-bit                            |

|            |                      |      | (MCU can boot from 32- bit Memory)               | Mode[0:1] = 01  8-bit                            |

|            | TREQA                |      | TREQA Signal for TIC Test,                       | Mode[0:1] = 10 16-bit<br>Mode[0:1] = 11 Reserved |

|            |                      |      | when TEST pin = 1                                |                                                  |

| 117        | Mode1                | Ι    | Boot Mode 1                                      | 4                                                |

|            | TREQB                |      | TREQB Signal for TIC Test                        |                                                  |

| 118Mode 2I/OBoot Mode 2 (BigEndian Pin)<br>Big-endian Selection Pin, when this pin = 1(HIGH)<br>Note) When this pin is HIGH, External Data will be<br>transferred "Big-endian" format.TACKTACKTACK Signal for TIC Test120UCLKINIUART Clock Oscillator Clock Input<br>UART block dedicated clock source supported.<br>(This clock source is used for UART and SMART Card Only)121UCLKOUTOUART Clock Oscillator Clock Output123TESTITest Input Pin, Select 116~118 pin as Boot Mode or TI124NEXTREQI/OExternal Master Request Bus Mastership, when PINMU<br>PG0125NRESETISystem Power On Reset Input<br>To ensure proper initialization after power is stable,<br>assert NRESET pin for at least 20ms127NEXTACKI/OBus Granted Signal for External Master, when PINMUZ<br>PIO Port G[1] = 1, when PINMUX_PG[2] = 0128NDREQ0I/ODMA Channel 0 Request, when PINMUX_PG[2] = 1129NDACK0I/ODMA Channel 0 Acknowledge, when PINMUX_PG[3] = 1131NDREQ1I/ODMA Channel 1 Request, when PINMUX_PG[4] = 1132NDACK1I/ODMA Channel 1 Acknowledge, when PINMUX_PG[5] | TC Signal<br>UX_PG[0] = 0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Note)Note)When this pin is HIGH,External Data will be<br>transferred "Big-endian" format.TACKTACKTACK Signal for TIC Test120UCLKINIUART Clock Oscillator Clock Input<br>UART block dedicated clock source supported.<br>(This clock source is used for UART and SMART Card Only)121UCLKOUTOUART Clock Oscillator Clock Output123TESTITest Input Pin, Select 116~118 pin as Boot Mode or TI124NEXTREQI/OExternal Master Request Bus Mastership, when PINMU<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TC Signal<br>UX_PG[0] = 0 |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TC Signal<br>UX_PG[0] = 0 |

| TACKTACK Signal for TIC Test120UCLKINIUART Clock Oscillator Clock Input<br>UART block dedicated clock source supported.<br>(This clock source is used for UART and SMART Card Only)121UCLKOUTOUART Clock Oscillator Clock Output123TESTITest Input Pin, Select 116~118 pin as Boot Mode or TI124NEXTREQI/OExternal Master Request Bus Mastership, when PINMU<br>PIO Port G[0], when PINMUX_PG[0] = 1125NRESETISystem Power On Reset Input<br>To ensure proper initialization after power is stable,<br>assert NRESET pin for at least 20ms127NEXTACKI/OBus Granted Signal for External Master, when PINMUZ<br>PIO Port G[1] = 1, when PINMUX_PG[1] = 1128NDREQ0I/ODMA Channel 0 Request, when PINMUX_PG[2] = 0129NDACK0I/ODMA Channel 0 Acknowledge, when PINMUX_PG[3] =1131NDREQ1I/ODMA Channel 1 Request, when PINMUX_PG[4] = 0PIO Port G[4], when PINMUX_PG[4] = 1I/OPIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                        | UX_PG[0] = 0              |

| 120UCLKINIUART Clock Oscillator Clock Input<br>UART block dedicated clock source supported.<br>(This clock source is used for UART and SMART Card Only)121UCLKOUTOUART Clock Oscillator Clock Output123TESTITest Input Pin, Select 116~118 pin as Boot Mode or TI124NEXTREQI/OExternal Master Request Bus Mastership, when PINMU<br>PG0PG0PIO Port G[0], when PINMUX_PG[0] = 1125NRESETI127NEXTACKI/OPG1PIO Port G[1] = 1, when PINMUX_PG[1] = 1128NDREQ0I/OPG2PIO Port G[2], when PINMUX_PG[2] = 0PG3I/ODMA Channel 0 Request, when PINMUX_PG[3] = 1131NDREQ1I/ODMA Channel 1 Request, when PINMUX_PG[4] = 0PIO Port G[4], when PINMUX_PG[4] = 110                                                                                                                                                                                                                                                                                                                                                                                                 | UX_PG[0] = 0              |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UX_PG[0] = 0              |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | UX_PG[0] = 0              |

| 121UCLKOUTOUART Clock Oscillator Clock Output123TESTITest Input Pin, Select 116~118 pin as Boot Mode or T124NEXTREQI/OExternal Master Request Bus Mastership, when PINMU<br>PIO Port G[0], when PINMUX_PG[0] = 1125NRESETISystem Power On Reset Input<br>To ensure proper initialization after power is stable,<br>assert NRESET pin for at least 20ms127NEXTACKI/OBus Granted Signal for External Master, when PINMUX<br>PIO Port G[1] = 1, when PINMUX_PG[1] = 1128NDREQ0I/ODMA Channel 0 Request, when PINMUX_PG[2] = 0129NDACK0I/ODMA Channel 0 Acknowledge, when PINMUX_PG[3]<br>PIO Port G[3], when PINMUX_PG[3] = 1131NDREQ1I/ODMA Channel 1 Request, when PINMUX_PG[4] = 0PIO Port G[4], when PINMUX_PG[4] = 110PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                        | UX_PG[0] = 0              |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | UX_PG[0] = 0              |

| 124NEXTREQI/OExternal Master Request Bus Mastership, when PINMU<br>PIO Port G[0], when PINMUX_PG[0] = 1125NRESETISystem Power On Reset Input<br>To ensure proper initialization after power is stable,<br>assert NRESET pin for at least 20ms127NEXTACKI/OBus Granted Signal for External Master, when PINMUX<br>PIO Port G[1] = 1, when PINMUX_PG[1] = 1128NDREQ0I/ODMA Channel 0 Request, when PINMUX_PG[2] = 0PG2PIO Port G[2], when PINMUX_PG[2] = 1129NDACK0I/ODMA Channel 0 Acknowledge, when PINMUX_PG[3]<br>PIO Port G[3], when PINMUX_PG[3] = 1131NDREQ1I/ODMA Channel 1 Request, when PINMUX_PG[4] = 0PIO Port G[4], when PINMUX_PG[4] = 1PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                                                            | UX_PG[0] = 0              |

| PG0         PIO Port G[0], when PINMUX_PG[0] = 1           125         NRESET         I         System Power On Reset Input<br>To ensure proper initialization after power is stable,<br>assert NRESET pin for at least 20ms           127         NEXTACK         I/O         Bus Granted Signal for External Master, when PINMUZ<br>PIO Port G[1] = 1, when PINMUX_PG[1] = 1           128         NDREQ0         I/O         DMA Channel 0 Request, when PINMUX_PG[2] = 0           PG2         PIO Port G[2], when PINMUX_PG[2] = 1           129         NDACK0         I/O           PG3         PIO Port G[3], when PINMUX_PG[3] = 1           131         NDREQ1         I/O           PG4         PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                     |                           |

| 125       NRESET       I       System Power On Reset Input<br>To ensure proper initialization after power is stable,<br>assert NRESET pin for at least 20ms         127       NEXTACK       I/O       Bus Granted Signal for External Master, when PINMUZ<br>PIO Port G[1] = 1, when PINMUX_PG[1] = 1         128       NDREQ0       I/O       DMA Channel 0 Request, when PINMUX_PG[2] = 0         PG2       PIO Port G[2], when PINMUX_PG[2] = 1         129       NDACK0       I/O       DMA Channel 0 Acknowledge, when PINMUX_PG[3]         PG3       PIO Port G[3], when PINMUX_PG[3] = 1       131       NDREQ1         I/O       DMA Channel 1 Request, when PINMUX_PG[4] = 0       PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                    | X PG[1] = 0               |

| Image: To ensure proper initialization after power is stable, assert NRESET pin for at least 20ms         127       NEXTACK       I/O       Bus Granted Signal for External Master, when PINMUX_PG[1] = 1         128       NDREQ0       I/O       DMA Channel 0 Request, when PINMUX_PG[2] = 0         129       NDACK0       I/O       DMA Channel 0 Acknowledge, when PINMUX_PG[3] = 1         131       NDREQ1       I/O       DMA Channel 1 Request, when PINMUX_PG[4] = 0         131       PG4       PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X PG[1] = 0               |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X PG[1] = 0               |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | X $PG[1] = 0$             |

| PG1PIO Port G[1] = 1, when PINMUX_PG[1] = 1128NDREQ0I/ODMA Channel 0 Request, when PINMUX_PG[2] = 0PG2PIO Port G[2], when PINMUX_PG[2] = 1129NDACK0I/ODMA Channel 0 Acknowledge, when PINMUX_PG[3]PG3PIO Port G[3], when PINMUX_PG[3] = 1131NDREQ1I/ODMA Channel 1 Request, when PINMUX_PG[4] = 0PG4PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\Lambda I U I I = 0 I$   |

| 128NDREQ0I/ODMA Channel 0 Request, when PINMUX_PG[2] = 0PG2PG2PIO Port G[2], when PINMUX_PG[2] = 1129NDACK0I/ODMA Channel 0 Acknowledge, when PINMUX_PG[3]PG3PIO Port G[3], when PINMUX_PG[3] = 1131NDREQ1I/ODMA Channel 1 Request, when PINMUX_PG[4] = 0PG4PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |

| PG2         PIO Port G[2], when PINMUX_PG[2] = 1           129         NDACK0         I/O         DMA Channel 0 Acknowledge, when PINMUX_PG[3]           PG3         PIO Port G[3], when PINMUX_PG[3] = 1           131         NDREQ1         I/O           PG4         PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           |

| 129     NDACK0     I/O     DMA Channel 0 Acknowledge, when PINMUX_PG[3]       PG3     PIO Port G[3], when PINMUX_PG[3] = 1       131     NDREQ1     I/O       PG4     PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |

| PG3         PIO Port G[3], when PINMUX_PG[3] = 1           131         NDREQ1         I/O         DMA Channel 1 Request, when PINMUX_PG[4] = 0           PG4         PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 – 0                     |

| 131NDREQ1I/ODMA Channel 1 Request, when PINMUX_PG[4] = 0PG4PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ] = 0                     |

| PG4 PIO Port G[4], when PINMUX_PG[4] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 - 0                     |

| PG5 PIO Port G[5], when PINMUX_PG[5] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ] = 0                     |

| $133 \qquad \text{NRASO} \qquad \text{I/O} \qquad \text{DRAM Bank #0 RAS Signal, when PINMUX_PG[6]} =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - 0                       |

| PG6 PIO Port G[6], when PINMUX_PG[6] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 0                       |

| 135 NRAS1 I/O DRAM Bank #1 RAS Signal, when PINMUX_PG[7] =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 0                       |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - 0                       |

| 136 NCASO I/O DRAM CASO Signal, when PINMUX_PH[0] = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                           |

| PHO PIO Port H[0], when PINMUX_PH[0] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |

| 137 NCAS1 I/O DRAM CAS1 Signal, when PINMUX_PH[1] = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                           |

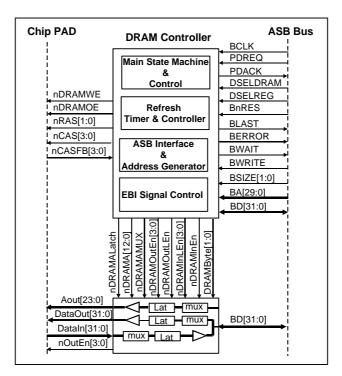

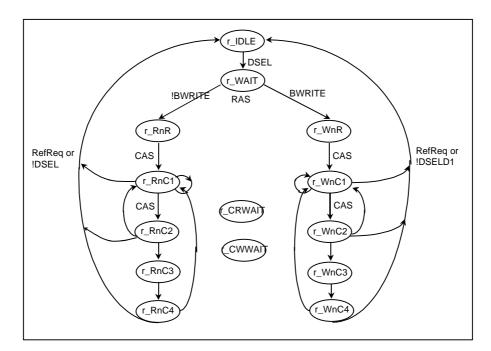

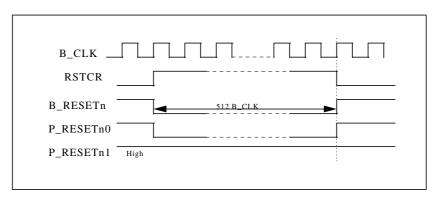

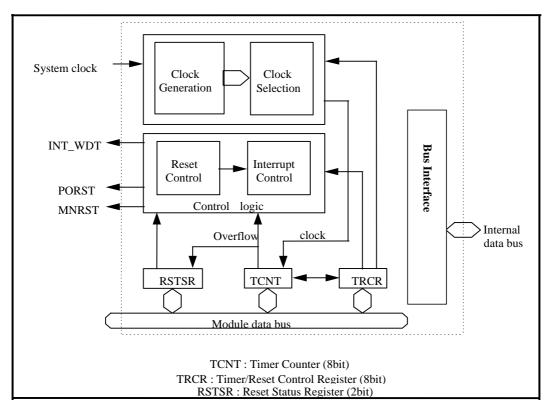

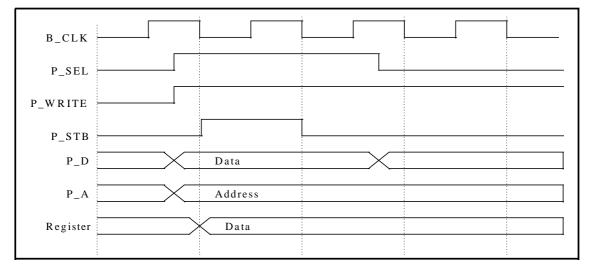

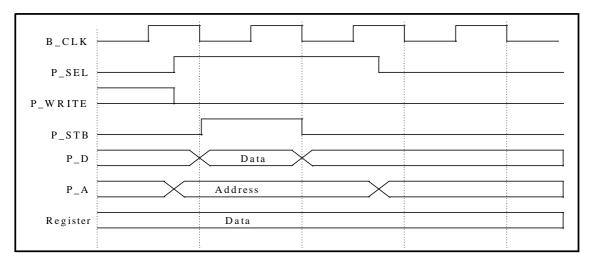

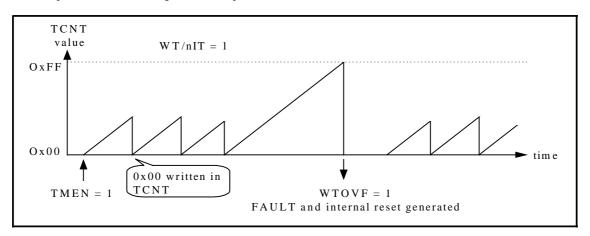

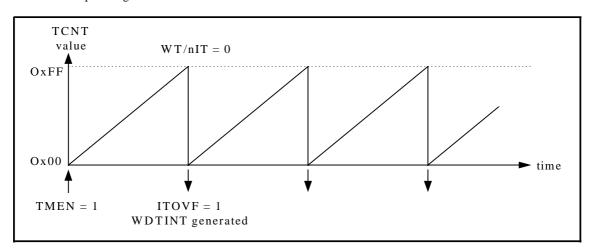

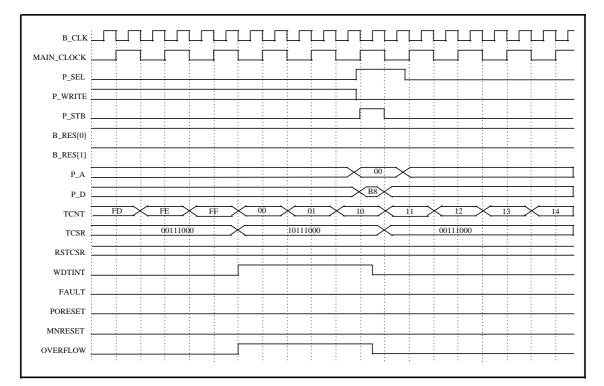

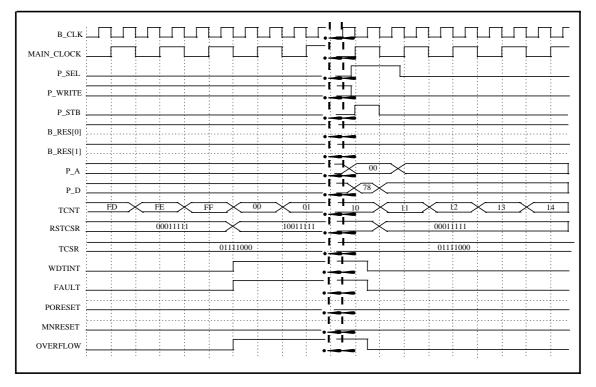

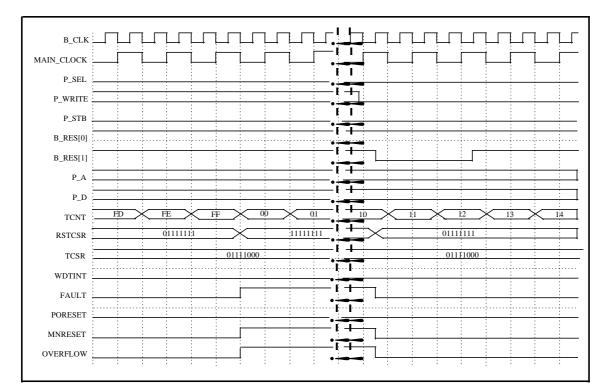

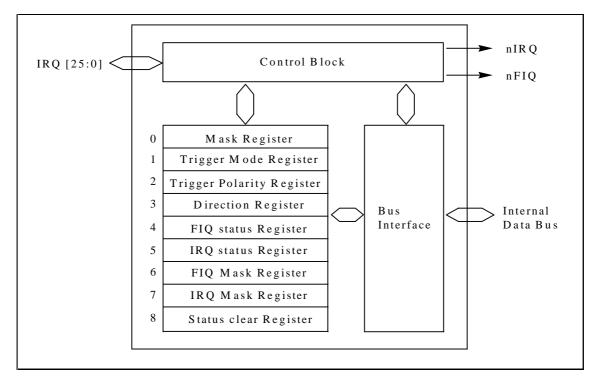

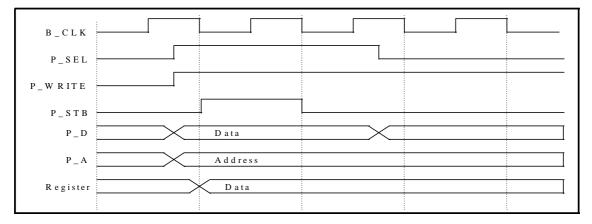

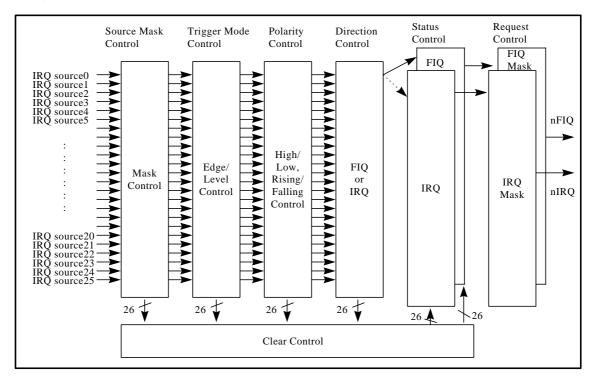

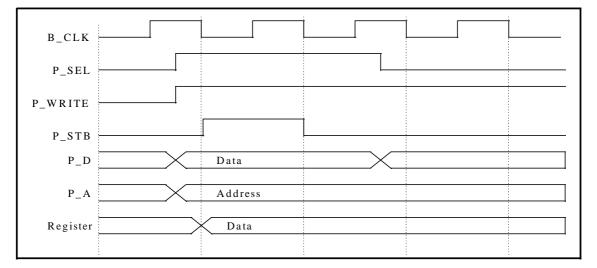

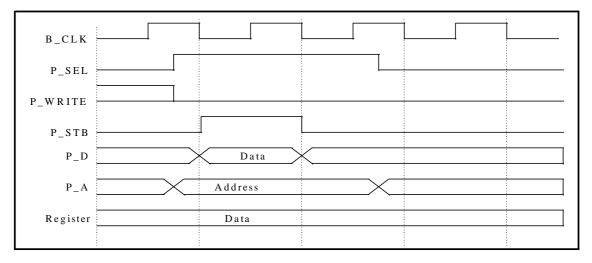

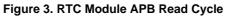

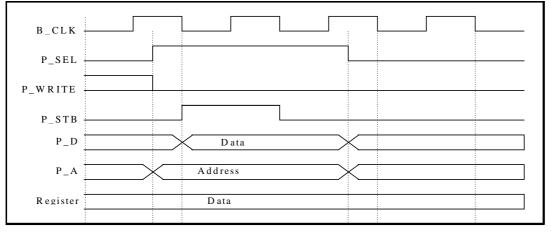

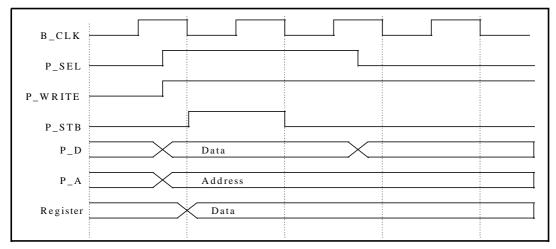

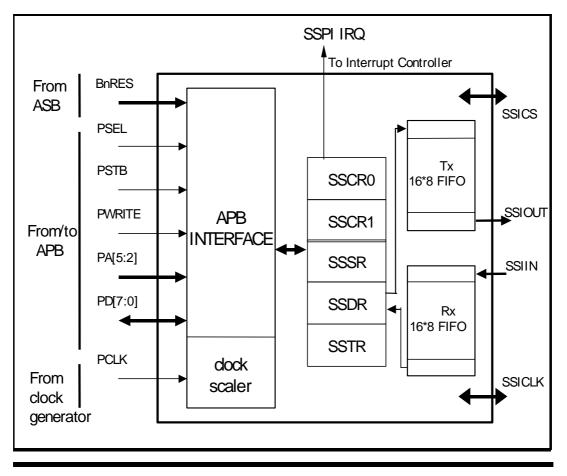

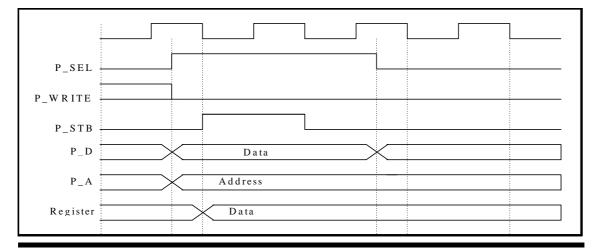

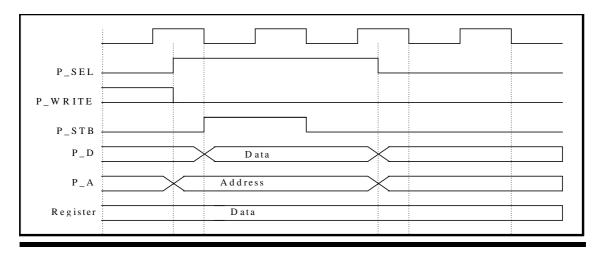

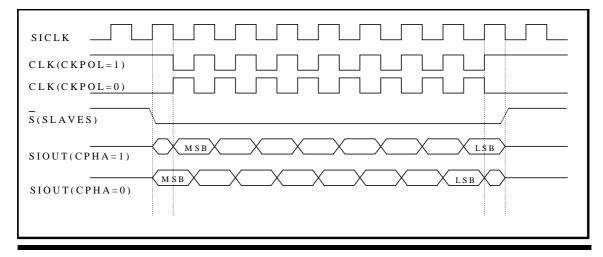

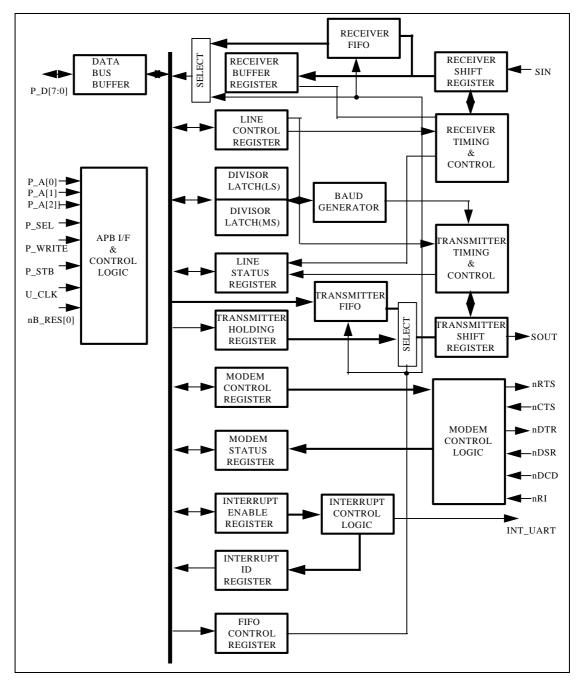

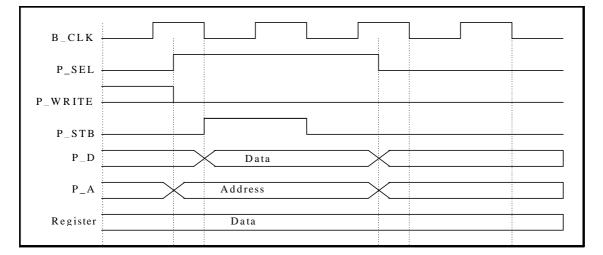

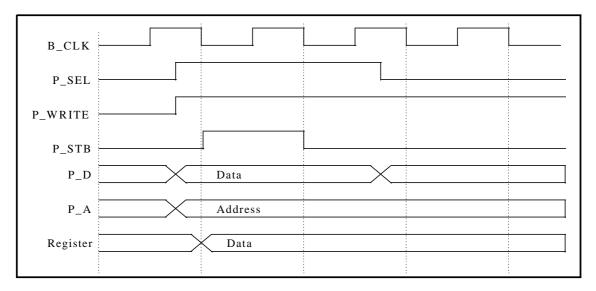

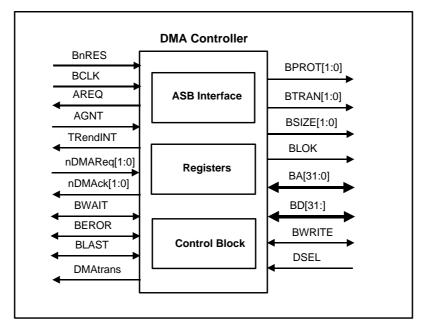

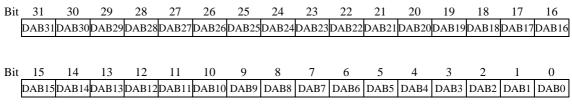

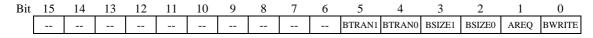

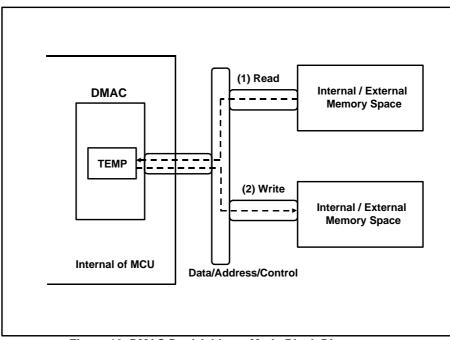

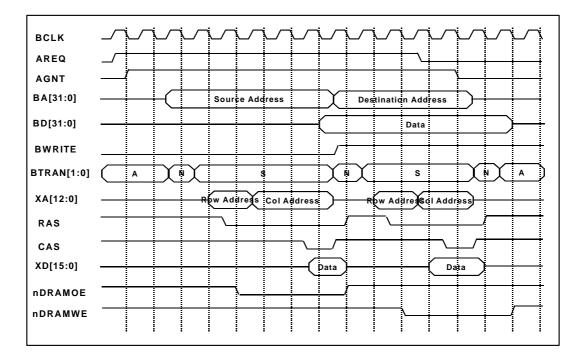

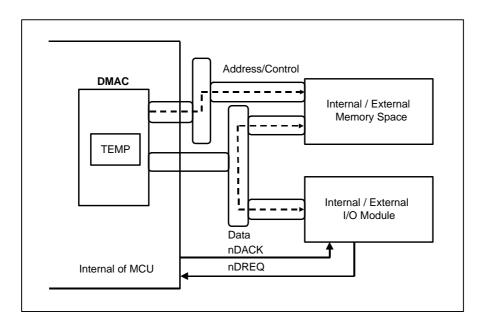

| PH1 PIO Port H[1], when PINMUX_PH[1] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |