HI-8588-10

January 2001

# **ARINC 429 LINE RECEIVER**

### DESCRIPTION

The HI-8588-10 ARINC 429 bus interface receiver is similar to the HI-8588 with the exception that it allows an external 10 Kohm resistor in series with each ARINC input without affecting the ARINC input thresholds. The product is especially useful in applications where lightning protection circuitry is also required. In addition, the test inputs force both of the outputs to zero instead open circuit. The analog/digital CMOS product requires only a 5 volt supply and is available in a SO 8 pin package.

Each side of the ARINC bus <u>must</u> be connected through a 10 Kohm series resistor in order for the chip to detect the correct ARINC levels. The typical 10 volt differential signal is translated and input to a window comparator and latch. The comparator levels are set so that with the external 10 Kohm resistors they are just below the standard 6.5 volt minimum ARINC data threshold and just above the standard 2.5 voltmaximum ARINC null threshold.

The TESTA and TESTB inputs bypass the analog inputs for testing purposes. Also if TESTA and TESTB are both taken high, the digital outputs are forced to zero.

# **FEATURES**

- ARINC 429 line receiver interface in a small outline package

- Lightning protection simplified with the ability to add 10 Kohm external series resistors

- Receiver input hystersis at least 2 volts

- Test inputs bypass analog inputs and force digital outputs to an one, zero or null state

- Plastic and ceramic package options surface mount and DIP

- Mil processing available

# **PIN CONFIGURATION**

|         | $\overline{}$ | 1       |

|---------|---------------|---------|

| VCC 1   | •             | 8 TESTB |

| TESTA 2 |               | 7 ROUTB |

| RINB 3  |               | 6 ROUTA |

| RINA 4  |               | 5 GND   |

|         |               |         |

### SUPPLY VOLTAGES

$VCC = 5.0V \pm 5\%$

## **FUNCTION TABLE**

#### RECEIVER

| RINA            | RINB            | TESTA | TESTB | ROUTA | ROUTB |

|-----------------|-----------------|-------|-------|-------|-------|

| -1.25V to 1.25V | -1.25V to 1.25V | 0     | 0     | 0     | 0     |

| -3.25V to -6.5V | 3.25V to 6.5V   | 0     | 0     | 0     | 1     |

| 3.25V to 6.5V   | -3.25V to -6.5V | 0     | 0     | 1     | 0     |

| Х               | Х               | 0     | 1     | 0     | 1     |

| Х               | Х               | 1     | 0     | 1     | 0     |

| Х               | Х               | 1     | 1     | 0     | 0     |

#### PIN DESCRIPTION TABLE

| PIN | SYMBOL | FUNCTION     | DESCRIPTION            |

|-----|--------|--------------|------------------------|

| 1   | VCC    | SUPPLY       | 5 VOLT SUPPLY          |

| 2   | TESTA  | LOGIC INPUT  | CMOS                   |

| 3   | RINB   | ARINC INPUT  | RECEIVER B INPUT       |

| 4   | RINA   | ARINC INPUT  | RECEIVER A INPUT       |

| 5   | GND    | POWER        | GROUND                 |

| 6   | ROUTA  | LOGIC OUTPUT | RECEIVER CMOS OUTPUT A |

| 7   | ROUTB  | LOGIC OUTPUT | RECEIVER CMOS OUTPUT B |

| 8   | TESTB  | LOGIC INPUT  | CMOS                   |

## **FUNCTIONAL DESCRIPTION**

#### **RECEIVER**

Figure 1 shows the general architecture of the ARINC 429 receiver. The receiver operates off the VCC supply only. The inputs RINA and RINB each require  $35 \mathrm{K}\Omega$  of resistance of which  $25 \mathrm{K}\Omega$  is internal to the chip. The series resistance is connected to level translators whose resistance to Ground is typically  $10 \mathrm{K}\Omega$ . In order for the voltage translation not to be adversely affected, an external  $10 \mathrm{K}\Omega$  series resister must be added to each ARINC input. The HI-8588-10 device is typically chosen for applications where external series resistors are required in its lightning protection circuitry.

After level translation, the inputs are buffered and become inputs to a differential amplifier. The amplitude of the differential signal is compared to levels derived from a divider

between VCC and Ground. The nominal settings correspond to a One/Zero amplitude of 6.0V and a Null amplitude of 3.3V.

The status of the ARINC receiver input is latched. A Null input resets the latches and a One or Zero input sets the latches.

The logic at the output is controlled by the test signal which is generated by the logical OR of the TestA and TestB pins. Unlike the HI-8588, if TestA and TestB are both One, the HI-8588-10 outputs are pulled low instead of being tri-stated. This allows the digital outputs of a transmitter to be connected to the test inputs through control logic for self-test purposes.

FIGURE 1 - RECEIVER BLOCK DIAGRAM

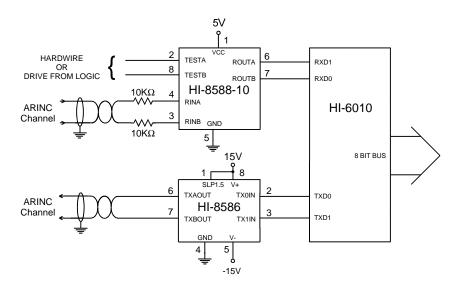

#### **APPLICATION INFORMATION**

Figure 2 shows a possible application of the HI-8588 interfacing an ARINC receive channel to the HI-6010 which in turn interfaces to an 8-bit bus.

FIGURE 2 - APPLICATION DIAGRAM

## **ABSOLUTE MAXIMUM RATINGS**

## **RECOMMENDED OPERATING CONDITIONS**

Voltages referenced to Ground

| Supply voltages VCC7V                                       |

|-------------------------------------------------------------|

| ARINC input - pins 3 & 4  Voltage at either pin+29V to -29V |

| DC current per input pin ±10mA                              |

| Power dissipation at 25°C plastic DIL0.7W ceramic DIL0.5W   |

| Solder Temperature275°C for 10 sec                          |

| Storage Temperature65°C to +150°C                           |

| Supply Voltages VCC5V ± 5%                                                                                           |

|----------------------------------------------------------------------------------------------------------------------|

| Temperature Range Industrial Screening40°C to +85°C Hi-Temp Screening55°C to +125°C Military Screening55°C to +125°C |

NOTE: Stresses above absolute maximum ratings or outside recommended operating conditions may cause permanent damage to the device. These are stress ratings only. Operation at the limits is not recommended.

#### DC ELECTRICAL CHARACTERISTICS

OPERATING TEMPERATURE RANGE, VCC = 5.0V UNLESS OTHERWISE STATED

| PARAMETERS                 | SYMBOL            | TEST CONDITIONS                                      | MIN | TYP  | MAX  | UNITS |

|----------------------------|-------------------|------------------------------------------------------|-----|------|------|-------|

| ARINC input voltage        |                   |                                                      |     |      |      |       |

| one or zero                | V <sub>DIN</sub>  | diff. volt. thru $10 \text{K}\Omega$ , pins $3 \& 4$ | 6.5 | 10   | 13   | volts |

| null                       | V <sub>NIN</sub>  | " " "                                                | -   | -    | 2.5  | volts |

| common mode                | <sup>V</sup> COM  | with respect to Ground                               | 1   | -    | 5.0  | volts |

| logic input voltage        |                   |                                                      |     |      |      |       |

| high                       | V ⊪               |                                                      | 3.5 | -    | -    | volts |

| low                        | V <sub>IL</sub>   |                                                      | -   | -    | 1.5  | volts |

| ARINC input resistance     |                   |                                                      |     |      |      |       |

| RINA to RINB               | R <sub>DIFF</sub> | supplies floating & series $10 \text{K}\Omega$       | 30  | 75   | -    | Kohm  |

| RINA or RINB to Gnd or VCC | R <sub>SUP</sub>  | 11 11 11                                             | 19  | 40   | -    | Kohm  |

| logic input current        |                   |                                                      |     |      |      |       |

| source                     | I <sub>IH</sub>   | V <sub>IN</sub> = 0 V                                | -   | -    | 0.1  | μΑ    |

| sink                       | I <sub>IL</sub>   | V <sub>IN</sub> = 5 V                                | -   | -    | 0.1  | μΑ    |

| logic output drive current |                   |                                                      |     |      |      |       |

| one                        | ГОН               | V <sub>OH</sub> = 4.6V                               | -   | -1.6 | -0.8 | mA    |

| zero                       | IOL               | $V_{OH} = 4.6V$<br>$V_{OL} = 0.4V$                   | 3.6 | 5.6  |      | mA    |

| Current drain              |                   |                                                      |     |      |      |       |

| operating                  | I <sub>CC1</sub>  | pins 2, 8 = 0V; pins 3, 4 open                       | -   | 2.3  | 6.3  | mA    |

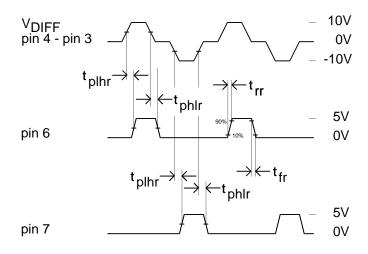

# **AC ELECTRICAL CHARACTERISTICS**

OPERATING TEMPERATURE RANGE, VCC = 5.0V UNLESS OTHERWISE STATED

| PARAMETERS                       | SYMBOL          | TEST CONDITIONS                            | MIN | TYP | MAX | UNITS |

|----------------------------------|-----------------|--------------------------------------------|-----|-----|-----|-------|

| Receiver propagation delay       |                 | defined in Figure 3, C <sub>L</sub> = 50pF |     |     |     |       |

| Output high to low               | t phir          |                                            | -   | 600 | -   | ns    |

| Output low to high               | t plhr          |                                            | -   | 600 | -   | ns    |

| Receiver output transition times |                 |                                            |     |     |     |       |

| Output high to low               | t fr            |                                            | -   | 50  | 80  | ns    |

| Output low to high               | t rr            |                                            | ı   | 50  | 80  | ns    |

| Input capacitance (1)            |                 |                                            |     |     |     |       |

| ARINC differential               | C <sub>AD</sub> |                                            | -   | 5   | 10  | pF    |

| ARINC single ended to Ground     | C <sub>AS</sub> |                                            | -   | -   | 10  | pF    |

| Logic                            | C <sub>IN</sub> |                                            | -   | -   | 10  | pF    |

#### Notes:

1. Guaranteed but not tested

FIGURE 3 - RECEIVER TIMING

#### **ORDERING INFORMATION**

| PART<br>NUMBER | PACKAGE<br>DESCRIPTION         | TEMPERATURE RANGE | FLOW | BURN<br>IN | LEAD<br>FINISH |  |  |

|----------------|--------------------------------|-------------------|------|------------|----------------|--|--|

| HI-8588PDI-10  | 8 PIN PLASTIC DIP              | -40°C TO +85°C    | I    | NO         | SOLDER         |  |  |

| HI-8588PDT-10  | 8 PIN PLASTIC DIP              | -55°C TO +125°C   | Т    | NO         | SOLDER         |  |  |

| HI-8588PSI-10  | 8 PIN PLASTIC NARROW BODY SOIC | -40°C TO +85°C    | - 1  | NO         | SOLDER         |  |  |

| HI-8588PST-10  | 8 PIN PLASTIC NARROW BODY SOIC | -55°C TO +125°C   | Т    | NO         | SOLDER         |  |  |

| HI-8588CDI-10  | 8 PIN CERAMIC SIDE BRAZED DIP  | -40°C TO +85°C    | - 1  | NO         | GOLD           |  |  |

| HI-8588CDT-10  | 8 PIN CERAMIC SIDE BRAZED DIP  | -55°C TO +125°C   | Т    | NO         | GOLD           |  |  |

| HI-8588CDM-10  | 8 PIN CERAMIC SIDE BRAZED DIP  | -55°C TO +125°C   | М    | YES        | SOLDER         |  |  |

| HI-8588CRI-10  | 8 PIN CERDIP                   | -40°C TO +85°C    | - 1  | NO         | SOLDER         |  |  |

| HI-8588CRT-10  | 8 PIN CERDIP                   | -55°C TO +125°C   | Т    | NO         | SOLDER         |  |  |

| HI-8588CRM-10  | 8 PIN CERDIP                   | -55°C TO +125°C   | М    | YES        | SOLDER         |  |  |

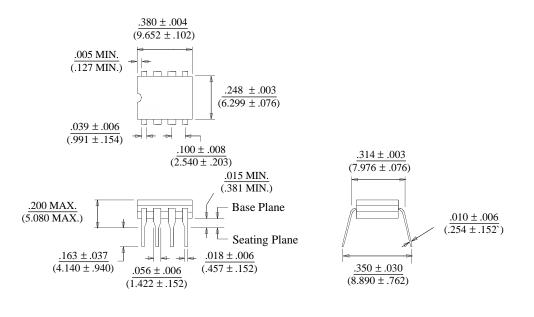

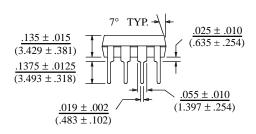

# HI-8588-10 PACKAGE DIMENSIONS

inches (millimeters)

#### 8-PIN PLASTIC DIP

Package Type: 8P

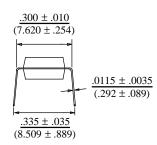

# 8-PIN PLASTIC SMALL OUTLINE (SOIC) - NB

(Narrow Body)

Package Type: 8HN

Detail A

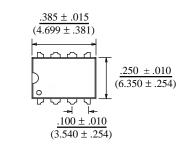

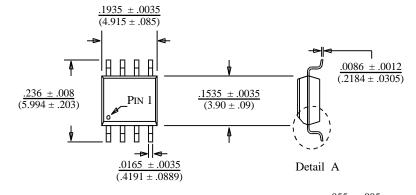

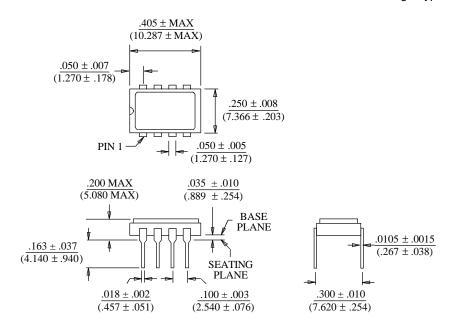

# HI-8588-10 PACKAGE DIMENSIONS

inches (millimeters)

#### 8-PIN CERAMIC SIDE-BRAZED DIP

Package Type: 8C

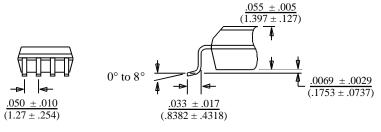

#### **8-PIN CERDIP**

Package Type: 8D