# Integrated Circuit Systems, Inc.

# **ICS1531**

Document Type: Data Sheet

Document Stage: Preliminary Product Preview

# Triple 8-bit MSPS A/D Converters with Line-Locked Clock Generator

## **General Description**

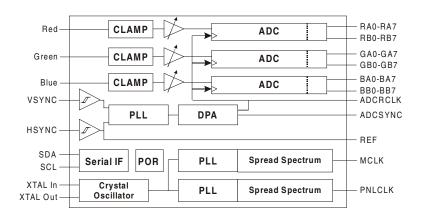

The ICS1531 is a high-performance, cost-effective, 3-channel, 8-bit analog-to-digital converter with an integrated line-locked clock generator. It is part of a family of chips intended for high-resolution video applications that use analog inputs, such as LCD monitors, LCD projectors, plasma displays, and projection TVs. Using ICS's low-voltage CMOS mixed-signal technology, the ICS1531 is an effective data-capture solution for resolutions from VGA to UXGA.

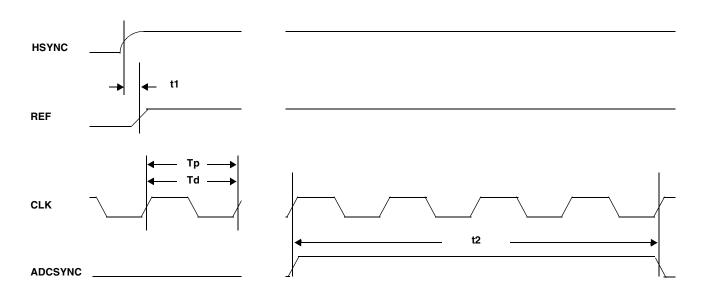

The ICS1531 offers analog-to-digital data conversion and synchronized pixel clock generation at speeds of 100, 140, or 165 MHz (or mega samples per second, MSPS). The Dynamic Phase Adjust (DPA) circuitry allows end-user control over the pixel clock phase, relative to the recovered sync signal and analog pixel data. Either the internal pixel clock can be used as a capture clock input to the analog-to-digital converters or an external clock input can be used. The ICS1531 provides either one or two 24-bit pixels per clock. An ADCSYNC output pin provides recovered HSYNC from the pixel clock phase-locked-loop (PLL) divider chain output, which can be used to synchronize display enable output.

A clamp signal can be generated internally or provided through the CLAMP pin. A high-bandwidth video amplifier with adjustable gain allows fine tuning of the analog signal. The advanced PLL uses an internal programmable feedback divider. Two additional, independent programmable PLLs, each with spread-spectrum functionality, support memory and panel clock requirements.

#### **Features**

- 3-channel 8-bit analog-to-digital conversion up to 165 MHz

- Direct connection to analog input data (no external pre-amplifier circuit needed)

- Video amplifier: 500-MHz analog bandwidth, software-adjustable gain

- Dynamic Phase Adjust (DPA) for software-adjustable analog sample points

- Software selectable: One pixel per clock (for 24-bit pixels) or two pixels per clock (for a total of 48 bits)

- Internal clamp circuit. Very low jitter.

- Low-voltage TTL clock outputs, synchronized with digital pixel data outputs

- Independent software reset for PLLs and DPA

- Double-buffered PLL and DPA control registers

- Two additional PLLs with spread spectrum for memory and panel clock

- External/internal loop-filter selection with software

- Automatic Power-On Reset (POR) detection

- Uses 3.3 VDC. Digital inputs are 5-V tolerant.

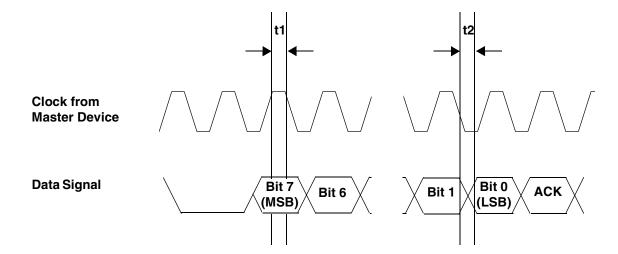

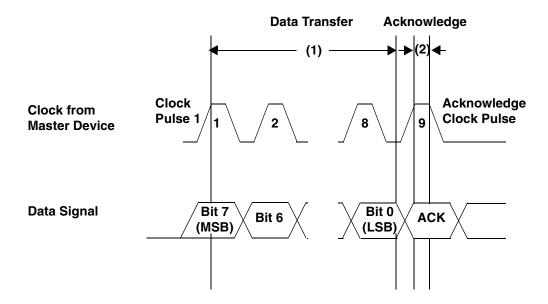

- Industry-standard 2-wire serial bus interface speeds: low (100 kHz), high (400 kHz), or ultra (800 kHz)

- Lock detection available in hardware and software

- 144-pin low-profile quad flat pack (LQFP) package

#### **Applications**

LCD displays, LCD projectors, plasma displays, and projection TVs

ICS1531 Functional Block Diagram

# **Table of Contents**

| <u>Section</u> | <u>Title</u>                    | <u>Page</u> |

|----------------|---------------------------------|-------------|

| Chapter 1      | Abbreviations and Acronyms      | 3           |

| Chapter 2      | Summary                         | 4           |

| Chapter 3      | Pin Diagram and Listings        | 9           |

| Chapter 4      | Functional Blocks               | 19          |

| Chapter 5      | Application Overview            | 22          |

| Chapter 6      | Register Set                    | 23          |

| Chapter 7      | Programming                     | 54          |

| Chapter 8      | Layout and Power Considerations | 58          |

| Chapter 9      | AC/DC Operating Conditions      | 61          |

| Chapter 10     | Timing Diagrams                 | 63          |

| Chapter 11     | VCO Transfer Characteristic     |             |

| Chapter 12     | Package Dimensions              | 71          |

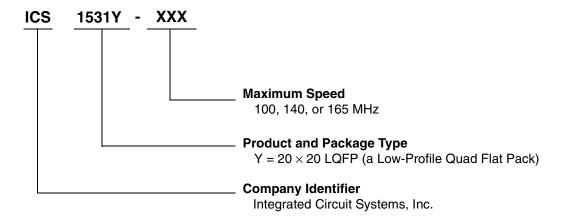

| Chapter 13     | Ordering Information            | 73          |

# **Chapter 1 Abbreviations and Acronyms**

Table 1-1 lists and interprets the abbreviations and acronyms used throughout this data sheet.

Table 1-1. Abbreviations and Acronyms

| Abbreviation / Acronym | Interpretation                                                         |

|------------------------|------------------------------------------------------------------------|

| ADC                    | analog-to-digital converter                                            |

| ASIC                   | application-specific integrated circuit                                |

| BNC                    | Type of connector, named for ("Bayonet") Paul Neill and Carl Concelman |

| CMOS                   | complimentary metal-oxide semiconductor                                |

| DAC                    | digital-to-analog converter                                            |

| DPA                    | Dynamic Phase Adjust                                                   |

| EMI                    | electro-magnetic interference                                          |

| FCC                    | (United States) Federal Communications Commission                      |

| IF                     | interface                                                              |

| LCD                    | liquid crystal display                                                 |

| LQFP                   | low-profile quad flat pack                                             |

| LSB                    | least-significant bit                                                  |

| LVTTL                  | low-voltage digital transistor-transistor logic                        |

| Max.                   | maximum                                                                |

| Min.                   | minimum                                                                |

| MSB                    | most-significant bit                                                   |

| MSPS                   | mega samples per second                                                |

| MUX                    | multiplexer                                                            |

| N/A                    | Not Applicable                                                         |

| PC                     | personal computer                                                      |

| PFD                    | phase/frequency detector                                               |

| PLL                    | phase-locked loop                                                      |

| POR                    | power-on reset                                                         |

| Reg                    | register                                                               |

| RGB                    | red, green, blue                                                       |

| R/W                    | read/write                                                             |

| SXGA                   | super XGA                                                              |

| TTL                    | transistor-transistor logic                                            |

| Тур.                   | typical                                                                |

| UXGA                   | ultra XGA                                                              |

| VCO                    | voltage-controlled oscillator                                          |

| VESA                   | Video Electronics Standards Association                                |

| VGA                    | video graphics array                                                   |

| XGA                    | eXtended graphics array                                                |

# **Chapter 2 Summary**

### 2.1 Overview

The ICS1531 addresses stringent display system line-locked applications by providing clock signals and digitized pixel data through internal high-performance analog-to-digital converters (ADCs). The ICS1531 is a complete solution for capturing analog red, green, and blue (RGB) signals from personal computers and workstations. It supports data capture for resolutions from VGA ( $640 \times 480$ ) to UXGA ( $1600 \times 1200$ ). The ICS1531 features are described in the following sections.

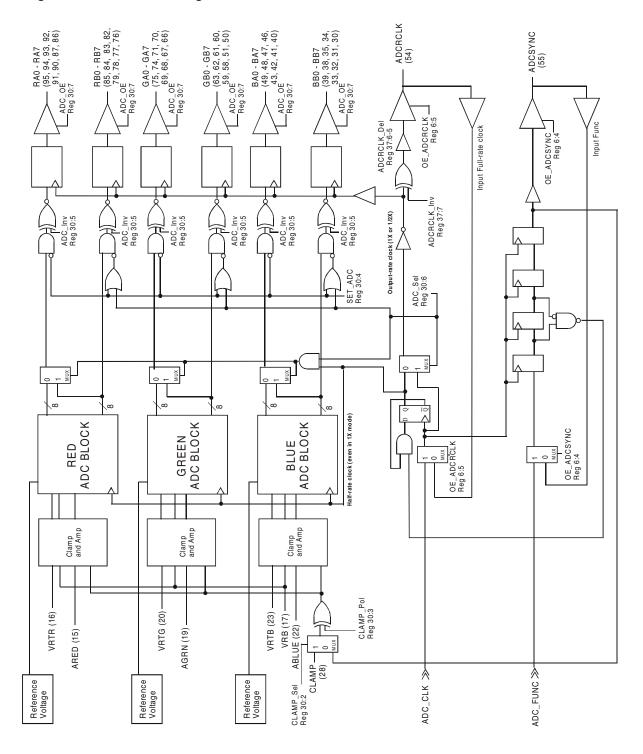

## 2.2 Clamp, Video Amplifier, and Analog-to-Digital Circuits (Condition RGB Inputs)

For the following circuits, see Figure 4-3.

#### 2.2.1 Clamp Circuits (Adjust RGB Inputs to ADC Range)

To properly digitize incoming RGB analog signals, the ICS1531 must adjust the signals to the range of the ADC. This adjustment is done by clamping the signal, which both (1) establishes a bottom voltage limit and (2) offsets the signal to align the black level of the incoming signal with the bottom voltage limit. Then the signal is amplified to adjust the top limit to the upper range of the ADC.

The ICS1531 incorporates an internal clamping circuit to generate a clamping signal. Optionally, the CLAMP pin can be used to input an externally generated clamp signal (Reg 30:2). In either case, the polarity of the signal to a clamp can be programmed (Reg 30:3). Typically, the clamp signal is generated by ADCSYNC (the recovered HSYNC timing pulse). The clamp signal is generated during a non-display region of time, when most PC display controllers output a black signal.

#### 2.2.2 Video Amplifier Circuits (Amplify RGB Inputs)

The ICS1531's video amplifier circuit can directly accept analog RGB input signals from a PC display controller (that is, no external pre-amplifier is required). The video amplifier circuit has three independent 500-MHz video amplifiers for the RGB inputs. To adjust the top level of the signal, this video amplifier circuit can be programmed for a gain of 1.0, 1.2, 1.4, or 1.6 (Regs 31:1-0, 32:1-0, and 33:1-0). As a result, the video amplifier circuit can improve low-amplitude signals and adjust analog input signals for the optimum sampling range of the ADC circuit.

## 2.2.3 Analog-to-Digital Circuits (Digitize RGB Inputs)

The ICS1531 has high-performance analog-to-digital converters (ADCs) to capture and digitize analog RGB data (Reg 30:7). Low-power CMOS technology is used to create 8-bit ADCs, which are calibrated to align the capture event between (1) the 3 analog input channels and (2) either 3 or 6 digital output channels. The ADC can provide (through Reg 30:6) one of the following:

- Two 24-bit pixels aligned to a half-rate pixel clock (two-pixels-per-clock mode), which can be used for 48-bit interface panels and image-scaling chips

- One 24-bit pixel aligned to a full-rate pixel clock (one-pixel-per-clock mode), which can be used for 24-bit-per-pixel applications

In addition, programmable digital-to-analog converters for the R, G, and B inputs fine-tune VRTR, VRTG, and VRTB, the individual R, G, and B maximum reference 'top' voltages (Regs 34-36).

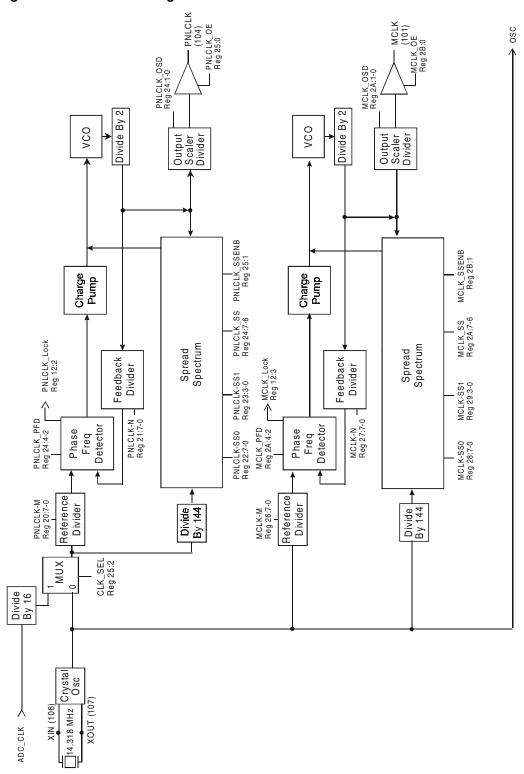

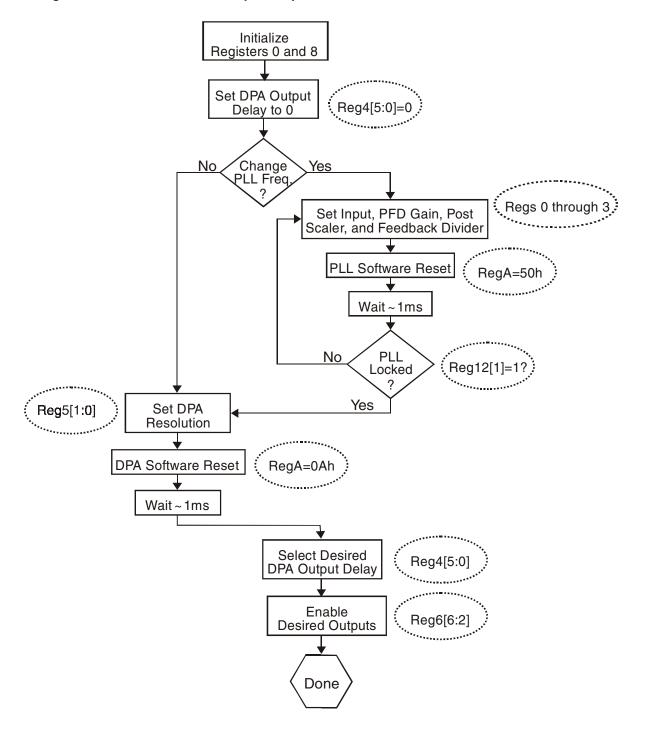

# 2.3 Phase-Locked Loop (Generates Pixel Clock from Input HSYNC)

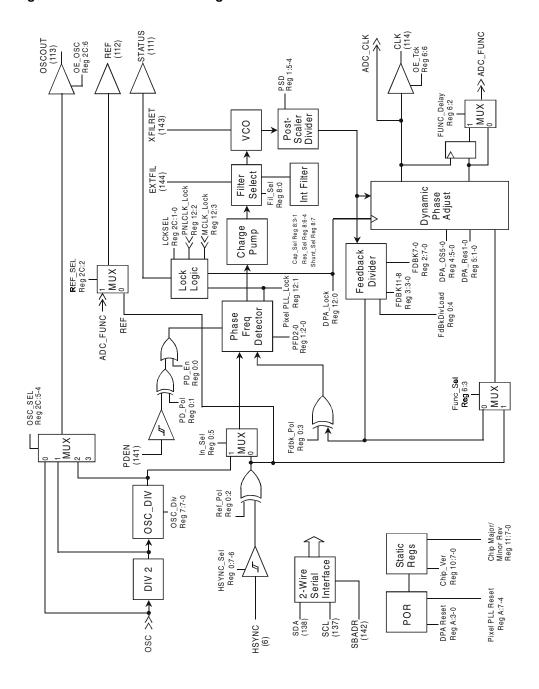

The ICS1531 uses a phase-locked loop (PLL) to generate its pixel clock output frequency. A PLL is a closed-loop feedback system that locks an output signal's phase and frequency to that of a reference input signal's phase and frequency. In the case of the ICS1531, when its PLL is locked it locks a pixel clock output to that of an HSYNC signal from input video. For a block diagram of the ICS1531 PLL, see Figure 4-1 and Figure 4-2.

## 2.3.1 Phase/Frequency Detector (Compares Two Input Signals)

The first section of the PLL is the Phase/Frequency Detector (PFD). To use the PLL, first the PFD must be enabled either through hardware control (with a signal from the PDEN pin) or software control (Reg 00:1-0). Once the PFD is enabled, the PFD compares both the phase and frequency of the following two input signals.

### • PFD Input Signal 1: External HSYNC Signal or Internal Oscillator Signal

The first input to the PFD can be selected from either the external HSYNC signal or the ICS1531 internal crystal oscillator signal (Reg 00:5).

- External HSYNC signal

- Typically, one of the input signals to the PFD comes from the HSYNC of a PC display controller. This input HSYNC signal can have a transition time of tens of nanoseconds. Furthermore, if the input HSYNC signal is from a remote source, its pulses can degrade.

- A high-performance Schmitt trigger (Reg 00:7-6) conditions the HSYNC pulse before it is input to the PFD. The polarity of this input pulse can be programmed (Reg 00:2). The result of this conditioning is REF, a clean reference clock signal that in comparison to the input HSYNC signal has a short transition time. [For more information on adjusting the HSYNC signal, see Section 2.6, "Dynamic Phase Adjust (Positions Pixel Clock on Sub-Pixel Basis)".]

- Internal crystal oscillator

Alternatively, one of the input signals to the PFD can be from the ICS1531 internal crystal oscillator (Regs 07:7-0 and 2C:6-4).

#### • PFD Input Signal 2: Signal from Feedback Loop

The second input to the PFD comes from the output of the PLL feedback loop, which results from the processing that takes place with the charge pump, filter, voltage-controlled oscillator, post-scaler divider, and feedback divider. That is, the PLL output (the signal from the feedback loop) also appears as one of the two inputs to the PFD.

As a result of the comparison of the two input signals, the PFD processes the inputs so there is the proper ratio between them. Then the PFD uses the output to drive a charge pump.

#### 2.3.2 Charge Pump (Boosts Voltage Gain of Signal from PFD)

The charge pump, which is a current-source and current-sink pair, boosts the voltage gain of the signal from the PFD. This PFD signal gain is programmable over a 7-bit range up to 128 µA (Reg 01:2-0).

#### 2.3.3 Loop Filter (Filters Output from Charge Pump)

The loop filter, which is a capacitance and resistance in series, acts as a low-bandpass filter for the frequency output from the charge pump. The ICS1531 can select between either an external loop filter, or more typically, an internal loop filter (Reg 08:0). The advantage of the internal filter is that it can be used for all Video Electronics Standards Association (VESA) timing modes, for ease in manufacturing.

**Note:** VESA establishes standard timing specifications for the personal-computer industry. Although many computer manufacturers require that display controllers adhere to the VESA timing specifications, there is no enforcement. As a result, not all display controllers conform precisely to the VESA timing specifications.

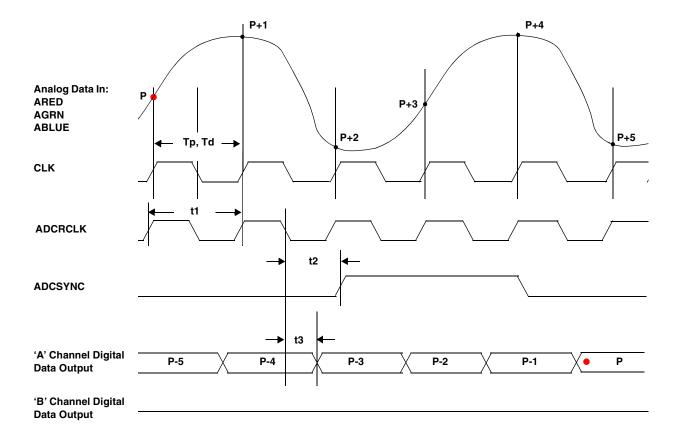

## 2.3.4 Voltage-Controlled Oscillator (Matches Input Signals to PFD)

The voltage level resulting from the output signals from the combined processing by the PFD, charge pump, and loop filter drives the voltage-controlled oscillator (VCO). The VCO uses the level of this input voltage to proportionally adjust its frequency output. This signal is compared to the input to the PFD so that both inputs to the PFD match in both phase and frequency. The VCO can operate up to nearly 600 MHz with a fixed gain. Consequently, the ICS1531 can be optimized for the best performance at all operating frequencies. (For more information on the VCO, see Chapter 11, "VCO Transfer Characteristics".)

### 2.3.5 Post-Scaler Divider (Sets Ratio of VCO and Pixel Clock Frequencies)

Using the frequency output from the VCO, the programmable Post-Scaler Divider (PSD) can set the ratio of VCO frequency-to-pixel clock frequency at 2:1, 4:1, 8:1, or 16:1 (Reg 01:5-4). The maximum pixel clock output frequency is therefore 300 MHz. However, for practical applications, the analog-to-digital converter limits this output frequency to either 100, 140, or 165 MHz.

### 2.3.6 Feedback Divider (Controls Number of Pixel Clocks per HSYNC)

The ICS1531's internal 12-bit pixel Feedback Divider (Regs 02 and 03) controls the total number of pixel clocks per line (that is, between successive HSYNCs). The total number of pixels per line includes both displayed and non-displayed pixels.

Reg 06:2 can delay the recovered HYSNC signal (that is, ADCSYNC) by one input clock period. This delay has the effect of moving channel 'A' data to the 'B' channel output pins and the channel 'B' data to the 'A' channel output pins.

#### Note:

- As a starting point to capture analog RGB input from VESA-compliant sources, ICS recommends certain register settings for the software "\*.ics files" that come with the ICS1531 Register Tool. However, the Register Tool register settings are only a guide. (For more information on the ICS1531 Register Tool and its \*.ics.files, see the ICS1531 Demo Board Guide.)

- 2. The display manufacturer must provide a way to optimize the display for the particular display controller in use.

- 3. If the ICS1531 internal pixel PLL Feedback Divider is not set correctly, it can create visible errors on the display.

- To adjust the ICS1531 on a sub-pixel basis, see Section 2.6, "Dynamic Phase Adjust (Positions Pixel Clock on Sub-Pixel Basis)".

## 2.4 Analog-to-Digital Converter (Synchronizes Data Capture)

By using the internal 3-channel analog-to-digital converter (ADC), the ICS1531 internally provides the pixel clock needed to synchronize data capture. The pixel clock can be further processed by the Dynamic Phase Adjust. [For more information on the ADC, see Section 2.2.3, "Analog-to-Digital Circuits (Digitize RGB Inputs)" and Figure 4-3.] For the pixel clock to appear on the CLK pin, the pixel clock output must be enabled (Reg 06:6).

## 2.5 Additional PLLs, with Spread Spectrum (Drive Memory and Panel Data Clocks)

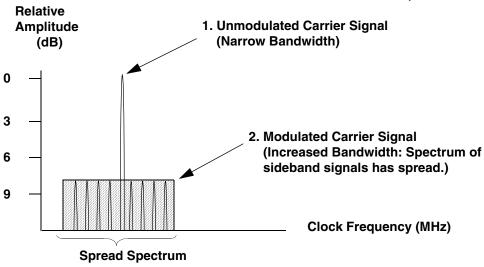

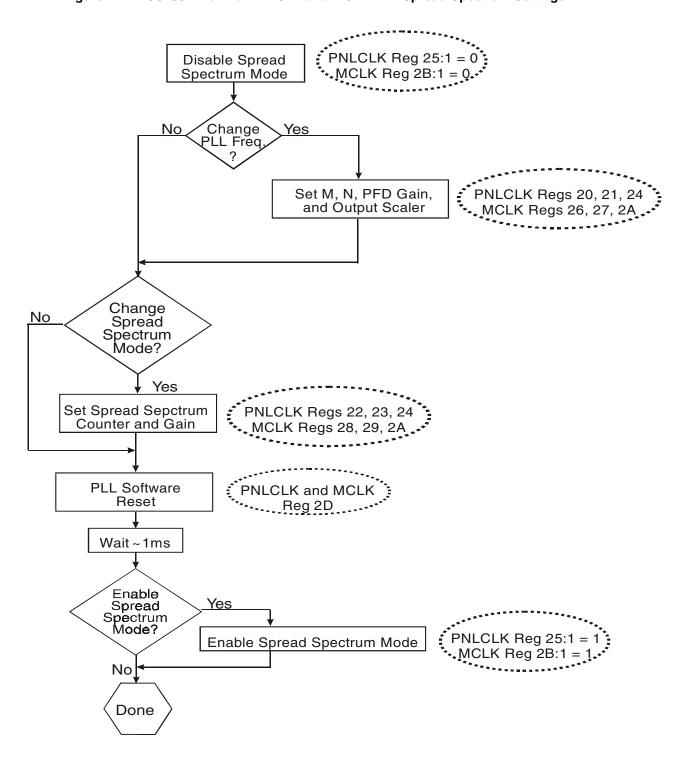

Besides the pixel clock PLL, the ICS1531 has two other independent PLLs for use as needed. Typically, one of the PLLs is used to drive memory clocks (Regs 26–2B and 2D) and the other PLL is used to drive panel data clocks (Regs 20–25 and 2D). Both of these additional PLLs are tailored for the required frequency ranges. Each supports software-controlled spread-spectrum clock dithering to reduce measured electro-magnetic interference (EMI).

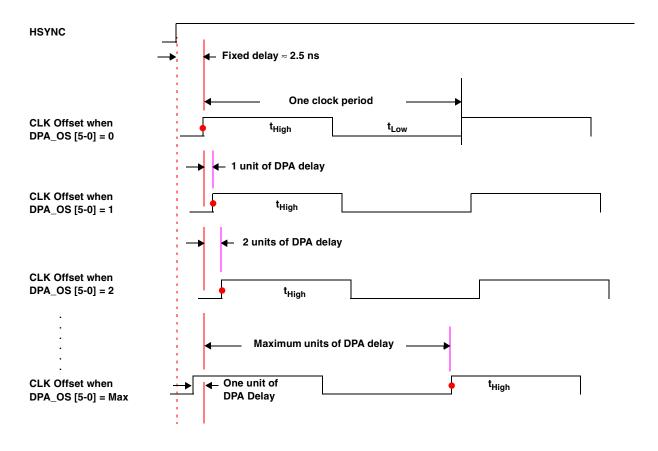

# 2.6 Dynamic Phase Adjust (Positions Pixel Clock on Sub-Pixel Basis)

Most display controllers provide an HSYNC signal that can be used as a reference signal for the pixel clock. However, when this HSYNC signal is used as an input, frequently it has significant jitter that impacts data capture. Furthermore, the analog data stream from the display controller to the ICS1531 has no pixel-rate reference clock.

So that analog pixel data inputs can be properly sampled and digitized, the ICS1531's pixel PLL tracks the input HSYNC signal and the line-to-line jitter. To provide a properly aligned sampling clock (ADCSYNC) to the ADC blocks, the ICS1531's Dynamic Phase Adjust (DPA) circuitry can add delays to the pixel clock position. The delay, which occurs in relation to the edge of ADCSYNC (the recovered HSYNC signal), is added in sub-pixel time increments.

Regs 04:5-0, 05:1-0 and 06 are used to program the ICS1531 DPA for a value representing incremental sub-pixel delay units. By choosing the proper value, pixel data to the ICS1531 can be sampled at the optimum time for proper digitization and the best-looking display. Typically, a system's microcontroller presets this value, based on either a table or proprietary algorithms. The end user can change the value through the system's on-screen display controls.

Table 2-1 lists the number of possible delay element units that can be used to program to add a delay of up to one pixel clock period, in increments of either 16, 32, or 64 (Reg 04:5-0 and Reg 5:1-0)

Table 2-1. Increments for Delay Element Units

| Number of<br>Delay Element Units | Pixel Clock Range, MHz |

|----------------------------------|------------------------|

| 16                               | 55 260                 |

| 32                               | 27 130                 |

| 64                               | 14 64                  |

**Note:** To adjust the ICS1531 on a pixel-by-pixel basis, see Section 2.3.6, "Feedback Divider (Controls Number of Pixel Clocks per HSYNC)".

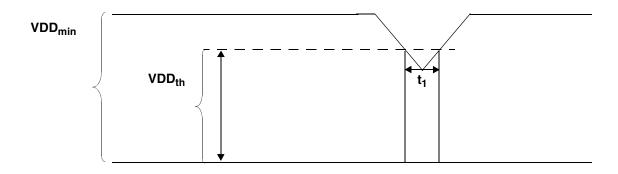

### 2.7 Automatic Power-On Reset Detection (Automatically Resets ICS1531)

The ICS1531 automatically detects power-on resets. As a result, the ICS1531 resets itself if the supply voltage drops below threshold values. No external connection to a reset signal is required.

#### 2.8 Logic Inputs and Outputs

- Inputs. The ICS1531 uses both of the following inputs:

- Analog inputs

- Digital inputs. The digital inputs are low-voltage TTL (LVTTL) inputs that operate at 3.3 V. These LVTTL inputs are also 5-V tolerant. (For inputs that are 5-V tolerant, see Section 3.2.3.10, "List of 5-V Tolerant Pins".)

- Outputs. The ICS1531 has high-speed LVTTL clock outputs.

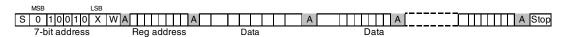

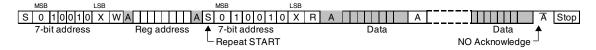

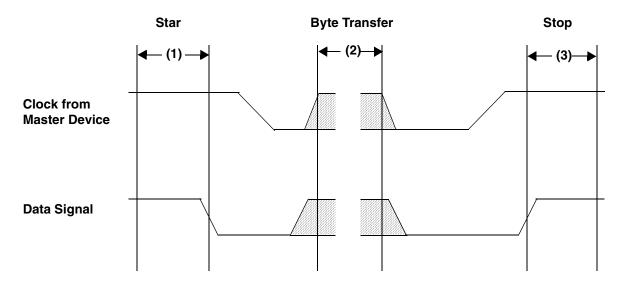

# 2.9 Industry-Standard 2-Wire Serial Interface

To access all its registers, the ICS1531 uses an industry-standard 2-wire serial interface that operates at one of the following speeds:

- A low speed of 100 kHz

- A high speed of 400 kHz

- An ultra speed of 800 kHz

For use with the 2-wire serial interface, the ICS1531 has 5 V-tolerant inputs. The ICS1531 can use either of two unique, alternative sets of addresses. Table 2-2 lists the addresses that can be used, depending on the state of the SBADR pin.

Table 2-2. ICS1531 Address Sets

| Addresses in<br>Address Set | Address Set 1.<br>(SBADR Pin Is Low) | Address Set 2.<br>(SBADR Pin Is High) |

|-----------------------------|--------------------------------------|---------------------------------------|

| 7-bit device address        | 24h                                  | 25h                                   |

| 8-bit read address          | 49h                                  | 4Bh                                   |

| 8-bit write address         | 48h                                  | 4Ah                                   |

# 2.10 Programmable Outputs

For general-purpose outputs, the ICS1531 provides three programmable pins, PSEL3, PSEL2, PSEL1 (Reg 37:2-0).

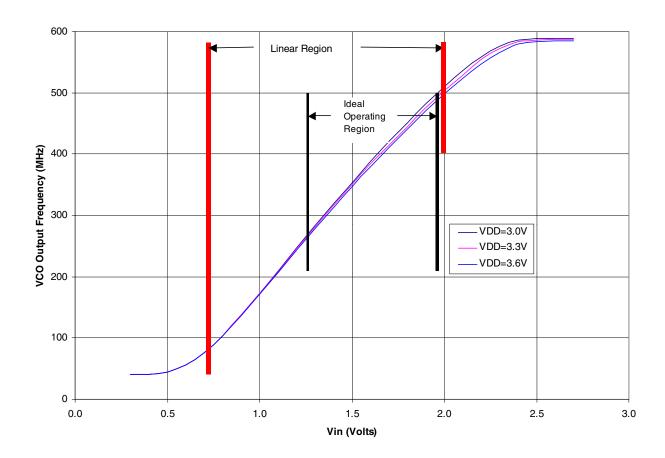

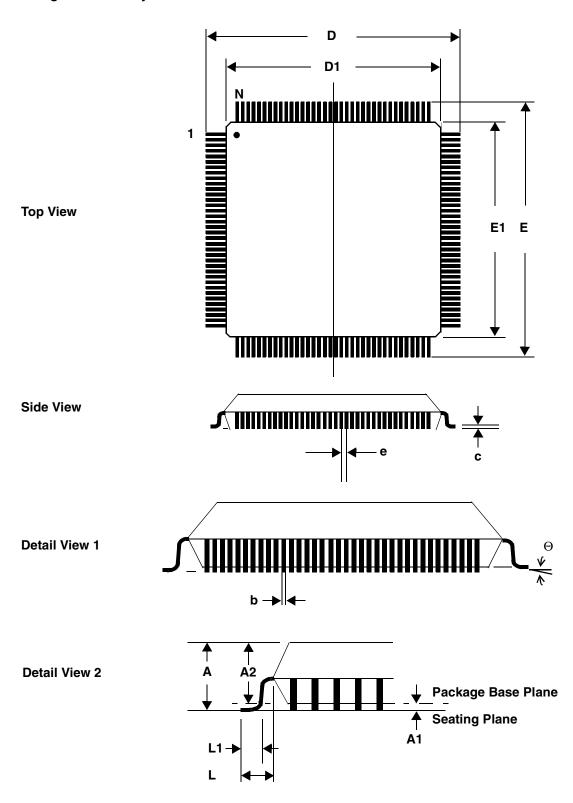

# **Chapter 3** Pin Diagram and Listings

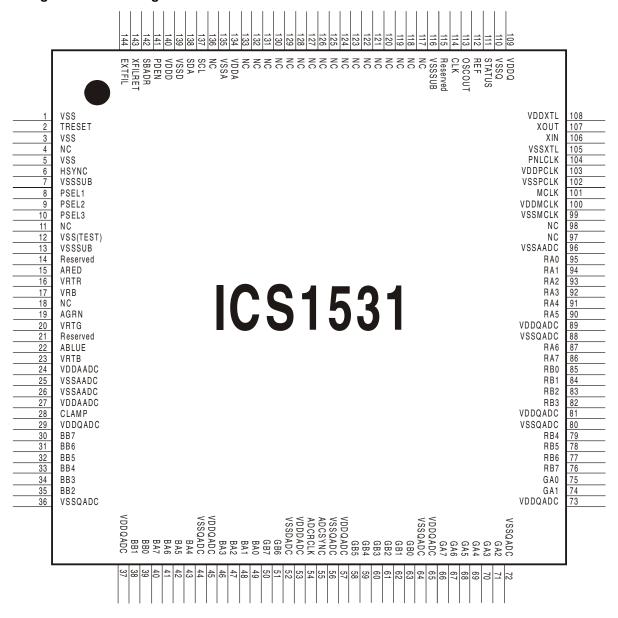

# 3.1 Pin Diagram for ICS1531

Figure 3-1 shows the pin diagram for the ICS1531, which is packaged in a 144-pin low-profile quad flat pack (LQFP).

Figure 3-1. Pin Diagram

# 3.2 Pin Listings

#### Note:

- 1. The TRESET pin (pin 2) was formerly a Reserved pin.

- 2. The following pins, formerly 'Reserved', are now NC (No Connect): 4, 11, 18, 97-98, 117-133, 136

- 3. The (active-low) STATUS pin (pin 111) was formerly called 'LOCK'

# 3.2.1 Pin Listing by Pin Number

Table 3-1. ICS1531 Pins, by Pin Number

| Table 0 | 1. 10313311 |

|---------|-------------|

| Pin No. | Pin Name    |

| 1       | VSS         |

| 2       | TRESET      |

| 3       | VSS         |

| 4       | NC          |

| 5       | VSS         |

| 6       | HSYNC       |

| 7       | VSSSUB      |

| 8       | PSEL1       |

| 9       | PSEL2       |

| 10      | PSEL3       |

| 11      | NC          |

| 12      | VSS(TEST)   |

| 13      | VSSSUB      |

| 14      | Reserved    |

| 15      | ARED        |

| 16      | VRTR        |

| 17      | VRB         |

| 18      | NC          |

| 19      | AGRN        |

| 20      | VRTG        |

| 21      | Reserved    |

| 22      | ABLUE       |

| 23      | VRTB        |

| 24      | VDDAADC     |

| 25      | VSSAADC     |

| 26      | VSSAADC     |

| 27      | VDDAADC     |

| 28      | CLAMP       |

| 29      | VDDQADC     |

| 30      | BB7         |

| 31      | BB6         |

| 32      | BB5         |

| 33      | BB4         |

| 34      | BB3         |

| 35      | BB2         |

| 1       |             |

| Pin No. | Pin Name |

|---------|----------|

| 37      | VDDQADC  |

| 38      | BB1      |

| 39      | BB0      |

| 40      | BA7      |

| 41      | BA6      |

| 42      | BA5      |

| 43      | BA4      |

| 44      | VSSQADC  |

| 45      | VDDQADC  |

| 46      | BA3      |

| 47      | BA2      |

| 48      | BA1      |

| 49      | BA0      |

| 50      | GB7      |

| 51      | GB6      |

| 52      | VSSDADC  |

| 53      | VDDDADC  |

| 54      | ADCRCLK  |

| 55      | ADCSYNC  |

| 56      | VSSQADC  |

| 57      | VDDQADC  |

| 58      | GB5      |

| 59      | GB4      |

| 60      | GB3      |

| 61      | GB2      |

| 62      | GB1      |

| 63      | GB0      |

| 64      | VSSQADC  |

| 65      | VDDQADC  |

| 66      | GA7      |

| 67      | GA6      |

| 68      | GA5      |

| 69      | GA4      |

| 70      | GA3      |

| 71      | GA2      |

| 72      | VSSQADC  |

| Pin No. | Pin Name |

|---------|----------|

| 73      | VDDQADC  |

| 74      | GA1      |

| 75      | GA0      |

| 76      | RB7      |

| 77      | RB6      |

| 78      | RB5      |

| 79      | RB4      |

| 80      | VSSQADC  |

| 81      | VDDQADC  |

| 82      | RB3      |

| 83      | RB2      |

| 84      | RB1      |

| 85      | RB0      |

| 86      | RA7      |

| 87      | RA6      |

| 88      | VSSQADC  |

| 89      | VDDQADC  |

| 90      | RA5      |

| 91      | RA4      |

| 92      | RA3      |

| 93      | RA2      |

| 94      | RA1      |

| 95      | RA0      |

| 96      | VSSAADC  |

| 97      | NC       |

| 98      | NC       |

| 99      | VSSMCLK  |

| 100     | VDDMCLK  |

| 101     | MCLK     |

| 102     | VSSPCLK  |

| 103     | VDDPCLK  |

| 104     | PNLCLK   |

| 105     | VSSXTL   |

| 106     | XIN      |

| 107     | XOUT     |

| 108     | VDDXTL   |

| Pin No. | Pin Name |

|---------|----------|

| 109     | VDDQ     |

| 110     | VSSQ     |

| 111     | STATUS   |

| 112     | REF      |

| 113     | OSCOUT   |

| 114     | CLK      |

| 115     | Reserved |

| 116     | VSSSUB   |

| 117     | NC       |

| 118     | NC       |

| 119     | NC       |

| 120     | NC       |

| 121     | NC       |

| 122     | NC       |

| 123     | NC       |

| 124     | NC       |

| 125     | NC       |

| 126     | NC       |

| 127     | NC       |

| 128     | NC       |

| 129     | NC       |

| 130     | NC       |

| 131     | NC       |

| 132     | NC       |

| 133     | NC       |

| 134     | VDDA     |

| 135     | VSSA     |

| 136     | NC       |

| 137     | SCL      |

| 138     | SDA      |

| 139     | VSSD     |

| 140     | VDDD     |

| 141     | PDEN     |

| 142     | SBADR    |

| 143     | XFILRET  |

| 144     | EXTFIL   |

# 3.2.2 Pin Listing by Alphabetical Pin Name

#### Note:

- 1. The TRESET pin was formerly a Reserved pin.

- 2. The following pins, formerly 'Reserved', are now NC (No Connect): 4, 11, 18, 97-98, 117-133, 136

- 3. The (active-low) STATUS pin was formerly called 'LOCK'.

Table 3-2. ICS1531 Pins, by Alphabetical Pin Name

| Pin Name | Pin No. |

|----------|---------|

| ABLUE    | 22      |

| ADCRCLK  | 54      |

| ADCSYNC  | 55      |

| AGRN     | 19      |

| ARED     | 15      |

| BA0      | 49      |

| BA1      | 48      |

| BA2      | 47      |

| BA3      | 46      |

| BA4      | 43      |

| BA5      | 42      |

| BA6      | 41      |

| BA7      | 40      |

| BB0      | 39      |

| BB1      | 38      |

| BB2      | 35      |

| BB3      | 34      |

| BB4      | 33      |

| BB5      | 32      |

| BB6      | 31      |

| BB7      | 30      |

| CLAMP    | 28      |

| CLK      | 114     |

| EXTFIL   | 144     |

| GA0      | 75      |

| GA1      | 74      |

| GA2      | 71      |

| GA3      | 70      |

| GA4      | 69      |

| GA5      | 68      |

| GA6      | 67      |

| GA7      | 66      |

| GB0      | 63      |

| GB1      | 62      |

| GB2      | 61      |

| Pin Name | Pin No.                           |

|----------|-----------------------------------|

| GB3      | 60                                |

| GB4      | 59                                |

| GB5      | 58                                |

| GB6      | 51                                |

| GB7      | 50                                |

| HSYNC    | 6                                 |

| MCLK     | 101                               |

| NC       | 4, 11, 18, 97–98,<br>117–133, 136 |

| OSCOUT   | 113                               |

| PDEN     | 141                               |

| PNLCLK   | 104                               |

| PSEL1    | 8                                 |

| PSEL2    | 9                                 |

| PSEL3    | 10                                |

| RA0      | 95                                |

| RA1      | 94                                |

| RA2      | 93                                |

| RA3      | 92                                |

| RA4      | 91                                |

| RA5      | 90                                |

| RA6      | 87                                |

| RA7      | 86                                |

| RB0      | 85                                |

| RB1      | 84                                |

| RB2      | 83                                |

| RB3      | 82                                |

| RB4      | 79                                |

| RB5      | 78                                |

| RB6      | 77                                |

| RB7      | 76                                |

| REF      | 112                               |

| Reserved | 14, 21, 115                       |

| SBADR    | 142                               |

| SCL      | 137                               |

| Pin Name  | Pin No.                           |

|-----------|-----------------------------------|

| SDA       | 138                               |

| STATUS    | 111                               |

| TRESET    | 2                                 |

| VDDA      | 134                               |

| VDDAADC   | 24, 27                            |

| VDDD      | 140                               |

| VDDDADC   | 53                                |

| VDDMCLK   | 100                               |

| VDDPCLK   | 103                               |

| VDDQ      | 109                               |

| VDDQADC   | 29, 37, 45, 57,<br>65, 73, 81, 89 |

| VDDXTL    | 108                               |

| VRB       | 17                                |

| VRTB      | 23                                |

| VRTG      | 20                                |

| VRTR      | 16                                |

| VSS       | 1, 3, 5                           |

| VSSA      | 135                               |

| VSSAADC   | 25, 26, 96                        |

| VSSD      | 139                               |

| VSSDADC   | 52                                |

| VSSMCLK   | 99                                |

| VSSPCLK   | 102                               |

| VSSQ      | 110                               |

| VSSQADC   | 36, 44, 56, 64,<br>72, 80, 88     |

| VSSSUB    | 7, 13, 116                        |

| VSS(TEST) | 12                                |

| VSSXTL    | 105                               |

| XFILRET   | 143                               |

| XIN       | 106                               |

| XOUT      | 107                               |

# 3.2.3 Pin Listing by Functional Grouping

# 3.2.3.1 Clock Pins

For more information on the clock pins, see Figure 4-2 and Figure 4-3.)

Table 3-3. Clock Pins

| Pin<br>Name | Pin<br>Type        | Pin Description                                                                                                                                                                                                                                                                         |

|-------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCRCLK     | Input or<br>Output | Analog-to-Digital Converter Reference Clock.  This pin outputs a half-rate pixel clock for latching digital output pixel data.  Typically, this pin connects to an LCD panel controller/scaler.  In this table, see also CLK.                                                           |

| ADCSYNC     | Input or<br>Output | <ul> <li>Analog-to-Digital Converter Sync.</li> <li>This pin provides a recovered HSYNC signal (that is, an HSYNC signal conditioned by a Schmitt trigger) that aligns to ADCRCLK.</li> <li>For some previous ICS chips, the ADCSYNC pin is called FUNC.</li> </ul>                     |

| CLK         | Output             | Clock.  This pin outputs the full-rate pixel clock for latching digital output pixel data.  In this table, see also ADCRCLK.                                                                                                                                                            |

| HSYNC       | Input              | Horizontal Sync. (See Table 3-6.)                                                                                                                                                                                                                                                       |

| MCLK        | Output             | Memory Clock.     This pin provides an independent user-programmable clock source.     Typically, this pin is used by LCD panel controller/scaler chips or microcontrollers.                                                                                                            |

| OSCOUT      | Output             | Oscillator Output.  This output from this pin is from a crystal oscillator.  The output frequency is one of the following:  The same frequency as the input frequency to the crystal oscillator  The frequency that results when the input frequency is divided by a programmable value |

| PNLCLK      | Output             | Panel Clock.  This pin provides an independent user-programmable clock source. Typically, this pin is used by LCD panel controller/scaler chips or microcontrollers.                                                                                                                    |

| REF         | Output             | Reference. This pin provides various reference line clock sync signals.                                                                                                                                                                                                                 |

| SCL         | Input              | Serial Clock. (See Table 3-7.)                                                                                                                                                                                                                                                          |

| XIN         | Input              | Crystal Input. This pin accepts input from one of the following:  • A 14.31818-MHz crystal  • An external clock source                                                                                                                                                                  |

| XOUT        | Output             | Crystal Output.  Do one of the following with this pin:  Connect it to a 14.31818-MHz crystal.  Leave it open for an external clock source.                                                                                                                                             |

## 3.2.3.2 Control Pins

Table 3-4. Control Pins

| Pin<br>Name               | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLAMP                     | Input       | Clamp. This pin accepts an external signal that is provided as an alternative to the ICS1531's internally generated clamp signal.                                                                                                                                                                                                                                                                                                                                                                             |

| PSEL1,<br>PSEL2,<br>PSEL3 | Output      | Programmable Select 1, 2, 3. These pins are used as general-purpose programmable output pins.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TRESET                    | Input       | Test Reset.  When the ICS1531:  ■ Is not in Test mode, this pin has no effect.  ■ Is placed into Test mode:  — This pin acts as a reset that sets the ICS1531 to an initial known state.  — For information about the Test mode, in this table see VSS(TEST).                                                                                                                                                                                                                                                 |

| VSS(TEST)                 | Input       | <ul> <li>Ground (Normal Mode) or Test Mode.</li> <li>Normal Mode. For the VSS(TEST) pin's Normal-mode function, see Table 3-4.</li> <li>Test Mode.  — When this pin is connected to either VDDA or VDDAADC, the ICS1531 is in Test mode. As a result, the ICS1531 is set to an initial known state.  — The Test mode overrides whatever the bit setting of Reg 37:3 is, so that the Calibration Regs 38h to 3Ch are automatically enabled.  — The Test mode bits are intended for use only by ICS.</li> </ul> |

|                           |             | VDDA or VDDAADC In Test mode, Test-mode bits are enabled and Calibration Regs 38h to 3Ch are automatically enabled.                                                                                                                                                                                                                                                                                                                                                                                           |

#### 3.2.3.3 Pixel Data Pins

Table 3-5. Pixel Data Pins

| Pin<br>Name                           | Pin<br>Type | Pin Description                                                                                                                                                                                                                                            |

|---------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABLUE,<br>AGRN,<br>ARED               | Input       | <ul> <li>Analog Blue, Analog Green, Analog Red.</li> <li>These pins accept analog data for the ADC blue, green, and red channels.</li> <li>Typically, the data for these pins comes from a PC display controller.</li> </ul>                               |

| BA7 – BA0,<br>GA7 – GA0,<br>RA7 – RA0 | Output      | Blue ('A channel') A7 – A0, Green ('A channel') A7 – A0, Red ('A channel') A7 – A0.  • These pins output first blue, green, and red pixel data, respectively.  • A7 pins reflect most-significant data bits. A0 pins reflect least-significant data bits.  |

| BB7 – BB0,<br>GB7 – GB0,<br>RB7 – RB0 | Output      | Blue ('B channel') B7 – B0, Green ('B channel') B7 – B0, Red ('B channel') B7 – B0.  • These pins output second blue, green, and red pixel data, respectively.  • B7 pins reflect most-significant data bits. B0 pins reflect least-significant data bits. |

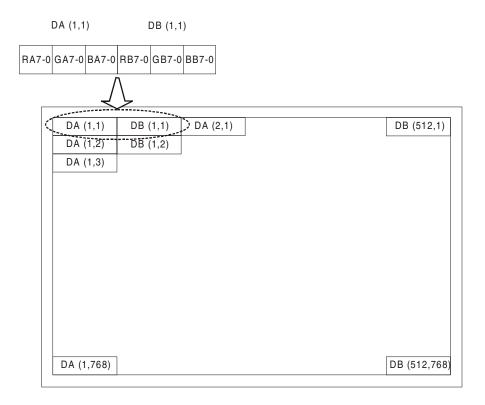

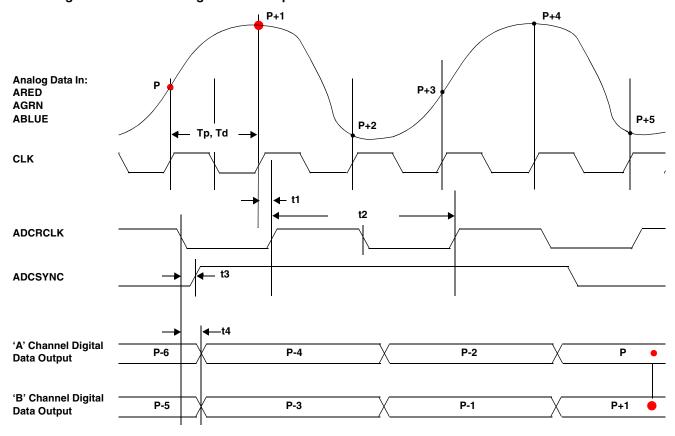

Figure 3-2 shows the following:

- The relationship of:

- Outputs from the ICS1531 ADC

- $-\,$  To inputs of a 1024  $\times$  768 LCD panel that samples 2 pixels of data with either a 36- or 48-bit data signal.

- DA indicates 'A channel' pixels, and DB indicates 'B channel' pixels.)

For timing information, see Chapter 10, "Timing Diagrams".

Figure 3-2. Relationship of Outputs from an ICS1531's ADC to Inputs of  $1024 \times 768$  LCD Panel

# 3.2.3.4 Phase-Locked Loop Pins

Table 3-6 lists the pins for the phase-locked loop circuitry. For a block diagram that shows the function of these pins, see Figure 4-1.

Table 3-6. Phase-Locked Loop Pins

| Pin<br>Name | Pin<br>Type | Pin Description                                                                                                                                                                                                                                                                                          |

|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTFIL      | Input       | External Filter. This pin works with XFILRET (in this table, see XFILRET) and other components as part of an optional external filter for the pixel phase-locked loop.                                                                                                                                   |

| HSYNC       | Input       | <ul> <li>Horizontal Sync.</li> <li>This 5-V tolerant pin is the clock input for the pixel PLL.</li> <li>Typically this pin is connected to the HSYNC from a PC display controller.</li> <li>In this data sheet, this HSYNC signal is also called 'input HSYNC'.</li> </ul>                               |

| LOCK        | Output      | In this table, see the 'STATUS' pin name.                                                                                                                                                                                                                                                                |

| PDEN        | Input       | Phase-Detector Enable. This pin is the input for the Phase/Frequency Detector enable that can suspend the charge pump activity. It is 5-V tolerant. (For more information, see Reg 00:1-0 in Section 6.5.1, "Register 00h: Input Control Register".)                                                     |

| STATUS      | Output      | Status (Formerly called 'Lock').  This active-low pin works with Reg 2C:1-0 and Reg 12:3-2. The signal on this pin is:  Low when a lock condition occurs for one of the PLLs selected by Reg 2C:1-0 or 12:3-2.  High when no lock condition occurs for one of the PLLs selected by Reg 2C:1-0 or 12:3-2. |

| XFILRET     | Input       | External Filter Return. This pin works with EXTFIL (in this table, see EXTFIL) and other components as part of an optional external filter for the pixel phase-locked loop.                                                                                                                              |

# 3.2.3.5 Industry-Standard 2-Wire Serial Bus Pins

Table 3-7. Industry-Standard 2-Wire Serial Bus Pins

| Pin<br>Name | Pin<br>Type      | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBADR       | Input            | Serial Bus Address.  This pin determines the address for the ICS1531 industry-standard 2-wire serial bus.  When the signal on this pin is:  Low, the pixel bit address is 49h for read operations and 48h for write operations.  High, the pixel bit address is 4Bh for read operations and 4Ah for write operations.  For more information on this pin, see Section 2.9, "Industry-Standard 2-Wire Serial Interface". |

| SCL         | Input            | Serial Clock. This 5-V tolerant pin is the clock for the interface to an industry-standard 2-wire serial bus.                                                                                                                                                                                                                                                                                                          |

| SDA         | Input/<br>Output | Serial Data. This 5-V tolerant pin connects to the data pin for an industry-standard 2-wire serial bus.                                                                                                                                                                                                                                                                                                                |

# 3.2.3.6 Ground Pins

Table 3-8. Ground Pins

| Pin Name  | Pin Description                                                                                                                                                                                                                                                                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS       | Ground for (Analog Inputs for Digital Pixel PLL Circuitry).  • These pins are used to ground digital portions of the pixel PLL circuitry that receive analog inputs.  • The VSSD pin must also be connected to these pins.                                                         |

| VSSA      | Ground for Analog (Pixel PLL Circuitry). This pin is used to ground the analog portions of the pixel PLL circuitry.                                                                                                                                                                |

| VSSAADC   | Ground for Analog ADC (Circuitry). These pins are used to ground the analog portions of the ADC.                                                                                                                                                                                   |

| VSSD      | Ground for Digital (Pixel PLL and Circuitry for Industry-Standard 2-Wire Serial Interface). This pin is used to ground the digital portions of the pixel PLL circuitry and the circuitry for an industry-standard 2-wire serial interface.                                         |

| VSSDADC   | Ground for Digital ADC (Circuitry). This pin is used to ground the digital portions of the ADC.                                                                                                                                                                                    |

| VSSMCLK   | Ground for Memory Clock (Circuitry). This pin is used to ground the circuitry for the memory clock PPL (that is, MCLK).                                                                                                                                                            |

| VSSPCLK   | Ground for Panel Clock (Circuitry). This pin is used to ground the circuitry for the panel clock PLL (that is, PNLCLK).                                                                                                                                                            |

| VSSQ      | Ground for Output Drivers. This pin is used to ground output drivers for the pixel PLL circuitry.                                                                                                                                                                                  |

| VSSQADC   | Ground for Output Drivers for ADC.  These pins are used to ground the pixel data output drivers for the analog-to-digital converter.                                                                                                                                               |

| VSSSUB    | Ground for Substrate. These pins are used to provide ground for the chip substrate.                                                                                                                                                                                                |

| VSS(TEST) | Ground (Normal Mode) or Test Mode.  ■ Normal Mode.  — Typically, this pin must be connected to ground (the Normal mode).  — When the ICS1531 is in Normal mode, the Calibration registers 38h to 3Ch can be enabled by using Reg 37:3. (See Section 6.5.39, "Register 37h: PSEL".) |

|           | Normal Mode  VSS(TEST)  Normal Mode  In Normal mode, use Reg 37:3 to enable Calibration Regs 38h to 3Ch.  • Test Mode. For the VSS(TEST) pin's Test-mode function, see Table 3-4.                                                                                                  |

| VSSXTL    | Ground for Crystal Oscillator. This pin is used to ground the internal crystal oscillator circuitry.                                                                                                                                                                               |

# 3.2.3.7 Power Pins

Table 3-9. Power Pins

| Pin Name               | Pin Description                                                                                                                                                                                                                     |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDA                   | (3.3 V) Supply for Analog (Pixel PLL Circuitry). This pin supplies 3.3 V to the analog portions of the pixel PLL circuitry.                                                                                                         |

| VDDAADC                | (3.3 V) Supply for Analog ADC (Circuitry). These pins supply 3.3 V to the analog portions of the ADC.                                                                                                                               |

| VDDD                   | (3.3 V) Supply for Digital (Pixel PLL and Industry-Standard 2-Wire Serial Bus) Circuitry. This pin supplies 3.3 V to the digital pixel PLL and circuitry for an industry-standard 2-wire serial bus interface.                      |

| VDDDADC                | (3.3 V) Supply for Digital ADC (Circuitry). This pin supplies 3.3 V to digital portions of the ADC.                                                                                                                                 |

| VDDMCLK                | (3.3 V) Supply for Memory Clock. This pin supplies 3.3 V to the memory clock PLL circuitry.                                                                                                                                         |

| VDDPCLK                | (3.3 V) Supply for Panel Clock. This pin supplies 3.3 V to the panel clock PLL circuitry.                                                                                                                                           |

| VDDQ                   | (3.3 V) Supply for Output Drivers. This pin supplies 3.3 V to the output driver circuitry for the pixel PLL.                                                                                                                        |

| VDDQADC                | (3.3 V) Supply for Output Drivers for Analog-to-Digital Converter.  These pins supply 3.3 V to the pixel data output drivers of the ADC.                                                                                            |

| VDDXTL                 | (3.3V) Supply for Crystal Oscillator. This pin supplies 3.3 V to the internal crystal oscillator circuitry.                                                                                                                         |

| VRB                    | Voltage Reference Bottom. The ADC uses this pin as a bottom reference voltage. Typically, this pin is grounded.                                                                                                                     |

| VRTB,<br>VRTG,<br>VRTR | Voltage Reference Top Blue, Green, Red  The ADC uses these pins as an alternative to the blue, green, and red top reference voltages from the internal DACs.  Each of these pins must connect to its own separate bypass capacitor. |

## 3.2.3.8 No-Connect Pins

Table 3-10. No-Connect Pins

| Pin<br>Name | Pin Description                                                                                                                                                   |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NC          | No Connect. Do not connect these pins.                                                                                                                            |  |  |  |  |  |

|             | Caution: Do not connect or use No-Connect pins. Connecting them can affect the performance and operation of the ICS1531 and future members of the ICS153X family. |  |  |  |  |  |

## 3.2.3.9 Reserved Pins

Table 3-11. Reserved Pins

| Pin<br>Name | Pin<br>Type |                        | Pin Description                                                                                                                                        |  |  |  |  |  |

|-------------|-------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Reserved    | _           | Reserved<br>These pins | s are always reserved for use by ICS.                                                                                                                  |  |  |  |  |  |

|             |             | Caution:               | Do not connect or use Reserved pins. Connecting them can affect the performance and operation of the ICS1531 and future members of the ICS153X family. |  |  |  |  |  |

#### 3.2.3.10 List of 5-V Tolerant Pins

The following pins are 5-V tolerant:

- HSYNC (Table 3-6)

- PDEN (Table 3-6)

- SCL (Table 3-7)

- SDA (Table 3-7)

- TRESET (Table 3-4)

# **Chapter 4 Functional Blocks**

## 4.1 Pixel PLL Functional Block

Figure 4-1. Pixel PLL Block Diagram

# 4.2 CLK Functional Block

Figure 4-2. CLK Block Diagram

# 4.3 ADC Functional Block

Figure 4-3. ADC Block Diagram

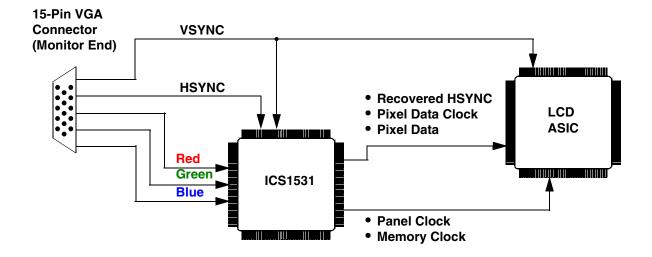

# **Chapter 5 Application Overview**

Figure 5-1 shows a basic application for the ICS1531.

Figure 5-1. ICS1531 Application

# Chapter 6 Register Set

The tables in this chapter detail the functionality of the bits in the ICS1531 Register Set. The tables include the register locations, the bit positions, names, and definitions, along with their read/write access, reset values, and any special functions or capabilities.

### 6.1 Reserved Bits

The ICS1531 has a number of reserved bits throughout the Register Set. These bits provide enhanced test functions (intended for use only by ICS manufacturing) and calibration functions (intended for use in production environments).

**Important:** The customer must not change the value of reserved bits. If the customer changes the default values of these reserved bits, normal operation of the ICS1531 can be affected.

## 6.2 Register Set Conventions

Register Set conventions include the following:

- Bits are listed in the order of most-significant bit (MSB) to least-significant bit (LSB).

- Unless otherwise indicated, bit settings are listed in terms of digital (and not hexadecimal) values.

- When a bit definition includes word(s) in parentheses, the word in parenthesis is not part of the bit name, but is given to explain the origin of the bit's name.

## 6.3 Register Set Abbreviations and Acronyms

Table 6-1 lists and defines abbreviations and acronyms used specifically in this chapter. (Table 1-1 lists other abbreviations and acronyms used throughout this data sheet.)

Table 6-1. Register Set Abbreviations and Acronyms

| Abbreviation or Acronym | Definition                                                                                                                                                        |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D-DPA                   | <b>Double-Buffered / Dynamic Phase Adjust.</b> Indicates double-buffered registers for which working registers load during a software Dynamic Phase Adjust reset. |

| D-MK                    | <b>Double-Buffered / Memory Clock.</b> Indicates double-buffered registers for which working registers load during a software MCLK reset.                         |

| D-PK                    | <b>Double-Buffered / Panel Clock.</b> Indicates double-buffered registers for which working registers load during a software PNLCLK reset.                        |

| D-PLL                   | <b>Double-Buffered / Phase-Locked Loop.</b> Indicates double-buffered registers for which working registers load during a software pixel PLL reset.               |

| IN-A                    | Increment All. Indicates a value that increments with each all-layer revision of the ICS1531.                                                                     |

| Reg                     | Register                                                                                                                                                          |

| R/W                     | Read/Write                                                                                                                                                        |

| Spec. Func.             | Special Function. Indicates a special function, such as the following (listed in this table): D-DPA, D-MK, D-PK, D-PLL                                            |

# 6.4 Register Set Outline

Table 6-2 outlines the ICS1531 Register Set.

# Note:

- 1. For the reserved bits, see Section 6.1, "Reserved Bits".

- 2. For abbreviations and acronyms, see Section 6.3, "Register Set Abbreviations and Acronyms".

Table 6-2. Register Set Outline

| Index<br>00h | Input Control   | Access<br>R/W |     |                 |                                                     | Value |

|--------------|-----------------|---------------|-----|-----------------|-----------------------------------------------------|-------|

| 00h          | Input Control   | R/W           |     |                 |                                                     |       |

|              |                 |               | 7-6 | HSYNC_Sel       | Select a Schmitt trigger                            | 0     |

|              |                 |               | 5   | In_Sel          | Select input                                        | 1     |

|              |                 |               | 4   | Fdbk Div Load   | Select load for Feedback Divider                    | 0     |

|              |                 |               | 3   | Fdbk_Pol        | Select polarity of feedback to Phase/Frequency      | 0     |

|              |                 |               |     |                 | Detector                                            |       |

|              |                 |               | 2   | Ref_Pol         | Select polarity of external reference               | 0     |

|              |                 |               | 1   | PD_Pol          | Select polarity of PDEN to Phase/Frequency Detector | 0     |

|              |                 |               | 0   | PD_En           | Enable Phase/Frequency Detector                     | 1     |

| 01h          | Loop Control    | R/W. D-PLL.   | 7-6 | Reserved        | Reserved                                            | 0     |

| UIII         | Loop Control    | n/vv. D-F LL. | 5-4 | PSD             | Select value for Post-Scaler Divider                | 0     |

|              |                 |               | 3   | Reserved        | Reserved                                            | 0     |

|              |                 |               | 2-0 | PFD             | Select Phase/Frequency Detector gain                | 0     |

|              |                 |               | 2-0 | FFD             | Select Friase/Frequency Detector gain               |       |

| 02h          | Fdbk Div 0      | R/W. D-PLL.   | 7-0 | FDBK [7-0]      | Select value for Feedback Divider LSBs bits 7-0     | FF    |

|              |                 | 1.4           |     | []              |                                                     |       |

| 03h          | Fdbk Div 1      | R/W. D-PLL.   | 7-4 | Reserved        | Reserved                                            | _     |

|              |                 |               | 3-0 | FDBK [11-8]     | Select value for Feedback Divider MSBs bits 11-8    | 0     |

|              |                 |               |     |                 |                                                     | .1    |

| 04h          | DPA Offset      | R/W           | 7-6 | Reserved        | Reserved                                            | 0     |

|              |                 |               | 5-0 | DPA_OS          | Select offset for Dynamic Phase Adjust              | 0     |

|              |                 |               |     | 1               |                                                     | .1    |

| 05h          | DPA Control     | R/W. D-DPA.   | 7-2 | Reserved        | Reserved                                            | _     |

|              |                 |               | 1-0 | DPA_Res         | Select resolution for Dynamic Phase Adjust          | 0     |

|              |                 |               |     |                 |                                                     |       |

| 06h          | Output Enables  | R/W           | 7   | Reserved        | Reserved                                            | 0     |

|              |                 |               | 6   | OE_Tck          | Enable clock output to ADC                          | 0     |

|              |                 |               | 5   | OE_ADCRCLK      | Enable clock output from ADC                        | 0     |

|              |                 |               | 4   | OE_ADCSYNC      | Enable output for delayed ADCSYNC                   | 0     |

|              |                 |               | 3   | FUNC_Sel        | Select signal source for ADC_FUNC signal            | 0     |

|              |                 |               | 2   | FUNC_Delay      | Select delay for ADC_FUNC signal                    | 0     |

|              |                 |               | 1-0 | Reserved        | Reserved                                            | 0     |

| 071          | 000 B: :1       | DAM           | 7.0 | 000 P:          | 0 " 1 ( " " 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1           |       |

| 07h          | OSC Divider     | R/W           | 7-0 | OSC_Div         | Specify value for oscillator divider                | 0     |

| 08h          | Internal Filter | R/W           | 7   | Shunt_Sel       | Select internal filter shunt capacitor size         | 1     |

|              |                 |               | 6-4 | Res_Sel         | Select internal filter resistor size                | 7     |

|              |                 |               | 3-1 | Cap_Sel         | Select internal filter capacitor size               | 7     |

|              |                 |               | 0   | Fil_Sel         | Select type of loop filter                          | 1     |

|              |                 |               |     | 00.             | Coloci type of loop line.                           |       |

| 09h          | Reserved        |               |     |                 |                                                     | N/A   |

|              |                 |               |     |                 |                                                     | -1    |

| 0Ah          | Pixel PLL       | Write         | 7-4 | Pixel PLL Reset | Writing 5xh resets pixel PLL and loads working Regs | N/A   |

|              | Reset/          |               |     |                 | 1h through 3h                                       |       |

|              | DPA Reset       |               |     |                 |                                                     |       |

|              |                 |               | 3-0 | DPA Reset       | Writing xAh resets DPA and loads working Reg 5h     | N/A   |

|              | _               |               |     |                 |                                                     |       |

| 0Bh-0Fh      | Reserved        |               |     |                 |                                                     | N/A   |

# ICS1531 Data Sheet - Preliminary

Table 6-2. Register Set Outline (Continued)

| Register<br>Index | Register Name | Register<br>Access | Bit # | Bit Name       | Brief Description                                              | Reset<br>Value |

|-------------------|---------------|--------------------|-------|----------------|----------------------------------------------------------------|----------------|

| 10h               | Chip Ver      | Read               | 7-0   | Chip Ver       | Read chip version 31 decimal (1F hex) as in 1531               | 1F             |

| 11h               | Chip Rev      | Read. IN-A.        | 7-4   | Chip Major Rev | Read initial value 00h. +Value increments with chip revision.  | 00+            |

|                   |               |                    | 3-0   | Chip Minor Rev | Read initial value 01h. +Value increments with chip revision.  | 01+            |

| 12h               | Rd_Reg        | Read               | 7-4   | Reserved       | Reserved                                                       | N/A            |

|                   | 1             |                    | 3     | PNLCLK_Lock    | Read PNLCLK lock status                                        | N/A            |

|                   |               |                    | 2     | MCLK_Lock      | Read MCLK lock status                                          | N/A            |

|                   |               |                    | 1     | Pixel PLL_Lock | Read pixel PLL lock status                                     | N/A            |

|                   |               |                    | 0     | DPA_Lock       | Read DPA lock status                                           | N/A            |

| 13h-1Fh           | Reserved      |                    |       |                |                                                                | N/A            |

| 001-              | DNII OLIZ M   | DAM D DK           | 7.0   | DNII OLIZ M    | Colortania for DNI CLIV M Defense a Divider                    | •              |

| 20h               | PNLCLK-M      | R/W. D-PK.         | 7-0   | PNLCLK_M       | Select value for PNLCLK M Reference Divider                    | 0              |

| 21h               | PNLCLK-N      | R/W. D-PK.         | 7-0   | PNLCLK_N       | Select value for PNLCLK N Feedback Divider                     | 0              |

| 22h               | PNLCLK-SS0    | R/W. D-PK.         | 7-0   | PNLCLK_SS0     | Select value for PNLCLK spread-spectrum counter LSBs bits 7-0  | 0              |

| 23h               | PNLCLK-SS1    | R/W. D-PK.         | 7-4   | Reserved       | Reserved                                                       | 0              |

|                   | I             |                    | 3-0   | PNLCLK_SS1     | Select value for PNLCLK spread-spectrum counter MSBs bits 11-8 | 0              |

| 24h               | PNLCLK-SSOE   | R/W. D-PK.         | 7-6   | PNLCLK_SS      | Select PNLCLK spread-spectrum gain                             | 0              |

|                   | I.            | l .                | 5     | Reserved       | Reserved                                                       | 0              |

|                   |               |                    | 4-2   | PNLCLK_PFD     | Select PNLCLK Phase/Frequency Detector gain                    | 0              |

|                   |               |                    | 1-0   | PNLCLK_OSD     | Select value for PNLCLK Output Scaler Divider                  | 0              |

| 25h               | PNLCLK-OE     | R/W                | 7-3   | Reserved       | Reserved                                                       | 0              |

|                   |               |                    | 2     | CLK_SEL        | Select input for PNLCLK PLL                                    | 0              |

|                   |               |                    | 1     | PNLCLK_SSENB   | Enable PNLCLK spread-spectrum                                  | 0              |

|                   |               |                    | 0     | PNLCLK_OE      | Enable PNLCLK output                                           | 0              |

| 26h               | MCLK-M        | R/W. D-MK.         | 7-0   | MCLK_M         | Select value for MCLK M Reference Divider                      | 0              |

| 27h               | MCLK-N        | R/W. D-MK.         | 7-0   | MCLK_N         | Select value for MCLK N Feedback Divider                       | 0              |

| 2711              | WIGER         | TI/VV. D-IVIIX.    | 7-0   | MOER_IV        | Gelect value for MOER IV Feedback Bivider                      | - 0            |

| 28h               | MCLK-SS0      | R/W. D-MK.         | 7-0   | MCLK_SS0       | Select MCLK spread-spectrum counter LSBs bits 7-0              | 0              |

| 29h               | MCLK-SS1      | R/W. D-MK.         | 7-4   | Reserved       | Reserved                                                       | 0              |

|                   | !             | !                  | 3-0   | MCLK_SS1       | Select MCLK spread-spectrum counter MSBs bits 11-8             | 0              |

| 2Ah               | MCLK-SSOE     | R/W. D-MK.         | 7-6   | MCLK_SS        | Select MCLK spread-spectrum gain                               | 0              |

|                   | •             | +                  | 5     | Reserved       | Reserved                                                       | 0              |

|                   |               |                    | 4-2   | MCLK_PFD       | Select MCLK Phase/Frequency Detector gain                      | 0              |

|                   |               |                    | 1-0   | MCLK_OSD       | Select value for MCLK Output Scaler Divider                    | 0              |

| 2Bh               | MCLK-OE       | R/W                | 7-2   | Reserved       | Reserved                                                       | 0              |

|                   | L             | II.                | 1     | MCLK_SSENB     | Enable MCLK spread-spectrum                                    | 0              |

|                   |               |                    | 0     | MCLK_OE        | Enable MCLK output                                             | 0              |

Table 6-2.

Register Set Outline (Continued)

| 2Ch     | OUTPUT MUX | R/W      | 7          |                    |                                                                                         |     |

|---------|------------|----------|------------|--------------------|-----------------------------------------------------------------------------------------|-----|

| 2Dh     | 1          |          |            | High_Drive         | Select drive strength for all ADC outputs                                               | 0   |

| 2Dh     |            |          | 6          | OE_OSC             | Enable OSCOUT output                                                                    | 1   |

| 2Dh     |            |          | 5-4        | OSC_Sel            | Select output from 4-way MUX to OSCOUT                                                  | 0   |

| 2Dh     |            |          | 3          | Reserved           | Reserved                                                                                | 0   |

| 2Dh     |            |          | 2          | REFSEL             | Select REF status                                                                       | 0   |

| 2Dh     |            |          | 1-0        | LCKSEL             | Select PLL lock status                                                                  | 1   |

|         | PLL Reset  | Write    | 7-4        | MCLK_Reset         | Writing 5xh resets MCLK PLL and loads working Regs 26h to 2Bh.                          | N/A |

|         |            |          | 3-0        | PNLCLK_Reset       | Writing xAh resets PNLCLK PLL and loads working Regs 20h to 25h.                        | N/A |

| 2Eh-2Fh | Reserved   |          |            |                    |                                                                                         | N/A |

| 30h     | ADC CTRL   | R/W      | 7          | ADC_OE             | Enable ADC output                                                                       | 0   |

| 3011    | ADOUTHL    | 1 1/ V V | 6          | ADC_Sel            | Select ADC capture                                                                      | 0   |

|         |            |          | 5          | ADC_Sel            | Invert ADC outputs                                                                      | 1   |

|         |            |          | 4          | Force_ADC          | Force all ADC output buffers off                                                        | 0   |

|         |            |          | 3          | CLAMP_Pol          | Select polarity of signal to a clamp                                                    | 0   |

|         |            |          | 2          | CLAMP_Sel          | Select source to a clamp                                                                | 0   |

|         |            |          | 1          | VA_Disable         | Disable video amplifier                                                                 | 0   |