## **Advance Information**

# **Dual Programmable Graphics Frequency Generator**

### **General Description**

The ICS82C404 is a fully programmable graphics clock generator. It can generate user specified clock frequencies using an externally generated input reference or by a single crystal. The output frequency is programmed by entering a 24-bit digital word through the serial port.

Two fully user-programmable phase-locked loops are offered in a single package. One PLL is designed to drive the memory clock, while the second drives the video clock. The outputs may be changed on-the-fly to any desired frequency between 390 kHz and 120 MHz. The ICS82C404 is ideally suited for any design where multiple or varying frequencies are required.

This part is ideal for graphics applications. It generates low jitter, high speed pixel clocks. It can be used to replace multiple, expensive high speed crystal oscillators. The flexibility of the device allows it to generate non-standard graphics clocks.

The leader in the area of multiple clock output clocks on a single chip, ICS has been shipping graphics frequency generators since October, 1990, and is constantly improving the phase-locked loop. The ICS82C404 incorporates a patented fourth generation PLL that offers the best jitter performance available.

#### **Features**

- Pin-for-pin and function compatible with ICD's version of the 82C404

- Dual programmable graphics clock generator

- Memory and video clocks are individually programmable "on-the-fly"

- Ideal for designs where multiple or varying frequencies are required

- Increased frequency resolution from optional pre-divideby-2 on the M counter

- Output enable feature available for tristating outputs

- Independent clock outputs range from 390 kHz to 120 MHz

- Operation up to 140 MHz available

- Power-down capabilities

- Low-power, high speed 0.8μ CMOS technology

- Glitch-free transitions

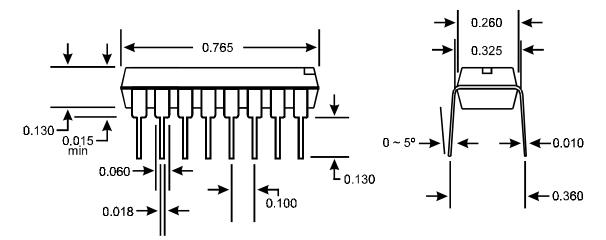

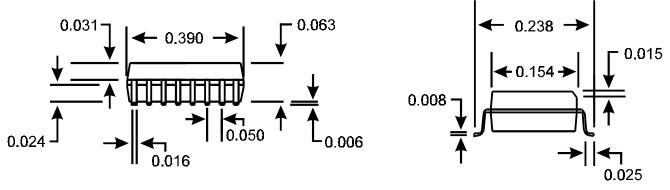

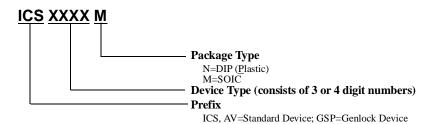

- Available in 16-pin PDIP or SOIC package

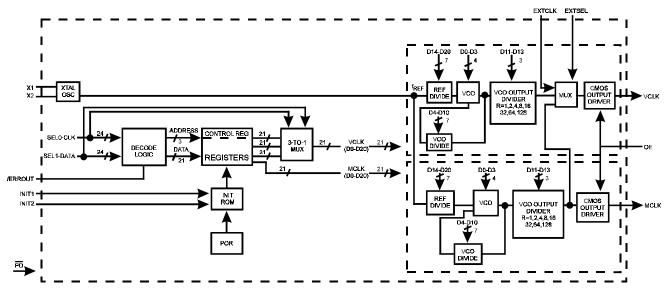

## **Block Diagram**

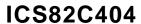

# **Pin Configuration**

16-Pin PDIP or SOIC

# **Pin Descriptions**

| PIN NUMBER | PIN NAME  | DESCRIPTION                                                                 |

|------------|-----------|-----------------------------------------------------------------------------|

| 1          | SEL0-CLK  | Clock input in serial programming mode. Clock select pin in operating mode. |

| 2          | SEL1-DATA | Data input in serial programming mode. Clock select pin in operating mode.  |

| 3          | AVDD      | Power.                                                                      |

| 4          | OE        | Tristates outputs when low.                                                 |

| 5          | GND       | Ground.                                                                     |

| 6          | X1        | Crystal input.                                                              |

| 7          | X2        | Crystal output.                                                             |

| 8          | MCLK      | Memory clock output.                                                        |

| 9          | VCLK      | Video clock output.                                                         |

| 10         | FPMODE    | Clock select input used to force REG2 programmed frequency.                 |

| 11         | EXTCLK    | External clock input.                                                       |

| 12         | INIT0     | Selects initial power-up conditions, LSB.                                   |

| 13         | VDD       | Power.                                                                      |

| 14         | INIT1     | Selects initial power-up conditions, MSB.                                   |

| 15         | EXTSEL    | Selects external clock input (EXTCLK) as VCLK output.                       |

| 16         | PD        | Power-down pin, active low.                                                 |

### **Register Definitions**

The register file consists of the following six registers:

#### **Register Addressing**

| Address | Register | Definition                  |

|---------|----------|-----------------------------|

| 000     | REG0     | Video Clock Register 1      |

| 001     | REG1     | Video Clock Register 2      |

| 010     | REG2     | Video Clock Register 3      |

| 011     | MREG     | Memory Register             |

| 100     | PWRDWN   | Divisor for Power-down mode |

| 110     | CNTL REG | Control Register            |

The ICS82C404 places the three video clock registers and the memory clock register in a known state upon power-up. The registers are initialized based on the state of the INIT1 and INIT0 pins at application of power to the device. The INIT pins must ramp up with VDD if a logical 1 on either pin is required. These input pins are internally pulled down and will default to a logical 0 if left unconnected.

The registers are initialized as follows:

#### **Register Initialization**

| INIT1 | INIT0 | MREG   | REG0   | REG1   | REG2   |

|-------|-------|--------|--------|--------|--------|

| 0     | 0     | 32.500 | 25.175 | 28.322 | 28.322 |

| 0     | 1     | 40.000 | 25.175 | 28.322 | 28.322 |

| 1     | 0     | 50.350 | 40.000 | 28.322 | 28.322 |

| 1     | 1     | 56.644 | 40.000 | 50.350 | 50.350 |

## **Register Selection**

When the ICS82C404 is operating, the video clock output is controlled with a combination of the SEL0, SEL1,  $\overline{PD}$ , and OE pins. The video clock is also multiplexed to an external clock (EXTCLK) which can be selected with the EXTSEL pin. The VCLK Selection Table shows how VCLK is selected.

#### **VCLK Selection**

| OE | PD | EXTSEL | FPMODE | SEL1 | SEL0 | VCLK        |

|----|----|--------|--------|------|------|-------------|

| 0  | X  | X      | X      | X    | X    | Tristate    |

| 1  | 0  | X      | X      | X    | X    | Forced High |

| 1  | 1  | X      | 1      | 0    | 0    | REG0        |

| 1  | 1  | X      | 1      | 0    | 1    | REG1        |

| 1  | 1  | 0      | 1      | 1    | 0    | EXTCLK      |

| 1  | 1  | 1      | 1      | 1    | X    | REG2        |

| 1  | 1  | X      | 1      | 1    | 1    | REG2        |

| 1  | 1  | X      | 0      | X    | X    | REG2        |

As seen in the table above, OE acts to tristate the output. The  $\overline{PD}$  pin forces the VCLK signal high while powering down the part. The EXTCLK pin will only be multiplexed in when EXTSEL and SEL0 are logic 0 and SEL1 is a logic 1.

The memory clock outputs are controlled by  $\overline{PD}$  and OE as follows:

#### MCLK Selection

| OE | PD | MCLK     |

|----|----|----------|

| 0  | X  | Tristate |

| 1  | 1  | MREG     |

| 1  | 0  | PWRDWN   |

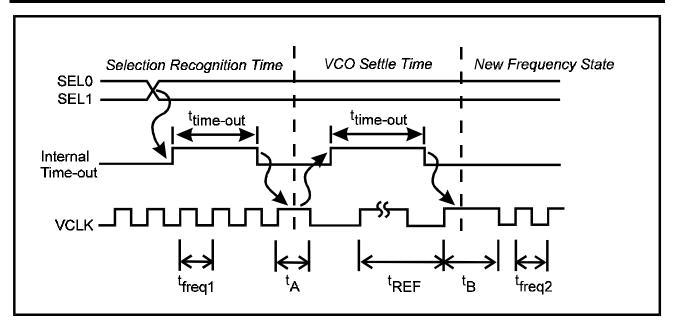

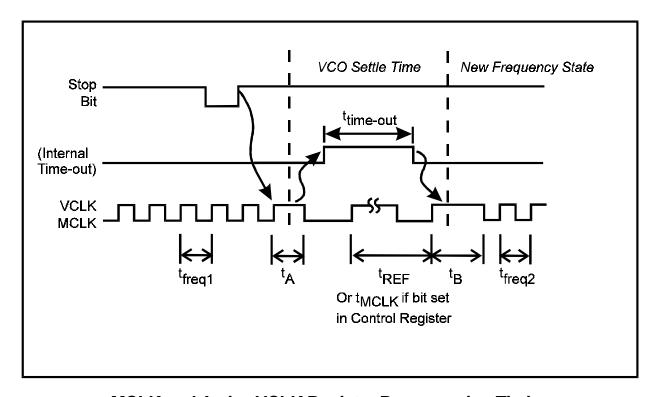

The Clock Select pins SEL0 and SEL1 have two purposes. In serial programming mode, these pins act as the clock and data pins. New data bits come in on SEL1 and these bits are clocked in by a signal on SEL0. While these pins are acquiring new information, the VCLK signal remains unchanged. When SEL0 and SEL1 are acting as register selects, a time-out interval is required to determine whether the user is selecting a new register or wants to program the part. During this initial time-out, the VCLK signal remains at its previous frequency. At the end of this time-out interval, a new register is selected. A second time-out interval is required to allow the VCO to settle to its new value. During this period of time, typically 5 ms, the input reference signal is multiplexed to the VCLK signal.

When MCLK or the active VCLK register is being reprogrammed, then the reference signal is multiplexed glitch-free to the output during the first time-out interval. A second time-out interval is also required to allow the VCO to settle. During this period, the reference signal is multiplexed to the appropriate output signal.

# ICS82C404

## **Control Register Definition**

The control register allows the user to adjust various internal options. The register is defined as follows:

| Bit | Bit Name | Default Value | Description                                                                                                                                                                                                                                                                    |  |

|-----|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9   | C5       | 0             | This bit determines which power-down mode the $\overline{PD}$ pin will implement. Power-down mode 1, C5=0, forces the MCLK signal to be a function of the power-down register. Power-down mode 2, C5=1, turns off the crystal and disables all outputs.                        |  |

| 8   | C4       | 0             | This bit determines which clock is multiplexed to VCLK during frequency changes. C4=0 multiplexes the reference frequency to the VCLK output. C4=1 multiplexes MCLK to the VCLK output for applications where the graphics controller cannot run as slow as f <sub>REF</sub> . |  |

| 7   | C3       | 0             |                                                                                                                                                                                                                                                                                |  |

|     |          |               | This bit determines the length of the time-out interval. The time-out interval is derived from the MCLK VCO. If this VCO is programmed to certain extremes, the time-out interval maybe too short. C3=0, normal time-out. C3=1, doubled time-out interval.                     |  |

| 6   | C2       | 0             | Reserved, must be set to 0.                                                                                                                                                                                                                                                    |  |

| 5   | C1       | 1             |                                                                                                                                                                                                                                                                                |  |

|     |          |               | This bit adjusts the duty cycle. C1=0 causes a 1ns decrease in output high time. C1=1 causes no adjustment. If the load capacitance is high, the adjustment can bring the duty cycle closer                                                                                    |  |

| 4   | C0       | 0             | to 50%.                                                                                                                                                                                                                                                                        |  |

| 3   | NS2      | 0             | Reserved, must be set to 0.                                                                                                                                                                                                                                                    |  |

| 2   | NS1      | 0             | Acts on register 2. NS2=0 prescales the N counter by 2. NS2=1 prescales the P counter value to 4.                                                                                                                                                                              |  |

| 1   | NS0      | 0             | Acts on register 1. NS1=0 prescales the N counter by 2. NS1=1 prescales the P counter value to 4.                                                                                                                                                                              |  |

|     |          |               | Acts on register 0. NS0=0 prescales the P counter by 2. NS0=1 prescales the P counter value to 4.                                                                                                                                                                              |  |

## **Serial Programming Architecture**

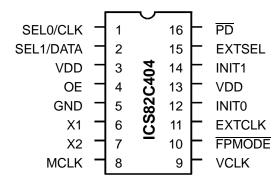

The pins SEL0 and SEL1 perform the dual functions of selecting registers and serial programming. In serial programming mode, SEL0 acts as a clock pin while SEL1 acts as the data pin. The ICS82C404-01 may not be serially programmed when in power-down mode.

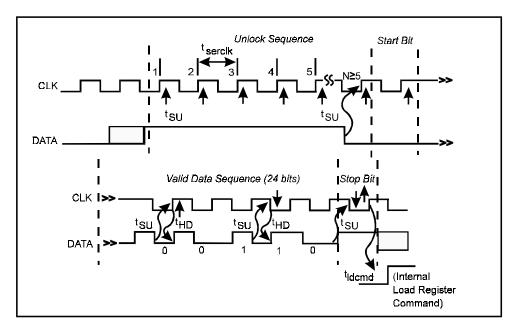

In order to program a particular register, an unlocking sequence must occur. The unlocking sequence is detailed in the following timing diagram:

The unlock sequence consists of at least five low-to-high transitions of CLK while data is high, followed immediately by a single low-to-high transition while data is low. Following this unlock sequence, data can be loaded into the serial data register.

Following any transition of CLK or DATA, the watchdog timer is reset and begins counting. The watchdog timer ensures that successive rising edges of CLK and DATA do not violate the time-out specification of 2ms. If a time-out occurs, the lock mechanism is reset and the data in the serial data register is ignored.

Since the VCLK registers are selected by the SEL0 and SEL1 pins, and since any change in their state may affect the output frequency, new data input on the selection bits is only permitted to pass through the decode logic after the watchdog timer has timed out. This delay of SEL0 or SEL1 data permits a serial program cycle to occur without affecting the current register selection.

## **Serial Data Register**

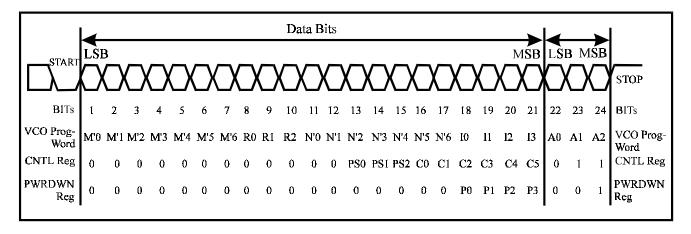

The serial data is clocked into the serial data register in the order described in Figure 1 below (Serial Data Timing).

The serial data is sent as follows: An individual data bit is sampled on the rising edge of CLK. The complement of the data bit must be sampled on the previous falling edge of CLK. The set-up and hold time requirements must be met on both CLK edges. For specifics on timing, see the timing diagrams on pages 10, 11 and 12.

The bits are shifted in this order: a start bit, 21 data bits, 3 address bits (which designate the desired register), and a stop bit. A total of 24 bits must always be loaded into the serial data register or an error is issued. Following the entry of the last data bit, a stop bit or load command is issued by bringing DATA high and toggling CLK high-to-low and low-to-high. The unlocking mechanism then resets itself following the load. Only after a time-out period are the SEL0 and SEL1 pins allowed to return to a register selection function.

Figure 1: Serial Data Timing

### ICS82C404

$F_{CLK} \le 120 \text{ MHz}$

The serial data register is exactly 24 bits long, enough to accept the data being sent. The stop bit acts a load command that passes the contents of the Serial Data Register into the register indicated by the three address bits. If a stop bit is not received after the serial register is full, and more data is sent, all data in the register is ignored and an error issued. If correct data is received, then the unlocking mechanism rearms, all data in the serial data register is ignored, and an error is issued.

### Programming the ICS82C404

The ICS82C404 has a wide operating range, but it is recommended that it is operated within the following limits:

$1 \text{ MHz} < F_{REF} < 60 \text{ MHz}$  Free=Input

3 to 129

$50 \text{ MHz} < F_{VCO} < 120 \text{ MHz}$   $F_{VCO} = VCO \text{ output}$

frequency

FCLK=output

frequency

The frequency of the programmable oscillator F<sub>VCO</sub> is determined by the following fields:

| Field                | # of Bits |

|----------------------|-----------|

| Index (I)            | 4         |

| N counter value (N') | 7         |

| Mux (R)              | 3         |

| M counter value (M') | 7         |

Where the least significant bit is the last bit of M and the most significant bit is the first bit of 1.

The equations used to determine the oscillator frequency are:

$\begin{array}{cc} N=N'+3 & M=M'+2 \\ F_{VCO}=Prescale \bullet N/M \bullet F_{CLK} \\ where \leq M \leq 129 \text{ and } 4 \leq N \leq 130 \\ \text{and prescale=2 or 4, as set in the control register} \end{array}$

The value of  $F_{VCO}$  must remain between 50 MHz and 120 MHz. As a result, for output frequencies below 50 MHz,  $F_{VCO}$  must be brought into range. To achieve this, an output divisor is selected by setting the values of the Mux Field (R) as follows:

#### **Output Divisor**

| R   | Divisor |

|-----|---------|

| 000 | 1       |

| 001 | 2       |

| 010 | 4       |

| 011 | 8       |

| 100 | 16      |

| 101 | 32      |

| 110 | 64      |

| 111 | 128     |

Unlike the ICD's 82C404, the **ICS82C404**'s VCO does not require tuning to place it in certain ranges. The **ICS82C404**'s VCO will operate from 50 MHz to 120 MHz without adjusting the VCO gain. However, to maintain compatibility, the I bits are programmed as in the ICD2061A.

These bits are dummy bits except for the following two cases:

#### Index Field (I)

| I    | VCLK F <sub>VCO</sub> | MCLK F <sub>VCO</sub> |

|------|-----------------------|-----------------------|

| 1110 | Turn off VCLK         | 50-120 MHz            |

| 1111 | Mux MCLK to VLCK      | 50-120 MHz            |

When the index field is set to 1111, VCLK is turned off and both channels run from the same MCLK VCO. This is done in an effort to reduce jitter, which may increase when VCOs run at 2<sup>n</sup> multiples of one another. If the two outputs must be multiples of one another, it is best to mux MCLK over to the output of the VCLK VCO, and to power-down the VCLK VCO. The multiplexed frequency will be divided down by the correct divisor (M) and output on VCLK.

### **Power Management Issues**

#### Power-down mode 1

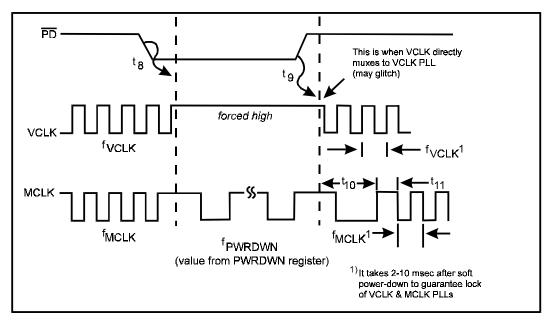

The ICS82C404 contains a mechanism to reduce the quiescent power when stand-by operation is desired. Power-down mode 1 is invoked by pulling  $\overline{PD}$  low and having the proper CNTL register bit set to zero. In this mode, VCOs are shut down, the VCLK output is forced high, and the MCLK output is set to a user-defined low frequency value to refresh dynamic RAM.

The power-down MCLK value is determined by the following equation:

MCLK<sub>PD</sub>=F<sub>REF</sub>/(PWRDWN register divisor value)

The power-down register divisor is determined according to the 4-bit word programmed into the PWRDWN register (see table below).

#### Power-down Mode 2

When there is no need for any output during power-down, an alternate mode is available which will completely shut down all outputs and the reference oscillator, but still preserves all register contents. Power-down mode 2 is invoked by the first programming the power-down bit in the CNTL register and then pulling the  $\overline{PD}$  pin low.

#### The PD pin

The  $\overline{PD}$  pin has a standard internal pull-up resistor during normal operation. When the chip goes into power-down mode 1 or 2, the normal pull-up resistor is dynamically switched to a weak pull-up, which reduces power consumption. If the  $\overline{PD}$  pin is allowed to float after it has been pulled down, the weak pull-up will bring the signal high and allow the device to resume operation.

### **Power-Down Register Table**

| PWRDWN bits |    |    |    | PWRDWN         | Power-down | MCLK <sub>PD</sub>           |

|-------------|----|----|----|----------------|------------|------------------------------|

| P3          | P2 | P1 | P0 | Register Value | Divisor    | (f <sub>REF</sub> =14.31818) |

| 0           | 0  | 0  | 0  | 0              | n/a        | n/a                          |

| 0           | 0  | 0  | 1  | 1              | 32         | 447.4 kHz                    |

| 0           | 0  | 1  | 0  | 2              | 30         | 477.3 kHz                    |

| 0           | 0  | 1  | 1  | 3              | 28         | 511.4 kHz                    |

| 0           | 1  | 0  | 0  | 4              | 26         | 550.7 kHz                    |

| 0           | 1  | 0  | 1  | 5              | 24         | 596.6 kHz                    |

| 0           | 1  | 1  | 0  | 6              | 22         | 650.8 kHz                    |

| 0           | 1  | 1  | 1  | 7              | 20         | 715.9 kHz                    |

| 1           | 0  | 0  | 0  | 8 (default)    | 18         | 795.5 kHz                    |

| 1           | 0  | 0  | 1  | 9              | 16         | 894.9 kHz                    |

| 1           | 0  | 1  | 0  | A              | 14         | 1.02 MHz                     |

| 1           | 0  | 1  | 1  | В              | 12         | 1.19 MHz                     |

| 1           | 1  | 0  | 0  | C              | 10         | 1.43 MHz                     |

| 1           | 1  | 0  | 1  | D              | 8          | 1.79 MHz                     |

| 1           | 1  | 1  | 0  | E              | 6          | 2.39 MHz                     |

| 1           | 1  | 1  | 1  | F              | 4          | 3.58 MHz                     |

## ICS82C404

## **Absolute Maximum Ratings**

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Electrical Characteristics**

$V_{DD} = +5V \pm 5\%$ ,  $0^{\circ}C \le T_{AMBIENT} \le +70^{\circ}C$  unless otherwise stated

| Maximum Ratings                    |                   |      |          |        |  |  |

|------------------------------------|-------------------|------|----------|--------|--|--|

| PARAMETER                          | SYMBOL            | MIN  | MAX      | UNITS  |  |  |

| Supply voltage relative to GND     | VDD               | -0.5 | 7.0      | Volts  |  |  |

| Input voltage with respect to GND  | $V_{\rm IN}$      | -0.5 | VDD +0.5 | Volts  |  |  |

| Operating temperature              | T <sub>OPER</sub> | 0    | +70      | °C     |  |  |

| Storage temperature                | $T_{STOR}$        | -65  | +150     | °C     |  |  |

| Max soldering temperature (10 sec) | $T_{SOL}$         |      | +260     | °C     |  |  |

| Junction temperature               | $T_{j}$           |      | +125     | °C     |  |  |

| Package power dissipation          | P <sub>DISS</sub> |      | 350      | mWatts |  |  |

| DC Characteristics             |                     |                        |      |     |      |       |  |  |

|--------------------------------|---------------------|------------------------|------|-----|------|-------|--|--|

| PARAMETER                      | SYMBOL              | TEST CONDITIONS        | MIN  | TYP | MAX  | UNITS |  |  |

| High level input voltage       | V <sub>IH</sub>     |                        | 2.0  |     |      | V     |  |  |

| Low level input voltage        | $V_{\rm IL}$        |                        |      |     | 0.8  | V     |  |  |

| High level CMOS output voltage | $V_{OH}$            | I <sub>OH</sub> =-4ma  | 3.84 |     |      | V     |  |  |

| Low level output voltage       | V <sub>OL</sub>     | I <sub>OL</sub> =4ma   |      |     | 0.4  | V     |  |  |

| Input high current             | $I_{IH}$            | V <sub>IH</sub> =5.25V |      |     | 100  | μΑ    |  |  |

| Input low current              | $I_{\rm IL}$        | V <sub>IL</sub> =0V    |      |     | -250 | μΑ    |  |  |

| Output leakage current         | Ioz                 | (tristate)             |      |     | 10   | μΑ    |  |  |

| Power supply current           | $I_{DD}$            |                        | 15   |     | 65   | ma    |  |  |

| Power supply current (typical) | I <sub>DD-TYP</sub> | @60 MHz                |      | 35  |      | ma    |  |  |

| Analog power supply current    | I <sub>ADD</sub>    |                        |      |     | 20   | ma    |  |  |

| Power-down current (Mode 1)    | I <sub>PD1</sub>    |                        |      | 6   | 7.5  | ma    |  |  |

| Power-down current (Mode 2)    | $I_{PD2}$           |                        |      | 25  | 50   | μΑ    |  |  |

| Input capacitance              | C <sub>IN</sub>     |                        |      |     | 10   | pF    |  |  |

## **Electrical Characteristics** (continued)

| AC Characteristics                                                                          |                            |                       |                           |                      |                       |       |

|---------------------------------------------------------------------------------------------|----------------------------|-----------------------|---------------------------|----------------------|-----------------------|-------|

| DESCRIPTION                                                                                 | NAME                       | SYMBOL                | MIN                       | TYP                  | MAX                   | UNITS |

| Reference oscillator value (Note 1)                                                         | Reference<br>frequency     | f <sub>REF</sub>      | 1                         | 14.31818             | 60                    | MHz   |

| 1/f <sub>REF</sub>                                                                          | Reference period           | tref                  | 16.6                      |                      | 1000                  | ns    |

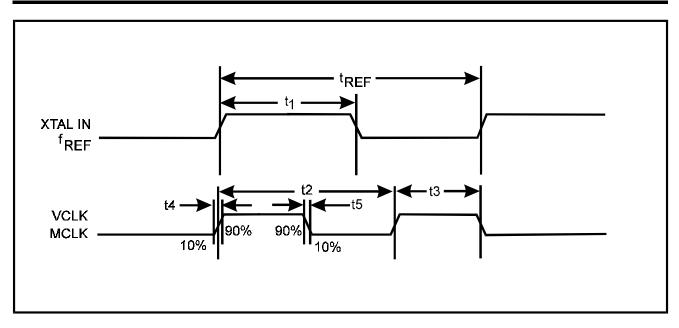

| Duty cycle for the input oscillator defined as t <sub>1</sub> /t <sub>REF</sub>             | Input duty cycle           | t <sub>1</sub>        | 25%                       |                      | 75%                   |       |

| Output oscillator values                                                                    | Output clock periods       | t <sub>2</sub>        | 8.33<br>(120 MHz)         |                      | 2564<br>(390 kHz)     | ns    |

| Duty cycle for the output oscillators (Note 2)                                              | Output duty cycle          | t <sub>3</sub>        | 45%                       |                      | 55%                   |       |

| Rise time for the output oscillators into a 25pF load                                       | Rise times                 | t4                    |                           |                      | 3                     | ns    |

| Fall time for the output oscillators into a 25pF load                                       | Fall times                 | t <sub>5</sub>        |                           |                      | 3                     | ns    |

| Old frequency output                                                                        | freq1 output               | t <sub>freq1</sub>    |                           |                      |                       |       |

| New frequency output                                                                        | freq2 output               | t <sub>freq2</sub>    |                           |                      |                       |       |

| Time clock output remains high while output muxes to reference frequency                    | fref mux time              | tA                    | $0.5_{\mathrm{t_{REF}}}$  |                      | 1.5 <sub>tref</sub>   | ns    |

| Interval for serial programming and for VCO changes to settle (Note 3)                      | Time-out interval          | t <sub>time-out</sub> | 2                         | 5                    | 10                    | ms    |

| Time clock output remains high while output muxes to new frequency value                    | t <sub>freq2</sub> muxtime | tB                    | $^{0.5}$ t <sub>REF</sub> | 1.5 t <sub>REF</sub> |                       | ns    |

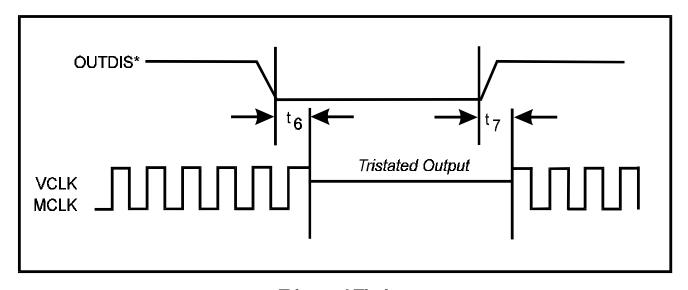

| Time for the output oscillators to go into tristate mode after OUTDIS-signal assertion      | Tristate                   | t <sub>6</sub>        |                           |                      | 12                    | ns    |

| Time for the output oscillators to recover from tristate mode after OUTDIS-signal goes high | CLK valid                  | t7                    |                           |                      | 12                    | ns    |

| Time for power-down mode of operation to take effect                                        | Power-Down                 | t8                    |                           |                      | 12                    | ns    |

| Time for recovery from power-down mode to a valid CLK                                       | Power-Up                   | t9                    |                           |                      | 12                    | ns    |

| Time for MCLK to go high after PWRDWN is asserted high                                      | MCLKOUT high               | t <sub>10</sub>       | 0                         |                      | tpwrdwn               | ns    |

| Delay of MCLK prior to f <sub>MCLK</sub> signal at output                                   | MCLKOUT delay              | t <sub>11</sub>       | 0.5 t <sub>MCLK</sub>     |                      | 1.5 t <sub>MCLK</sub> | ns    |

| Clock period of serial clock                                                                |                            | tserclk               | 2 • tref                  |                      | 2                     | ms    |

| Set-up time                                                                                 |                            | tsu                   | 20                        |                      |                       | ns    |

| Hold time                                                                                   |                            | tHD                   | 10                        |                      |                       | ns    |

| Load command                                                                                |                            | tldemd                | 0                         |                      | t <sub>1</sub> +30    | ns    |

#### Notes:

- For reference frequencies other than 14.81818 MHz, the pre-loaded ROM frequencies will shift proportionally. Duty cycle is measured at CMOS threshold levels. At 5 volts,  $V_{TH}$ =2.5 volts. If the interval is too short, see the time-out interval section in the control register definition.

**Rise and Fall Times**

**Tristated Timing**

**Selection Timing**

**MCLK and Active VCLK Register Programming Timing**

**Soft Power-down Timing (Mode 2)**

**Serial Programming Timing**

16-Pin PDIP Package

16-Pin SOIC Package

## **Ordering Information**

ICS82C404N or 82C404M

Example:

ADVANCE INFORMATION documents contain information on new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.