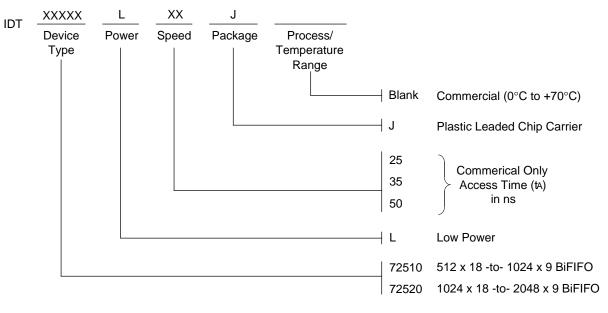

# **BUS-MATCHING BIDIRECTIONAL FIFO** 512 x 18-BIT - 1024 x 9-BIT 1024 x 18-BIT – 2048 x 9-BIT

# FEATURES:

- Two side-by-side FIFO memory arrays for bidirectional data transfers

- 512 x 18-Bit 1024 x 9-Bit (IDT72510)

- 1024 x 18-Bit 2048 x 9-Bit (IDT72520)

- 18-bit data bus on Port A side and 9-bit data bus on Port B side

- Can be configured for 18-to-9-bit, 36-to-9-bit, or 36-to-18bit communication

- · Fast 25ns access time

- Fully programmable standard microprocessor interface

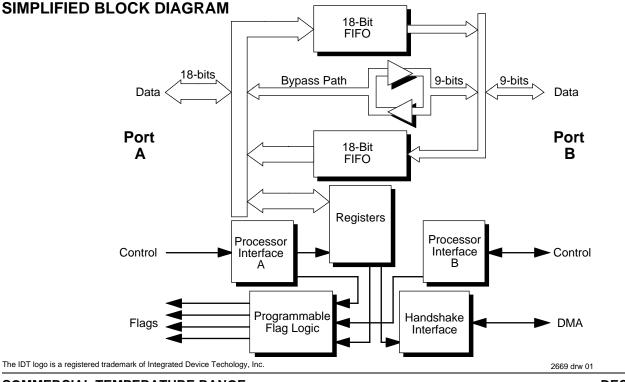

- Built-in bypass path for direct data transfer between two ports

- Two fixed flags, Empty and Full, for both the A-to-B and the B-to-A FIFO

- Two programmable flags, Almost-Empty and Almost-Full for each FIFO

- · Programmable flag offset can be set to any depth in the **FIFO**

- Any of the eight internal flags can be assigned to four external flag pins

- Flexible reread/rewrite capabilities.

- On-chip parity checking and generation

- · Standard DMA control pins for data exchange with peripherals

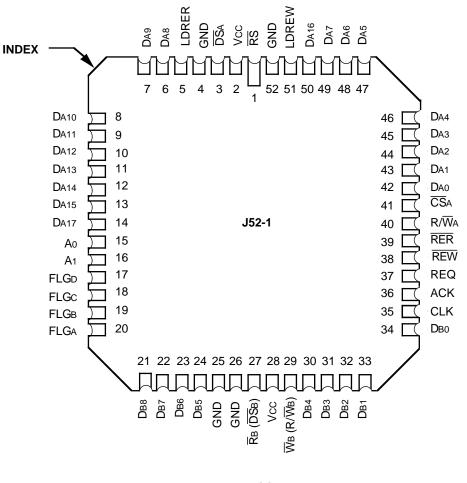

- IDT72510 and IDT72520 available in the the 52-pin PLCC package

## **DESCRIPTION:**

The IDT72510 and IDT72520 are highly integrated firstin, first-out memories that enhance processor-to-processor and processor-to-peripheral communications. IDT BiFIFOs integrate two side-by-side memory arrays for data transfers in two directions.

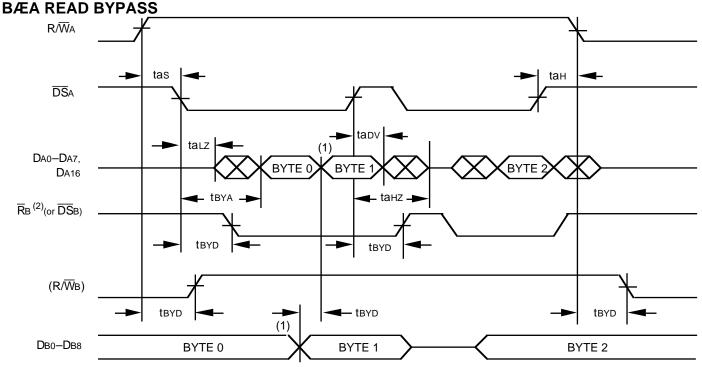

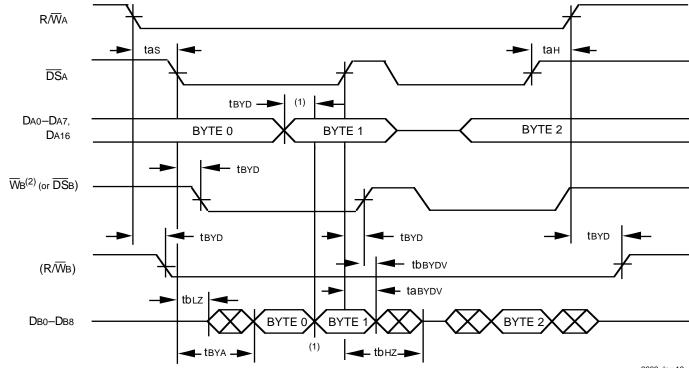

The BiFIFOs have two ports, A and B, that both have standard microprocessor interfaces. All BiFIFO operations are controlled from the 18-bit wide Port A. The BiFIFOs incorporate bus matching logic to convert the 18-bit wide memory data paths to the 9-bit wide Port B data bus. The BiFIFOs have a bypass path that allows the device connected to Port A to pass messages directly to the Port B device.

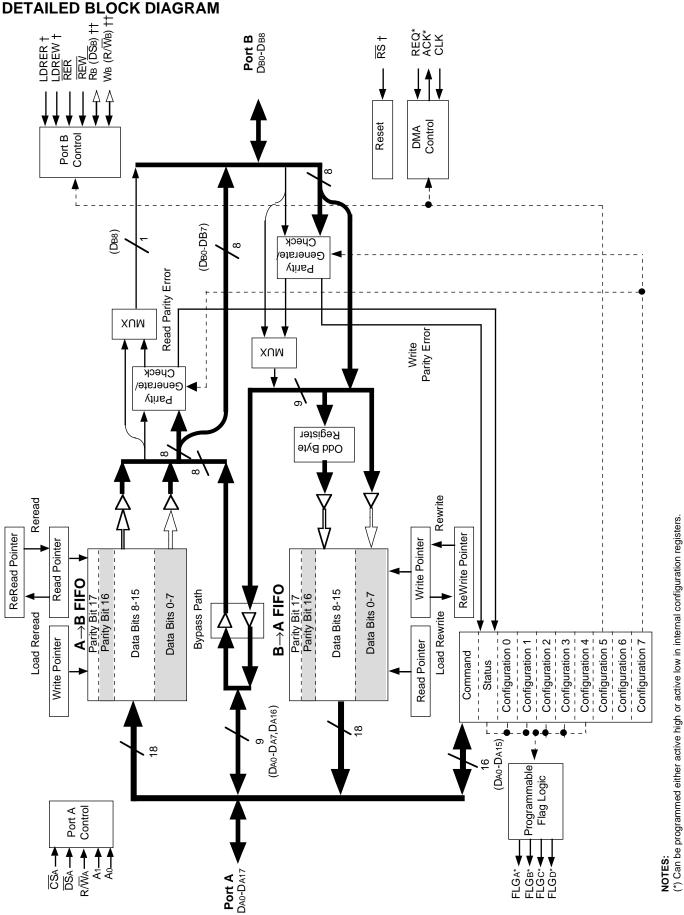

Ten registers are accessible through Port A, a Command Register, a Status Register, and eight Configuration Registers.

The IDT BiFIFOs have programmable flags. Each FIFO memory array has four internal flags, Empty, Almost-Empty, Almost-Full and Full, for a total of eight internal flags. The Almost-Empty and Almost-Full flag offsets can be set to any depth through the Configuration Registers. These eight internal flags can be assigned to any of four external flag pins (FLGA-FLGD) through one Configuration Register.

Port B has parity, reread/rewrite and DMA functions. Parity generation and checking can be done by the BiFIFO on data passing through Port B. The Reread and Rewrite con-

# SIMPLIFIED BLOCK DIAGRAM

## **COMMERCIAL TEMPERATURE RANGE**

©1996 Integrated Device Technology, Inc. For latest information contact IDT's web site at www.idt.com or fax-on-demand at 408-492-8391. 5.31 trols will read or write Port B data blocks multiple times. The BiFIFOs have three pins, REQ, ACK and CLK, to control DMA transfers from Port B devices.

## **PIN CONFIGURATION**

PLCC TOP VIEW

# PIN DESCRIPTIONS

| Symbol    | Name          | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DA0-DA15  | Data A        | I/O    | Data inputs and outputs for 16 bits of the 18-bit Port A bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DA16-DA17 | Parity A      | I/O    | DA16 is the parity bit for DA0-DA7. DA17 is the parity bit for DA8-<br>DA15. DA16 and DA17 can be used as two extra data bits if the<br>parity generate function is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CSA       | Chip Select A | I      | Port A is accessed when Chip Select A is LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

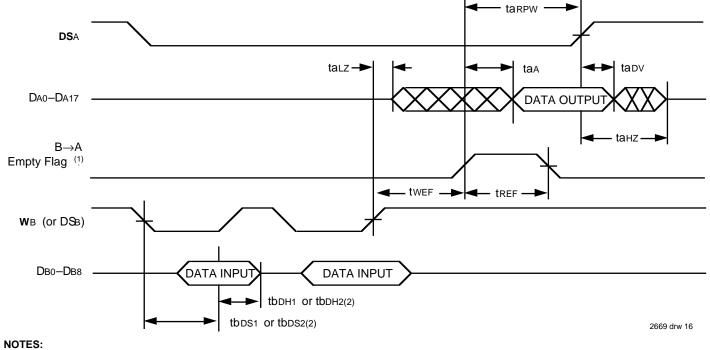

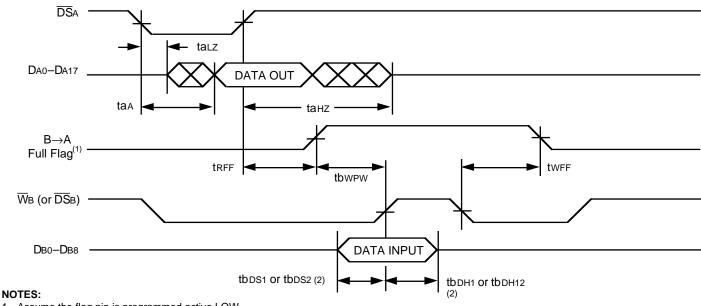

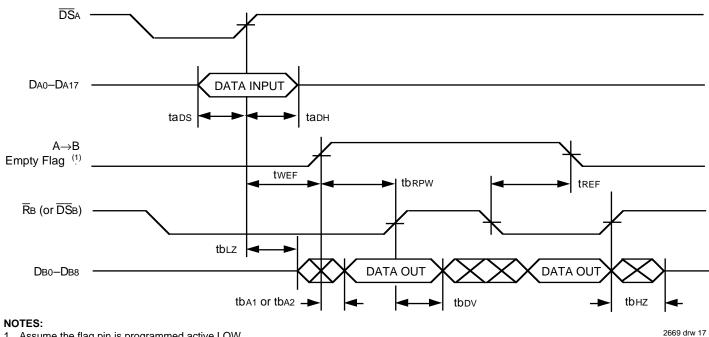

| DSA       | Data Strobe A | I      | Data is written into Port A on the rising edge of Data Strobe when<br>Chip Select is LOW. Data is read out of Port A on the falling edge of<br>Data Strobe when Chip Select is LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R/WA      | Read/Write A  | I      | This pin controls the read or write direction of Port A. When $\overline{CS}A$ is LOW and R/WA is HIGH, data is read from Port A on the falling edge of $\overline{DS}A$ . When $\overline{CS}A$ is LOW and R/WA is LOW, data is written into Port A on the rising edge of $\overline{DS}A$ .                                                                                                                                                                                                                                                                                                                                                                |

| A0, A1    | Addresses     | I      | When Chip Select A is asserted, A0, A1, and Read/Write A are used to select one of six internal resources.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DB0-DB7   | Data B        | Ι/Ο    | Data inputs and outputs for 8 bits of the 9-bit Port B bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DB8       | Parity B      | Ι/Ο    | DB8 is the parity bit for DB0-DB7. DB8 can be used as a data bit if the parity generate function is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RB (DSB)  | Read B        | I or O | If Port B is programmed to processor mode, this pin functions as an input. If Port B is programmed to peripheral mode this pin functions as an output. This pin can function as part of an Intel-style interface ( $\overline{RB}$ ) or as part of a Motorola-style interface ( $\overline{DSB}$ ). As an Intel-style interface, data is read from Port B on a falling edge of $\overline{RB}$ . As a Motorola-style interface, data is read on the falling edge of $\overline{DSB}$ or written on the rising edge of $\overline{DSB}$ through Port B. The Default is Intel-style style processor mode ( $\overline{RB}$ as an input).                       |

| WB (R/WB) | Write B       | I or O | If Port B is programmed to processor mode, this pin functions as an input. If Port B is programmed to peripheral mode this pin functions as an output. This pin can function as part of an Intel-style interface ( $\overline{WB}$ ) or as part of a Motorola-style interface ( $R/\overline{WB}$ ). As an Intel style interface, data is written to Port B on a rising edge of $\overline{WB}$ . As a Motorola-style interface, data is read ( $R/\overline{WB}$ = HIGH) or written ( $R/\overline{WB}$ = LOW) to Port B in conjunction with a Data Strobe B falling or rising edge. The Default is Intel-style processor mode ( $\overline{WB}$ as input). |

| RER       | Reread        | I      | Loads A-to-B FIFO Read Pointer with the value of the Reread Pointer when LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| REW       | Rewrite       | I      | Loads B-to-A FIFO Write Pointer with the value of the Rewrite Pointer when LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LDRER     | Load Reread   | I      | Loads the Reread Pointer with the value of the A-to-B FIFO Read<br>Pointer when HIGH. This signal is accessible through the Command<br>Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LDREW     | Load Rewrite  | I      | Loads the Rewrite Pointer with the value of the B-to-A FIFO Write<br>Pointer when HIGH. This signal is accessible through the Command<br>Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| REQ       | Request       | I      | When Port B is programmed in peripheral mode, asserting this pin begins a data transfer. Request can be programmed either active HIGH or active LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# PIN DESCRIPTIONS

| Symbol    | Name        | I/O | Description                                                                                                                                                                                                                                                                                                                   |

|-----------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK       | Acknowledge | 0   | When Port B is programmed in peripheral mode, Acknowledge is asserted in response to a Request signal. This confirms that a data transfer may begin. Acknowledge can be programmed either active HIGH or active LOW.                                                                                                          |

| CLK       | Clock       | I   | This pin is used to generate timing for ACK, $\overline{R}B$ , $\overline{W}B$ , $\overline{DS}B$ and $R/\overline{W}B$ when Port B is in the peripheral mode.                                                                                                                                                                |

| FLGA-FLGD | Flags       | 0   | These four outputs pins can be assigned to any one of the eight<br>internal flags in the BiFIFO. Each of the two internal FIFOs (A-to-B<br>and B-to-A) has four internal flags: Empty, Almost-Empty, Almost-<br>Full, and Full. If parity checking is enabled, the FLGA pin can also<br>be assigned as a parity error output. |

| RS        | Reset       | I   | A LOW on this pin will perform a reset of all BiFIFO functions.<br>Software reset can be achieved through command register.                                                                                                                                                                                                   |

| VCC       | Power       |     | There are two +5V power pins on all four devices.                                                                                                                                                                                                                                                                             |

| GND       | Ground      |     | There are four ground pins                                                                                                                                                                                                                                                                                                    |

2669 drw 03

Accessible through internal registers.

Can be programmed through an internal through an international contents.

Can be programmed through an internal configuration register to be either an input or an output.

## FUNCTIONAL DESCRIPTION

IDT's BiFIFO family is versatile for both multiprocessor and peripheral applications. Data can be sent through both FIFO memories concurrently, thus freeing both processors from laborious direct memory access (DMA) protocols and frequent interrupts.

Two full 18-bit wide FIFOs are integrated into the IDT BiFIFO, making simultaneous data exchange possible. Each FIFO is monitored by separate internal read and write pointers, so communication is not only bidirectional, it is also totally independent in each direction. The processor connected to Port A of the BiFIFO can send or receive messages directly to the Port B device using the BiFIFO's 9-bit bypass path.

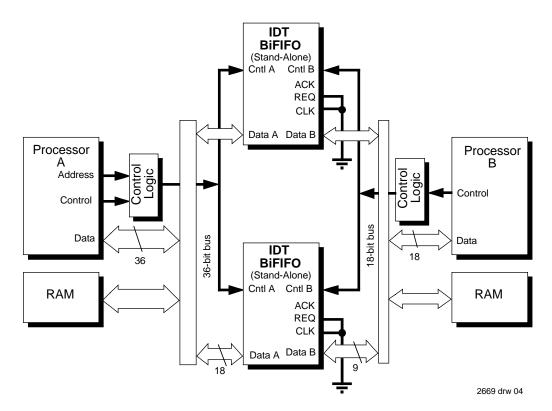

The BiFIFOs can be used in three different bus configurations: 18 bits to 9 bits, 36 bits to 9 bits and 36 bits to 18 bits. One BiFIFO can be used for the 18- to 9-bit configuration, and two BiFIFOs are required for 36- to 9-bit or 36- to 18-bit configurations. Bits 11 and 12 of Configuration Register 5 determine the BiFIFO configuration (see Table 11 for Configuration Register 5 format). The microprocessor or microcontroller connected to Port A controls all operations of the BiFIFOs. Thus, all Port A interface pins are inputs driven by the controlling processor. Port B can be programmed to interface either with a second processor or a peripheral device. When Port B is programmed in processor interface mode, the Port B interface pins are inputs driven by the second processor. If a peripheral device is connected to the BiFIFOs, Port B is programmed to peripheral interface mode and the interface pins are outputs.

#### 18- to 9-bit Configurations

A single BiFIFO can be configured to connect an 18-bit processor to another 9-bit processor or a 9-bit peripheral. Bits 11 and 12 of Configuration Register 5 should be set to **00** for a stand-alone configuration. Figures 1 and 2 show the BiFIFO in 18- to 9-bit configurations for processor and peripheral interface modes respectively.

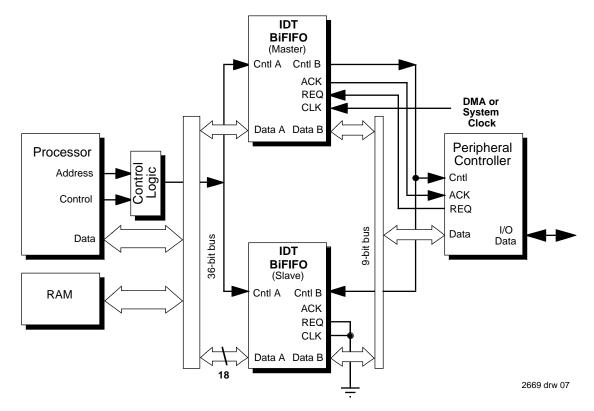

#### 36- to 9-bit Configurations

Two BiFIFOs can be hooked together to create a 36-bit to 9-bit configuration. This means that a 36-bit processor can

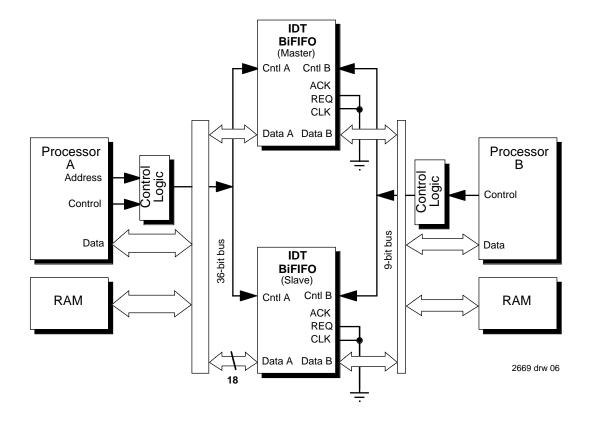

## **36-BIT PROCESSOR to 18-BIT PROCESSOR CONFIGURATION**

Figure 1. 36- to 18-Bit Processor Interface Configuration

#### NOTE:

1. Upper BiFIFO only is used in 18- to 9-bit configuration. Note that *Cntl A* refers to  $\overline{CSA}$ , A1, A0, R/ $\overline{WA}$  and  $\overline{DSA}$ ; *Cntl B* refers to R/ $\overline{WB}$  and  $\overline{DSB}$  or  $\overline{RB}$  and  $\overline{WB}$ .

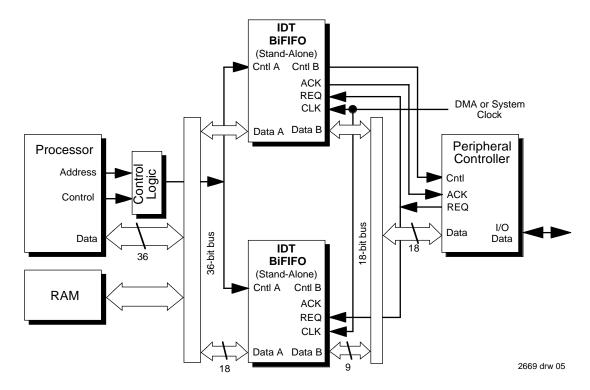

## **36-BIT PROCESSOR to 18-BIT PERIPHERAL CONFIGURATION**

Figure 2. 36- to 18-Bit Peripheral Interface Configuration

#### NOTE:

1. Upper BiFIFO only is used in 18- to 9-bit configuration. Note that *Cntl A* refers to CSA, A1, A0, R/WA and DSA; *Cntl B* refers to R/WB and DSB or RB and WB.

talk to a 9-bit processor or a 9-bit peripheral. Both BiFIFOs are programmed simultaneously through Port A by placing one command word on the most significant 16 data bits and one command word on the least significant 16 data bits (parity bits should be ignored).

One BiFIFO must be programmed as the master device and the other BiFIFO is the slave device. Bits 11 and 12 of Configuration Register 5 are set to **10** for the slave device and **11** for the master device. The first two 9-bit words on Port B are read from or written to the slave device and the next two 9-bit words go to the master device.

When both BiFIFOs are in peripheral interface mode, the Port B interface pins of the master device are outputs and this BiFIFO controls the bus. The Port B interface pins of the slave device are inputs driven by the master BiFIFO. Two BiFIFOs are connected in Figure 4 to create a 36- to 9-bit peripheral interface.

The two BiFIFOs shown in Figure 3 are configured to connect a 36-bit processor to a 9-bit processor.

#### 36- to 18-bit Configurations

In a 36- to 18-bit configuration, two BiFIFOs operate in parallel. Both BiFIFOs are programmed simultaneously, 16 data bits to each device with the 4 parity bits ignored.

Both BiFIFOs must be programmed into stand-alone mode for a 36-bit processor to communicate with an 18-bit processor or an 18-bit peripheral. This means that bits 11 and 12 of Configuration Register 5 must be set to 00.

This configuration can be extended to wider bus widths (54- to 27-bits, 72- to 36-bits, ...) by adding more BiFIFOs to the configuration. Figures 1 and 2 show multiple BiFIFOs configured for processor and peripheral interface modes respectively.

#### **Processor Interface Mode**

When a microprocessor or microcontroller is connected to Port B, all BiFIFOs in the configuration must be programmed to processor interface mode. In this mode, all Port B interface controls are inputs. Both REQ and CLK pins should be pulled LOW to ensure that the set-up and hold time requirements for these pins are met during reset. Figures 1 and 3 show BiFIFOs in processor interface mode.

#### Peripheral Interface Mode

If Port B is connected to a peripheral controller, all BiFIFOs in the configuration must be programmed in the peripheral interface mode. To assure fixed high states for  $\overline{R}B$  and  $\overline{W}B$  before they are programmed into an output, both pins should be pulled-up to VCC with 10K resistors.

If the BiFIFOs are in stand-alone configuration mode (18- to 9-bit, 36- to 18-bit, ...), then the Port B interface pins are all outputs. Of course, only one set of Port B interface pins should be used to control a single peripheral device, while the other interface pins are all ignored. Figure 2 shows stand-

alone configuration BiFIFOs connected to a peripheral.

In a 36- to 9-bit configuration, the master device controls the bus. The Port B interface pins of the master device are outputs and the interface pins of the slave device are inputs. A 36- to 9-bit configuration of two BiFIFOs connected to a peripheral is shown in Figure 4.

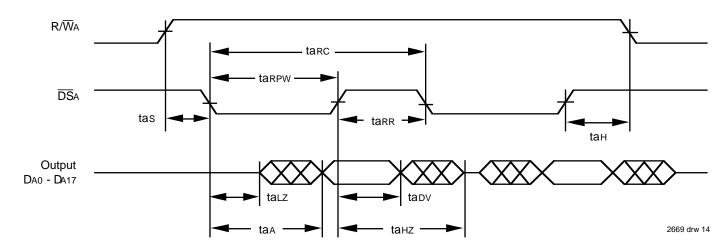

#### **Port A Interface**

The BiFIFO is straightforward to use in microprocessorbased systems because each BiFIFO port has a standard microprocessor control set. Port A has access to six resources: the  $A \rightarrow B$  FIFO, the  $B \rightarrow A$  FIFO, the 9-bit direct data bus (bypass path), the configuration registers, status and command registers. The Port A Address and Read/Write pins determine the resource being accessed as shown in Table 1. Data Strobe is used to move data in and out of the BiFIFO.

When either of the internal FIFOs are accessed 18 bits of data are transferred across Port A. Since the bypass path is only 9 bits wide, the least significant byte with parity (DA0-DA7, DA16) is used on Port A. All of the registers are 16 bits wide which means only the data bits (DA0-DA15) are passed by Port A.

## **36-BIT PROCESSOR to 9-BIT PROCESSOR CONFIGURATION**

Figure 3. 36- to 9-Bit Processor Interface Configuration

#### NOTE:

1. *Cntl A* refers to  $\overline{CSA}$ , A1, A0, R/ $\overline{WA}$  and  $\overline{DSA}$ ; *Cntl B* refers to R/ $\overline{WB}$  and  $\overline{DSB}$  or  $\overline{RB}$  and  $\overline{WB}$ .

NOTE:

## **36-BIT PROCESSOR to 9-BIT PERIPHERAL CONFIGURATION**

Figure 4. 36- to 9-Bit Peripheral Interface Configuration

1. Cntl A refers to CSA, A1, A0, R/WA and DSA; Cntl B refers to R/WB and DSB or RB and WB.

## PORT A RESOURCES

| CSA | <b>A</b> 1 | A0 | Read                       | Write                      |

|-----|------------|----|----------------------------|----------------------------|

| 0   | 0          | 0  | B→A FIFO                   | A→B FIFO                   |

| 0   | 0          | 1  | 9-bit Bypass Path          | 9-bit Bypass Path          |

| 0   | 1          | 0  | Configuration<br>Registers | Configuration<br>Registers |

| 0   | 1          | 1  | Status Register            | Command Register           |

| 1   | Х          | Х  | Disabled                   | Disabled                   |

2669 tbl 03

Table 1. Accessing Port A Resources Using CSA, A0, and A1

#### **Bypass Path**

The bypass path acts as a bidirectional bus transceiver directly between Port A and Port B. The direct connection requires that the Port A interface pins are inputs and the Port B interface pins are outputs. The bypass path is 9 bits wide in an 18- to 9-bit configuration or in a 36- to 9-bit configuration. Only in the 36- to 18-bit configuration is the bypass path 18 bits wide.

During bypass operations, the BiFIFOs must be programmed into peripheral interface mode. Bit 10 of Configuration Register 5 (see Table 11) is set to **1** for peripheral interface mode. In a 36- to 9-bit configuration, both Port B data buses will be active. Data written into Port A will appear on both master and slave Port B buses concurrently. To avoid Port B bus contention, the data on DA0-DA7 and DA16 of both BiFIFOs should be exactly the same. Data read from Port A will appear on pins DA0-DA7 and DA16 of both BiFIFOs within the same 36bit word.

### **Command Register**

Ten registers are accessible through Port A, a Command Register, a Status Register, and eight Configuration Registers.

The Command Register is written by setting  $\overline{CSA} = 0$ , A1 = 1, A0 = 1. Commands written into the BiFIFO have a 4-bit opcode (bit 8 – bit 11) and a 3-bit operand (bit 0 – bit 2) as shown in Figure 5. The commands can be used to reset the BiFIFO, to select the Configuration Register, to perform intelligent reread/rewrite, to set the Port B DMA direction, to set the Status Register format, to modify the Port B Read and Write Pointers, and to clear Port B parity errors. The command opcodes are shown in Table 2.

The reset command initializes different portions of the BiFIFO depending on the command operand. Table 3 shows the reset command operands.

The Configuration Register address is set directly by the command operands shown in Table 4.

Intelligent reread/rewrite is performed by changing the Port B Read Pointer with the Reread Pointer or by changing the

## **COMMAND OPERATIONS**

| Command<br>Opcode | Function                                                            |

|-------------------|---------------------------------------------------------------------|

| 0000              | Reset BiFIFO (see Table 3)                                          |

| 0001              | Select Configuration Register (see Table 4)                         |

| 0010              | Load Reread Pointer with Read Pointer Value                         |

| 0011              | Load Rewrite Pointer with Write Pointer Value                       |

| 0100              | Load Read Pointer with Reread Pointer Value                         |

| 0101              | Load Write Pointer with Rewrite Pointer Value                       |

| 0110              | Set DMA Transfer Direction (see Table 5)                            |

| 0111              | Set Status Register Format (see Table 6)                            |

| 1000              | Increment in byte for $A \rightarrow B$ FIFO Read Pointer (Port B)  |

| 1001              | Increment in byte for $B \rightarrow A$ FIFO Write Pointer (Port B) |

| 1010              | Clear Write Parity Error Flag                                       |

| 1011              | Clear Read Parity Error Flag                                        |

Table 2. Functions Performed by Port A Commands

Port B Write Pointer with the Rewrite Pointer. No command operands are required to perform a reread/rewrite operation.

When Port B of the BiFIFO is in peripheral mode, the DMA direction is controlled by the Command Register. Table 5 shows the Port B read/write DMA direction operands.

The BiFIFO supports two Status Register formats. Status Register format 1 gives all the internal flag status, while Status Register format 0 provides the data in the Odd Byte Register. Table 6 gives the operands for selecting the appropriate Status Register format. See Table 8 for the details of the two Status Register formats.

Two commands are provided to increment the Port B Read and Write Pointers in case reread/rewrite is performed. Incrementing the pointers guarantees that pointers will be on a word boundary when an odd number of bytes is transmitted through Port B. No operands are required for these commands.

When parity check errors occur on Port B, a clear parity error command is needed to remove the parity error. There are no operands for these commands.

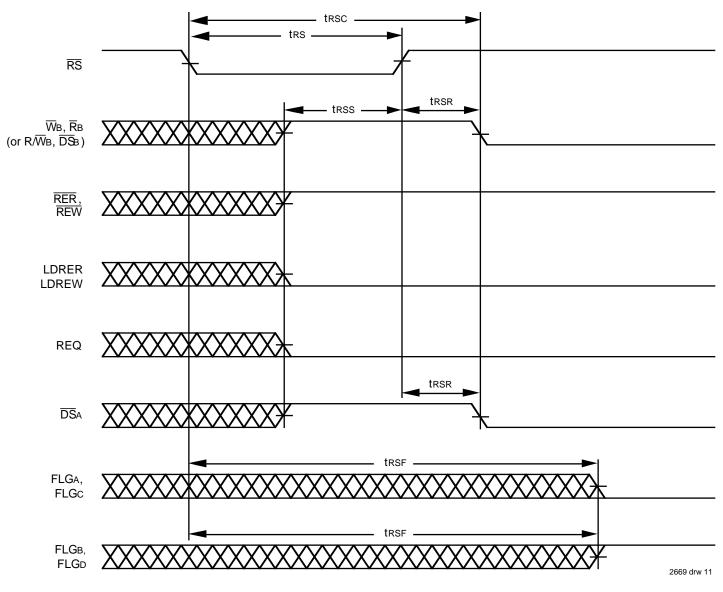

### Reset

The IDT72510 and IDT72520 have a hardware reset pin ( $\overline{RS}$ ) that resets all BiFIFO functions. A hardware reset requires the following four conditions:  $\overline{RB}$  and  $\overline{WB}$  must be HIGH, RER and REW must be HIGH, LDRER and LDREW must be LOW, and  $\overline{DSA}$  must be HIGH (Figure 9). After a hardware reset, the BiFIFO is in the following state: Configuration Registers 0-3 are **0000H**, Configuration Register 4 is set to

## **COMMAND FORMAT**

| 15 |   |   | 12 | 11             | 8 | 7 |   |   |   | 3 | 2       | 0       |

|----|---|---|----|----------------|---|---|---|---|---|---|---------|---------|

| Х  | Х | Х | Х  | Command Opcode |   | Х | Х | Х | Х | Х | Command | Operand |

Figure 5. Format for Commands Written into Port A

## **RESET COMMAND FUNCTIONS**

| Reset<br>Operands | Function                                                             |

|-------------------|----------------------------------------------------------------------|

| 000               | No Operation                                                         |

| 001               | Reset $B \rightarrow A$ FIFO (Read, Write, and Rewrite Pointers = 0) |

| 010               | Reset A $\rightarrow$ B FIFO (Read, Write, and Reread Pointers = 0)  |

| 011               | Reset $B \rightarrow A$ and $A \rightarrow B$ FIFO                   |

| 100               | Reset Internal DMA Request Circuitry                                 |

| 101               | No Operation                                                         |

| 110               | No Operation                                                         |

| 111               | Reset All                                                            |

2669 tbl 06

**Table 3. Reset Command Functions**

6420H, and Configuration Registers 5 and 7 are 0000H. Additionally, Status Register format 0 is selected, all the pointers including the Reread and Rewrite Pointers are set to 0, the odd byte register valid bit is cleared, the DMA direction is set to  $B \rightarrow A$  write, the internal DMA request circuitry is cleared (set to its initial state), and all parity errors are cleared.

A software reset command can reset  $A \rightarrow B$  pointers and the  $B \rightarrow A$  pointers to **0** independently or together. The request (REQ) DMA circuitry can also be reset independently. A software Reset All command resets all the pointers, the DMA request circuitry, and sets all the Configuration Registers to their default condition. Note that a hardware reset is **NOT** the same as a software Reset All command. Table 7 shows the BiFIFO state after the different hardware and software resets.

## SELECT CONFIGURATION REGISTER **COMMAND FUNCTIONS**

| Operands | Function                        |

|----------|---------------------------------|

| 000      | Select Configuration Register 0 |

| 001      | Select Configuration Register 1 |

| 010      | Select Configuration Register 2 |

| 011      | Select Configuration Register 3 |

| 100      | Select Configuration Register 4 |

| 101      | Select Configuration Register 5 |

| 110      | Select Configuration Register 6 |

| 111      | Select Configuration Register 7 |

2669 tbl 07

Table 4. Select Configuration Register Command Functions.

## DMA DIRECTION COMMAND FUNCTIONS

| Operands | Function       |

|----------|----------------|

| XX0      | Write B→A FIFO |

| XX1      | Read A→B FIFO  |

2669 tbl 08

Table 5. Set DMA Direction Command Functions. Command Only **Operates in Peripheral Interface Mode**

## STATUS REGISTER FORMAT COMMAND **FUNCTIONS**

| Operands | Function                 |

|----------|--------------------------|

| XX0      | Status Register Format 0 |

| XX1      | Status Register Format 1 |

|          | 2669 tbl 09              |

Table 6. Command Functions to Set the Status Register Format

## STATE AFTER RESET

|                                      | Hardware Reset |           |           | Software Rese        | t                            |           |

|--------------------------------------|----------------|-----------|-----------|----------------------|------------------------------|-----------|

|                                      | (RS asserted)  | B→A (001) | A→B (010) | B→A and<br>A→B (011) | Internal<br>Request<br>(100) | All (111) |

| Configuration Registers 0-3          | 0000H          |           | _         | _                    | _                            | 0000H     |

| Configuration Register 4             | 6420H          | —         |           |                      |                              | 6420H     |

| Configuration Register 5             | 0000H          | —         | _         | _                    | _                            | 0000H     |

| Configuration Register 7             | 0000H          | —         | _         | _                    | —                            | 0000H     |

| Status Register format               | 0              | —         |           | _                    |                              | _         |

| B→A Read, Write, Rewrite<br>Pointers | 0              | 0         | —         | 0                    | —                            | 0         |

| A→B Read, Write, Reread<br>Pointers  | 0              | —         | 0         | 0                    | _                            | 0         |

| Odd byte register valid bit          | clear          | clear     | _         | clear                | _                            | clear     |

| DMA direction                        | B→A write      | —         | _         | _                    | _                            | _         |

| DMA internal request                 | clear          | —         | _         | —                    | clear                        | clear     |

| Parity errors                        | clear          | _         | _         | _                    | _                            | _         |

Table 7. The BiFIFO State After a Reset Command

#### **Status Register**

The Status Register reports the state of the programmable flags, the DMA read/write direction, the Odd Byte Register valid bit, and parity errors. The Status Register is read by setting  $\overline{CS}A = 0$ , A1 = 1, A0 = 1 (see Table 1).

There are two Status Register formats that are set by a Status Register format command. Format 0 stores the Odd Byte Register data in the lower eight bits of the Status Register, while format 1 reports the flag states and the DMA read/write direction in the lower eight bits. The upper eight bits are identical for both formats. The flag states, the parity errors, the Odd Byte Register valid bit, and the Status Register format are all in the upper eight bits of the Status Register. See Table 8 for both Status Register formats.

#### **Configuration Registers**

The eight Configuration Register formats are shown in Table 9. Configuration Registers 0-3 contain the programmable flag offsets for the Almost Empty and Almost Full flags. These offsets are set to **0** when a hardware reset or a software reset all is applied. Note that Table 9 shows that Configuration Registers 0-3 are 10 bits wide to accommodate the 1024 locations in each FIFO memory of the IDT72520. Only 9 least significant bits are used for the 512 locations of the IDT72510; the most significant bit, bit 9, must be set to 0.

Configuration Register 4 is used to assign the internal flags to the external flag pins (FLGA-FLGD). Each external flag pin is assigned an internal flag based on the four bit codes shown in Table 10. The default condition for Configuration Register 4 is 6420H as shown in Table 7. The default flag assignments are: FLGD is assigned  $B \rightarrow A \overline{Full}$ , FLGC is assigned  $B \rightarrow A \overline{Empty}$ , FLGB is assigned A $\rightarrow$ B Full, FLGA is assigned A $\rightarrow$ B Empty.

STATUS REGISTER FORMAT 0

Configuration Register 5 is a general control register. The format of Configuration Register 5 is shown in Table 11. Bit 0 sets the Intel-style interface ( $\overline{R}B$ ,  $\overline{W}B$ ) or Motorola-style interface (DSB, R/WB) for Port B. Bit 1 changes the byte order for data coming through Port B. Bits 2 and 3 redefine Full and Empty Flags for reread/rewrite data protection.

Bits 4-9 control the DMA interface and are only applicable in peripheral interface mode. In processor interface mode, these bits are don't care states. Bits 4 and 5 set the polarity of the DMA control pins REQ and ACK, respectively. An internal clock controls all DMA operations. This internal clock is derived from the external clock (CLK). Bit 9 determines the internal clock frequency: the internal clock = CLK or the internal clock = CLK divided by 2. Bit 8 sets whether  $\overline{R}B$ ,  $\overline{W}B$ , and DSB are asserted for either one or two internal clocks. Bits 6 and 7 set the number of internal clocks between REQ assertion and ACK assertion. The timing can be from 2 to 5 cycles as shown in Figure 17.

Bit 10 controls Port B processor or peripheral interface mode. In processor mode, the Port B control pins ( $\overline{R}B$ ,  $\overline{W}B$ ,  $\overline{DS}B$ , R/WB) are inputs and the DMA controls are ignored. In peripheral mode, the Port B control pins are outputs and the DMA controls are active.

Bits 11 and 12 set the width expansion mode. For 18- to 9-bit configurations or 36- to 18-bit configurations, the BiFIFO should be set in stand-alone mode. For a 36- to 9-bit configuration, one BiFIFO must be in slave mode and the other BiFIFO must be in master mode. The master BiFIFO allows the first two bytes transferred across Port B to go to the slave BiFIFO, then the next two bytes go to the master BiFIFO.

Configuration Register 7 controls the parity functions of Port B as shown in Table 12. Either parity generation or parity

## STATUS REGISTER FORMAT 1

| Bit | Signal                     |   |

|-----|----------------------------|---|

| 0   |                            |   |

| 1   |                            | ļ |

| 2   |                            |   |

| 3   | Odd Byte Register          |   |

| 4   |                            |   |

| 5   |                            | ſ |

| 6   |                            | ľ |

| 7   |                            | ł |

| 8   | Valid Bit                  | ŀ |

| 9   | Write Parity Error         | ł |

| 10  | Read Parity Error          | ł |

| 11  | Status Register Format = 0 | ľ |

| 12  | A→B Full Flag              | ĺ |

| 13  | A→B Almost-Full Flag       | Ì |

| 14  | B→A Empty Flag             | ſ |

| 15  | B→A Almost-Empty Flag      | Ī |

|     | 2669 tbl 11                |   |

| Bit     | Signal                      |

|---------|-----------------------------|

| 0       | Reserved                    |

| 1       | Reserved                    |

| 2       | Reserved                    |

| 3       | DMA Direction               |

| 4       | A→B Empty Flag              |

| 5       | A→B Almost-Empty Flag       |

| 6       | $B \rightarrow A$ Full Flag |

| 7       | B→A Almost-Full Flag        |

| 8       | Valid Bit                   |

| 9       | Write Parity Error          |

| 10      | Read Parity Error           |

| 11      | Status Register Format = 1  |

| 12      | A→B Full Flag               |

| 13      | A→B Almost-Full Flag        |

| 14      | B→A Empty Flag              |

| 15      | B→A Almost-Empty Flag       |

| <u></u> | 2669 tbl 12                 |

Table 8. The Two Status Register Formats

## CONFIGURATION REGISTER FORMATS

|                | 15   |         |        |      |     | 10     | 9             |            |                 |            | 0              |

|----------------|------|---------|--------|------|-----|--------|---------------|------------|-----------------|------------|----------------|

| Config. Reg. 0 | X    | Х       | х      | Х    | Х   | Х      |               | A→B FIFO A | Almost-Empty F  | lag Offset |                |

|                | 15   |         |        |      |     | 10     | 9             |            |                 |            | 0              |

| Config. Reg. 1 | х    | х       | х      | х    | х   | х      |               | A→B FIFO   | Almost-Full Fla | ig Offset  |                |

|                | 15   | -       | -      |      |     | 10     | 9             |            |                 |            | 0              |

| Config. Reg. 2 | Х    | х       | х      | х    | Х   | х      |               | B→A FIFO A | Almost-Empty F  | lag Offset |                |

|                | 15   | -       | -      |      |     | 10     | 9             |            |                 |            | 0              |

| Config. Reg. 3 | Х    | х       | х      | х    | Х   | х      |               | B→A FIFO   | Almost-Full Fla | g Offset   |                |

|                | 15   |         |        | 12   | 11  |        | 8             | 7          | 4               | 3          | 0              |

| Config. Reg. 4 | Flag | D Pin . | Assign | ment | Fla | ag C P | in Assignment | Flag B Pin | Assignment      | Flag A F   | Pin Assignment |

|                | 15   |         |        |      |     |        |               |            |                 |            | 0              |

| Config. Reg. 5 |      |         |        |      |     |        | Genera        | l Control  |                 |            |                |

|                | 15   |         |        |      |     |        |               |            |                 |            | 0              |

| Config. Reg. 6 |      |         |        |      |     |        | Rese          | erved      |                 |            |                |

|                | 15   |         |        |      |     |        |               |            |                 |            | 0              |

| Config. Reg. 7 |      |         |        |      |     |        | Parity        | Control    |                 |            |                |

| NOTE:          |      |         |        |      |     |        |               |            |                 |            | 2669 tbl 13    |

1. Bit 9 of Configuration Registers 0-3 must be set to 0 on the IDT72510.

Table 9. The BiFIFO Configuration Register Formats

checking is enabled for data read and written through Port B. Bit8 controls parity checking and generation for  $B \rightarrow A$  write data. Bit9 controls parity checking and generation for  $A \rightarrow B$  read data. Bit 10 controls whether the parity is odd or even. Bit 11 is used to assign the internal parity checking error to the FLGA pin. When the parity error is assigned to FLGA, the Configuration Register 4 flag assignment for FLGA is ignored.

#### **Programmable Flags**

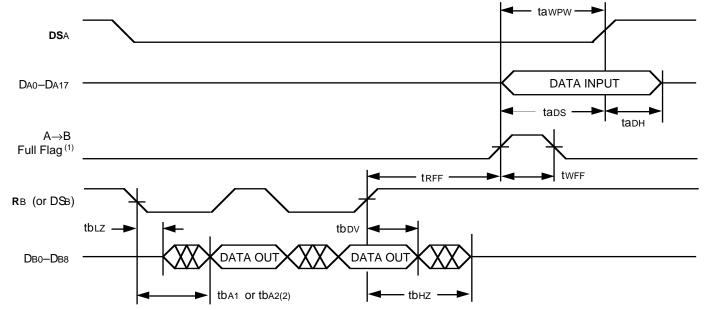

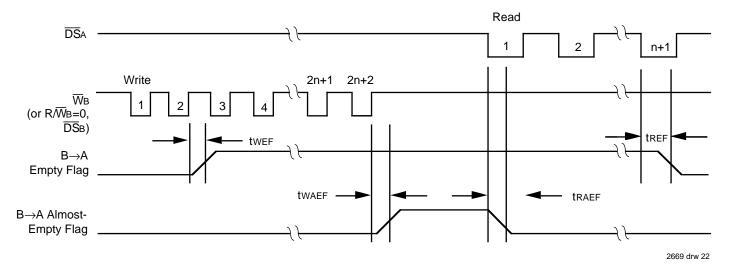

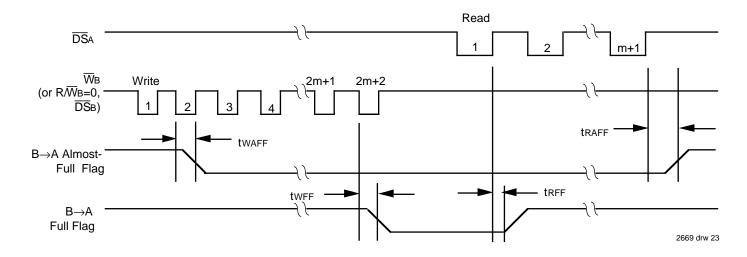

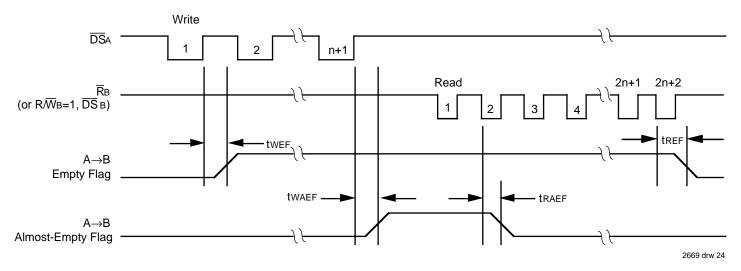

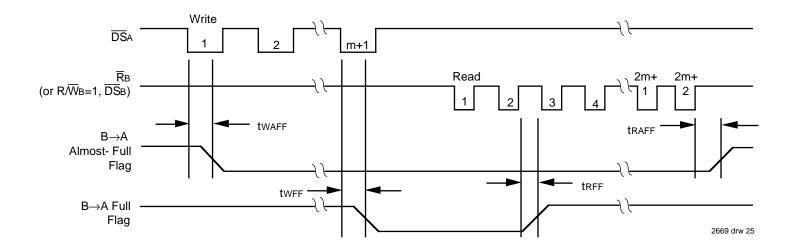

The IDT BiFIFO has eight internal flags; four of these flags have programmable offsets, the other four are empty or full. Associated with each FIFO memory array are four internal flags, Empty, Almost-Empty, Almost-Full and Full, for the total of eight internal flags. The Almost-Empty and Almost-Full offsets can be set to any depth through the Configuration Registers 0-3 (see Table 9). The offset (or depth) of FIFO RAM array is based on the unit of an 18-bit word. The flags are asserted at the depths shown in Table 13. After a hardware reset or a software reset all, the almost flag offsets are set to **0**. Even though the offsets are equivalent, the Empty and Almost-Empty flags have different timing which means that the flags are not coincident. Similarly, the Full and Almost-Full flags are not coincident because of timing.

These eight internal flags can be assigned to any of four external flag pins (FLGA-FLGD) through Configuration Register 4 (see Table 10). For the specific flag timings, see Figures 20-23.

The current state of all eight flags is available in the Status Register in Status Register format 1. In Status Register format 0, only four flags can be found in the Status Register (see Table 8).

## **EXTERNAL FLAG ASSIGNMENT CODES**

| Assignment<br>Code | Internal Flag Assigned to Flag Pin |

|--------------------|------------------------------------|

| 0000               | A→B Empty                          |

| 0001               | A→B Almost-Empty                   |

| 0010               | A→B <del>Full</del>                |

| 0011               | A→B Almost-Full                    |

| 0100               | B→A Empty                          |

| 0101               | B→A Almost-Empty                   |

| 0110               | B→A Full                           |

| 0111               | B→A Almost-Full                    |

| 1000               | A→B Empty                          |

| 1001               | A→B Almost-Empty                   |

| 1010               | A→B Full                           |

| 1011               | A→B Almost-Full                    |

| 1100               | B→A Empty                          |

| 1101               | B→A Almost-Empty                   |

| 1110               | B→A Full                           |

| 1111               | B→A Almost-Full                    |

|                    | 2669 tbl 14                        |

Table 10. Configuration Register 4 Internal Flag Assignments to

External Flag Pins.

#### **Port B Interface**

Port B also has parity, reread/rewrite and DMA functions. Port B can be configured to interface to either Intel-style ( $\overline{R}B$ ,  $\overline{W}B$ ) or Motorola-style ( $\overline{DS}B$ ,  $R/\overline{W}B$ ) devices in Configuration Register 5 (see Table 11). Port B can also be configured to talk to a processor or a peripheral device through Configuration Register 5. In processor interface mode, the Port B interface controls are inputs. In peripheral interface mode, the Port B interface to a software Reset All command, Port B defaults to an Intel-style processor interface; the controls are inputs.

Two 9-bit words are put together to create each 18-bit word stored in the internal FIFOs. The first 9-bit word written to Port B goes into the Odd Byte Register shown in the detailed block diagram. The Odd Byte Register valid bit (Bit 8) in the Status Register is 1 when this first 9-bit word is written. The data bits from Port B (DB0-DB7) are also stored in the lower 8 bits of the Status Register when Status Register format 0 is selected (see Table 8). The second write on Port B moves the 9-bits from Port B and the 9-bits in the Odd Byte Register into the B $\rightarrow$ A FIFO and advances the B $\rightarrow$ A Write Pointer. The Status Register valid bit is set to **0** after the second write.

When Port B reads data from the A $\rightarrow$ B FIFO, two buffers choose which 9 of the 18 memory bits are sent to Port B. These buffers alternate between the upper 9 bits (DA8-DA15, DA17) and the lower 9 bits (DA0-DA7, DA16). The A $\rightarrow$ B Read Pointer is advanced after every two Port B reads.

The BiFIFO can be set to order the 9-bit data so the first 9-

| Bit   | Function                                                                  |    |                                                                                                      |

|-------|---------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------|

| 0     | Select Port B Interface                                                   | 0  | Pins are $\overline{R}B$ and $\overline{W}B$ (Intel-style interface)                                 |

|       | $\overline{R}B$ & $\overline{W}B$ or $\overline{DS}B$ & $R/\overline{W}B$ | 1  | Pins are $\overline{\text{DS}}\text{B}$ and $R/\overline{W}\text{B}$ (Motorola-style interface)      |

| 1     | Byte Order of 18-bit Word                                                 | 0  | Lower byte DA7-DA0 and parity DA16 are read or written first on Port B                               |

|       |                                                                           | 1  | Upper byte DA15-DA8 and parity DA17 are read or written first on Port B                              |

| 2     | Full Flag Definition                                                      | 0  | Full Flag is asserted when write pointer meets read pointer                                          |

|       |                                                                           | 1  | Full Flag is asserted when write pointer meets reread pointer                                        |

| 3     | Empty Flag Definition                                                     | 0  | Empty Flag is asserted when read pointer meets write pointer                                         |

|       |                                                                           | 1  | Empty Flag is asserted when read pointer meets rewrite pointer                                       |

| 4     | REQ Pin Polarity                                                          | 0  | REQ pin active HIGH                                                                                  |

|       |                                                                           | 1  | REQ pin active LOW                                                                                   |

| 5     | ACK Pin Polarity                                                          | 0  | ACK pin active LOW                                                                                   |

|       |                                                                           | 1  | ACK pin active HIGH                                                                                  |

|       |                                                                           | 00 | 2 internal clocks between REQ assertion and ACK assertion                                            |

| 7-6   | REQ / ACK Timing                                                          | 01 | 3 internal clocks between REQ assertion and ACK assertion                                            |

|       |                                                                           | 10 | 4 internal clocks between REQ assertion and ACK assertion                                            |

|       |                                                                           | 11 | 5 internal clocks between REQ assertion and ACK assertion                                            |

| 8     | Port B Read and Write                                                     | 0  | $\overline{R}_{B}$ , $\overline{W}_{B}$ , and $\overline{DS}_{B}$ are asserted for 1 internal clock  |

|       | Timing Control for Peripheral Mode                                        | 1  | $\overline{R}_{B}$ , $\overline{W}_{B}$ , and $\overline{DS}_{B}$ are asserted for 2 internal clocks |

| 9     | Internal Clock                                                            | 0  | internal clock = CLK                                                                                 |

|       | Frequency Control                                                         | 1  | internal clock = CLK divided by 2                                                                    |

| 10    | Port B Interface                                                          | 0  | Processor interface mode (Port B controls are inputs)                                                |

|       | Mode Control                                                              | 1  | Peripheral interface mode (Port B controls are outputs)                                              |

|       |                                                                           | 00 | Stand-alone mode (18- to 9-bits, 36- to 18-bits)                                                     |

| 12-11 | Width Expansion                                                           | 01 | Reserved                                                                                             |

|       | Mode Control                                                              | 10 | Slave width expansion mode (36- to 9-bits)                                                           |

|       |                                                                           | 11 | Master width expansion mode (36- to 9-bits)                                                          |

| 13    | Unused                                                                    |    | -1                                                                                                   |

| 14    | Unused                                                                    |    |                                                                                                      |

| 15    | Unused                                                                    |    |                                                                                                      |

## **CONFIGURATION REGISTER 5 FORMAT**

Table 11. BiFIFO Configuration Register 5 Format

## **CONFIGURATION REGISTER 7 FORMAT**

| BIT   | FUNCTION               | ] |                                              |

|-------|------------------------|---|----------------------------------------------|

| 0-7   | Unused                 |   |                                              |

| 8     | Parity Input Control   | 0 | Disable Parity Generate, Enable Parity Check |

|       | B→A                    | 1 | Enable Parity Generate, Disable Parity Check |

| 9     | Parity Output Control  | 0 | Disable Parity Generate, Enable Parity Check |

|       | A→B                    | 1 | Enable Parity Generate, Disable Parity Check |

| 10    | Parity Odd/Even        | 0 | Odd                                          |

|       | Control                | 1 | Even                                         |

| 11    | Assign Parity Error to | 0 | No Parity Error Output                       |

|       | Flag A Pin             | 1 | Parity Error on Flag A Pin                   |

| 12-15 | Unused                 |   | 2669 tbl 16                                  |

Table 12. BiFIFO Configuration Register 7 Format

bits go to the LSB (DA0-DA7, DA16) or the MSB (DA8-DA15, DA17) of Port A. This data ordering is controlled by bit 1 of Configuration Register 5 (see Table 11).

#### **DMA Control Interface**

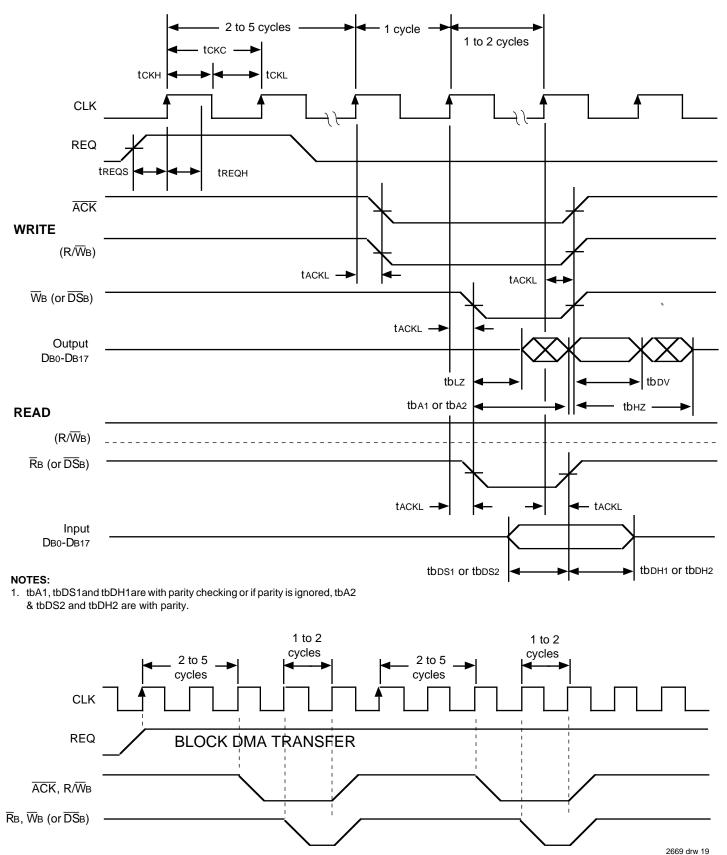

The BiFIFO has DMA control to simplify data transfers with peripherals. For the BiFIFO DMA controls (REQ, ACK and CLK) to operate, the BiFIFO must be in peripheral interface mode (Configuration Register 5, Table 11).

DMA timing is controlled by the external clock input, CLK. An internal clock is derived from this CLK signal to generate the  $\overline{R}B$ ,  $\overline{W}B$ ,  $\overline{DS}B$  and  $R/\overline{W}B$  output signals. The internal clock also determines the timing between REQ assertion and ACK assertion. Bit 9 of Configuration Register 5 determines whether the internal clock is the same as CLK or whether the internal clock is CLK divided by 2.

Bit 8 of Configuration Register 5 sets whether  $\overline{R}B$ ,  $\overline{W}B$  and  $\overline{DS}B$  are asserted for 1 or 2 internal clocks. Bits 6 and 7 of Configuration Register 5 set the number of clocks between REQ assertion and ACK assertion. The clocks between REQ assertion and ACK assertion can be 2, 3, 4 or 5.

Bits 4 and 5 of Configuration Register 5 set the polarity of the REQ and ACK pins, respectively.

A DMA transfer command sets the Port B read/write direction (see Table 5). The timing diagram for DMA transfers is shown in Figure 17. The basic DMA transfer starts with REQ assertion. After 2 to 5 internal clocks, ACK is asserted by the BiFIFO. ACK will not be asserted if a read is attempted on an Empty A $\rightarrow$ B FIFO or if a write is attempted on a Full B $\rightarrow$ A FIFO. If the BiFIFO is in Motorola-style interface mode, R/WB is set at the same time that ACK is asserted. One internal clock later, DSB is asserted. If the BiFIFO is in Intel-style interface mode, either RB or WB is asserted one internal clock after ACK assertion. These read/write controls stay asserted for 1 or 2 internal clocks, then ACK, DSB, RB and WB are made inactive. This completes the transfer of one 9-bit word.

On the next rising edge of CLK, REQ is sampled. If REQ is still asserted, another DMA transfer starts with the assertion of ACK. Data transfers will continue as long as REQ is asserted.

#### **Parity Checking and Generation**

Parity generation or checking is performed by the BiFIFO on data passing through Port B. Parity can either be odd or even as determined by Bit 10 of Configuration Register 7.

When parity checking is enabled, DB8 is treated as a data bit. DB8 data will be passed to DA16 (bypass operation) or stored in the RAM array (FIFO operation) for B->A operation; similarly, DA16 or parity bits from the RAM array will be passed to DB8 for A->B operations. A->B read parity errors and B->A write parity errors are shown in Bit 9 and 10 in the Status Register. If an external parity error signal is required, a logical OR of the

| Number of Words in FIFO |             |              |                   |                  |              |

|-------------------------|-------------|--------------|-------------------|------------------|--------------|

| From                    | То          | Empty Flag   | Almost-Empty Flag | Almost-Full Flag | Full Flag    |

| 0                       | 0           | Asserted     | Asserted          | Not Asserted     | Not Asserted |

| 1                       | n           | Not Asserted | Asserted          | Not Asserted     | Not Asserted |

| n + 1                   | D - (m + 1) | Not Asserted | Not Asserted      | Not Asserted     | Not Asserted |

| D - m                   | D - 1       | Not Asserted | Not Asserted      | Asserted         | Not Asserted |

| D                       | D           | Not Asserted | Not Asserted      | Asserted         | Asserted     |

## **INTERNAL FLAG TRUTH TABLE**

NOTE:

1. BiFIFO flags can be assigned to external flag pins to be observed. D = FIFO depth (IDT72510 = 512, IDT72520 = 1024),

n = Almost-Empty flag offset, m = Almost-Full flag offset.

Table 13. Internal Flag Truth Table.

two parity error bits is brought out to FLGA pin by setting Bit 11 of Configuration Register 7.

Parity generation creates the ninth bit. This ninth bit is placed on DB8 for A->B read operation, and on DA16 or RAM array for B->A write operation.

It is recommended that if the parity pins (DB8, DA16, and DA17) are not used, they should be pulled down with 10K resistors for noise immunity.

## Intelligent Reread/Rewrite

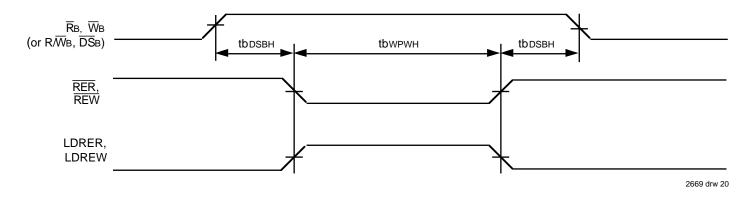

Intelligent reread/rewrite is a method the BiFIFO uses to help assure data integrity. Port B of the BiFIFO has two extra pointers, the Reread Pointer and the Rewrite Pointer. The Reread Pointer is associated with the A->B FIFO Read Pointer, while the Rewrite Pointer is associated with the B->A FIFO Write Pointer. The Reread Pointer holds the start address of a data block in the A->B FIFO RAM, and the Read Pointer is the current address of the same FIFO RAM array. By loading the Read Pointer with the value held in the Reread Pointer (RER asserted), reads will start over at the beginning of the data block. In order to mark the beginning of a data block, the Reread Pointer should be loaded with the Read Pointer value (LDRER asserted) before the first read is performed on this data block. Figure 6 shows a Reread operation.

Similarly, the Rewrite Pointer holds the start address of a data block in the B->A FIFO RAM, while the Write Pointer is the current address within the RAM array. The operation of the REW and LDREW is identical to the RER and LDRER discussed above. Figure 7 shows a Rewrite operation.

For the reread data protection, Bit 2 of Configuration Register 5 can be set to 1 to prevent the data block form being overwritten. In this way, the assertion of A->B full flag will occur when the write pointer meets the reread pointer instead of the read pointer as in the normal definition. For the rewrite data protection, Bit 3 of Configuration Register 5 can be set to 1 to prevent the data block from being read. In this case, the assertion of B->A empty flag will occur when the read pointer.

In conclusion, Bit 2 and 3 of Configuration Register 5 are used to redefine Full & Empty flags for data block partition. Although it can serve the purpose of data protection, the setting of these 2 bits is independent of the functions caused by RER/REW, or LDRER/LDREW assertions.

**REWRITE OPERATIONS** (3,4)

## **REREAD OPERATIONS**<sup>(1,2)</sup>

Reread Read Pointer Pointer Reread function Write Write Pointer  $B \rightarrow A$ A→B Pointer **FIFC FIFO** Load Reread function Load Rewrite function Rewrite Read Pointer Pointer Rewrite function 2669 drw 08 NOTES: 2669 drw 09 NOTES: 1. If bit 2 is set to 1, 1. If bit 3 is set to 1, Empty flag asserted if Read = Write Empty flag asserted if Read = Rewrite Full flag asserted if Reread + FIFO size = Write Full flag asserted if Read + FIFO size = Write 2. If bit 2 is set to 0. 2. If bit 3 is set to 0, Empty flag asserted if Read = Write Empty flag asserted if Read = Write Full flag asserted if Read + FIFO size = Write Full flag asserted if Read + FIFO size = Write Figure 6. BiFIFO Reread Operations Figure 7. BiFIFO Rewrite Operations

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol | Rating                                           | Commercial   | Unit |

|--------|--------------------------------------------------|--------------|------|

| VTERM  | Terminal<br>Voltage with<br>Respect to<br>Ground | -0.5 to +7.0 | V    |

| Та     | Operating<br>Temperature                         | 0 to +70     | °C   |

| TBIAS  | Temperature<br>Under Bias                        | -55 to +125  | °C   |

| Tstg   | Storage<br>Temperature                           | -55 to +125  | °C   |

| Ιουτ   | DC Output<br>Current                             | 50           | mA   |

#### NOTE:

2669 tbl 18 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# DC ELECTRICAL CHARACTERISTICS

(Commercial: Vcc =  $5V \pm 10\%$ , TA =  $0^{\circ}C$  to + $70^{\circ}C$ )

## **RECOMMENDED DC OPERATING** CONDITIONS

| Symbol             | Parameter             | Min. | Тур. | Max. | Unit        |

|--------------------|-----------------------|------|------|------|-------------|

| Vcc                | Supply Voltage        | 4.5  | 5.0  | 5.5  | V           |

| GND                | Supply Voltage        | 0    | 0    | 0    | V           |

| Viн                | Input HIGH<br>Voltage | 2.0  | —    | _    | V           |

| VIL <sup>(1)</sup> | Input LOW Voltage     | _    | _    | 0.8  | V           |

| NOTE:              |                       |      |      |      | 2669 tbl 19 |

1. 1.5V undershoots are allowed for 10ns once per cycle.

|                     |                                                                                          | IDT72510L<br>IDT72520L<br>Commercial<br>tA = 25, 35, 50 ns |      |      |      |  |  |

|---------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------|------|------|------|--|--|

| Symbol              | Parameter                                                                                | Min.                                                       | Тур. | Max. | Unit |  |  |

| IL <sup>(1)</sup>   | Input Leakage Current (Any Input)                                                        | -1                                                         | —    | 1    | μA   |  |  |

| IOL <sup>(2)</sup>  | Output Leakage Current                                                                   | -10                                                        | —    | 10   | μA   |  |  |

| Vон                 | Output Logic "1" Voltage IOUT = -1mA                                                     | 2.4                                                        | —    |      | V    |  |  |

| Vol                 | Output Logic "0" Voltage IOUT = 4mA                                                      | _                                                          | —    | 0.4  | V    |  |  |

| ICC1 <sup>(3)</sup> | Average Vcc Power Supply Current                                                         | _                                                          | 150  | 220  | mA   |  |  |

| ICC2 <sup>(3)</sup> | Average Standby Current ( $\overline{R}_B = \overline{W}_B = \overline{DS}_A = V_{IH}$ ) | _                                                          | 16   | 30   | mA   |  |  |

#### NOTES:

1. Measurements with  $0.4V \le VIN \le VCC$ , DSA = DSB  $\ge VIH$ .

2. Measurements with  $0.4V \le VOUT \le VCC$ , DSA = DSB  $\ge$  VIH.

3. Measurements are made with outputs open. Tested at f = 20 MHz.

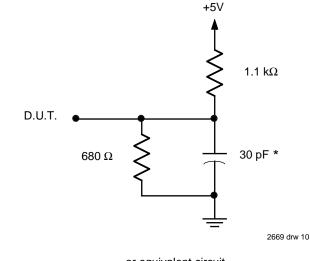

## **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 3ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure 8 |

|                               | 2669 tbl 21  |

## CAPACITANCE (TA = +25°C, f = 1.0MHz)

| Symbol                | Parameter          | Conditions | Max. | Unit        |

|-----------------------|--------------------|------------|------|-------------|

| CIN <sup>(2)</sup>    | Input Capacitance  | VIN = 0V   | 8    | рF          |

| Cout <sup>(1,2)</sup> | Output Capacitance | Vout = 0V  | 12   | pF          |

| NOTES:                |                    | -          | 2    | 2669 tbl 22 |

1. With output deselected.

2. Characterized values, not currently tested.

or equivalent circuit Figure 8. Output Load

\* Includes jig and scope capacitances

# AC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5V $\pm$ 10%, TA = 0°C to +70°C)

|                     |                                                         | Commercial |        |       |             |       |        |      |                |

|---------------------|---------------------------------------------------------|------------|--------|-------|-------------|-------|--------|------|----------------|

|                     |                                                         | IDT72      | 510L25 | IDT72 | IDT72510L35 |       | 510L50 |      |                |

|                     |                                                         | IDT72      | 520L25 | IDT72 | 520L35      | IDT72 | 520L50 |      | Timing         |

| Symbol              | Parameter                                               | Min.       | Max.   | Min.  | Max.        | Min.  | Max.   | Unit | Figure         |

| RESET T             | MING (Port A and Port B)                                |            | -      |       |             | -     | -      | _    |                |

| tRSC                | Reset cycle time                                        | 35         |        | 45    |             | 65    | _      | ns   | 9              |

| tRS                 | Reset pulse width                                       | 25         |        | 35    |             | 50    |        | ns   | 9              |

| tRSS                | Reset set-up time                                       | 25         |        | 35    |             | 50    |        | ns   | 9              |

| trsr                | Reset recovery time                                     | 10         |        | 10    |             | 15    |        | ns   | 9              |

| tRSF                | Flag reset pulse width                                  | _          | 35     | —     | 45          | —     | 65     | ns   | 9              |

| PORT A              | ſIMING                                                  |            | -      |       | -           | -     | -      |      |                |

| taA                 | Port A access time                                      |            | 25     | _     | 35          | —     | 50     | ns   | 12, 14, 15     |

| ta∟z                | Read or write pulse<br>LOW to data bus at<br>Low-Z      | 5          | _      | 5     |             | 5     | _      | ns   | 12, 15, 16     |

| taнz                | Read or write pulse<br>HIGH to data bus at<br>High-Z    | _          | 15     | —     | 20          | —     | 30     | ns   | 12, 14, 15, 16 |

| tadv                | Data valid from read<br>pulse HIGH                      | 5          | _      | 5     |             | 5     | —      | ns   | 12, 14, 16     |

| tarc                | Read cycle time                                         | 35         | _      | 45    | —           | 65    | —      | ns   | 12             |

| tarpw               | Read pulse width                                        | 25         | _      | 35    | _           | 50    | _      | ns   | 12, 14, 15     |

| tarr                | Read recovery time                                      | 10         | _      | 10    | —           | 15    | —      | ns   | 12             |

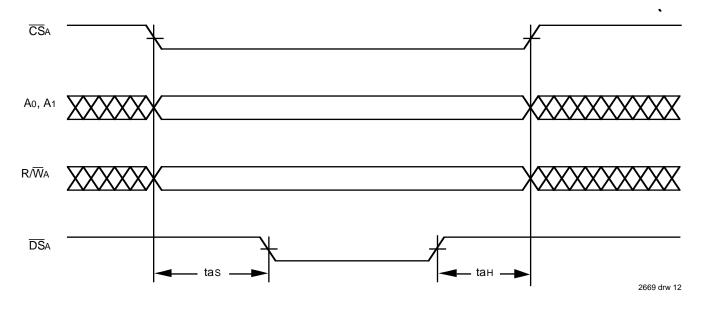

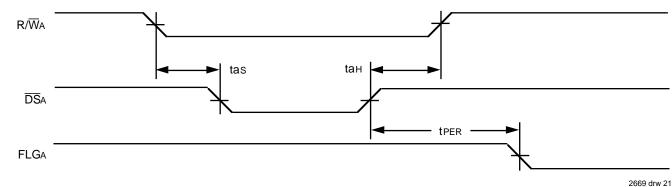

| tas                 | CSA, A0, A1, R/WA set-<br>up time                       | 5          | _      | 5     | _           | 5     | _      | ns   | 10, 12, 16     |

| taн                 | $\overline{CS}A$ , A0, A1, R/ $\overline{W}A$ hold time | 5          | _      | 5     | _           | 5     | _      | ns   | 10, 12         |

| taos                | Data set-up time                                        | 15         |        | 18    |             | 30    | _      | ns   | 11, 12, 14, 15 |

| tарн <sup>(1)</sup> | Data hold time                                          | 0          | _      | 0     |             | 5     | _      | ns   | 11, 12, 14, 15 |

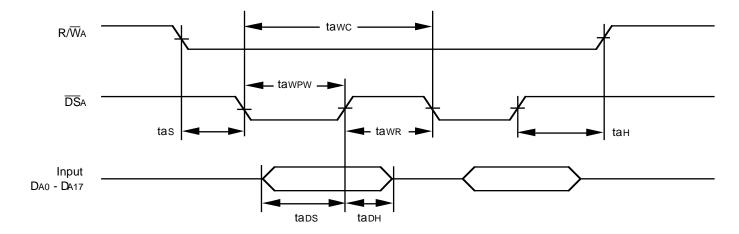

| tawc                | Write cycle time                                        | 35         |        | 45    |             | 65    | _      | ns   | 12             |

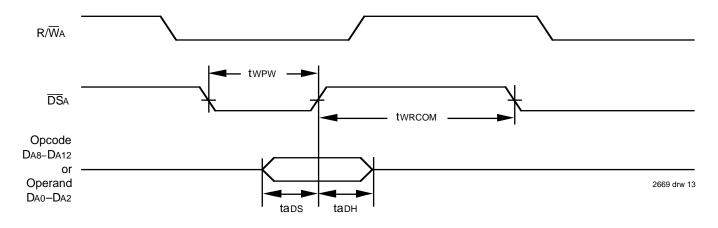

| tawpw               | Write pulse width                                       | 25         |        | 35    |             | 50    | _      | ns   | 11, 12, 14     |

| tawr                | Write recovery time                                     | 10         | _      | 10    |             | 15    | _      | ns   | 12             |

| tawrcom             | Write recovery time after a command                     | 25         |        | 35    |             | 50    |        | ns   | 11             |

#### NOTE:

2669 tbl 23

1. The minimum data hold time is 5ns (10ns for the 80ns speed grade) when writing to the Command or Configuration registers.

# AC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5V $\pm$ 10%, TA = 0°C to +70°C)

|                |                                                      | IDT72  | 510L25 | IDT72 | 510L35 | IDT72 | 510L50 |      |                |

|----------------|------------------------------------------------------|--------|--------|-------|--------|-------|--------|------|----------------|

|                |                                                      | IDT72  | 520L25 | IDT72 | 520L35 | IDT72 | 520L50 |      | Timing         |

| Symbol         | Parameter                                            | Min.   | Max.   | Min.  | Max.   | Min.  | Max.   | Unit | Figure         |

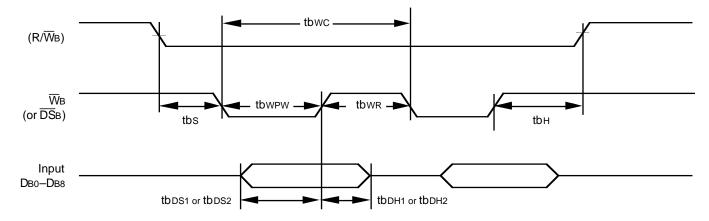

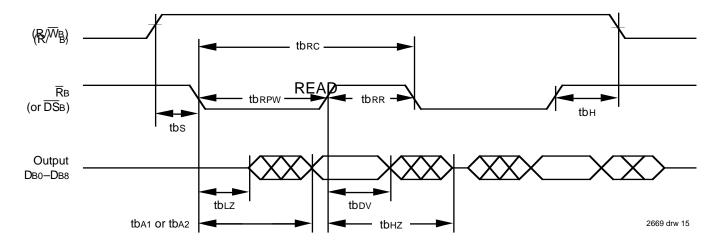

| PORT B         | PROCESSOR INTERFACE                                  | TIMING | -      |       | -      | -     | -      | -    | -              |

| tbA1           | Port B access time with no parity                    | —      | 25     |       | 35     | —     | 50     | ns   | 13, 14, 15     |

| tbA2           | Port B access time with parity                       | _      | 30     | —     | 42     | -     | 60     | ns   | 13, 14, 15     |

| tbLZ           | Read or write pulse<br>LOW to data bus at<br>Low-Z   | 5      | _      | 5     | _      | 5     | _      | ns   | 13, 14, 15     |

| tbнz           | Read or write pulse<br>HIGH to data bus at<br>High-Z | _      | 15     | —     | 20     | _     | 30     | ns   | 13, 14, 15     |

| tbDV           | Data valid from read<br>pulse HIGH                   | 5      | _      | 5     | _      | 5     | _      | ns   | 13, 14, 15, 16 |

| tbrc           | Read cycle time                                      | 35     | _      | 45    |        | 65    |        | ns   | 13             |

| tbrpw          | Read pulse width                                     | 25     |        | 35    | _      | 50    |        | ns   | 13             |

| tbrr           | Read recovery time                                   | 10     | _      | 10    | _      | 15    |        | ns   | 13             |

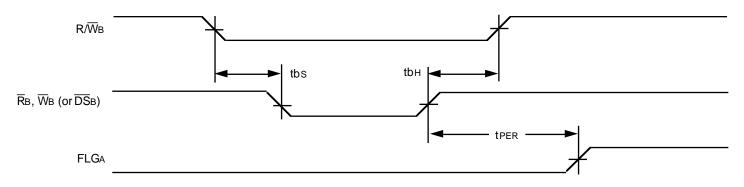

| tbs            | R/Wв set-up time                                     | 5      | _      | 5     | _      | 5     | _      | ns   | 13             |

| tbн            | R/Wв hold time                                       | 5      |        | 5     |        | 5     | _      | ns   | 13             |

| tbDS1          | Data set-up time with no parity                      | 15     | _      | 18    | _      | 30    |        | ns   | 13, 14, 15     |

| tbdh1          | Data hold time with no parity                        | 0      |        | 0     |        | 5     |        | ns   | 13, 14, 15     |

| tbDS2          | Data set-up time with parity                         | 18     | _      | 22    |        | 35    | _      | ns   | 13, 14, 15     |

| tbDH2          | Data hold time with parity                           | 0      |        | 0     | _      | 5     | —      | ns   | 13, 14, 15     |

| tbwc           | Write cycle time                                     | 35     |        | 45    |        | 65    |        | ns   | 13             |

| tbwpw          | Write pulse width                                    | 25     | —      | 35    | _      | 50    | —      | ns   | 13, 15         |

| tbwR           | Write recovery time                                  | 10     | —      | 10    | —      | 15    | _      | ns   | 13             |

| PORT B         | PERIPHERAL INTERFACE                                 | TIMING |        |       |        |       |        | -    |                |

| tbA1           | Port B access time with no parity                    |        | 25     | —     | 40     | —     | 55     | ns   | 17             |

| tbA2           | Port B access time with parity                       |        | 30     | —     | 42     | —     | 60     | ns   | 17             |

| tbcĸc          | Clock cycle time                                     | 15     |        | 20    |        | 25    |        | ns   | 17             |

| tbcкн          | Clock pulse HIGH time                                | 6      | _      | 6     |        | 10    |        | ns   | 17             |

| tbcĸ∟          | Clock pulse LOW time                                 | 6      |        | 6     |        | 10    |        | ns   | 17             |