# HIGH-SPEED 8K x 16 SEQUENTIAL ACCESS RANDOM ACCESS MEMORY (SARAM™)

### FEATURES:

- 8K x 16 Sequential Access Random Access Memory (SARAM<sup>™</sup>)

- Sequential Access from one port and standard Random Access from the other port

- Separate upper-byte and lower-byte control of the Random Access Port

- High-speed operation

- 20ns tAA for random access port

- 20ns tCD for sequential port

- 25ns clock cycle time

- Architecture based on Dual-Port RAM cells

- Electrostatic discharge ≥ 2001V, Class II

- Compatible with Intel BMIC and 82430 PCI Set

- Width and Depth Expandable

- Sequential side

- Address based flags for buffer control

- Pointer logic supports two internal buffers

- Battery backup operation—2V data retention

- TTL-compatible, single 5V (±10%) power supply

- Available in 80-pin TQFP and 84-pin PGA

- Military product compliant to MIL-STD-883.

- Industrial temperature range (-40°C to +85°C) is available, tested to military electrical specifications.

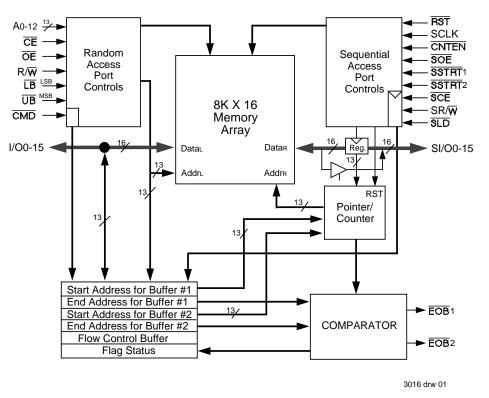

# FUNCTIONAL BLOCK DIAGRAM

## **DESCRIPTION:**

The IDT70825 is a high-speed 8K x 16-bit Sequential Access Random Access Memory (SARAM). The SARAM offers a single-chip solution to buffer data sequentially on one port, and be accessed randomly (asynchronously) through the other port. The device has a Dual-Port RAM based architecture with a standard SRAM interface for the random (asynchronous) access port, and a clocked interface with counter sequencing for the sequential (synchronous) access port.

Fabricated using CMOS high-performance technology, this memory device typically operates on less than 900mW of power at maximum high-speed clock-to-data and Random Access. An automatic power down feature, controlled by  $\overline{CE}$ , permits the on-chip circuitry of each port to enter a very low standby power mode.

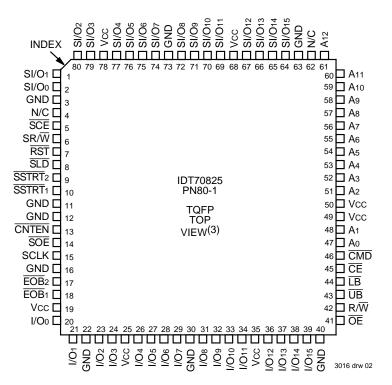

The IDT70825 is packaged in a 80-pin Thin Plastic Quad Flatpack (TQFP) or 84-pin Ceramic Pin Grid Array (PGA). Military grade product is manufactured in compliance with the latest revision of MIL-STD-883, Class B, making it ideally suited to military temperature applications demanding the highest level of performance and reliability.

The IDT logo is a registered trademark and SARAM is a trademark of Integrated Device Technology, Inc.

### MILITARY AND COMMERCIAL TEMPERATURE RANGES

### .

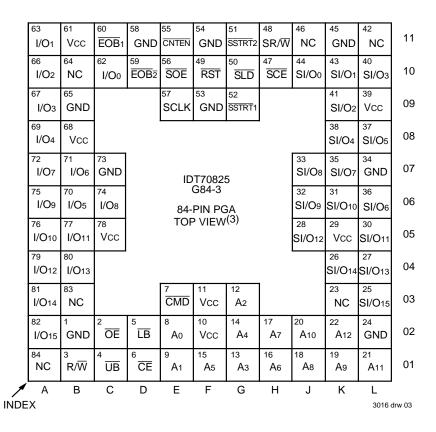

### PIN CONFIGURATIONS<sup>(1,2)</sup>

#### NOTES:

1. All Vcc pins must be connected to power supply.

2. All GND pins must be connected to ground supply.

3. This text does not indicate orientation of the actual part-marking.

### PIN DESCRIPTIONS: RANDOM ACCESS PORT

| SYMBOL     | NAME                              | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-----------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A12     | Address Lines                     | I                  | Address inputs to access the 8192-word (16 bit) memory array.                                                                                                                                                                                                                                                                                                                    |

| I/00-I/015 | Inputs/Outputs                    | Ι                  | Random access data inputs/outputs for 16-bit wide data.                                                                                                                                                                                                                                                                                                                          |

| CE         | Chip Enable                       | I                  | When $\overline{CE}$ is LOW, the random access port is enabled. When $\overline{CE}$ is HIGH, the random access port is disabled into power-down mode and the I/O outputs are in the high-impedance state. All data is retained during $\overline{CE}$ = VIH, unless it is altered by the sequential port. $\overline{CE}$ and $\overline{CMD}$ may not be LOW at the same time. |

| CMD        | Control Register<br>Enable        | I                  | When $\overline{\text{CMD}}$ is LOW, Address lines A0-A2, R/ $\overline{\text{W}}$ , and inputs/outputs I/O0-I/O11, are used to access the control register, the flag register, and the start and end of buffer registers. $\overline{\text{CMD}}$ and $\overline{\text{CE}}$ may not be LOW at the same time.                                                                   |

| R/W        | Read/Write Enable                 | I                  | If $\overline{CE}$ is LOW and $\overline{CMD}$ is HIGH, data is written into the array when R/ $\overline{W}$ is LOW and read out of the array when R/ $\overline{W}$ is HIGH. If $\overline{CE}$ is HIGH and $\overline{CMD}$ is LOW, R/ $\overline{W}$ is used to access the buffer command registers. $\overline{CE}$ and $\overline{CMD}$ may not be LOW at the same time.   |

| ŌĒ         | Output Enable                     | I                  | When $\overline{OE}$ is LOW and R/ $\overline{W}$ is HIGH, I/O0-I/O15 outputs are enabled. When $\overline{OE}$ is HIGH, the I/O outputs are in the high-impedance state.                                                                                                                                                                                                        |

| LB,UB      | Lower Byte, Upper<br>Byte Enables | I                  | When $\overline{LB}$ is LOW, I/O0-I/O7 are accessible for read and write operations. When $\overline{LB}$ is HIGH, I/O0-I/O7 are tri-stated and blocked during read and write operations. UB controls access for I/O8-I/O15 in the same manner and is asynchronous from $\overline{LB}$ .                                                                                        |

| VCC        | Power Supply                      |                    | Seven +5V power supply pins. All Vcc pins must be connected to the same +5V VCC supply.                                                                                                                                                                                                                                                                                          |

| GND        | Ground                            |                    | Ten Ground pins. All Ground pins must be connected to the same Ground supply.                                                                                                                                                                                                                                                                                                    |

### **PIN DESCRIPTIONS: SEQUENTIAL ACCESS PORT**

| SYMBOL            | NAME                              | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|-----------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SI/O0-15          | Inputs                            | I/O                | Sequential data inputs/outputs for 16-bit wide data.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SCLK              | Clock                             | I                  | SI/O0-SI/O15, $\overline{SCE}$ , SR/ $\overline{W}$ , and $\overline{SLD}$ are registered on the LOW-to-HIGH transition of SCLK.<br>Also, the sequential access port address pointer increments by 1 on each LOW-to-HIGH transition of SCLK when $\overline{CNTEN}$ is LOW.                                                                                                                                                                                                        |

| SCE               | Chip Enable                       | Ι                  | When $\overline{\text{SCE}}$ is LOW, the sequential access port is enabled on the LOW-to-HIGH transition of SCLK. When $\overline{\text{SCE}}$ is HIGH, the sequential access port is disabled into powered-down mode on the LOW-to-HIGH transition of SCLK, and the SI/O outputs are in the high-impedance state. All data is retained, unless altered by the random access port.                                                                                                 |

| CNTEN             | Counter Enable                    | I                  | When $\overline{\text{CNTEN}}$ is LOW, the address pointer increments on the LOW-to-HIGH transition of SCLK. This function is independent of $\overline{\text{SCE}}$ .                                                                                                                                                                                                                                                                                                             |

| SR/W              | Read/Write Enable                 | Ι                  | When SR/ $\overline{W}$ and $\overline{SCE}$ are LOW, a write cycle is initiated on the LOW-to-HIGH transition of SCLK. When SR/ $\overline{W}$ is HIGH, and $\overline{SCE}$ and $\overline{SOE}$ are LOW, a read cycle is initiated on the LOW-to-HIGH transition of SCLK. Termination of a Write cycle is done on the Low-to-High transistion of SCLK if SR/ $\overline{W}$ or $\overline{SCE}$ is High.                                                                        |

| SLD               | Address Pointer<br>Load Control   | Ι                  | When SLD is sampled LOW, there is an internal delay of one cycle before the address pointer changes. When SLD is LOW, data on the inputs SI/O0-SI/O11 is loaded into a data-in register on the LOW-to-HIGH transition of SCLK. On the cycle following SLD, the address pointer changes to the address location contained in the data-in register. SSTRT1 and SSTRT2 may not be LOW while SLD is LOW or during the cycle following SLD.                                             |

| SSTRT1,<br>SSTRT2 | Load Start of<br>Address Register | Ι                  | When SSTRT1 or SSTRT2 is LOW, the start of address register #1 or #2 is loaded into the address pointer on the LOW-to-HIGH transition of SCLK. The start addresses are stored in internal registers. SSTRT1 and SSTRT2 may not be LOW while SLD is LOW or during the cycle following SLD.                                                                                                                                                                                          |

| EOB1,<br>EOB2     | End of Buffer Flag                | 0                  | $\overline{\text{EOB}}$ 1 or $\overline{\text{EOB}}$ 2 is output LOW when the address pointer is incremented to match the address stored in the end of buffer registers. The flags can be cleared by either asserting $\overline{\text{RST}}$ LOW or by writing zero into bit 0 and/or bit 1 of the control register at address 101. $\overline{\text{EOB}}$ 1 and $\overline{\text{EOB}}$ 2 are dependent on separate internal registers, and therefore separate match addresses. |

| SOE               | Output Enable                     | I                  | $\overline{\text{SOE}}$ controls the data outputs and is independent of SCLK. When $\overline{\text{SOE}}$ is LOW, output buffers and the sequentially addressed data is output. When $\overline{\text{SOE}}$ is HIGH, the SI/O output bus is in the high-impedance state. $\overline{\text{SOE}}$ is asynchronous to SCLK.                                                                                                                                                        |

| RST               | Reset                             | Ι                  | When $\overline{\text{RST}}$ is LOW, all internal registers are set to their default state, the address pointer is set to zero and the $\overline{\text{EOB}}$ 1 and $\overline{\text{EOB}}$ 2 flags are set HIGH. $\overline{\text{RST}}$ is asynchronous to SCLK.                                                                                                                                                                                                                |

| NOTE:             |                                   |                    | 3016 tbl 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

1. "I/O" is bidirectional Input and Output. "I" is Input and "O" is Output.

| Symbol               | Rating                                     | Commercial   | Military     | Unit |

|----------------------|--------------------------------------------|--------------|--------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0 | –0.5 to +7.0 | V    |

| ТА                   | Operating<br>Temperature                   | 0 to +70     | –55 to +125  | °C   |

| TBIAS                | Temperature<br>Under Bias                  | -55 to +125  | -65 to +135  | °C   |

| TSTG                 | Storage<br>Temperature                     | -55 to +125  | -65 to +150  | °C   |

| IOUT                 | DC Output<br>Current                       | 50           | 50           | mA   |

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

#### NOTES:

- 3016 tbl 03 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. VTERM must not exceed Vcc + 0.5V for more than 25% of the cycle time or 10ns maximum, and is limited to  $\leq$  20mA for the period of VTERM  $\geq$  Vcc + 0.5V.

### RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade      | Ambient<br>Temperature | GND | vcc         |

|------------|------------------------|-----|-------------|

| Military   | –55°C to +125°C        | 0V  | 5.0V ± 10%  |

| Commercial | 0°C to +70°C           | 0V  | 5.0V ± 10%  |

|            |                        |     | 3016 tbl 04 |

### **RECOMMENDED DC OPERATING** CONDITIONS

| Symbol | Parameter          | Min.                | Тур. | Max.   | Unit |

|--------|--------------------|---------------------|------|--------|------|

| VCC    | Supply Voltage     | 4.5                 | 5.0  | 5.5    | V    |

| GND    | Supply Voltage     | 0                   | 0    | 0      | V    |

| VIH    | Input High Voltage | 2.2                 | —    | 6.0(2) | V    |

| VIL    | Input Low Voltage  | -0.5 <sup>(1)</sup> | _    | 0.8    | V    |

NOTES:

1.  $V_{IL} \ge -1.5V$  for pulse width less than 10ns.

2. VTERM must not exceed Vcc + 0.5V.

### CAPACITANCE<sup>(1)</sup>

### (TA = +25°C, F = 1.0MHz)TQFP ONLY

| Symbol | Parameter             | Conditions <sup>(2)</sup> | Max. | Unit        |

|--------|-----------------------|---------------------------|------|-------------|

| CIN    | Input Capacitance     | VIN = 3dV                 | 9    | pF          |

| COUT   | Output<br>Capacitance | VOUT = 3dV                | 10   | pF          |

| NOTES: |                       |                           | 3    | 3016 tbl 06 |

NOTES:

1. This parameter is determined by device characterization, but is not production tested.

2. 3dV references the interpolated capacitance when the input and output signals switch from 0V to 3V or from 3V to 0V.

### DC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE (Vcc = $5.0V \pm 10\%$ )

|        |                                      |                                                                            | IDT7 | )825S | IDT7 | 0825L |             |

|--------|--------------------------------------|----------------------------------------------------------------------------|------|-------|------|-------|-------------|

| Symbol | Parameter                            | Test Conditions                                                            | Min. | Max.  | Min. | Max.  | Unit        |

| ILI    | Input Leakage Current <sup>(1)</sup> | VCC = Max. VIN = GND to VCC                                                | _    | 5.0   | _    | 1.0   | μA          |

| ILO    | Output Leakage Current               | VCC = Max. $\overline{CE}$ and $\overline{SCE}$ = VIH<br>VOUT = GND to VCC | —    | 5.0   | —    | 1.0   | μΑ          |

| VOL    | Output Low Voltage                   | IOL = 4mA, VCC = Min.                                                      | —    | 0.4   |      | 0.4   | V           |

| Voh    | Output High Voltage                  | IOH = -4mA, VCC = Min.                                                     | 2.4  | _     | 2.4  | _     | V           |

| NOTE   |                                      |                                                                            |      |       |      |       | 3016 tbl 07 |

1. At Vcc ≤ 2.0V input leakages are undefined.

3016 tbl 05

### DC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE<sup>(1)</sup> (VCC = $5.0V \pm 10\%$ )

|        |                                                           | Test                                                                                                                                       |               |                     | 5X20<br>. Only |            | 5X25<br>. Only      | 70825X35            |            | 70825X45            |            |      |

|--------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|----------------|------------|---------------------|---------------------|------------|---------------------|------------|------|

| Symbol | Parameter                                                 | Condition                                                                                                                                  | Version       | Typ. <sup>(2)</sup> | Max.           | Тур.       | <sup>(2)</sup> Max. | Typ. <sup>(2)</sup> | Max.       | Typ. <sup>(2)</sup> | Max.       | Unit |

| ICC    | Dynamic Operating<br>Current                              | $\overline{CE}$ = VIL, Outputs<br>Open, $\overline{SCE}$ = VIL <sup>(5)</sup>                                                              | MIL. S<br>L   |                     |                |            | _                   | 160<br>160          | 400<br>340 | 155<br>155          | 400<br>340 | mA   |

|        | (Both Ports Active)                                       | $f = fMAX^{(3)}$                                                                                                                           | COM'L. S<br>L | 180<br>180          | 380<br>330     | 170<br>170 | 360<br>310          | 160<br>160          | 340<br>290 | 155<br>155          | 340<br>290 |      |

| ISB1   | Standby Current<br>(Both Ports - TTL Level                | $\frac{\overline{\text{SCE}}}{\overline{\text{CMD}}} = \text{VIH}^{(7)}$                                                                   | MIL. S<br>L   | _                   |                |            | _                   | 20<br>20            | 85<br>65   | 16<br>16            | 85<br>65   | mA   |

|        | Inputs)                                                   | $f = fMAX^{(3)}$                                                                                                                           | COM'L. S<br>L | 25<br>25            | 70<br>50       | 25<br>25   | 70<br>50            | 20<br>20            | 70<br>50   | 16<br>16            | 70<br>50   |      |

| ISB2   | Standby Current<br>(One Port - TTL Level                  | $\overline{CE}$ or $\overline{SCE}$ = VIH<br>Active Port Outputs                                                                           | MIL. S<br>L   | _                   |                | _          | _                   | 95<br>95            | 290<br>250 | 90<br>90            | 290<br>250 | mA   |

|        | Input)                                                    | Open, $f = fMAX^{(3)}$                                                                                                                     | COM'L. S<br>L | 115<br>115          | 260<br>230     | 105<br>105 | 250<br>220          | 95<br>95            | 240<br>210 | 90<br>90            | 240<br>210 |      |

| ISB3   | Full Standby Current<br>(Both Ports - CMOS                | $\frac{Both \text{ Ports } \overline{CE} \text{ and }}{\overline{SCE}} \ge VCC \text{ - } 0.2V^{(6,7)}$                                    | MIL. S<br>L   |                     |                |            | _                   | 1.0<br>0.2          | 30<br>10   | 1.0<br>0.2          | 30<br>10   | mA   |

|        | Level Inputs)                                             | $\begin{array}{l} \text{VIN} \geq \text{VCC} \text{ - } 0.2 \text{V} \text{ or} \\ \text{VIN} \leq 0.2 \text{V},  f = 0^{(4)} \end{array}$ | COM'L. S<br>L | 1.0<br>0.2          | 15<br>5        | 1.0<br>0.2 | 15<br>5             | 1.0<br>0.2          | 15<br>5    | 1.0<br>0.2          | 15<br>5    |      |

| ISB4   | Full Standby Current<br>(One Port - CMOS<br>Level Inputs) | One Port $\overline{CE}$ or<br>$\overline{SCE} \ge VCC - 0.2V^{(6)}$<br>Outputs Open                                                       | MIL. S<br>L   | _                   | _              |            | _                   | 90<br>90            | 260<br>215 | 85<br>85            | 260<br>215 | mA   |

|        |                                                           | VIN $\geq$ VCC - 0.2V or                                                                                                                   | COM'L. S      | 110                 | 240            | 100        | 230                 | 90                  | 220        | 85                  | 220        |      |

|        |                                                           | $VIN \le 0.2V$                                                                                                                             | L             | 110                 | 200            | 100        | 190                 | 90                  | 180        | 85                  | 180        |      |

#### NOTES:

1. "X" in part number indicates power rating (S or L).

2. Vcc = 5V, Ta =  $+25^{\circ}$ C; guaranteed by device characterization but not production tested.

3. At f = fMAX, address, control lines (except Output Enable), and SCLK are cycling at the maximum frequency read cycle of 1/tRC.

4. f = 0 means no address or control lines change.

5. SCE may transition, but is Low (SCE=VIL) when clocked in by SCLK.

6. SCE may be  $\leq$  0.2V, after it is clocked in, since SCLK=VIH must be clocked in prior to powerdown.

7. If one port is enabled (either CE or SCE = Low) then the other port is disabled (SCE or CE = High, respectively). CMOS High ≥ Vcc - 0.2V and Low ≤ 0.2V, and TTL High = VIH and Low = VIL.

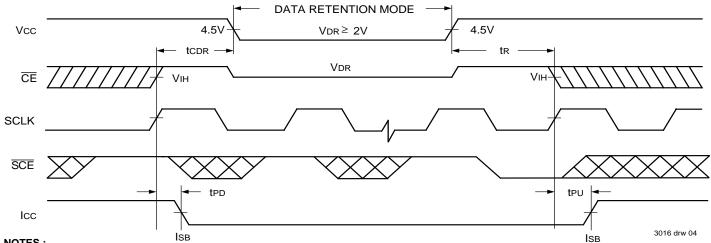

### DATA RETENTION CHARACTERISTICS OVER ALL TEMPERATURE RANGES

(L VERSION ONLY) (VLC  $\leq$  0.2V, VHC  $\geq$  VCC - 0.2V)

| Symbol              | Parameter                            | Test Conditio                                     | Min.   | Typ. <sup>(1)</sup> | Max. | Unit |    |

|---------------------|--------------------------------------|---------------------------------------------------|--------|---------------------|------|------|----|

| Vdr                 | VCC for Data Retention               | VCC = 2V                                          |        | 2.0                 | _    | _    | V  |

| ICCDR               | Data Retention Current               | CE = VHC                                          | MIL.   | _                   | 100  | 4000 | μA |

|                     |                                      | VIN = VHC or = VLC                                | COM'L. | _                   | 100  | 1500 |    |

| tCDR <sup>(3)</sup> | Chip Deselect to Data Retention Time | $\overline{\text{SCE}} = \text{VHC}^{(4)}$ when S | CLK=_∕ | 0                   | _    | _    | ns |

| tR <sup>(3)</sup>   | Operation Recovery Time              | CMD = VHC                                         |        | tRC <sup>(2)</sup>  | _    |      | ns |

NOTES :

1.  $TA = +25^{\circ}C$ , Vcc = 2V; guaranteed by device characterization but not production tested.

2. tRC = Read Cycle Time

3. This parameter is guaranteed by device characterization, but is not production tested.

4. To initiate data retention,  $\overline{SCE} = VIH$  must be clocked in.

3016 tbl 08

### DATA RETENTION AND POWER DOWN/UP WAVEFORM (RANDOM AND SEQUENTIAL PORT) (1,2)

#### NOTES :

1. SCE is synchronized to the sequential clock input.

2.  $\overline{CMD} \ge Vcc - 0.2V.$

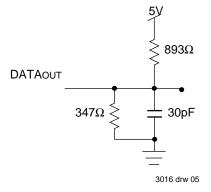

893Ω DATAOUT-347Ω 5pF 3016 drw 06

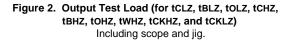

Figure 1. AC Output Test Load

5Y

### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V         |

|-------------------------------|---------------------|

| Input Rise/Fall Times         | 3ns Max.            |

| Input Timing Reference Levels | 1.5V                |

| Output Reference Levels       | 1.5V                |

| AC Test Load                  | Figures 1, 2, and 3 |

|                               | 3016 tbl 10         |

Figure 3. Lumped Capacitance Load Typical Derating Curve

### TRUTH TABLE I – RANDOM ACCESS READ AND WRITE (1,2)

|      |     | Inp | uts/Ou           | Itputs           | 5                |           |           | MODE                                                         |

|------|-----|-----|------------------|------------------|------------------|-----------|-----------|--------------------------------------------------------------|

| CE   | CMD | R/W | ŌĒ               | LB               | UB               | I/O0-I/O7 | I/O8-I/O- |                                                              |

| L    | Н   | Н   | L                | L                | L                | DATAOUT   | DATAOUT   | Read both Bytes.                                             |

| L    | Н   | Н   | L                | L                | Н                | DATAOUT   | High-Z    | Read lower Byte only.                                        |

| L    | Н   | Н   | L                | Н                | L                | High-Z    | DATAOUT   | Read upper Byte only.                                        |

| L    | Н   | L   | H(3)             | L                | L                | DATAIN    | DATAIN    | Write to both Bytes.                                         |

| L    | Н   | L   | H(3)             | L                | н                | DATAIN    | High-Z    | Write to lower Byte only.                                    |

| L    | Н   | L   | H <sup>(3)</sup> | Н                | L                | High-Z    | DATAIN    | Write to upper Byte only.                                    |

| Н    | Н   | Х   | Х                | Х                | Х                | High-Z    | High-Z    | Both Bytes deselected and powered down.                      |

| L    | Н   | Н   | Н                | Х                | Х                | High-Z    | High-Z    | Outputs disabled but not powered down.                       |

| L    | Н   | Х   | Х                | Н                | н                | High-Z    | High-Z    | Both Bytes deselected but not powered down.                  |

| Н    | L   | L   | H <sup>(3)</sup> | L <sup>(4)</sup> | L <sup>(4)</sup> | DATAIN    | DATAIN    | Write I/O0-I/O12 to the Buffer Command Register.             |

| Н    | L   | Н   | L                | L(4)             | L(4)             | DATAOUT   | DATAOUT   | Read contents of the Buffer Command Register via I/O0-I/O12. |

| NOTE | ç.  |     |                  |                  |                  |           |           | 3016 tbl 1                                                   |

1.  $H = V_{H}$ ,  $L = V_{L}$ , X = Don't Care, and High-Z = High-impedance.

2. RST, SCE, CNTEN, SR/W, SLD, SSTRT1, SSTRT2, SCLK, SI/O0-SI/O15, EOB1, EOB2, and SOE are unrelated to the random access port control and operation.

3. If OE = VIL during write, twHz must be added to the twP or tcw write pulse width to allow the bus to float prior to being driven.

4. Byte operations to control register using UB and LB separately are also allowed.

### TRUTH TABLE II - SEQUENTIAL READ (1,2,3,6,8)

|          |     | Inpu  | its/Out | puts |      |     |            | MODE                                                                                                     |

|----------|-----|-------|---------|------|------|-----|------------|----------------------------------------------------------------------------------------------------------|

| SCLK     | SCE | CNTEN | SR/W    | EOB1 | EOB2 | SOE | SI/O       |                                                                                                          |

| <u> </u> | L   | L     | Н       | LOW  | LAST | L   | [EOB1]     | Counter Advanced Sequential Read with $\overline{\text{EOB}}$ 1 reached.                                 |

| 1        | L   | Н     | Н       | LAST | LAST | L   | [EOB1 - 1] | Non-Counter Advanced Sequential Read, without $\overline{\text{EOB}}$ 1 reached.                         |

| 1        | L   | L     | Н       | LAST | LOW  | L   | [EOB2]     | Counter Advanced Sequential Read with EOB2 reached.                                                      |

| <u> </u> | L   | Н     | Н       | LAST | LAST | L   | [EOB2 - 1] | Non-Counter Advanced Sequential Read without EOB2 reached.                                               |

| ſ        | L   | L     | Н       | LOW  | LOW  | Н   | HIGH-Z     | Counter Advanced Sequential Non-Read with $\overline{\text{EOB}}1$ and $\overline{\text{EOB}}2$ reached. |

3016 tbl 12

### TRUTH TABLE III – SEQUENTIAL WRITE (1,2,3,4,5,6,7,8)

| Inputs/Outputs |     |       |      |                    |      |   |        | MODE                                                                                                  |

|----------------|-----|-------|------|--------------------|------|---|--------|-------------------------------------------------------------------------------------------------------|

| SCLK           | SCE | CNTEN | SR/W | EOB1 EOB2 SOE SI/O |      |   |        |                                                                                                       |

| $\checkmark$   | L   | Н     | L    | LAST               | LAST | Н | SI/OIN | Non-Counter Advanced Sequential Write, without EOB1 or EOB2 reached                                   |

| $\checkmark$   | L   | L     | L    | LOW                | LOW  | Н | SI/OIN | Counter Advanced Sequential Write with $\overline{\text{EOB}}1$ and $\overline{\text{EOB}}2$ reached. |

| 1              | Н   | Н     | Х    | LAST               | LAST | Х | High-Z | No Write or Read due to Sequential port Deselect. No counter advance.                                 |

| 1              | Н   | L     | Х    | NEXT               | NEXT | Х | High-Z | No Write or Read due to Sequential port Deselect. Conter does advance.                                |

| NOTES          |     |       |      |                    |      |   |        | 3016 tbl 13                                                                                           |

NOTES:

1.  $H = V_{H}$ ,  $L = V_{L}$ , X = Don't Care, and High-Z = High-impedance. LOW = VoL.

2. RST, SLD, SSTRT1, SSTRT2 are continuously HIGH during a sequential write access, other than pointer access operations.

3. CE, OE, R/W, CMD, LB, UB, and I/O0-I/O15 are unrelated to the sequential port control and operation except for CMD which must not be used concurrently with the sequential port operation (due to the counter and register control). CMD should be HIGH (CMD = VIH) during sequential port access.

4. SOE must be HIGH (SOE=VIH) prior to write conditions only if the previous cycle is a read cycle, since the data being written must be an input at the rising edge of the clock during the cycle in which SR/W = VIL.

5. SI/OIN refers to SI/O0-SI/O15 inputs.

6. "LAST" refers to the previous value still being output, no change.

7. Termination of a write is done on the Low-to-High transition of SCLK if SR/W or SCE is High.

8. When CLKEN=Low, the address is incremented on the next rising edge before any operation takes place. See the diagrams called "Sequential Counter Enable Cycle after Reset, Read (and write) Cycle".

3016 tbl 14

# TRUTH TABLE IV – SEQUENTIAL ADDRESS POINTER OPERATIONS (1,2,3,4,5)

|                                    | Inputs/Outputs |                  |                                                   |     |                                                          |

|------------------------------------|----------------|------------------|---------------------------------------------------|-----|----------------------------------------------------------|

| SCLK                               | SLD            | SSTRT1           | SSTRT2                                            | SOE | MODE                                                     |

| ſ                                  | Н              | L                | Н                                                 | Х   | Start address for Buffer #1 loaded into Address Pointer. |

| ſ                                  | Н              | Н                | L                                                 | Х   | Start address for Buffer #2 loaded into Address Pointer. |

| $\int$ L H H H <sup>(6)</sup> Data |                | H <sup>(6)</sup> | Data on SI/O0-SI/O12 loaded into Address Pointer. |     |                                                          |

#### NOTES:

1. H = VIH, L = VIL, X = Don't Care, and High-Z = High-impedance.

2. RST is continuously HIGH. The conditions of SCE, CNTEN, and SR/W are unrelated to the sequential address pointer operations.

3. CE, OE, R/W, LB, UB, and I/Oo-I/O15 are unrelated to the sequential port control and operation, except for CMD which must not be used concurrently with the sequential port operation (due to the counter and register control). CMD should be HIGH (CMD = VIH) during sequential port access.

4. Address pointer can also change when it reaches an end of buffer address. See Flow Control Bits table.

5. When SLD is sampled LOW, there is an internal delay of one cycle before the address pointer changes. The state of CNTEN is ignored and the address is not incremented during the two cycles.

6.  $\overline{\text{SOE}}$  may be LOW with  $\overline{\text{SCE}}$  deselect or in the write mode using SR/W.

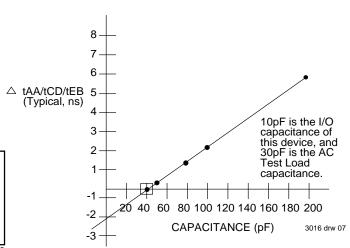

### ADDRESS POINTER LOAD CONTROL (SLD)

In  $\overline{\text{SLD}}$  mode, there is an internal delay of one cycle before the address pointer changes in the cycle following  $\overline{\text{SLD}}$ . When  $\overline{\text{SLD}}$  is LOW, data on the inputs SI/O0-SI/O12 is loaded into a data-in register on the LOW-to-HIGH transition of  $\overline{\text{SCLK}}$ . On the cycle following  $\overline{\text{SLD}}$ , the address pointer changes to the address location contained in the data-in register. SSTRT1, SSTRT2 may not be low while SLD is LOW, or during the cycle following SLD. The SSTRT1 and SSTRT2 require only one clock cycle, since these addresses are pre-loaded in the registers already.

### SLD MODE (1)

NOTE:

At SCLK edge (A), SI/Oo-SI/O12 data is loaded into a data-in register. At edge (B), contents of the data-in register are loaded into the address pointer (i.e. address pointer changes). At SCLK edge (A), STRT1 and SSTRT2 must be high to ensure for proper sequential address pointer loading. At SCLK edge (B), SLD and SSTRT1.2 must be high to ensure for proper sequential address pointer loading. For SSTRT1 or SSTRT2, the data to be read will be ready for edge (B), while data will not be ready at edge (B) when SLD is used, but will be ready at edge (C).

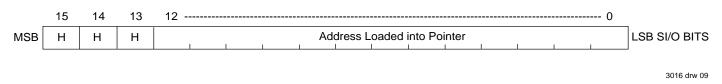

## SEQUENTIAL LOAD OF ADDRESS INTO POINTER/COUNTER<sup>(1)</sup>

#### NOTE:

1. "H" = VIH for the SI/O intput state.

## Reset (RST)

Setting RST LOW resets the control state of the SARAM. RST functions asynchronously of SCLK. (i.e. not registered). The default states after a reset operation are as follows:

| Register                | Contents                                                       |

|-------------------------|----------------------------------------------------------------|

| Address Pointer         | 0                                                              |

| EOB Flags               | Cleared to High state                                          |

| Buffer Flow Mode        | BUFFER CHAINING                                                |

| Start Address Buffer #1 | 0 (1)                                                          |

| End Address Buffer #1   | 4095 (4K)                                                      |

| Start Address Buffer #2 | 4096 (4K+1)                                                    |

| End Address Buffer #2   | 8191 (8K)                                                      |

| Registered State        | $\overline{\text{SCE}}$ = VIH, SR/ $\overline{\text{W}}$ = VIL |

3016 tbl 15

# BUFFER COMMAND MODE (CMD)

Buffer Command Mode (CMD) allows the random access port to control the state of the two buffers. Address pins A0-A2 and I/O pins I/O0-I/O12 are used to access the start of buffer and the end of buffer addresses and to set the flow control mode of each buffer. The Buffer Command Mode also allows

reading and clearing the status of the EOB flags. Seven different CMD cases are available depending on the conditions of A0-A2 and R/W. Address bits A3-A12 and data I/O bits I/O13-I/O15 are not used during this operation.

## RANDOM ACCESS PORT CMD MODE<sup>(1)</sup>

| Case # | A2-A0   | R/W   | DESCRIPTIONS                                                    |             |

|--------|---------|-------|-----------------------------------------------------------------|-------------|

| 1      | 000     | 0 (1) | Write (read) the start address of Buffer #1 through I/O0-I/O12. |             |

| 2      | 001     | 0 (1) | Write (read) the end address of Buffer #1 through I/O0-I/O12.   |             |

| 3      | 010     | 0 (1) | Write (read) the start address of Buffer #2 through I/O0-I/O12. |             |

| 4      | 011     | 0 (1) | Write (read) the end address of Buffer #2 through I/O0-I/O12.   |             |

| 5      | 100     | 0 (1) | Write (read) flow control register                              |             |

| 6      | 101     | 0     | Write only – clear EOB1 and/or EOB2 flag                        |             |

| 7      | 101     | 1     | Read only – flag status register                                |             |

| 8      | 110/111 | (X)   | (Reserved)                                                      |             |

| IOTE:  | •       | •     | •                                                               | 3016 tbl 16 |

NOTE:

1. R/W input "0(1)" indicates a write(0) or read(1) occurring with the same address input.

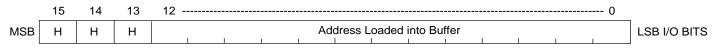

# CASES 1 THROUGH 4: START AND END OF BUFFER REGISTER DESCRIPTION<sup>(1,2)</sup>

#### NOTES

1. "H" = VOH for I/O in the output state and "Don't Cares" for I/O in the input state.

2. A write into the buffer occurs when R/W = VIL and a read when R/W = VIH. EOB1/SOB1 and EOB2/SOB2 are chosen through address A0-A2 while CMD = VIL and  $\overline{CE}$  = VIH.

### CASE 5: BUFFER FLOW MODES

Within the SARAM, the user can designate one of four buffer flow modes for each buffer. Each buffer flow mode defines a unique set of actions for the sequential port address pointer and EOB flags. In BUFFER CHAINING mode, after the address pointer reaches the end of the buffer, it sets the corresponding EOB flag and continues from the start address of the other buffer. In STOP mode, the address pointer stops incrementing after it reaches the end of the buffer. In LINEAR mode, the address pointer ignores the end of buffer address and increments past it, but sets the EOB flag. MASK mode is the same as LINEAR mode except EOB flags are not set.

3016 drw 10

### FLOW CONTROL REGISTER DESCRIPTION<sup>(1,2)</sup>

|       | 15 |   |   |   |   |         |   |   |     |       |                    |   |          |         |           | 0       |              |

|-------|----|---|---|---|---|---------|---|---|-----|-------|--------------------|---|----------|---------|-----------|---------|--------------|

| MSB   | Н  | н | н | н | н | Н       | н | н | н   | н     | н                  | 4 | 3        | 2       | 1         | 0       | LSB I/O BITS |

|       |    |   | - | - |   | · · · · | - |   |     |       | ounter  <br>STOP N |   |          | E       | Buffer #1 | flow co | ontrol       |

| NOTES |    |   | 4 |   |   |         |   |   | . : | - 4 - |                    | В | uffer #2 | flow co | ontrol    |         | 3016 drw 11  |

1. "H" = VOH for I/O in the output state and "Don't Cares"' for I/O in the input state.

2. Writing a 0 into bit 4 releases the address pointer after it is stopped due to the STOP mode and allows sequential write operations to resume. This occurs asynchronously of SCLK, and therefore caution should be taken. The pointer will be at address EOB+2 on the next rising edge of SCLK that is enabled by CNTEN. The pointer is also released by RST, SLD, SSTRT1 and SSTRT2 operations.

### **FLOW CONTROL BITS**

| Flow C                           | ontrol Bits        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 1 & Bit 0<br>(Bit 3 & Bit 2) | Mode               | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 00                               | BUFFER<br>CHAINING | $\overline{\text{EOB}}$ 1 ( $\overline{\text{EOB}}$ 2) is asserted (Active Low output) when the pointer matches the end address of Buffer #1 (Buffer #2). The pointer value is changed to the start address of Buffer #2 (Buffer #1). <sup>(1,3)</sup>                                                                                                                                                                                                                                                                                                                                               |

| 01                               | STOP               | $\overline{\text{EOB}}_1$ ( $\overline{\text{EOB}}_2$ ) is asserted when the pointer matches the end address of Buffer #1 (Buffer #2).<br>The address pointer will stop incrementing when it reaches the next address ( $\overline{\text{EOB}}$ address + 1), if<br>$\overline{\text{CNTEN}}$ is Low on the next clock's rising edge. Otherwise, the address pointer will stop incrementing on<br>$\overline{\text{EOB}}$ . Sequential write operations are inhibited after the address pointer is stopped. The pointer can be<br>released by bit 4 of the flow control register. <sup>(1,2,4)</sup> |

| 10                               | LINEAR             | EOB1 (EOB2) is asserted when the pointer matches the end address of Buffer #1 (Buffer #2).      The pointer keeps incrementing for further operations. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11                               | MASK               | $\overline{\text{EOB}}$ 1 ( $\overline{\text{EOB}}$ 2) is not asserted when the pointer reaches the end address of Buffer #1 (Buffer #2), although the flag status bits will be set. The pointer keeps incrementing for further operations.                                                                                                                                                                                                                                                                                                                                                          |

#### NOTES:

1. EOB1 and EOB2 may be asserted (set) at the same time, if both end addresses have been loaded with the same value.

2. CMD Flow Control bits are unchanged, the count does not continue advancement.

3. If  $\overline{\text{EOB}}_1$  and  $\overline{\text{EOB}}_2$  are equal, then the pointer will jump to the start of Buffer #1.

4. If counter has stopped at EOBx and was released by bit 4 of the flow control register, CNTEN must be LOW on the next rising edge of SCLK otherwise the flow control will remain in the STOP mode.

# CASES 6 AND 7: FLAG STATUS REGISTER BIT DESCRIPTION<sup>(1)</sup>

|        | 15      |           |          |           |         |          |          |           |           |           |   |   |   |    |          | 0          |                         |

|--------|---------|-----------|----------|-----------|---------|----------|----------|-----------|-----------|-----------|---|---|---|----|----------|------------|-------------------------|

| MSB    | Н       | н         | н        | н         | н       | н        | н        | н         | н         | н         | н | н | н | н  | 1        | 0          | LSB I/O BITS            |

| NOTE   | :       |           |          |           |         |          |          |           |           | 1         |   |   |   |    | Er       | nd of but  | ffer flag for Buffer #1 |

| 1. "H" | ' = Vон | for I/O i | n the ou | utput sta | ate and | "Don't ( | Cares" f | or I/O ir | n the inp | out state | • |   |   | Er | nd of bu | iffer flag | for Buffer #2           |

|        |         |           |          |           |         |          |          |           |           |           |   |   |   |    |          |            | 3016 drw 12             |

## CASE 6: FLAG STATUS REGISTER WRITE CONDITIONS<sup>(1)</sup>

| Flag Status Bit 0, (Bit 1) | Functional Description                       |

|----------------------------|----------------------------------------------|

| 0                          | Clears Buffer Flag EOB1, (EOB2).             |

| 1                          | No change to the Buffer Flag. <sup>(2)</sup> |

| NOTES:                     | 3016 tbl 18                                  |

NOTES:

1. Either bit 0 or bit 1, or both bits, may be changed simultaneously. One may be cleared while the second is left alone or cleared.

2. Remains as it was prior to the CMD operation, either HIGH (1) or LOW (0).

## **CASE 7: FLAG STATUS REGISTER READ CONDITIONS**

| Flag Status Bit 0, (Bit 1) | Functional Description                                                                      |

|----------------------------|---------------------------------------------------------------------------------------------|

| 0                          | EOB1 (EOB2) flag has not been set, the<br>Pointer has not reached the End of the<br>Buffer. |

| 1                          | EOB1 (EOB2) flag has been set, the<br>Pointer has reached the End of the Buffer.            |

3016 tbl 19

3016 tbl 17

### CASES 8 AND 9: (RESERVED)

Illegal operations. All outputs will be HIGH on the I/O bus during a READ.

### **RANDOM ACCESS PORT: AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE** <sup>(2,3)</sup>

|         |                                          | IDT708 | 325X20 | IDT70 | 825X25 | IDT7 | 0825X35 | IDT70 |      |      |

|---------|------------------------------------------|--------|--------|-------|--------|------|---------|-------|------|------|

|         |                                          | Com'l  | . Only | Com'l | . Only |      |         |       |      |      |

| Symbol  | Parameter                                | Min.   | Max.   | Min.  | Max.   | Min. | Max.    | Min.  | Max. | Unit |

| READ CY | CLE                                      |        | -      |       |        |      |         |       |      |      |

| tRC     | Read Cycle Time                          | 20     | —      | 25    | —      | 35   | —       | 45    | —    | ns   |

| tAA     | Address Access Time                      | —      | 20     | _     | 25     | —    | 35      | —     | 45   | ns   |

| tACE    | Chip Enable Access Time                  | —      | 20     | _     | 25     | —    | 35      |       | 45   | ns   |

| tBE     | Byte Enable Access Time                  | —      | 20     | _     | 25     | —    | 35      |       | 45   | ns   |

| tOE     | Output Enable Access Time                | —      | 10     | _     | 10     | —    | 15      |       | 20   | ns   |

| tOH     | Output Hold from Address Change          | 3      | —      | 3     | —      | 3    | —       | 3     | —    | ns   |

| tCLZ    | Chip Select Low-Z Time <sup>(1)</sup>    | 3      | —      | 3     | —      | 3    | —       | 3     | —    | ns   |

| tBLZ    | Byte Enable Low-Z Time <sup>(1)</sup>    | 3      | —      | 3     | —      | 3    | —       | 3     | —    | ns   |

| tOLZ    | Output Enable Low-Z Time <sup>(1)</sup>  | 2      | _      | 2     | —      | 2    | —       | 2     | —    | ns   |

| tCHZ    | Chip Select High-Z Time <sup>(1)</sup>   | —      | 10     | _     | 12     | —    | 15      |       | 15   | ns   |

| tBHZ    | Byte Enable High-Z Time <sup>(1)</sup>   | —      | 10     | _     | 12     | —    | 15      |       | 15   | ns   |

| tOHZ    | Output Enable High-Z Time <sup>(1)</sup> | —      | 9      | —     | 11     | —    | 15      |       | 15   | ns   |

| tPU     | Chip Select Power-Up Time                | 0      | —      | 0     | —      | 0    | —       | 0     | —    | ns   |

| tPD     | Chip Select Power-Down Time              | 1 —    | 20     | _     | 25     | 1 —  | 35      | _     | 45   | ns   |

#### NOTES:

1. Transition measured at ±200mV from steady state. This parameter is guaranteed with the AC Test Load (Figure 2) by device characterization, but is not production tested.

2. "X" in part number indicates power rating (S or L).

3. CMD access follows standard timing listed for both read and write accesses, (CE = VIH when CMD = VIL) or (CMD = VIH when CE = VIL).

## **RANDOM ACCESS PORT: AC ELECTRICAL CHARACTERISTICS** OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE (2,4)

|         |                                                | IDT708<br>Com'l |      | IDT708<br>Com'l |      | IDT70 | 825X35 | IDT708 |      |           |

|---------|------------------------------------------------|-----------------|------|-----------------|------|-------|--------|--------|------|-----------|

| Symbol  | Parameter                                      | Min.            | Max. | Min.            | Max. | Min.  | Max.   | Min.   | Max. | Unit      |

| WRITE C | YCLE                                           | _               | _    | -               | -    | -     |        |        | -    |           |

| tWC     | Write Cycle Time                               | 20              | —    | 25              | —    | 35    | —      | 45     | —    | ns        |

| tCW     | Chip Select to End-of-Write                    | 15              | —    | 20              | —    | 25    | —      | 30     |      | ns        |

| tAW     | Address Valid to End-of-Write <sup>(3)</sup>   | 15              | —    | 20              | —    | 25    | —      | 30     | _    | ns        |

| tAS     | Address Set-up Time                            | 0               | —    | 0               | —    | 0     | —      | 0      | _    | ns        |

| tWP     | Write Pulse Width <sup>(3)</sup>               | 13              | —    | 20              | —    | 25    | —      | 30     | _    | ns        |

| tBP     | Byte Enable Pulse Width <sup>(3)</sup>         | 15              | —    | 20              | —    | 25    | —      | 30     | —    | ns        |

| tWR     | Write Recovery Time                            | 0               | —    | 0               | —    | 0     | —      | 0      | —    | ns        |

| tWHZ    | Write Enable Output High-Z Time <sup>(1)</sup> | —               | 10   | —               | 12   | —     | 15     | —      | 15   | ns        |

| tDW     | Data Set-up Time                               | 13              | —    | 15              | —    | 20    | —      | 25     | —    | ns        |

| tDH     | Data Hold Time                                 | 0               | —    | 0               | —    | 0     | —      | 0      | _    | ns        |

| tOW     | Output Active from End-of-Write                | 3               | —    | 3               | _    | 3     | —      | 3      | —    | ns        |

| NOTES:  |                                                |                 | -    |                 |      |       |        |        | . 30 | 16 tbl 21 |

3016 tbl 20

1. Transition measured at ±200mV from steady state. This parameter is guaranteed with the AC Test Load (Figure 2) by device characterization, but is not production tested.

2. "X" in part number indicates power rating (S or L).

3.  $\overline{OE}$  is continuously HIGH,  $\overline{OE}$  = VIH. If during the R/W controlled write cycle the  $\overline{OE}$  is LOW, two must be greater or equal to twHz + tow to allow the I/O drivers to turn off and on the data to be placed on the bus for the required tow. If OE is HIGH during the R/W controlled write cycle, this requirement does not apply and the minimum write pulse is the specified twp. For the CE controlled write cycle, OE may be LOW with no degradation to tcw timing. 4. CMD access follows standard timing listed for both read and write accesses, (CE = VIH when CMD = VIL) or (CMD = VIH when CE = VIL).

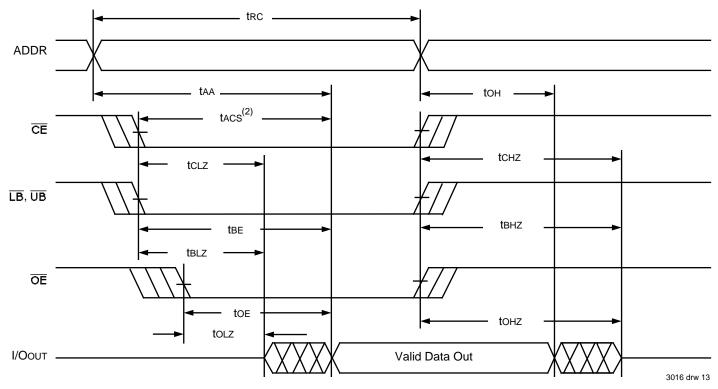

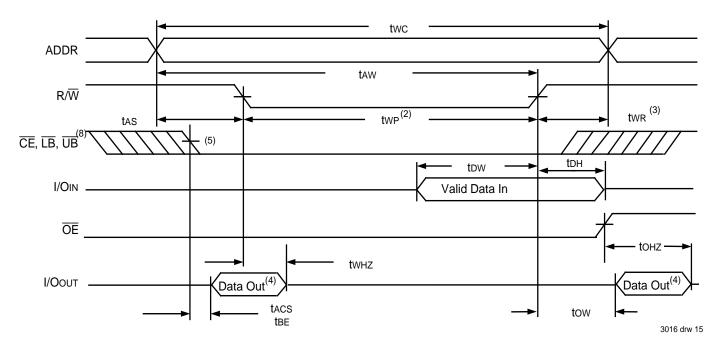

# RANDOM ACCESS PORT WAVEFORM: READ CYCLES (1,2)

#### NOTES:

1.  $R/\overline{W}$  is HIGH for Read cycle.

2. Address valid prior to or coincident with CE transition LOW; otherwise tAA is the limiting parameter.

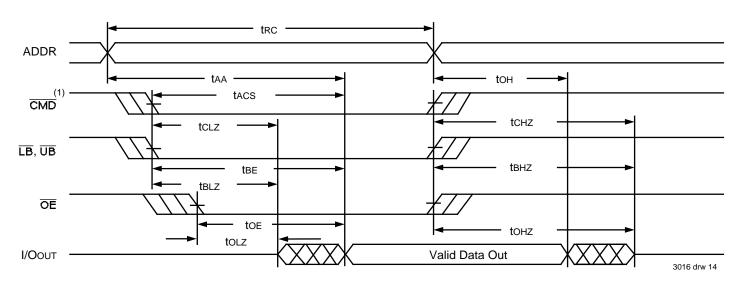

### RANDOM ACCESS PORT WAVEFORM: READ CYCLES BUFFER COMMAND MODE

#### NOTE:

1.  $\overline{CE} = VIH$  when  $\overline{CMD} = VIL$ .

# RANDOM ACCESS PORT WAVEFORM: WRITE CYCLE NO.1 (R/W CONTROLLED TIMING) (1,6)

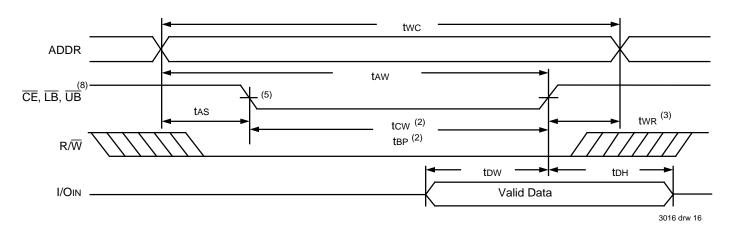

RANDOM ACCESS PORT WAVEFORM: WRITE CYCLE NO.2 ( $\overline{CE}$ ,  $\overline{LB}$ , AND/OR  $\overline{UB}$  CONTROLLED TIMING) <sup>(1,6,7)</sup>

- 1. R/ $\overline{W}$ ,  $\overline{CE}$ , or  $\overline{LB}$  and  $\overline{UB}$  must be inactive during all address transitions.

- 2. A write occurs during the overlap of  $R/W = V_{IL}$ ,  $\overline{CE} = V_{IL}$  and  $\overline{LB} = V_{IL}$  and/or  $\overline{UB} = V_{IL}$ .

- 3. twr is measured from the earlier of  $\overline{CE}$  (and  $\overline{LB}$  and/or  $\overline{UB}$ ) or R/W going HIGH to the end of the write cycle.

- 4. During this period, I/O pins are in the output state and the input signals must not be applied.

- 5. If the CE LOW transition occurs simultaneously with or after the R/W LOW transition, the outputs remain in the High-impedance state.

- 6. OE is continuously HIGH, OE = VIH. If during the R/W controlled write cycle the OE is LOW, twp must be greater or equal to twHz + tow to allow the I/O drivers to turn off and on the data to be placed on the bus for the required tow. If OE is HIGH during the R/W controlled write cycle, this requirement does not apply and the minimum write pulse is the specified twp. For the CE controlled write cycle, OE may be LOW with no degregation to tcw timing.

7. I/Oour is never enabled, therefore the output is in High-Z state during the entire write cycle.

- 8.  $\overline{\text{CMD}}$  access follows the standard  $\overline{\text{CE}}$  access described above. If  $\overline{\text{CMD}} = \text{V}_{\text{IL}}$ , then  $\overline{\text{CE}}$  must = VIH or, when  $\overline{\text{CE}} = \text{V}_{\text{IL}}$ ,  $\overline{\text{CMD}}$  must = VIH.

### SEQUENTIAL PORT: AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE<sup>(2)</sup>

|          |                                              | _    | 325X20<br>I. Only | IDT70825X25<br>Com'l. Only |      | IDT708 | 25X35 | IDT708 | 825X45 |      |

|----------|----------------------------------------------|------|-------------------|----------------------------|------|--------|-------|--------|--------|------|

| Symbol   | Parameter                                    | Min. | Max.              | Min.                       | Max. | Min.   | Max.  | Min.   | Max.   | Unit |

| READ CYC | CLE                                          |      |                   |                            |      | _      |       |        |        |      |

| tCYC     | Sequential Clock Cycle Time                  | 25   | —                 | 30                         | —    | 40     | —     | 50     | —      | ns   |

| tCH      | Clock Pulse High                             | 10   | —                 | 12                         | —    | 15     | —     | 18     | —      | ns   |

| tCL      | Clock Pulse Low                              | 10   |                   | 12                         | —    | 15     | —     | 18     | —      | ns   |

| tES      | Count Enable and Address Pointer Set-up Time | 5    | —                 | 5                          | —    | 6      | —     | 6      | —      | ns   |

| tEH      | Count Enable and Address Pointer Hold Time   | 2    | _                 | 2                          | —    | 2      | —     | 2      | —      | ns   |

| tSOE     | Output Enable to Data Valid                  | _    | 8                 | —                          | 10   | _      | 15    |        | 20     | ns   |

| tOLZ     | Output Enable Low-Z Time <sup>(1)</sup>      | 2    | _                 | 2                          | —    | 2      | —     | 2      | —      | ns   |

| tOHZ     | Output Enable High-Z Time <sup>(1)</sup>     | —    | 9                 | —                          | 11   | —      | 15    | —      | 15     | ns   |

| tCD      | Clock to Valid Data                          | _    | 20                | —                          | 25   | _      | 35    |        | 45     | ns   |

| tCKHZ    | Clock High-Z Time <sup>(1)</sup>             | —    | 12                | _                          | 14   |        | 17    | _      | 20     | ns   |

| tCKLZ    | Clock Low-Z Time <sup>(1)</sup>              | 3    | _                 | 3                          | —    | 3      | —     | 3      | —      | ns   |

| tEB      | Clock to EOB                                 | —    | 13                | —                          | 15   | —      | 18    | —      | 23     | ns   |

NOTES:

1. Transition measured at ±200mV from steady state. This parameter is guaranteed with the AC Test Load (Figure 2) by device characterization, but is not production tested.

2. "X" in part numbers indicates power rating (S or L).

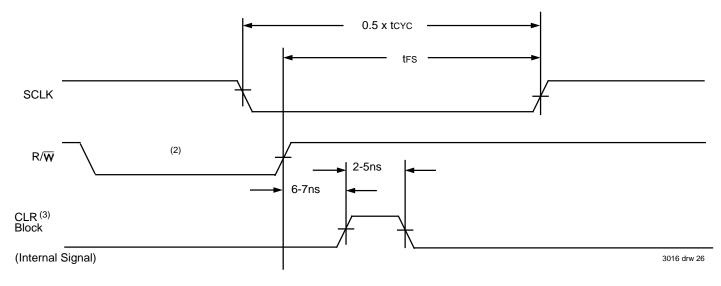

### SEQUENTIAL PORT: AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE<sup>(1)</sup>

|          |                                        | IDT70825X20<br>Com'l. Only |      | IDT70825X25<br>Com'l. Only |      | IDT70825X35 |      | IDT70825X45 |      |      |

|----------|----------------------------------------|----------------------------|------|----------------------------|------|-------------|------|-------------|------|------|

| Symbol   | Parameter                              | Min.                       | Max. | Min.                       | Max. | Min.        | Max. | Min.        | Max. | Unit |

| WRITE CY | /CLE                                   |                            |      |                            |      |             |      |             |      |      |

| tCYC     | Sequential Clock Cycle Time            | 25                         | _    | 30                         |      | 40          |      | 50          | _    | ns   |

| tFS      | Flow Restart Time                      | 13                         |      | 15                         |      | 20          |      | 20          | _    | ns   |

| tWS      | Chip Select and Read/Write Set-up Time | 5                          | _    | 5                          |      | 6           | -    | 6           |      | ns   |

| tWH      | Chip Select and Read/Write Hold Time   | 2                          | _    | 2                          | _    | 2           | _    | 2           |      | ns   |

| tDS      | Input Data Set-up Time                 | 5                          |      | 5                          |      | 6           |      | 6           | _    | ns   |

| tDH      | Input Data Hold Time                   | 2                          |      | 2                          | _    | 2           | _    | 2           |      | ns   |

NOTE:

1. "X" in part numbers indicates power rating (S or L).

3016 tbl 23

3016 tbl 22

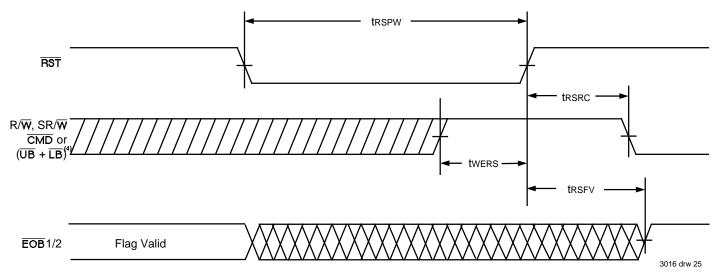

# SEQUENTIAL PORT: AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE<sup>(1)</sup>

|             |                                 | IDT70825X20 IDT70825X25<br>Com'l. Only Com'l. Only |      | IDT70825X35 |      | IDT70825X45 |      |      |      |      |

|-------------|---------------------------------|----------------------------------------------------|------|-------------|------|-------------|------|------|------|------|

| Symbol      | Parameter                       | Min.                                               | Max. | Min.        | Max. | Min.        | Max. | Min. | Max. | Unit |

| RESET CYCLE |                                 |                                                    |      |             |      |             |      |      |      |      |

| tRSPW       | Reset Pulse Width               | 13                                                 |      | 15          | —    | 20          | —    | 20   | —    | ns   |

| tWERS       | Write Enable High to Reset High | 10                                                 | _    | 10          | —    | 10          | —    | 10   | —    | ns   |

| tRSRC       | Reset High to Write Enable Low  | 10                                                 | _    | 10          | —    | 10          | —    | 10   | —    | ns   |

| tRSFV       | Reset High to Flag Valid        | 15                                                 | —    | 20          | —    | 25          | —    | 25   | —    | ns   |

NOTE:

1. "X" in part numbers indicates power rating (S or L).

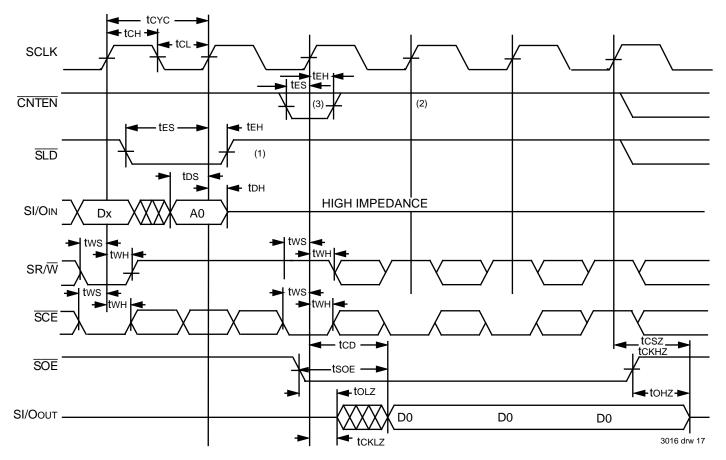

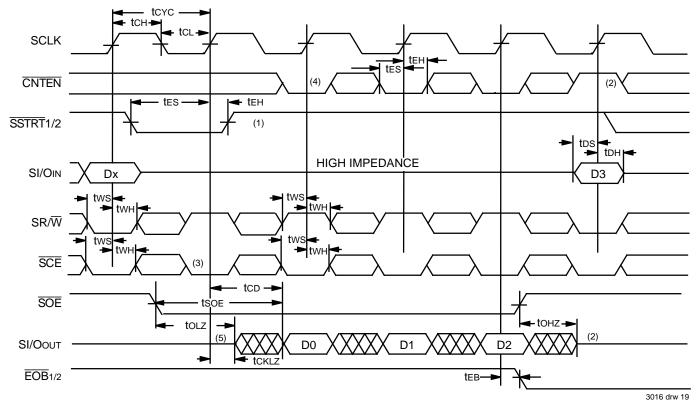

### SEQUENTIAL PORT WAVEFORM: WRITE, POINTER LOAD, NON-INCREMENTING READ

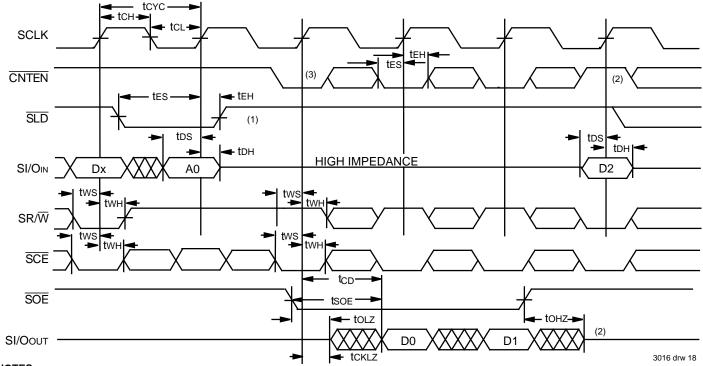

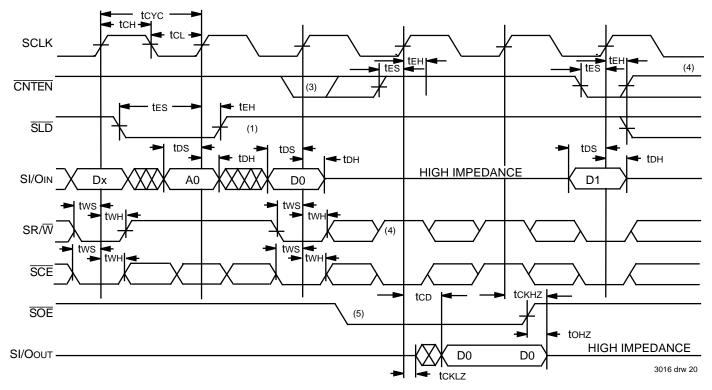

## SEQUENTIAL PORT WAVEFORM: WRITE, POINTER LOAD, BURST READ

- 1. If  $\overline{SLD} = V_{IL}$ , then address will be clocked in on the SCLK's rising edge.

- 2. If CNTEN = VIH for the SCLK's rising edge, the internal address counter will not advance.

- 3. Pointer is not incremented on cycle immediately following SLD even if CNTEN is LOW.

### SEQUENTIAL PORT WAVEFORM: READ STRT/EOB FLAG TIMING

- 1. If  $\overline{\text{SSTRT}_1}$  or  $\overline{\text{SSTRT}_2} = \text{VIL}$ , then address will be clocked in on the SCLK's rising edge.

- 2. If CNTEN = VIH for the SCLK's rising edge, the internal address counter will not advance.

- 3. SOE will control the output and should be High on Power-Up. If SCE = VIL and is clocked in while SR/W = VIH, the data addressed will be read out within that cycle. If SCE = VIL and is clocked in while SR/W = VIL, the data addressed will be written to if the last cycle was a Read. SOE may be used to control the bus contention and permit a Write on this cycle.

- 4. Unlike SLD case, CNTEN is not disabled on cycle immediately following SSTRT.

- 5. If SR/W = VIL, data would be written to D0 again since  $\overline{CNTEN} = VIH$ .

- 6. SOE = VIL makes no difference at this point since the SR/W = VIL disables the output until SR/W = VIH is clocked in on the next rising clock edge.

### **SEQUENTIAL PORT WAVEFORM: WRITE CYCLES**

### **SEQUENTIAL PORT WAVEFORM: BURST WRITE CYCLES**

- 1. If  $\overline{SLD} = V_{IL}$ , then address will be clocked in on the SCLK's rising edge.

- 2. If CNTEN = VIH for the SCLK's rising edge, the internal address counter will not advance.

- 3. Pointer is not incrementing on cycle immediately following <u>SLD</u> even if <u>CNTEN</u> is Low.

- 4. If SR/ $\overline{W}$  = VIL, data would be written to D0 again since  $\overline{CNTEN}$  = VIH.

- 5.  $\overline{\text{SOE}} = \text{VIL}$  makes no difference at this point since the SR/W = VIL disables the output until SR/W = VIH is clocked in on the next rising clock edge.

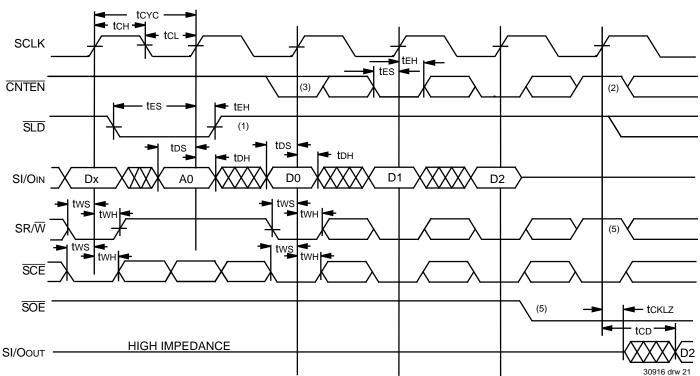

### SEQUENTIAL PORT WAVEFORM: WRITE CYCLES (STRT/EOB FLAG TIMING)

3016 drw 22

- 1. If  $\overline{\text{SSTRT}_1}$  or  $\overline{\text{SSTRT}_2} = \text{VIL}$ , then address will be clocked in on the SCLK's rising edge.

- 2. If CNTEN = VIH for the SCLK's rising edge, the internal address counter will not advance.

- 3. SOE will control the output and should be High on Power-Up. If SCE = VIL and is clocked in while SR/W = VIH, the data addressed will be read out within that cycle. If SCE = VIL and is clocked in while SR/W = VIL, the data addressed will be written to if the last cycle was a Read. SOE may be used to control the bus contention and permit a Write on this cycle.

- 4. Unlike SLD case, CNTEN is not disabled on cycle immediately following SSTRT.

- 5. If SR/ $\overline{W}$  = VIL, data would be written to D0 again since  $\overline{CNTEN}$  = VIH.

- 6. SOE = VIL makes no difference at this point since the SRW = VIL disables the output until SRW = VIH is clocked in on the next rising clock edge.

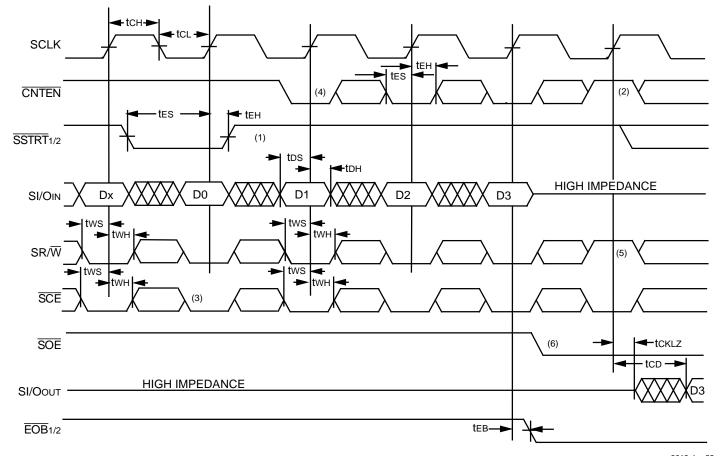

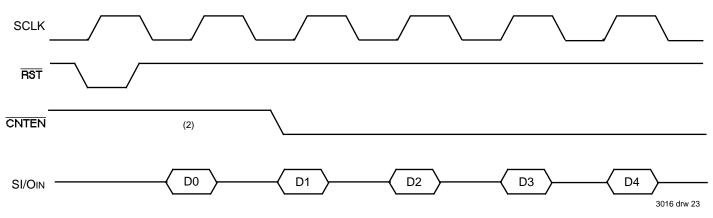

# SEQUENTIAL COUNTER ENABLE CYCLE AFTER RESET, WRITE CYCLE<sup>(2, 4, 6)</sup>

# SEQUENTIAL COUNTER ENABLE CYCLE AFTER RESET, READ CYCLE<sup>(2, 4)</sup>

| SCLK    |                                           |

|---------|-------------------------------------------|

| RST     |                                           |

| SR/₩    |                                           |

|         | (5)                                       |

| SI/Oout | D0 <sup>(5)</sup> D1 D2 D3 D3 3016 drw 24 |

- 1. 'D0' represents data input for Address=0, 'D1' represents data input for Address=1, etc.

- 1. If CNTEN=VIL then 'D1' would be written into 'A1' at this point.

- 3. Data output is available at a tcD after the SR/W=VIH is clocked. The RST sets SR/W=Low internally and therefore disables the output until the next clock.

- 4. SCE=VIL throughout all cycles.

- 5. If CNTEN=VIL then 'D1' would be clocked out (read) at this point.

- 6. SR/ $\overline{W}$ =VIL.

## RANDOM ACCESS PORT WAVEFORM: RESET TIMING

## RANDOM ACCESS PORT WAVEFORM: RESTART TIMING OF SEQUENTIAL PORT <sup>(1)</sup>

- 1. The sequential port is in the STOP mode and is being restarted from the random port by the Bit 4 Counter Release (see Case 5).

- 2. "0" is written to Bit 4 from the random port at address [A2 A0] = 100, when  $\overline{CMD}$  = VIL and  $\overline{CE}$  = VIH. The device is in the Buffer Command Mode (see Case 5).

- 3. CLR is an internal signal only and is shown for reference only.

- 4. Sequential port must also prohibit SR/W or SCE from being low for twers and trsrc periods, or SCLK must not toggle from Low-to-High until after trsrc.

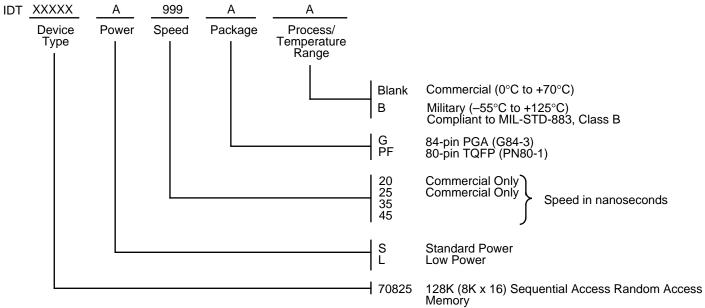

### **ORDERING INFORMATION**

3016 drw 27