innov**ASIC**

### **FEATURES**

- Form, Fit, and Function Compatible with the Intel<sup>a</sup> 8044/8344

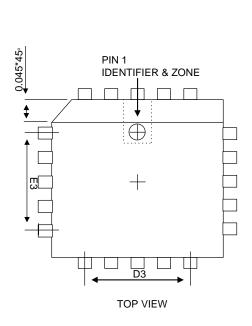

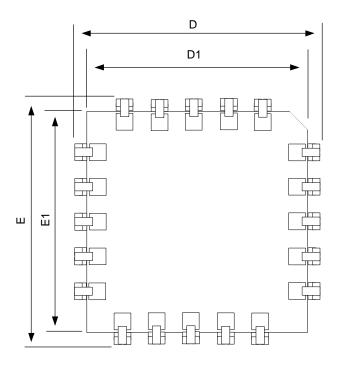

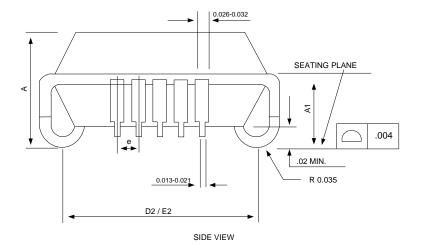

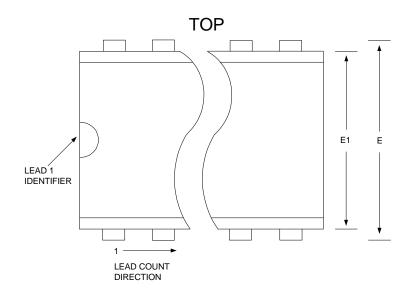

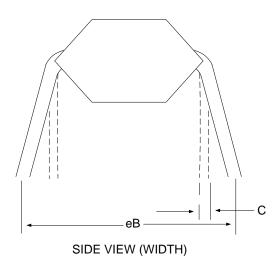

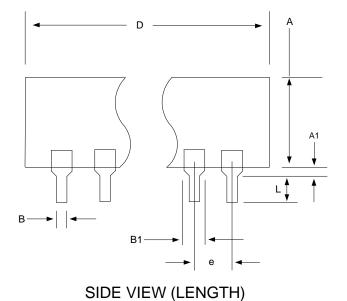

- Packaging options available: 40 Pin Plastic Dual In-Line Package (PDIP),

44 Pin Plastic Leaded Chip Carrier (PLCC)

- 8-Bit Control Unit

- 8-Bit Arithmetic-Logic Unit with 16-Bit multiplication and division

- 12 MHz clock

- Four 8-Bit Input / Output ports

- Two 16-Bit Timer/Counters

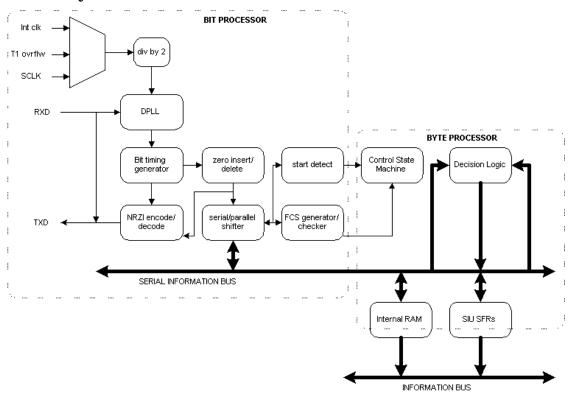

- Serial Interface Unit with SDLC/HDLC compatibility

- 2.4 Mbps maximum serial data rate

- Two Level Priority Interrupt System

- 5 Interrupt Sources

- Internal Clock prescaler and Phase generator

- 192 Bytes of Read/Write Data Memory Space

- 64kB External Program Memory Space

- 64kB External Data Memory Space

- 4kB Internal ROM (IA8044 only)

#### IA8044/IA8344 Variants

| IA8044 | 4kB internal ROM with R0117 version 2.3 firmware, 192 byte internal RAM, 64kB external program and data space. |

|--------|----------------------------------------------------------------------------------------------------------------|

| IA8344 | 192 byte internal RAM, 64kB external program and data space.                                                   |

The IA8044/IA8344 is a "plug-and-play" drop-in replacement for the original IC. InnovASIC produces replacement ICs using its MILES<sup>TM</sup>, or Managed IC Lifetime Extension System, cloning technology. This technology produces replacement ICs far more complex than "emulation" while ensuring they are compatible with the original IC. MILES<sup>TM</sup> captures the design of a clone so it can be produced even as silicon technology advances. MILES<sup>TM</sup> also verifies the clone against the original IC so that even the "undocumented features" are duplicated. This data sheet documents all necessary engineering information about the IA8044/IA8344 including functional and I/O descriptions, electrical characteristics, and applicable timing.

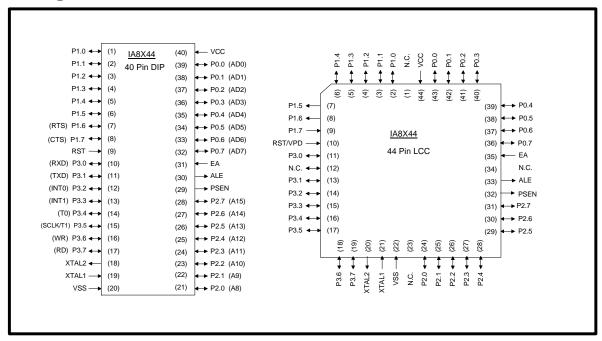

# **Package Pinout**

### DESCRIPTION

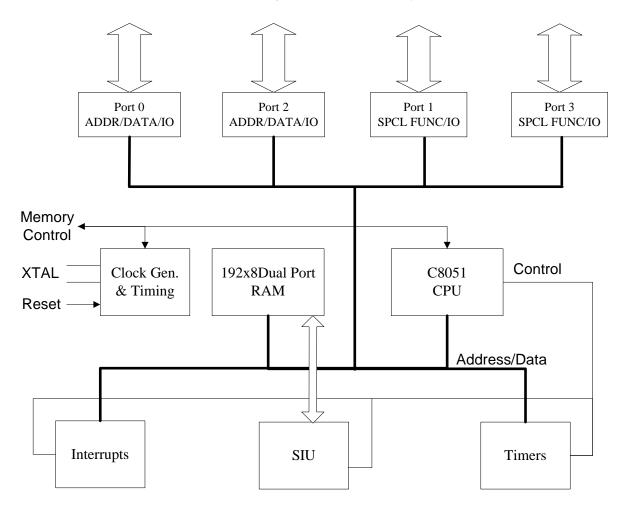

The IA8044/IA8344 is a form, fit and function compatible part to the Intel® 8X44 SDLC communications controller. The IA8044/IA8344 is a Fast Single-Chip 8-Bit Microcontroller with an integrated SDLC/HDLC serial interface controller. The IA8044/IA8344 is a fully functional 8-Bit Embedded Controller that executes all ASM51 instructions and has the same instruction set as the Intel 80C51. The IA8044/IA8344 can access the instructions from two types of program memory, serves software and hardware interrupts, provides an interface for serial communications and a timer system. The IA8044/IA8344 is fully compatible with the Intel® 8X44 series. The functional block diagram is shown below.

# **Functional Block Diagram**

I/O for Memory, SIU, DMA, Interrupts, Timers

# I/O Characteristics

The table below describes the I/O characteristics for each signal on the IC. The signal names correspond to the signal names on the pinout diagrams provided. The table below provides the I/O description of the IA8044 and the IA8344.

| Name        | Туре | Description                                                         |

|-------------|------|---------------------------------------------------------------------|

| RST         | I    | Reset. This pin when held high for two machine cycles while         |

|             |      | the oscillator is running will cause the chip to reset.             |

| ALE         | 0    | Address Latch Enable. Used to latch the address on the falling      |

|             |      | edge for external memory accesses.                                  |

| PSEN        | 0    | Program Store Enable. When low acts as an output enable for         |

|             |      | external program memory.                                            |

| EA          | I    | External Access. When held low EA will cause the                    |

|             |      | IA8044/IA8344 to fetch instructions from external memory.           |

| P0.7 – P0.0 | I/O  | Port 0. 8 bit I/O port and low order multiplexed address/data       |

|             |      | byte for external accesses.                                         |

| P1.7 – P1.0 | I/O  | Port 1. 8-bit I/O port. Two bits have alternate functions, P1.6     |

|             |      | (RTS) and P1.7 (CTS).                                               |

| P2.7 – P2.0 | I/O  | Port 2. 8-bit I/O port. It also functions as the high order         |

|             |      | address byte during external accesses.                              |

| P3.7 – P3.0 | I/O  | Port 3. 8-bit I/O port. Port 3 bits also have alternate functions   |

|             |      | as described below.                                                 |

|             |      | P3.0 – RXD. Receive data input for SIU or direction control         |

|             |      | for P3.1 dependent upon datalink configuration.                     |

|             |      | P3.1 – TXD. Transmit data output for SIU or data                    |

|             |      | input/output dependent upon datalink configuration. Also            |

|             |      | enables diagnostic mode when cleared.                               |

|             |      | P3.2 – INT0. Interrupt 0 input or gate control input for counter    |

|             |      | 0. D2 2 INIT1 Interment 1 input or gets control input for country.  |

|             |      | P3.3 – INT1. Interrupt 1 input or gate control input for counter 1. |

|             |      | P3.4 – T0. Input to counter 0.                                      |

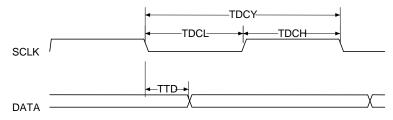

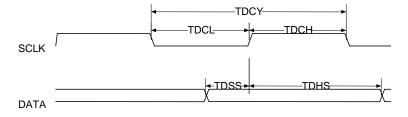

|             |      | P3.5 – SCLK/T1. SCLK input to SIU or input to counter 1.            |

|             |      | P3.6 – WR. External memory write signal.                            |

|             |      | P3.7 – RD. External memory read signal.                             |

| XTAL1       | I    | Crystal Input 1. Connect to VSS when external clock is used on      |

|             |      | XTAL2. May be connected to a crystal (with XTAL2), or may           |

|             |      | be driven directly with a clock source (XTAL2 not connected).       |

| XTAL2       | O    | Crystal Input 2. May be connected to a crystal (with XTAL1),        |

|             |      | or may be driven directly with an inverted clock source (XTAL1      |

|             |      | tied to ground).                                                    |

| VSS         | P    | Ground.                                                             |

| VCC         | P    | +5V power.                                                          |

# **Memory Organization**

### **Program Memory**

Program Memory includes interrupt and Reset vectors. The interrupt vectors are spaced at 8-byte intervals, starting from 0003H for External Interrupt 0.

#### **Reset Vectors**

| Location | Service              |

|----------|----------------------|

| 0003H    | External Interrupt 0 |

| 000BH    | Timer 0 overflow     |

| 0013H    | External Interrupt 1 |

| 001BH    | Timer 1 overflow     |

| 0023H    | SIU Interrupt        |

These locations may be used for program code, if the corresponding interrupts are not used (disabled). The Program Memory space is 64K, from 0000H to FFFFH. The lowest 4K of program code (0000H to 0FFFH) can be fetched from external or internal Program Memory. This selection is made by strapping pin 'EA' (External Address) to GND or VCC. If during reset, 'EA' is held low, all the program code is fetched from external memory. If, during reset, 'EA' is held high, the lowest 4K of program code (0000H to 0FFFH) is fetched from internal memory (ROM). Program memory addresses above 4K (0FFFH) will cause the program code to be fetched from external memory regardless of the setting of 'EA'.

# **Data Memory**

# **External Data Memory**

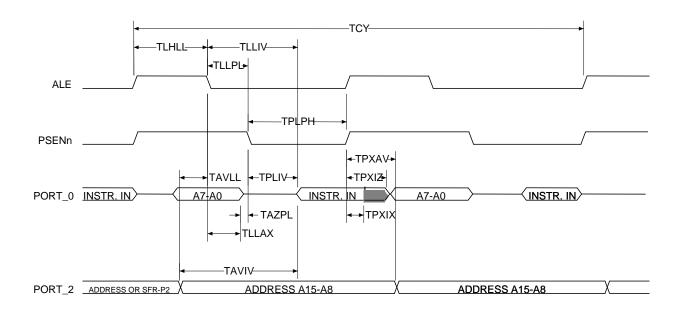

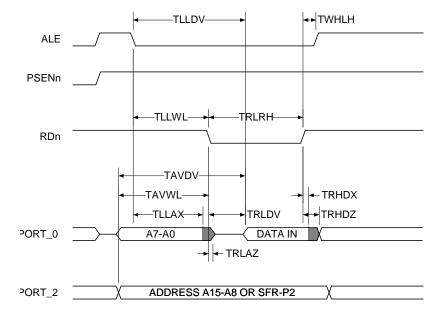

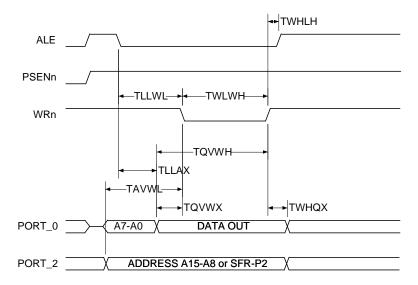

The IA8044/IA8344 Microcontroller core incorporates the Harvard architecture, with separate code and data spaces. The code from external memory is fetched by 'psen' strobe, while data is read from RAM by bit 7 of P3 (read strobe) and written to RAM by bit 6 of P3 (write strobe). The External Data Memory space is active only by addressing through use of the MOVX instruction and the 16-bit Data Pointer Register (DPTR). A smaller subset of external data memory (8 bit addressing) may be accessed by using the MOVX instruction with register indexed addressing.

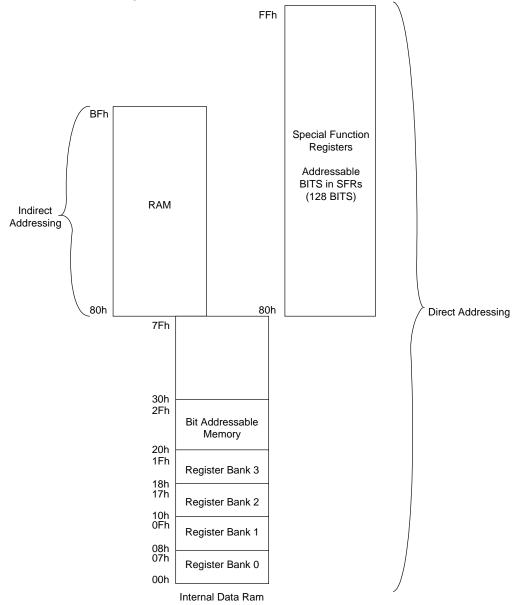

# **Internal Data Memory**

The Internal Data Memory address is always 1 byte wide. The memory space is 192 bytes large (00H to BFH), and can be accessed by either direct or indirect addressing. The Special Function Registers occupy the upper 128 bytes. This SFR area is available only by direct addressing. Internal memory that overlaps the SFR address space is only accessible by indirect addressing.

# **Internal Memory**

### **Bit Addressable Memory**

Both the internal RAM and the Special Function Registers have locations that are bit addressable in addition to the byte addressable locations.

### **SFR Bit Addressable Locations**

| Byte Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | Register |

|--------------|-------|-------|-------|-------|-------|-------|-------|-------|----------|

| F0h          | F7h   | F6h   | F5h   | F4h   | F3h   | F2h   | F1h   | F0h   | В        |

| E0h          | E7h   | E6h   | E5h   | E4h   | E3h   | E2h   | E1h   | E0h   | ACC      |

| D8h          | DFh   | DEh   | DDh   | DCh   | DBh   | DAh   | D9h   | D8h   | NSNR     |

| D0h          | D7h   | D6h   | D5h   | D4h   | D3h   | D2h   | D1h   | D0h   | PSW      |

| C8h          | CFh   | CEh   | CDh   | CCh   | CBh   | CAh   | C9h   | C8h   | STS      |

| B8h          | -     | -     | -     | BCh   | BBh   | BAh   | B9h   | B8h   | IP       |

| B0h          | B7h   | B6h   | B5h   | B4h   | B3h   | B2h   | B1h   | B0h   | P3       |

| A8h          | AFh   | -     | -     | ACh   | ABh   | AAh   | A9h   | A8h   | IE       |

| A0h          | A7h   | A6h   | A5h   | A4h   | A3h   | A2h   | A1h   | A0h   | P2       |

| 90h          | 97h   | 96h   | 95h   | 94h   | 93h   | 92h   | 91h   | 90h   | P1       |

| 88h          | 8Fh   | 8Eh   | 8Dh   | 8Ch   | 8Bh   | 8Ah   | 89h   | 88h   | TCON     |

| 80h          | 87h   | 86h   | 85h   | 84h   | 83h   | 82h   | 81h   | 80h   | P0       |

### **Internal RAM Bit Addressable Locations**

| Byte Address | bit 7 | bit 6 | bit 5 | bit 4      | bit 3   | bit 2  | bit 1 | bit 0 |

|--------------|-------|-------|-------|------------|---------|--------|-------|-------|

| 30h-BFh      |       |       | Upper | · Internal | Ram loc | ations |       |       |

| 2Fh          | 7Fh   | 7Eh   | 7Dh   | 7Ch        | 7Bh     | 7Ah    | 79h   | 78h   |

| 2Eh          | 77h   | 76h   | 75h   | 74h        | 73h     | 72h    | 71h   | 70h   |

| 2Dh          | 6Fh   | 6Eh   | 6Dh   | 6Ch        | 6Bh     | 6Ah    | 69h   | 68h   |

| 2Ch          | 67h   | 66h   | 65h   | 64h        | 63h     | 62h    | 61h   | 60h   |

| 2Bh          | 5Fh   | 5Eh   | 5Dh   | 5Ch        | 5Bh     | 5Ah    | 59h   | 58h   |

| 2Ah          | 57h   | 56h   | 55h   | 54h        | 53h     | 52h    | 51h   | 50h   |

| 29h          | 4Fh   | 4Eh   | 4Dh   | 4Ch        | 4Bh     | 4Ah    | 49h   | 48h   |

| 28h          | 47h   | 46h   | 45h   | 44h        | 43h     | 42h    | 41h   | 40h   |

| 27h          | 3Fh   | 3Eh   | 3Dh   | 3Ch        | 3Bh     | 3Ah    | 39h   | 38h   |

| 26h          | 37h   | 36h   | 35h   | 34h        | 33h     | 32h    | 31h   | 30h   |

| 25h          | 2Fh   | 2Eh   | 2Dh   | 2Ch        | 2Bh     | 2Ah    | 29h   | 28h   |

| 24h          | 27h   | 26h   | 25h   | 24h        | 23h     | 22h    | 21h   | 20h   |

| 23h          | 1Fh   | 1Eh   | 1Dh   | 1Ch        | 1Bh     | 1Ah    | 19h   | 18h   |

| 22h          | 17h   | 16h   | 15h   | 14h        | 13h     | 12h    | 11h   | 10h   |

| 21h          | 0Fh   | 0Eh   | 0Dh   | 0Ch        | 0Bh     | 0Ah    | 09h   | 08h   |

| 20h          | 07h   | 06h   | 05h   | 04h        | 03h     | 02h    | 01h   | 00h   |

| 18h-1Fh      |       |       |       | Register   | Bank 3  |        |       |       |

| 10h-17h      |       |       |       | Register   | Bank 2  |        |       |       |

| 08h-0Fh      |       |       |       | Register   | Bank 1  |        |       |       |

| 00h-07h      |       |       |       | Register   | Bank 0  |        |       |       |

### **Instruction Set**

The 8X44 architecture and instruction set are identical to the 8051's. The following tables give a survey of the instruction set of the IA8044/IA8344 Microcontroller core.

# **Arithmetic Operations**

| Mnemonic      | Description                                 | Byte | Cycle |

|---------------|---------------------------------------------|------|-------|

| ADD A,Rn      | Add register to accumulator                 | 1    | 1     |

| ADD A, direct | Add direct byte to accumulator              | 2    | 1     |

| ADD A,@Ri     | Add indirect RAM to accumulator             | 1    | 1     |

| ADD A,#data   | Add immediate data to accumulator           | 2    | 1     |

| ADDC A,Rn     | Add register to accumulator with carry flag | 1    | 1     |

| ADDC A,direct | Add direct byte to A with carry flag        | 2    | 1     |

| ADDC A,@Ri    | Add indirect RAM to A with carry flag       | 1    | 1     |

| ADDC A,#data  | Add immediate data to A with carry flag     | 2    | 1     |

| SUBB A,Rn     | Subtract register from A with borrow        | 1    | 1     |

| SUBB A,direct | Subtract direct byte from A with borrow     | 2    | 1     |

| SUBB A,@Ri    | Subtract indirect RAM from A with borrow    | 1    | 1     |

| SUBB A,#data  | Subtract immediate data from A with borrow  | 2    | 1     |

| INC A         | Increment accumulator                       | 1    | 1     |

| INC Rn        | Increment register                          | 1    | 1     |

| INC direct    | Increment direct byte                       | 2    | 1     |

| INC @ Ri      | Increment indirect RAM                      | 1    | 1     |

| DEC A         | Decrement accumulator                       | 1    | 1     |

| DEC Rn        | Decrement register                          | 1    | 1     |

| DEC direct    | Decrement direct byte                       | 2    | 1     |

| DEC @Ri       | Decrement indirect RAM                      | 1    | 1     |

| INC DPTR      | Increment data pointer                      | 1    | 2     |

| MUL A,B       | Multiply A and B                            | 1    | 4     |

| DIV A,B       | Divide A by B                               | 1    | 4     |

| DA A          | Decimal adjust accumulator                  | 1    | 1     |

# **Logic Operations**

| Mnemonic         | Description                                | Byte | Cycle |

|------------------|--------------------------------------------|------|-------|

| ANL A,Rn         | AND register to accumulator                | 1    | 1     |

| ANL A,direct     | AND direct byte to accumulator             | 2    | 1     |

| ANL A,@Ri        | AND indirect RAM to accumulator            | 1    | 1     |

| ANL A,#data      | AND immediate data to accumulator          | 2    | 1     |

| ANL direct,A     | AND accumulator to direct byte             | 2    | 1     |

| ANL direct,#data | AND immediate data to direct byte          | 3    | 2     |

| ORL A,Rn         | OR register to accumulator                 | 1    | 1     |

| ORL A,direct     | OR direct byte to accumulator              | 2    | 1     |

| ORL A,@Ri        | OR indirect RAM to accumulator             | 1    | 1     |

| ORL A,#data      | OR immediate data to accumulator           | 2    | 1     |

| ORL direct,A     | OR accumulator to direct byte              | 2    | 1     |

| ORL direct,#data | OR immediate data to direct byte           | 3    | 2     |

| XRL A,Rn         | Exclusive OR register to accumulator       | 1    | 1     |

| XRL A,direct     | Exclusive OR direct byte to accumulator    | 2    | 1     |

| XRL A,@Ri        | Exclusive OR indirect RAM to accumulator   | 1    | 1     |

| XRL A,#data      | Exclusive OR immediate data to accumulator | 2    | 1     |

| XRL direct,A     | Exclusive OR accumulator to direct byte    | 2    | 1     |

| XRL direct,#data | Exclusive OR immediate data to direct byte | 3    | 2     |

| CLR A            | Clear accumulator                          | 1    | 1     |

| CPL A            | Complement accumulator                     | 1    | 1     |

| RL A             | Rotate accumulator left                    | 1    | 1     |

| RLC A            | Rotate accumulator left through carry      | 1    | 1     |

| RR A             | Rotate accumulator right                   | 1    | 1     |

| RRC A            | Rotate accumulator right through carry     | 1    | 1     |

| SWAP A           | Swap nibbles within the accumulator        | 1    | 1     |

# **Data Transfer**

| Mnemonic           | Description                                    | Byte | Cycle |

|--------------------|------------------------------------------------|------|-------|

| MOV A,Rn           | Move register to accumulator                   | 1    | 1     |

| MOV A,direct       | Move direct byte to accumulator                | 2    | 1     |

| MOV A,@Ri          | Move indirect RAM to accumulator               | 1    | 1     |

| MOV A,#data        | Move immediate data to accumulator             | 2    | 1     |

| MOV Rn,A           | Move accumulator to register                   | 1    | 1     |

| MOV Rn,direct      | Move direct byte to register                   | 2    | 2     |

| MOV Rn,#data       | Move immediate data to register                | 2    | 1     |

| MOV direct,A       | Move accumulator to direct byte                | 2    | 1     |

| MOV direct,Rn      | Move register to direct byte                   | 2    | 2     |

| MOV direct, direct | Move direct byte to direct byte                | 3    | 2     |

| MOV direct,@Ri     | Move indirect RAM to direct byte               | 2    | 2     |

| MOV direct,#data   | Move immediate data to direct byte             | 3    | 2     |

| MOV @Ri,A          | Move accumulator to indirect RAM               | 1    | 1     |

| MOV @Ri,direct     | Move direct byte to indirect RAM               | 2    | 2     |

| MOV @ Ri, #data    | Move immediate data to indirect RAM            | 2    | 1     |

| MOV DPTR, #data16  | Load data pointer with a 16-bit constant       | 3    | 2     |

| MOVC A,@A + DPTR   | Move code byte relative to DPTR to accumulator | 1    | 2     |

| MOVC A,@A + PC     | Move code byte relative to PC to accumulator   | 1    | 2     |

| MOVX A,@Ri         | Move external RAM (8-bit addr.) to A           | 1    | 2     |

| MOVX A,@DPTR       | Move external RAM (16-bit addr.) to A          | 1    | 2     |

| MOVX @Ri,A         | Move A to external RAM (8-bit addr.)           | 1    | 2     |

| MOVX @DPTR,A       | Move A to external RAM (16-bit addr.)          | 1    | 2     |

| PUSH direct        | Push direct byte onto stack                    | 2    | 2     |

| POP direct         | Pop direct byte from stack                     | 2    | 2     |

| XCH A,Rn           | Exchange register with accumulator             | 1    | 1     |

| XCH A,direct       | Exchange direct byte with accumulator          | 2    | 1     |

| XCH A,@Ri          | Exchange indirect RAM with accumulator         | 1    | 1     |

| XCHD X,@ Ri        | Exchange low-order nibble indir. RAM with A    | 1    | 1     |

# **Boolean Manipulation**

| Mnemonic  | Description                           | Byte | Cycle |

|-----------|---------------------------------------|------|-------|

|           |                                       |      |       |

| CLR C     | Clear carry flag                      | 1    | 1     |

| CLR bit   | Clear direct bit                      | 2    | 1     |

| SETB C    | Set carry flag                        | 1    | 1     |

| SETB bit  | Set direct bit                        | 2    | 1     |

| CPL C     | Complement carry flag                 | 1    | 1     |

| CPL bit   | Complement direct bit                 | 2    | 1     |

| ANL C,bit | AND direct bit to carry flag          | 2    | 2     |

| ANL C,bit | AND complement of direct bit to carry | 2    | 2     |

| ORL C,bit | OR direct bit to carry flag           | 2    | 2     |

| ORL C,bit | OR complement of direct bit to carry  | 2    | 2     |

| MOV C,bit | Move direct bit to carry flag         | 2    | 1     |

| MOV bit,C | Move carry flag to direct bit         | 2    | 2     |

# **Program Branches**

| Mnemonic           | Description                                    | Byte | Cycle |

|--------------------|------------------------------------------------|------|-------|

| ACALL addr11       | Absolute subroutine call                       | 2    | 2     |

| LCALL addr16       | Long subroutine call                           | 3    | 2     |

| RET Return         | from subroutine                                | 1    | 2     |

| RETI Return        | from interrupt                                 | 1    | 2     |

| AJMP addr11        | Absolute jump                                  | 2    | 2     |

| LJMP addr16        | Long jump                                      | 3    | 2     |

| SJMP rel           | Short jump (relative addr.)                    | 2    | 2     |

| JMP @A + DPTR      | Jump indirect relative to the DPTR             | 1    | 2     |

| JZ rel             | Jump if accumulator is zero                    | 2    | 2     |

| JNZ rel            | Jump if accumulator is not zero                | 2    | 2     |

| JC rel             | Jump if carry flag is set                      | 2    | 2     |

| JNC rel            | Jump if carry flag is not set                  | 2    | 2     |

| JB bit,rel         | Jump if direct bit is set                      | 3    | 2     |

| JNB bit,rel        | Jump if direct bit is not set                  | 3    | 2     |

| JBC bit,rel        | Jump if direct bit is set and clear bit        | 3    | 2     |

| CJNE A,direct,rel  | Compare direct byte to A and jump if not equal | 3    | 2     |

| CJNE A,#data,rel   | Compare immediate to A and jump if not equal   | 3    | 2     |

| CJNE Rn,#data rel  | Compare immed. to reg. and jump if not equal   | 3    | 2     |

| CJNE @Ri,#data,rel | Compare immed. to ind. and jump if not equal   | 3    | 2     |

| DJNZ Rn,rel        | Decrement register and jump if not zero        | 2    | 2     |

| DJNZ direct,rel    | Decrement direct byte and jump if not zero     | 3    | 2     |

| NOP                | No operation                                   | 1    | 1     |

# **Special Function Registers**

The IA8044/IA8344 contains the following special function registers:

| Symbol  | Register Description          | Byte         | Bit Addresses (Hex) |

|---------|-------------------------------|--------------|---------------------|

|         |                               | Address(Hex) | (MSB - LSB)         |

| ACC     | Accumulator                   | E0h          | E7h – E0h           |

| В       | B register                    | F0h          | F7h – F0h           |

| PSW     | Program Status Word           | D0h          | D7h - D0h           |

| SP      | Stack Pointer                 | 81h          | -                   |

| DPH     | Data Pointer High Byte        | 82h          | -                   |

| DPL     | Data Pointer Low Byte         | 83h          | -                   |

| P0      | Port 0                        | 80h          | 87h – 80h           |

| P1      | Port 1                        | 90h          | 97h – 90h           |

| P2      | Port 2                        | A0h          | A7h – A0h           |

| P3      | Port 3                        | B0h          | B7h – B0h           |

| IP      | Interrupt Priority            | B8h          | BCh – B8h           |

| IE      | Interrupt Enable              | A8h          | AFh,ACh – A8h       |

| TMOD    | Timer/Counter Mode            | 89h          | -                   |

| TCON    | Timer/Counter Control         | 88h          | 8Fh – 88h           |

| TH0     | Timer/Counter 0 high byte     | 8Ch          | -                   |

| TL0     | Timer/Counter 0 low byte      | 8Ah          | -                   |

| TH1     | Timer/Counter 1 high byte     | 8Dh          | -                   |

| TL1     | Timer/Counter 1 low byte      | 8Bh          | -                   |

| SMD     | Serial Mode                   | C9h          | -                   |

| STS     | SIU Status and Command        | C8h          | CFh – C8h           |

| NSNR    | SIU Send/Receive Count        | D8h          | DFh – D8h           |

| STAD    | SIU Station Address           | CEh          | -                   |

| TBS     | Transmit Buffer Start Address | DCh          | -                   |

| TBL     | Transmit Buffer Length        | DBh          | -                   |

| TCB     | Transmit Control Byte         | DAh          | -                   |

| RBS     | Receive Buffer Start Address  | CCh          | -                   |

| RBL     | Receive Buffer Length         | CBh          | -                   |

| RFL     | Receive Field Length          | CDh          | -                   |

| RCB     | Receive Control Byte          | CAh          | -                   |

| DMA CNT | DMA Count                     | CFh          | -                   |

| FIFO    | FIFO contents (3 bytes)       | DF,DE,DDh    | -                   |

| SIUST   | SIU State Counter             | D9h          | -                   |

#### **Ports**

Ports P0, P1, P2 and P3 are Special Function Registers. The contents of the SFR can be observed on corresponding pins on the chip. Writing a '1' to any of the ports causes the corresponding pin to be at high level (VCC), and writing a '0' causes the corresponding pin to be held at low level (GND).

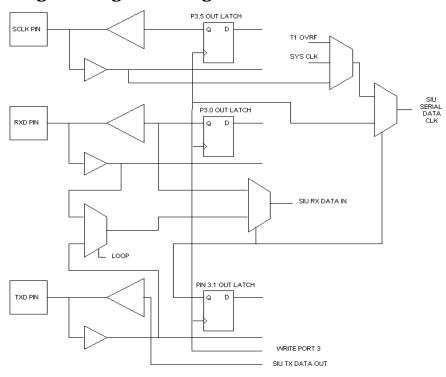

All four ports on the chip are bi-directional. Each of them consists of a Latch (SFR P0 to P3), an output driver, and an input buffer, so the CPU can output or read data through any of these ports if they are not used for alternate purposes.

Ports P0, P1, P2 and P3 can perform some alternate functions. Ports P0 and P2 are used to access external memory. In this case, port 'p0' outputs the multiplexed lower 8 bits of address with 'ale' strobe high and then reads/writes 8 bits of data. Port P2 outputs the higher 8 bits of address. Keeping 'ea' pin low (tied to GND) activates this alternate function for ports P0 and P2.

Port P3 and P1 can perform some alternate functions. The pins of Port P3 are multifunctional. They can perform additional functions as described below.

| <b>Pin</b> P3.0 | <b>Symbol</b><br>RxD, I/O | <b>Function</b> In point-to-point or multipoint configurations (SMD.3 = 0) this pin is I/O and signals the direction of data flow on DATA (P3.1). In loop mode (SMD.3 = 1) and diagnostic mode this pin is RxD, Receive Data input.                       |

|-----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.1            | TxD, DATA                 | In point to point or multipoint configurations (SMD.3 = 0) this pin is DATA and is the transmit/receive data pin. In loop mode (SMD.3 = 1) this pin is the transmit data, $TxD$ , pin. Writing a '0' to this port buffer bit enables the diagnostic mode. |

| P3.2            | INT0                      | External interrupt 0 input. Also gate control input for counter 0.                                                                                                                                                                                        |

| P3.3            | INT1                      | External interrupt 1 input. Also gate control input for counter 1.                                                                                                                                                                                        |

| P3.4            | T0                        | Timer/Counter 0 external input. Setting the appropriate bits in the Special Function Registers TCON and TMOD activates this function.                                                                                                                     |

| P3.5            | T1, SCLK                  | Timer/Counter 1 external input. Setting the appropriate bits in the Special Function Registers TCON and TMOD activates this function Can also function as the external clock source for the SIU.                                                          |

| P3.6            | WR                        | External Data Memory write strobe, active LOW. This function is activated by a CPU write access to External Data Memory (i.e. MOVX @DPTR, A).                                                                                                             |

Page 13 of 49

P3.7 RD External Data Memory read strobe, active LOW. This function is

activated by a CPU read access from External Data Memory (i.e. MOVX

A, @DPTR).

P1.6 RTS Request To Send output, active low.

P1.7 CTS Clear To Send input, active low.

# **Port Registers**

# Port 0 (P0):

General purpose, 8 bit, I/O port and multiplexed low order address and data bus with open-drain output buffers.

| P0     |      |      |      |      |      |      |      |

|--------|------|------|------|------|------|------|------|

| Bit: 7 | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| P0.7   | P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0 |

### Port 1 (P1):

General purpose, 8 bit, I/O port with pullups and auxiliary functions.

| P1       |          |              |            |      |      |      |      |

|----------|----------|--------------|------------|------|------|------|------|

| Bit: 7   | 6        | 5            | 4          | 3    | 2    | 1    | 0    |

| RTS/P1.7 | CTS/P1.6 | P1.5         | P1.4       | P1.3 | P1.2 | P1.1 | P1.0 |

|          |          |              |            |      |      |      |      |

| P1.0     | -        |              |            |      |      |      |      |

| P1.1     | -        |              |            |      |      |      |      |

| P1.2     | -        |              |            |      |      |      |      |

| P1.3     | -        |              |            |      |      |      |      |

| P1.4     | -        |              |            |      |      |      |      |

| P1.5     | -        |              |            |      |      |      |      |

| P1.6     | RTS      | Request To   | Send outpi | ut.  |      |      |      |

| P1.7     | CTS      | Clear To Ser | nd input.  |      |      |      |      |

#### Port 2 (P2):

General purpose, 8 bit, I/O port with pullups and high order address bus.

| P2     |      |      |      |      |      |      |      |

|--------|------|------|------|------|------|------|------|

| Bit: 7 | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| P2.7   | P2.6 | P2.5 | P2.4 | P2.3 | P2.2 | P2.1 | P2.0 |

# **Port 3 (P3):**

General purpose, 8-bit I/O port with pullups and auxiliary functions. Bits on this port also functions as the SIU data transmit/receive I/O, external interrupt inputs, timer inputs and the read and write strobes for external memory accesses.

| P3     |      |        |                   |               |                 |      |     |  |  |  |

|--------|------|--------|-------------------|---------------|-----------------|------|-----|--|--|--|

| Bit: 7 | 6    | 5      | 4                 | 3             | 2               | 1    | 0   |  |  |  |

| RD     | WR   | T1     | T0                | INT1          | INT0            | TxD  | RxD |  |  |  |

| •      |      |        |                   |               |                 |      | _   |  |  |  |

| P3.0   | RxD  | Serial | Serial input pin. |               |                 |      |     |  |  |  |

| P3.1   | TxD  | Serial | output pin.       |               |                 |      |     |  |  |  |

| P3.2   | INT0 | Exter  | nal interrupt     | t <b>0</b> .  |                 |      |     |  |  |  |

| P3.3   | INT1 | Exter  | nal interrupt     | t <b>1</b> .  |                 |      |     |  |  |  |

| P3.4   | T0   | Time   | r/Counter 0       | external inp  | ut.             |      |     |  |  |  |

| P3.5   | T1   | Time   | r/Counter 1       | external inp  | ut.             |      |     |  |  |  |

| P3.6   | WR   | Exter  | nal Data Me       | emory write s | strobe, active  | LOW. |     |  |  |  |

| P3.7   | RD   | Exter  | nal Data Me       | emory read st | trobe, active 1 | LOW. |     |  |  |  |

1-888-824-4184

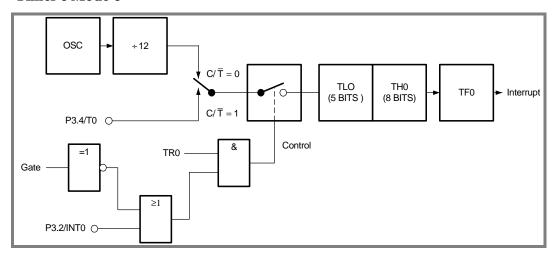

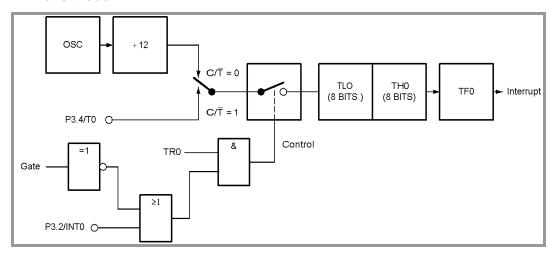

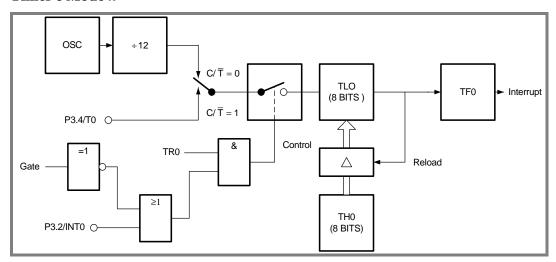

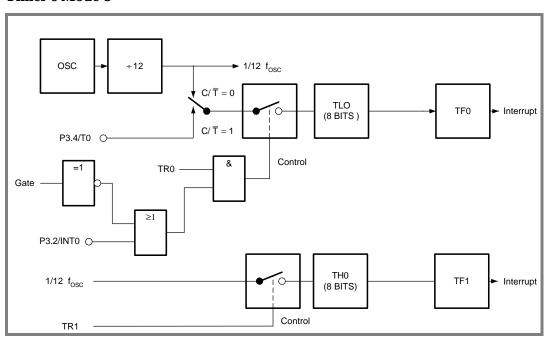

### **Timers/Counters**

#### Timers 0 and 1

The IA8X44 has two 16-bit timer/counter registers: Timer 0 and Timer 1. Both can be configured for counter or timer operations. In timer mode, the register is incremented every machine cycle, which means that it counts up after every 12 oscillator periods. In counter mode, the register is incremented when the falling edge is observed at the corresponding input pin T0 or T1. Since it takes 2 machine cycles to recognize a 1-to-0 event, the maximum input count rate is 1/24 of the oscillator frequency. There are no restrictions on the duty cycle, however to ensure proper recognition of 0 or 1 state, an input should be stable for at least 1 machine cycle (12 clock periods).

Four operating modes can be selected for Timer 0 and Timer 1. Two Special Function Registers (TMOD and TCON) are used to select the appropriate mode.

#### Mode 0

In mode 0 the timers operate as an 8-bit timer (TH0/1) with a divide by 32 bit prescalar (TL0/1). Mode 0 uses all 8 bits of TH0/1 and the lower 5 bits of TL0/1. The upper 3 bits of TL0/1 are unknowns. Setting TR0/1 does not reset the registers TH0/1 and TL0/1. As the timer rolls over from all 1's to all 0's it will set the interrupt flag TF0/1.

#### Mode 1

Mode 1 is the same as mode 0 except that all 8 bits of TL0/1 are used instead of just the lower 5 bits.

#### Mode 2

Mode 2 configures TL0/1 as an 8-bit counter with automatic reload from the contents of TH0/1. Overflow of TL0/1 causes the interrupt TF0/1 to be set and the reload to occur. The contents of TH0/1 are not affected by the reload.

#### Mode 3

Mode 3 creates two separate 8 bit counters from TL0 and TH0. TL0 uses the timer 0 mode bits from TMOD, TMOD .0 through TMOD.3. TH0 is a timer only (not a counter) and uses timer 1's control bits, TR1 and TF1 for operation. Timer 1 can still be used if an interrupt is not required by switching it in and out of its own mode 3. With TMOD.4 and TMOD.5 both high timer 1 will stop and hold its count.

#### **Timer Mode (TMOD):**

\_\_The End of Obsolescenceä

The Timer Mode register contains bits that select the mode that the timers are to be operated in. The lower nibble controls timer 0 and the upper nibble controls timer 1.

| Copyright ã 2003 ENG210 innovASIC    |     |    | 0010112-00 |      |     | www.innovasic.com<br>Customer Support: |    |

|--------------------------------------|-----|----|------------|------|-----|----------------------------------------|----|

| TMOD.0 M0 Timer 0 mode selector bit. |     |    |            |      |     |                                        |    |

| GATE                                 | C/T | M1 | M0         | GATE | C/T | M1                                     | M0 |

| TMOD<br>Bit: 7                       | 6   | 5  | 4          | 3    | 2   | 1                                      | 0  |

Page 16 of 49

| TMOD.1 | M1   | Timer 0 mode selector bit.                                                                                                                                                                                     |

|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMOD.2 | C/T  | C/T Selects Timer0 or Counter0 operation. When set to 1, the Counter operation is performed, when cleared to 0, the register will function as a Timer.                                                         |

| TMOD.3 | GATE | If set, enables external gate control for counter/timer0 (pin INT0/ for Counter 0). When INT0/ is high, and TR0 bit is set (see TCON register), the counter is incremented every falling edge on T0 input pin. |

| TMOD.4 | M0   | Timer 1 mode selector bit.                                                                                                                                                                                     |

| TMOD.5 | M1   | Timer 1 mode selector bit.                                                                                                                                                                                     |

| TMOD.6 | C/T  | C/T Selects Timer1 or Counter1 operation. When set to 1, the Counter operation is performed, when cleared to 0, the register will function as a Timer.                                                         |

| TMOD.7 | GATE | If set, enables external gate control for counter/timer1 (pin INT1/ for Counter 1). When INT1/ is high, and TR1 bit is set (see TCON register), the counter is incremented every falling edge on T1 input pin  |

#### Timer Mode Select Bits

| M1 | M0 | Op | erating Mode                                                                                                                                                |

|----|----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | 13 bit timer                                                                                                                                                |

| 0  | 1  | 1  | 16 bit timer/counter                                                                                                                                        |

| 1  | 0  | 2  | 8 bit auto-reload timer/counter                                                                                                                             |

| 1  | 1  | 3  | Timer0 – TL0 is a standard 8-bit timer/counter controlled by timer 0 control bits. TH0 is an 8-bit timer function only, controlled by timer 1 control bits. |

| 1  | 1  | 3  | Timer/counter1 stopped and holds its count. Can be used to start/stop timer 1 when timer 0 is in mode 3.                                                    |

# **Timer Control (TCON):**

The Timer Control register provides control bits that start and stop the counters. It also contains bits to select the type of external interrupt desired, edge or level. Additionally TCON contains status bits showing when a timer overflows and when an interrupt edge has been detected.

| TCON<br>Bit: 7                             | 6   | 5   | 4                                                                                                                                                                     | 3          | 2   | 1   | 0                                      |  |  |

|--------------------------------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|----------------------------------------|--|--|

| TF1                                        | TR1 | TF0 | TR0                                                                                                                                                                   | IE1        | IT1 | IE0 | IT0                                    |  |  |

| TCON.0                                     | ]   | Т0  | Interrupt 0 type control bit. Selects falling edge or low level on input pin to cause interrupt.                                                                      |            |     |     |                                        |  |  |

| TCON.1                                     | ]   | E0  | Interrupt 0 edge flag. Set by hardware, when falling edge on                                                                                                          |            |     |     |                                        |  |  |

| TCON.2                                     | 1   | T1  | external pin INT1/ is observed. Cleared when interrupt is processed. Interrupt 1 type control bit. Selects falling edge or low level on input pin to cause interrupt. |            |     |     |                                        |  |  |

| Copyright <b>ã</b> 20<br><u>innov</u> ASIC | 003 |     | ENG210                                                                                                                                                                | 0010112-00 |     |     | www.innovasic.com<br>Customer Support: |  |  |

Page 17 of 49 \_\_\_\_The End of Obsolescenceä

1-888-824-4184

# IA8044/IA8344 **SDLC COMMUNICATIONS CONTROLLER**

### **Data Sheet**

| TCON.3 | IE1 | Interrupt 1 edge flag. Set by hardware, when falling edge on external pin INT1/ is observed Cleared when interrupt is processed. |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------|

| TCON.4 | TR0 | Timer 0 Run control bit. If cleared, Timer 0 stops.                                                                              |

| TCON.5 | TF0 | Timer 0 overflow flag set by hardware when Timer 0                                                                               |

|        |     | overflows. This flag should be cleared by software.                                                                              |

| TCON.6 | TR1 | Timer 1 Run control bit. If cleared, Timer 1 stops. In mode                                                                      |

|        |     | 3 this bit controls TH0.                                                                                                         |

| TCON.7 | TF1 | Timer 1 overflow flag set by hardware when Timer 1                                                                               |

|        |     | overflows. This flag should be cleared by software In mode                                                                       |

|        |     | 3 this bit is controlled by TH0.                                                                                                 |

# **Timer 0 High byte (TH0):** High order byte of timer/counter0.

TH<sub>0</sub>

| Bit: 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|

| TH0.7  | TH0.6 | TH0.5 | TH0.4 | TH0.3 | TH0.2 | TH0.1 | TH0.0 |

# Timer 0 Low byte (TL0):

Low order byte of timer/counter0.

TL0

| Bit: 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|

| TL0.7  | TL0.6 | TL0.5 | TL0.4 | TL0.3 | TL0.2 | TL0.1 | TL0.0 |

# **Timer 1 High byte (TH1):**

High order byte of timer/counter1.

TH1

| Bit: 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|--------|-------|-------|-------|-------|-------|-------|-------|--|

| TH1.7  | TH1.6 | TH1.5 | TH1.4 | TH1.3 | TH1.2 | TH1.1 | TH1.0 |  |

# **Timer 1 Low byte (TL1):**

Low order byte of timer/counter1.

TL1

| Bit: 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|

| TL1.7  | TL1.6 | TL1.5 | TL1.4 | TL1.3 | TL1.2 | TL1.1 | TL1.0 |

# **Timers/Counters Configuration**

#### Timer 0 Mode 0

#### Timer 0 Mode 1

#### Timer 0 Mode 2

#### Timer 0 Mode 3

#### Reset

A reset is accomplished by holding the RST pin high for at least two machine cycles (24 oscillator periods) while the oscillator is running. The CPU responds by generating an internal reset, which is executed during the second cycle in which RST is high.

The internal reset sequence affects all SFRs as shown below. The internal reset sequence does not affect the contents of internal RAM.

### **Reset Values**

| Register | Reset value |

|----------|-------------|

| PC       | H0000       |

| ACC      | 00000000B   |

| В        | 00000000B   |

| PSW      | 00000000B   |

| SP       | 00000111B   |

| DPTR     | H0000       |

| P0 – P3  | 11111111B   |

| IP       | XXX00000B   |

| IE       | 0XX00000B   |

| TMOD     | 00000000B   |

| TCON     | 00000000B   |

| TH0      | 00000000B   |

| TL0      | 00000000B   |

| TH1      | 00000000B   |

| TL1      | 00000000B   |

| SMD      | 00000000B   |

| STS      | 00000000B   |

| NSNR     | 00000000B   |

| STAD     | XXXXXXXXB   |

| TBS      | XXXXXXXXB   |

| TBL      | XXXXXXXXB   |

| TCB      | XXXXXXXXB   |

| RBS      | XXXXXXXXB   |

| RBL      | XXXXXXXXB   |

| RFL      | XXXXXXXXB   |

| RCB      | XXXXXXXXB   |

| DMA CNT  | 00000000B   |

| FIFO1    | 00000000B   |

| FIFO2    | 0000000B    |

| FIFO3    | 00000000B   |

| SIUST    | 00000001B   |

# General CPU Registers Accumulator (ACC):

ACC is the Accumulator register. Most instructions use the accumulator to hold the operand. The mnemonics for accumulator-specific instructions refer to accumulator as A, not ACC.

| ٨ | 1 | ٦, | $\boldsymbol{\Gamma}$ |

|---|---|----|-----------------------|

| r | 1 | 'ر | L                     |

| Bit: 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|

| ACC.7  | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |

# **B** register (B):

The B register is used during multiply and divide instructions. It can also be used as a scratch-pad register to hold temporary data.

| В      |     |     |     |     |     |     |     |

|--------|-----|-----|-----|-----|-----|-----|-----|

| Bit: 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| B.7    | B.6 | B.5 | B.4 | B.3 | B.2 | B.1 | B.0 |

# **Program Status Word (PSW):**

Contains CPU status flags, register select bits and user flags.

| _ ~    | -   |

|--------|-----|

| 1)('\1 | . / |

| P.3 VI | v   |

| 6   | 5                  | 4                                                                                 | 3                                                                                                                                                                                                     | 2                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC  | F0                 | RS1                                                                               | RS0                                                                                                                                                                                                   | OV                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P   |                    |                                                                                   |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ımber                                                                                                                                                                                                                                                                                                                                                                                                              |

| -   | User d             | efined flag.                                                                      |                                                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                     | ū                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OV  | Overfl             | ow flag.                                                                          |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RS0 |                    |                                                                                   | t control bit (                                                                                                                                                                                       | ), used to sele                                                                                                                                                                                                                                                                       | ect working                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RS1 | Registe<br>bank.   | er bank select                                                                    | t control bit 1                                                                                                                                                                                       | l, used to sele                                                                                                                                                                                                                                                                       | ect working r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | egister                                                                                                                                                                                                                                                                                                                                                                                                            |

| F0  | Gener              | al purpose Fl                                                                     | ag 0 available                                                                                                                                                                                        | e for user.                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AC  | Auxilia            | ry Carry flag                                                                     | for carry ou                                                                                                                                                                                          | t of or into b                                                                                                                                                                                                                                                                        | it 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                    |