## 80C51SL-BG KEYBOARD CONTROLLER

The 80C51SL-BG, based on Intel's industry-standard MCS®-51 microcontroller family, is designed for key-board control in laptop and notebook PCs. The highly integrated keyboard controller incorporates an 8042-style host interface with expanded memory, keyboard-scan, and power management. The 80C51SL supports both serial and scanned keyboard interfaces and is available in pre-programmed versions to reduce time to

- Superset of 80C51 Architecture

- Complete 8042 Keyboard Controller Functionality

- **■** 8042-Style Host Interface

- Optional Hardware Speed-Up of Gate A20 and RCL

- Local 16 x 8 Keyboard Switch Matrix Support

- Two Industry-Standard Serial Keyboard Interfaces; Supported via Four High-Drive Outputs

- **5 LED Drivers**

market.

- Low Power CHMOS Technology

- Power Management

- # 4-Channel, 8-Bit A/D

- Interface for up to 32 Kbytes of External Memory

- Slew-Rate-Controlled I/O Buffers Used to Minimize Noise

- 256 Bytes Data RAM

- 8 Kbytes Factory-Programmable Mask ROM Available

- Three Multifunction I/O Ports

- 10 Interrupt Sources with 6 User-Definable External Interrupts

- 2 MHz-16 MHz Clock Frequency, V<sub>CC</sub> = 5V ±10%

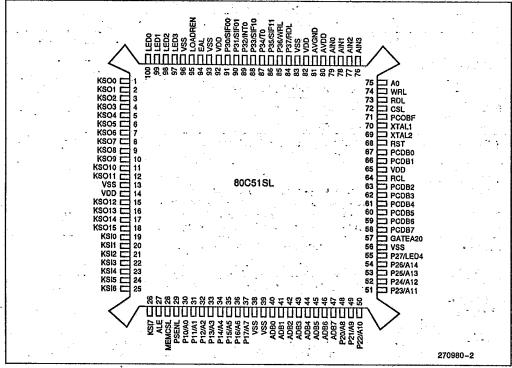

- 100-Pin PQFP

- Customizable to Specific Application Requirements

- Pre-Programmed Keyboard Controller/ Scanner Firmware Available

T-52-33-15

PRODUCT PREVIEW

T-52-33-15

#### **FUNCTIONAL DESCRIPTION**

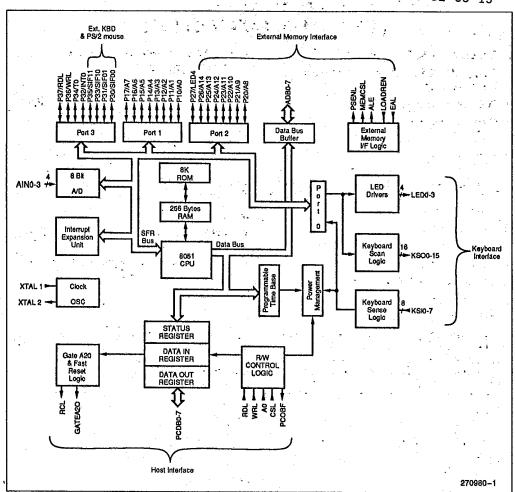

The 80C51SL is a universal keyboard controller that is designed for intelligent keyboard management in laptop and notebook computer applications. It uses an 80C51 microcontroller CPU core to produce a superset of the features provided by the industry-standard 8042 keyboard controller. Added features include two high-drive serial keyboard interfaces, on-chip optional hardware speedup for both GATEA20 and RCL, five LED drivers, a four-channel, eight-bit A/D converter and ten interface sources.

This data sheet concentrates on the 80C51SL enhancements to the 80C51. For general information about the 80C51SL, refer to the "Hardware Description of the 8051, 8052 and 80C51". and the "80C51BH-1/80C51BH-2 CHMOS Single-Chip 8-Bit Microcomputer with Factory Mask-Programmable ROM" data sheet in the *Embedded Microcontroller and Processor Handbook*.

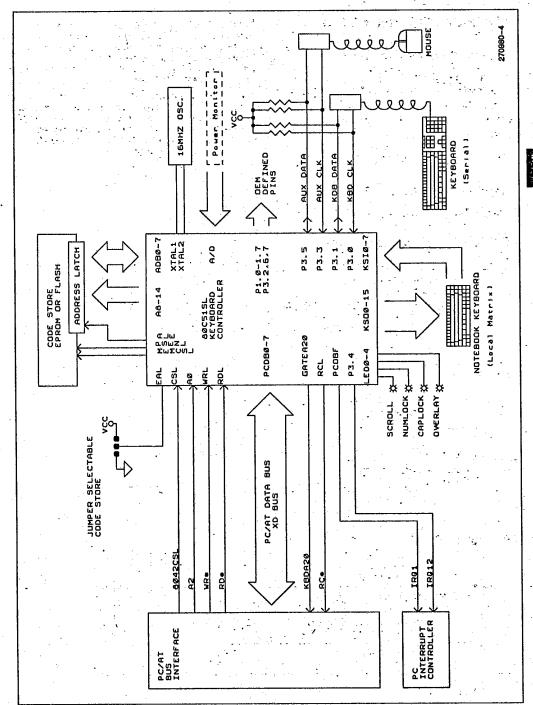

Figure 2. Connection Diagram

44E D

4826175 0103943 4 MITLL G PRODUCT PREVIEW

T-52-33-15

## PIN DESCRIPTIONS

## **Table 1. Pin Descriptions**

80C51SL-BG

|                                   |      | Table 1. Pin Descriptions                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                            | Type | Description                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| V <sub>SS</sub>                   |      | Circuit ground potential.                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| V <sub>DD</sub>                   |      | Supply voltage during normal, Idle, and Power-Down operation; nominally $\pm 5V \pm 10\%$ .                                                                                                                                                                                               |  |  |  |  |  |

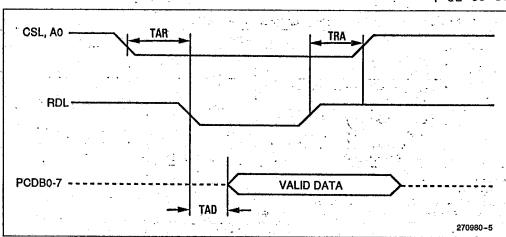

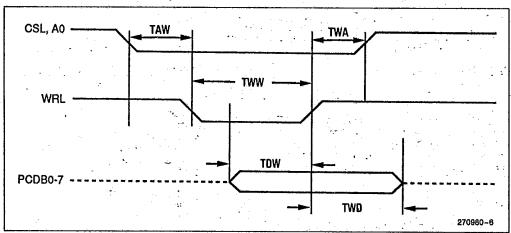

| PCDB0-7                           | 1/0  | Host interface data bus. An 8-bit, bidirectional port for data transfers between the host processor and the keyboard controller.                                                                                                                                                          |  |  |  |  |  |

| WRL                               | ı    | The active-low, host-interface write signal.                                                                                                                                                                                                                                              |  |  |  |  |  |

| RDL                               | 1.   | The active-low, host-interface read signal.                                                                                                                                                                                                                                               |  |  |  |  |  |

| CSL                               | 1    | The active-low, host-interface chip select.                                                                                                                                                                                                                                               |  |  |  |  |  |

| A0                                | 1    | Host-Interface Address select input. When high, it selects the command/status register; when low it selects the data registers.                                                                                                                                                           |  |  |  |  |  |

| PCOBF                             | 0    | The active-high, host-interface Output Buffer Full interrupt.                                                                                                                                                                                                                             |  |  |  |  |  |

| GATEA20                           | 0    | Gate A20 control signal output.                                                                                                                                                                                                                                                           |  |  |  |  |  |

| RCL                               | 0    | Host reset — active low.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| LED0-3                            | 0    | LED output drivers.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| KSI0-7                            |      | Keyboard input scan lines (input Port 0). Schmitt inputs with 5K-20K pull-<br>up resistors.                                                                                                                                                                                               |  |  |  |  |  |

| KSO0-15                           | 0    | Keyboard output scan lines.                                                                                                                                                                                                                                                               |  |  |  |  |  |

| PORT 1<br>P10/A0<br>P17/A7        | 1/0  | Port 1 is a general-purpose, 8-bit bidirectional port with internal pull-ups. It also supports the following user-selectable functions: P10-P16 are available for connection to dedicated keyboard inputs. A0-A7 output the low-order address byte (refer to LOADREN signal).             |  |  |  |  |  |

| LOADREN                           | ľ    | Low address enable. When set high, address bits A0-A7 are output on P10-P17.                                                                                                                                                                                                              |  |  |  |  |  |

| PORT 2<br>P20-6/A8-14<br>P27/LED4 | 1/0  | Port 2 is a general-purpose, 8-bit bidirectional port with internal pull-ups on P20-6/A8-14. It also supports the following user-selectable functions: P20-6/A8-14 output the high-order address byte. P27/LED4 is available as a fifth LED output driver (by writing to the port bit 7). |  |  |  |  |  |

| PORT 3                            | 1/0  | Port 3 is a general-purpose, 8-bit bidirectional port. P32/INT0, P34/T0, P36/WRL, and P37/RDL have internal pull-ups. P30/SIF00, P31/SIF01, P33/SIF10, and P35/SIF11 are high-drive open-drain outputs. It also supports the following user-selectable functions:                         |  |  |  |  |  |

| P30/SIF00                         |      | A high-drive, open-drain output to support an external serial keyboard interface (typically CLK); RXD (8051 UART serial input port); SIF0INTL (serial interface interrupt 0).                                                                                                             |  |  |  |  |  |

| P31/SIF01                         |      | A high-drive, open-drain output to support an external serial keyboard interface (typically DATA); TXD (8051 UART serial output port).                                                                                                                                                    |  |  |  |  |  |

| P32/INT0<br>P33/SIF10             |      | INTOL (external interrupt 0).  A high-drive, open-drain output to support an external serial keyboard interface (typically mouse CLK); SIF1INTL (external interrupt 1).                                                                                                                   |  |  |  |  |  |

| P34/T0                            |      | AUXOBF1 (output buffer full — mouse support); T0 (Timer/Counter 0 external input).                                                                                                                                                                                                        |  |  |  |  |  |

| P35/SIF11                         |      | A high-drive, open-drain output to support an external serial keyboard interface (typically mouse DATA); T1 (Timer/Counter 1 external input).                                                                                                                                             |  |  |  |  |  |

44E D 80C51SL-BG 4826175 0103944 6 ■ITL1 PRODUCT PREVIEW

T-52-33-15

## PIN DESCRIPTIONS (Continued)

## Table 1. Pin Descriptions (Continued)

| Symbol                                      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PORT 3<br>(Continued)<br>P36/WRL<br>P37/RDL |      | WRL (external data memory write strobe); inactive at addresses 7FF0–7FFFH. AUXOBF2 (output buffer full interrupt); INT2L (external interrupt); RDL (external data memory read strobe); inactive at addresses 7FF0–FFFFH.                                                                                                                                                                   |

| XTAL1                                       | 1    | Input to the on-chip oscillator.                                                                                                                                                                                                                                                                                                                                                           |

| XTAL2                                       | 0    | Output from the on-chip oscillator.                                                                                                                                                                                                                                                                                                                                                        |

| AVGND                                       |      | Analog ground potential.                                                                                                                                                                                                                                                                                                                                                                   |

| AVDD                                        |      | Analog supply voltage; nominally ±5V ±10%.                                                                                                                                                                                                                                                                                                                                                 |

| AIN0-3                                      | 1    | A/D Analog input channels.                                                                                                                                                                                                                                                                                                                                                                 |

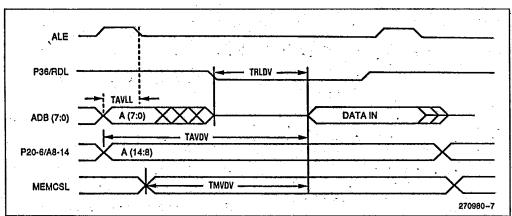

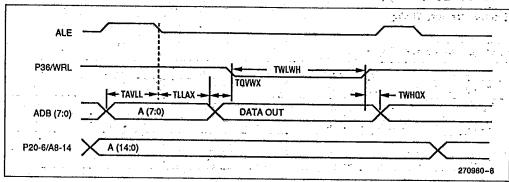

| ADB0-7                                      | 1/0  | External address/data bus. Multiplexes the low-address byte and data during external memory accesses.                                                                                                                                                                                                                                                                                      |

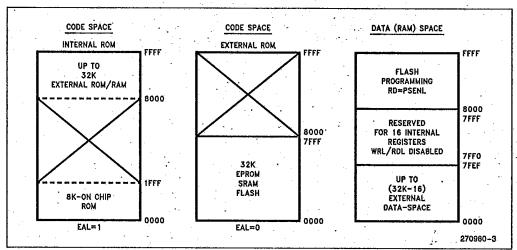

| EAL                                         |      | External address input. When held high, the 80C51SL CPU executes out of internal Program Memory unless the program counter exceeds 1FFFH. When held low, the 80C51SL CPU always executes out of external memory. EAL is latched on the falling edge of RST.                                                                                                                                |

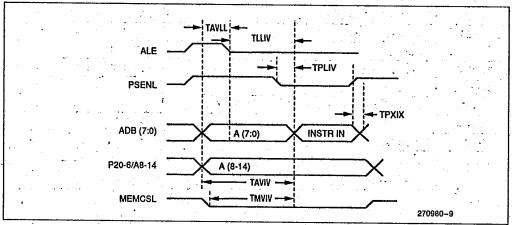

| ALE                                         | 0    | Address Latch Enable output pulse latches the low address byte during external memory access. ALE is output at a constant rate of 1/6 the oscillator frequency, whether or not there are accesses to external memory. One ALE pulse is skipped during the execution of a MOVX instruction. ALE is disabled during Idle mode and can also be disabled via Configuration register 1 control. |

| PSENL                                       | 0    | Program Store Enable is the read strobe to external program memory. PSENL is qualified with RDL and A15 for use with an external Flash memory. PSENL is not active when the device executes out of internal program memory.                                                                                                                                                                |

| MEMCSL                                      | I/O  | External Memory Chip Select for code space address 8000H and above, when EAL is inactive (i.e., high). For EAL low, MEMCSL is active. Goes inactive during Idle mode and Power-Down mode. If external memory interfacing is not required, MEMCSL can be configured as a general purpose I/O (controlled via Configuration register 1).                                                     |

| RST                                         | . 1. | Resets the keyboard controller. Hold RST high for two machine cycles.                                                                                                                                                                                                                                                                                                                      |

PRODUCT PREVIEW

T-52-33-15

#### **HOST INTERFACE**

The 80C51SL host interface is functionally compatible with the 8042-style host interface. It consists of the PCDB0-7 data bus; the RDL, WRL, A0 and CSL control signals; and the Status register, Input Data register, and Output Data register. Table 2 shows how the interface decodes the control signals. In addition to the above signals, the host interface in-cludes PCOBF, GATEA20, RCL, and the optional AUXOBF1 and AUXOBF2 signals available through firmware configuration of P34/T0 and P37/RDL, respectively.

Table 2. Control Signal Decode (Host Interface)

| WRL | RDL | CSL | A0 | Operation                               |

|-----|-----|-----|----|-----------------------------------------|

| 0   | 1   | 0   | 0  | Write Data to Input<br>Data Register    |

| 0   | 1   | 0   | 1  | Write Command to<br>Input Data Register |

| 1   | 0   | 0   | O: | Read the Output<br>Data Register        |

| 1   | 0   | 0   | 1  | Read the Status<br>Register             |

#### **Host-Interface Registers**

The Input Data register, Output Data register, and Status register are each 8 bits wide. Table 3 lists the addresses of the host-interface registers. Figure 3 shows the contents of the Status register.

Table 3. 80C51SL Memory Map for **Host-Interface Registers**

| Register                                | Address | 80C51SL<br>CPU<br>Access |

|-----------------------------------------|---------|--------------------------|

| Input and Output<br>Data Registers(1)   | 7FF1H   | R/W                      |

| Status Register                         | 7FF2H   | R/W(2)                   |

| Auxiliary Output<br>Data Register #1(3) | 7FF6H   | Write Only               |

| Auxiliary Output<br>Data Register #2(3) | 7FF7H   | Write Only               |

#### NOTES:

- 1. Although the Input and Output Data registers are physi-

- Although the input and output bata registers are physically separate, they share address 7FF1H.

The 80C51SL CPU cannot write to bits 0, 1 or 3 of the Status register.

Alternate Output Data register function.

| (MSB) |                                                                           |                              |                              |                                 |                                 |                                    | (LSB)                          |

|-------|---------------------------------------------------------------------------|------------------------------|------------------------------|---------------------------------|---------------------------------|------------------------------------|--------------------------------|

| UD    | UD                                                                        | UD                           | UD                           | C/D                             | UD                              | IBF                                | OBF                            |

| 7     | 6                                                                         | <u>.</u> 5                   | .4.                          | 3                               | 2                               | 1                                  | 0                              |

| C/D   | are user-definate<br>(Command Data<br>mand (0 = data<br>reset to "0" if A | a)—This bit s<br>, 1 = comma | pecifies whe                 | ther the input<br>host write op | data registe<br>eration, this b | r contains da<br>lit is set to "1" | ita or a com-<br>'if A0 = 1 or |

| IBF   | (Input Buffer Ful<br>register. Setting<br>CPU reads the i                 | this flag acti               | vates the 80                 | C51SL CPU's                     | KDINTL inte                     | rrupt. When                        | the 80C51SL                    |

| OBF   | (Output Buffer I<br>register using or<br>the output data                  | Full)—This fla               | ig is set to<br>Idresses: 7F | 1 whenever the                  | he 80C51SL                      | CPU writes                         | into the data                  |

Figure 3. Status Register

PRODUCT PREVIEW

T-52-33-15

#### 80C51SL-to-Host Communication

The 80C51SL CPU can write to the Output Data register via any of the following addresses: 7FF1H, 7FF6H, or 7FF7H. A write to any of the three addresses automatically sets Bit 0 (OBF) in the Status register. In addition, a unique output flag differentiates the three addresses. Table 4 lists the signal that corresponds to each flag. Each flag is automatically set when data is written to the corresponding address.

Table 4. Host-Interface Flags

| Address | Flag                                                                                              |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7FF1H   | PCOBF output signal goes high if, and only if, bit 4 of Configuration register 1 equals 0.        |  |  |  |  |  |

|         | Port 3, pin 4 output (P34) goes high if, and only if, bit 5 of Configuration register 0 equals 1. |  |  |  |  |  |

| 7FF7H   | Port 3, pin 8 output (P37) goes high if, and only if, bit 6 of Configuration register 0 equals 1. |  |  |  |  |  |

#### Host-to-80C51SL Communication

The host system can send both commands and data to the Input Data register. The 80C51SL differentiates between commands and data by reading the value of Bit 3 of the Status register. When bit 3 is "1", the 80C51SL interprets the register contents as a command. When Bit 3 is "0", the 80C51SL interprets the register contents as data. During a host write operation, Bit 3 is set to "1" if AO = 1 or reset to "0" if AO = 0.

#### **Host-Interface Dedicated Outputs**

The 80C51SL host-interface provides three dedicated output signals: Output-Buffer Full (PCOBF), GATEA20, and the host "fast" reset, RCL.

#### **PCOBF**

The PCOBF signal is an active-high system interrupt which signifies that the 80C51SL CPU has written to the output data register via address 7FF1H. On power-up, after a valid RST pulse has been delivered to the device, PCOBF is reset to 0. PCOBF will normally reflect the status of writes to 7FF1H, if bit 4 of Configuration register 1 equals 0.

Additional flexibility has been added which allows firmware to directly control the PCOBF output signal, independent of data transfers to the host-interface data output register. This feature allows the 80C51SL to be operated via the host "polled" mode. This firmware control is active when PCOBFEN is high and firmware can then bring PCOBF high by writing a "1" to the LSB of the 1-bit data register allocated at 7FFDH.

This register is also readable; residual bits 1–7 will return a "0" on the readback. The value read back on bit 0 of the register always reflects the present value of the PCOBF output. If PCOBFEN = 1, then this value reflects the output of the firmware latch at 7FFDH. If PCOBFEN = 0, then the value read back reflects the in-process status of write cycles to 7FF1H (i.e., if the value read back is high, the host interface output data register has just been written to).

#### **GATEA20 HARDWARE SPEED-UP**

The 80C51SL contains on-chip logic support for the GATEA20 hardware speed-up feature. GATEA20 from the 80C51SL is part of the control required to mask address line A20 to emulate 8086 addressing.

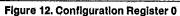

In addition to the ability for the host to control the GATEA20 output signal directly, a configuration bit called "SAEN" (Software Assist Enable, bit 7 of Configuration register 0) is provided; when set, SAEN allows firmware to control the GATEA20 output.

When SAEN is set, a 1-bit register assigned to address 7FFBH controls the GATEA20 output. The register bit allocation is shown in Figure 4.

| 4- D | 7 |   |   |   |   |   |   | <b>DO</b> . |

|------|---|---|---|---|---|---|---|-------------|

| X    |   | х | х | x | Х | х | × | GATEA20     |

Figure 4. Register Bit Allocation

Writing a "0" into location D0 causes the GATEA20 output to go low, and vice versa. When the register at location 7FFBH is read, all unused bits (D7-D1) are tied low.

Host control and firmware control of GATEA20 affect two separate register elements. Readback of

PRODUCT PREVIEW

T-52-33-15

GATEA20 through the use of 7FFBH reflects the present state of the GATEA20 output signal: if SAEN is set, the value read back corresponds to the last firmware-initiated control of GATEA20; if SAEN is reset, the value read back corresponds to the last host-initiated control of GATEA20.

Host control of the GATEA20 output is provided by the hardware interpretation of the "GATEA20 se-quence" (see Table 5). The foregoing description assumes that the SAEN configuration bit is reset.

When the 80C51SL receives a "D1" command followed by data (via the host interface), the on-chip hardware copies the value of data bit 1 in the received data field to the GATEA20 host latch. At no time during this host-interface transaction will PCOBF or the IBF flag (bit 1) in the Status register be activated; i.e., this host control of GATEA20 is transparent to firmware, with no consequent degradation of overall system performance. Table 5 details the possible GATEA20 sequences and the 80C51SL responses.

On receiving an external hardware reset via the RST pin or a soft reset via the dedicated address 7FF0H (see the "Soft Reset" section), GATEA20 will be set. Internally sourced resets, such as those initiated by a host write sequence during Power-Down mode, will have no effect on the GATEA20 output.

An additional level of control flexibility is offered via a memory-mapped asynchronous set and reset ca-pability. Any data written to 7FFEH causes the GATEA20 host latch to be set, while any data written to 7FFFH causes it to be reset. This control mechanism should be used with caution. It was added to augment the "normal" control flow as described above—not to replace it. Since the host and the firmware have asynchronous control capability of the host latch via this mechanism, a potential conflict could arise. Therefore, after using the 7FFEH and 7FFFH addresses, firmware should read back the GATEA20 status via 7FFBH (with SAEN = 0) to confirm the actual GATEA20 response.

Table 5. GATEA20 Command/Data Sequence Examples

| A0          | R/W         | PCDB0-7                 | IBF Flag         | GATEA20          | Comments                                  |

|-------------|-------------|-------------------------|------------------|------------------|-------------------------------------------|

| 1<br>0<br>1 | W<br>W<br>W | D1<br>DF<br>FF          | 0<br>0<br>0      | Q<br>1<br>Q      | Valid GATEA20<br>Turn-on Sequence         |

| 1<br>0<br>1 | W<br>W<br>W | D1<br>DD<br>FF          | .0<br>0<br>0     | Q<br>0<br>Q      | Valid GATEA20<br>Turn-off Sequence        |

| 1<br>1<br>0 | W<br>W<br>W | D1<br>D1<br>DF<br>FF    | 0<br>0<br>0<br>0 | Q<br>Q<br>1<br>Q | Multiple D1 Trigger<br>Turn-on Sequence*  |

| 1<br>1<br>0 | W<br>W<br>W | D1<br>D1<br>DD<br>FF    | 0<br>0<br>0<br>0 | Q<br>Q<br>1<br>Q | Multiple D1 Trigger<br>Turn-off Sequence* |

| 1 1         | W<br>W<br>W | D1<br><i>XX**</i><br>FF | 0<br>1<br>1      | Q<br>Q<br>Q      | Invalid Sequence                          |

#### NOTES:

All examples assume that the SAEN configuration bit is 0.

"Q" indicates the bit remains set at the previous state.

\*Not a standard sequence.

\*\*\*XX = Anything except D1.

80C51SL-BG

PRODUCT PREVIEW

T-52-33-15

#### RCL HARDWARE SPEED-UP

RCL is the system reset output. In a similar manner to the GATEA20 control structure, RCL may be controlled via firmware or via direct hardware interpretation of the host reset command (FE). A dedicated, programmable counter is provided in hardware, which allows the RCL active pulse width to be correctly sized. This 7-bit down counter is allocated to address 7FF9H within the 80C51SL memory map;

If the 80C51SL receives an FE command byte over the host interface, one of two responses can be configured via firmware to occur:

- 1. If bit 1 in Configuration register 1 (HARSTEN) is set, then immediately on receiving the FE command, the 80C51SL output RCL will go active. PCOBF and the IBF status flag (bit 1 of the Status register) will remain unaffected by the transaction; i.e., when HARSTEN is set, the FE command is transparent to firmware. RCL will remain low until the pre-programmed 7-bit counter times out, at which point RCL will return to its inactive high state.

- 2. If HARSTEN is reset, then the FE command will be processed in the conventional way; i.e., IBF status flag and PCOBF(1) will both be automaticality forced high, and it is up to firmware to control the RCL response via the 1-bit register element allocated to address 7FFA within the 80C51SL memory map. The bit assignment for this register is shown in Figure 5.

Figure 5. Register Bit Allocation

If bit 0 is set, then RCL = 1 and vice versa. The register is also readable, and any read cycle will show the unused bits (7-1) tied low. The value read back on bit 0 is determined by the state of HAR-STEN: if HARSTEN is high, the value read back will reflect the status of hardware FE interpretation; if the HARSTEN bit is low, the value read back will reflect the present status of the firmware-controlled register at 7FFAH. In either case, the value read back on bit 0 corresponds to the present value on RCL.

When HARSTEN is low, it is firmware's responsibility to time the RCL pulse width; i.e., when HARSTEN is low, the RCL active low pulse width is independent of the programmable 7-bit counter. When HARSTEN is high, however, the active low pulse width on RCL is dependent on the data loaded into the counter before the FE command is received. The following calculation may be used to determine the pre-load value for a given desired output pulse width.

$$Load\ Value = \frac{Desired\ Pulse\ Width}{T}$$

where T = clock or external crystal period.

For example, assuming a 16 MHz external crystal (or clock source) and assuming we require the nominal 6  $\mu s$  pulse width:

Load Value =

$$\frac{6 \times 10^{-6}}{62.5 \times 10^{-9}}$$

= 96 DEC = 60 HEX

The down counter is set when the 80C51SL receives an active RST or firmware-initiated reset via an active write cycle to 7FF0H.

When HARSTEN is set and the 7-bit counter times out, the counter is automatically reloaded with the pre-loaded data that was written to 7FF9H prior to the FE transaction. If the RCL output is therefore to be controlled by this mechanism, the firmware must pre-load the counter to the desired value at least once prior to any reception of the FE command. Further loads are not then required unless the 80C51SL receives an active reset via RST or a software-initiated reset.

## **KEYBOARD SCAN**

The interface to the keyboard scan logic includes 16 slew-rate-controlled, open-drain scan-out lines (KSOO-15) and eight Schmitt Trigger sense lines (KSIO-7) with internal pull-up resistors. KSIO-7 connect directly to Port 0 of the 80C51SL CPU. The 16 scan-out lines are controlled by the four low-order bits of Port 0 (see Table 6). Together KSOO-15 and KSIO-7 form a keyboard matrix.

1. Bit 4 of Configuration register 1 (PCOBFEN) must be set for this to occur.

PRODUCT PREVIEW

T-52-33-15

Table 6. Keyboard Matrix Decode

|      | Po          | rt 0 | Keyboard Scan<br>Out Lines |                    |  |

|------|-------------|------|----------------------------|--------------------|--|

| .P03 | P02 P01 P00 |      |                            | KSO15-KSO0         |  |

| 0    | 0           | 0    | 0                          | 1111111111111110   |  |

| 0    | 0           | 0    | 1                          | 111111111111111101 |  |

| 0    | 0.          | 1    | 0                          | 11111111111111011  |  |

| •    | •           | •    | •                          | •                  |  |

| •    | •           | •.   | •                          | •                  |  |

| •    | •           | •    | •                          | •                  |  |

| 1    | 1.          | 1    | 0                          | 10111111111111111  |  |

| 1    | 1           | 1    | 1                          | 0111111111111111   |  |

Since the KSO0-15 outputs are a decode of the low order Port 0 nibble, the outputs can be expected to glitch during a normal binary code control sequence. In the pre-programmed part, however, the firmware uses a "grey" code sequence, thus effectively eliminating this potential noise source. Because of this strategy, however, the part will follow a non-standard matrix sequence when viewed at the KSO15-0 outputs in normal operation. Table 7 shows the sequence of activated KSO output lines in normal operation for the 80C51SL.

**Table 7. KSO Output Line Sequence**

| followed by KSO13 |  |  |

|-------------------|--|--|

| followed by KSO15 |  |  |

| followed by KSO14 |  |  |

| followed by KSO10 |  |  |

| followed by KSO11 |  |  |

| followed by KSO9  |  |  |

| followed by KSO8  |  |  |

| followed by KSO0  |  |  |

| etc.              |  |  |

|                   |  |  |

#### **Keyboard Interrupt Logic**

If Bit 1 of the Configuration register 0 is set to "1", the KSO0-15 lines are simultaneously driven low and the Keyboard Scan Logic will generate the KDINTL interrupt if one or more of the KSI0-7 lines goes low. If Bit 1 is reset to "0", then a low level on KSI0-7 will not generate an interrupt and a firmware service routine can poll the KSI0-7 lines to detect a transition.

#### **DEDICATED INPUT KEYS**

Bits 0-6 of Port 1 are available as inputs for dedicated keys. The keyboard interrupt logic can be configured to generate the KDINTL interrupt whenever a key depression is detected on one of these dedicated keys. To enable this interrupt feature, set Bit 2 of the Configuration 0 register to "1". The KSO15-0 outputs are unaffected by the state of this configuration bit. KDINTL is configured as an edge-sensitive interrupt. Any falling edge on either KSI7-0 or P16-0, assuming correct setting of the configuration bits as explained earlier, will cause the 80C51SL core to receive the active KDINTL interrupt.

#### **LED DRIVERS**

The 80C51SL has four dedicated high-drive, opendrain, LED drivers (LED0-3). These drivers connect to Bits 4-7 of the 80C51SL internal Port 0.

Bit 7 of Port 2 can be configured as a fifth high-drive, open-drain LED driver. Writing a 0 to the appropriate port bit will cause the associated LED output to go low. During and after an external or firmware-initiated reset, the LED outputs (including P27) will be high until firmware writes to the appropriate port.

# EXTERNAL KEYBOARD AND MOUSE INTERFACE

Industry-standard PC-AT-compatible keyboards employ a two-wire, bidirectional TTL interface for data transmission. Several sources also supply PS/2 mouse products that employ the same type of interface. To facilitate system expansion, the 80C51SL provides four signal pins that may be used to implement this interface directly for an external keyboard and mouse.

The 80C51SL has four high-drive, open-drain output(1), bidirectional port pins that can be used for external serial interfaces, such as ISA external keyboard and PS/2-type mouse interfaces. They are P30/SIF00, P31/SIF01, P33/SIF10, and P35/SIF11. P33/SIF10 is connected to the firmware-configurable level/edge sensitive INTL interrupt pin of the 80C51SL CPU. P30/SIF00 is connected to the edge-sensitive SIF0INTL interrupt pin of the 80C51SL CPU.

NOTE:

1. External pull-ups may be required.

PRODUCT PREVIEW.

Γ-52-33-15

The serial clock lines, P30/SIF00 and P33/SIF10, are inhibited (driven low) by hardware during and immediately after an external or firmware-initiated reset. This is so that any power-on self-test completion code transmitted from the serial keyboard will not be missed by the 80C51SL due to power-up timing mismatches. It is however, necessary to write a "0" to these pins immediately after power-up in order to release the hardware inhibit function. If the external keyboard or mouse is not required, P30/SIF00, P31/SIF01, P33/SIF10, and P35/SIF11 can be used as general-purpose I/O pins.

# PORT STRUCTURES AND OPERATION

All three 80C51SL ports are bidirectional. Each consists of a latch (Special Function Registers P1 through P3), an output driver, and an input buffer. Port 0 of the 80C51SL CPU does not connect to the package pins. It is used internally to drive the keyboard scan logic.

The output drivers of Ports 1 and 2 can be used in accesses to external memory. The 80C51SL provides the LOADREN signal to facilitate external memory interfaces. When the LOADREN signal is high, Port 1 outputs the low byte of the external memory address. If LOADREN is tied low, then the Port 1 signals continue to emit the P1 SFR content. Port 2 outputs the upper seven bits of the high byte of the external address when the address is 15 bits wide and either EAL is tied low or EAL is tied high

and Bit 0 (ADDREN) of Configuration register 1 is set. Otherwise, the Port 2 pins continue to emit the P2 SFR content.

During external memory access, the ADB0-7 lines also provide the low byte of the address, time-multiplexed with the data being written or read.

Many of the port pins are multifunctional. In addition to the standard 80C51 alternate functions, the 80C51SL port pins provide additional alternate functions (see Table 8). The alternate functions can be activated only by writing a "1" to the corresponding port bit.

## I/O Configurations

All port pins with the exception of P27/LED4, P30/SIF00, P31/SIF01, P33/SIF10, P35/SIF11 have fixed internal pull-ups and are therefore called "quasi-bidirectional" ports. When configured as inputs, the pins are pulled high by the internal pull-ups and will source current when externally pulled low.

#### NOTE:

During a 16-bit external Program Memory access, Port 2 outputs the high address byte. In the 80C51, the Port 2 drivers use the strong pull-up during the entire time that they are emitting a "1" on a Port 2 bit. In this instance, the 80C51 weak quasi-bidirectional pull-up condition that normally occurs after two oscillator periods does not occur. Port 1 of the 80C51SL emulates the quasi-bidirectional pull-up condition, not this extended strong pull-up condition.

Table 8. Port Pin Alternate Functions

| Port Pin    | 80C51 Alternate Function                | 80C51SL Aiternate Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P10-6/A0-6  |                                         | Output A0-6 Address Bits or Dedicated Keyboard Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| P17/A7      |                                         | Output A7 Address Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| P20-6/A8-14 |                                         | Output A8-14 Address Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| P27/LED4    |                                         | LED4 Output Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| P30/SIF00   | RXD (Serial Input Port)                 | SIF00, External Keyboard CLK/SIF0INTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| P31/SIF01   | TXD (Serial Output Port)                | SIF01, External Keyboard Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| P32/INTO    | INTOL (External Interrupt 0)            | and the second of the second o |  |  |

| P33/SIF10   | INT1L (External Interrupt 1)            | SIF10, External Auxiliary Mouse CLK/SIF1INTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| P34/T0      | T0 (Timer 0 External Input)             | AUXOBF1, Auxiliary Output Buffer Full 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| P35/SIF11   | T1 (Timer 1 External Input)             | SIF11, External Auxiliary Mouse Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| P36/WRL     | WRL (External Data Memory Write Strobe) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| P37/RDL     | RDL (External Data Memory Read Strobe)  | AUXOBF2, Auxiliary Output Buffer Full 2, INT2L (External Interrupt 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

PRODUCT PREVIEW

T-52-33-15

#### 80C51SL POWER MANAGEMENT

The 80C51SL uses low power CHMOS and provides support for two further power-saving modes, available when inactive: Idle mode, typically between keystrokes; and Power-Down mode, upon command from the host. A four-channel, eight-bit A/D converter is also included for power management (i.e., battery voltage monitoring, etc.).

#### Idle Mode

Idle mode is initiated by an instruction that sets the PCON.0 bit (SFR address 87H) in the 80C51SL. In Idle mode, the internal clock signal to the 80C51SL CPU is gated off, but not to the Interrupt Timer and Serial Port functions. The 80C51SL CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator, and all other registers maintain their data. The port pins hold the logical levels they had when Idle mode was activated. ALE and PSENL are held high. If an A/D conversion is in process when Idle mode is entered, any conversion results may contain erroneous data.

There are two ways to terminate Idle mode. First, activation of any enabled interrupt will cause the PCON.0 bit to be cleared by hardware. The interrupt will be serviced and, following the RETI, the CPU will resume operation by executing the instruction following the one that put the CPU into Idle mode.

The second way to terminate the Idle mode is with a hardware reset. Note that in the 80C51SL, a hardware reset will clear the registers. The 80C51SL CPU will not resume program execution from where it left off.

During Idle mode, MEMCSL, ALE, and PSENL will all be forced high. MEMCSL will not go high if MEMCSL is being used as a general-purpose I/O (i.e., if bit 2 or 3 in Configuration register 1 is high).

#### **Power-Down Mode**

Power-Down mode is initiated by an instruction that sets bit PCON.1 in the 80C51SL CPU. When the 80C51SL enters Power-Down mode, all internal clocks, including the 80C51SL core clock, are turned off, if an external crystal is used, the internal oscillator is turned off. MEMCSL, the external memory select signal, goes inactive (high) unless it is configured as a general-purpose I/O (i.e., unless bit 3 of Configuration register 1 is "1"); ALE and PSENL are both forced low, RAM contents are preserved.

#### PROGRAMMABLE RESET TIMER

The on-chip oscillator (if used with an external crystal) requires at least 10 ms to stabilize after initial power-up or when exiting the Power-Down mode. Even if the 80C51SL is driven from an external clock source (i.e., no crystal) the 80C51SL core specifies the minimum pulse width duration of a reset to be  $\geq$  24 clock cycles.

The 80C51SL includes a fully programmable reset counter which, when correctly configured, ensures that any internally sourced reset signal delivered to the 80C51SL core is at least 10 ms in duration. It is the user's responsibility to ensure that any externally sourced reset signal (via the RST pin) also meets the 10 ms pulse width specification on power-up or when exiting the Power-Down mode.

The 80C51 CPU drives a divide-by-32 pre-scaler, which in turn drives the Programmable Reset counter. (1) The firmware must preload the program counter with a 16-bit value before invoking the Power-Down mode. The counter resides at the following addresses: Low Byte, 7FF3H; High Byte, 7FF4H. The preload value depends upon the clock frequency and clock source, as explained below.

#### **EXITING POWER-DOWN MODE**

If the Programmable Reset counter is correctly configured and if Configuration register 0 is prefigured properly (i.e., if bits 1-4 are set as described in figure 12 in the "Configuration Registers" section), the following situations will automatically terminate Power-Down mode.(2)

#### NOTES:

The divide-by-32 pre-scaler ensures that even with the programmable reset counter loaded with 0000H, the reset delivered to the 80C51SL core is at least 24 clock cycles wide. (Due to the nature of the internal hardware, the actual pulse width of the reset pulse delivered to the 80C51SL is 34 clock cycles wide.)

Only the 80C51SL core processor and its SFR peripherals will receive the reset pulse thus generated; on-chip logic, such as the configuration registers, host registers, GATEA20, and fast reset (RCL) logic will remain unaffected.

80C51SL-BG

44E D

T-52-33-15

- A host data/command Write sequence to the Host interface.(1)

- An input key depression sensed via KSI0-7 or P10-6/A0-6.

- A high to low transition on P32/INT0 while EXTINTEN (config. reg. 0, bit 4) is set. P32/INT0 must be high before entering Power-Down mode.

The 80C51SL device outputs will respond in the following manner on exiting the Power-Down mode:

$\begin{array}{ll} \text{GATEA20} & = & \text{Q(3)} \\ \text{RCL} & = & \text{Q} \\ \text{PCOBF} & = & \text{Q} \end{array}$

MEMCSL = Q, if MEMCSL is used as a general-

purpose I/O = 0, otherwise

KSO15 = 0

KSO0-14 = high impedance (open drain)

P27 = high impedance LED0-3 = high impedance

P20-6 = high order address, if EAL = 0

= weak high, if EAL = 1

P30/SIF00 = open drain P33/SIF01 = open drain P31/SIF01 = open drain = open drain P35/SIF11 P32/INTO = weak high P34/T0 = weak high P36/WRL = weak high P37/RDL = weak high PCDB0-7 = high impedance

P10-7 = weak high, if LOADREN = 0

= low order address, if LOADREN = 1

A Power-Down status flag (PDFLAG) on Bit 0 of the Configuration register 0 can be set by firmware before entering Power-Down mode. Only an externally generated reset pulse on the RST input or a firmware "soft" reset will reset the PDFLAG bit; an inter-

#### NOTES:

1. There are two important exceptions to this, If the SAEN bit in Configuration register 0 is reset to "0", the device will ignore the "D1" GATEA20 sequence with respect to exiting power-down mode. Similarly, if the HARSTEN bit in Configuration register 1 is set to "1", the device will ignore an "FE" command with respect to exiting power-down mode.

2. Bit 4 of Configuration Register 0 must be "1" for this to occur.

Where Q = Quiescent; i.e., no change as a result of exiting power-down mode.

4. All inputs without internal pull-ups and floating I/Os must be driven to a known state.

nally-sourced reset signal from the Programmable Reset counter has no effect on the PDFLAG bit. After a reset occurs, the 80C51SL CPU can read the value of the PDFLAG bit to determine whether the reset source was internal or external.

#### **External Crystal Oscillator**

When an external crystal is the clock source for the 80C51SL, the reset pulse width must be 10 ms or greater to allow the internal oscillator to stabilize. The pulse-width requirement applies to both internally and externally generated reset signals.

Use the following formula to calcuate the appropriate preload value for the Programmable Reset counter:

Preload value =  $[(10 \times 10^6)/32]$ /TPERIOD

The following examples calculate the Programmable Reset counter preload value for two different clock frequencies.

#### **EXAMPLE 1**

Assume that the clock frequency = 2 MHz.

TPERIOD = 1/2M = 500 nspreload value =  $[(10 \times 10^6)/32]/500$

> = 625 DEC = 0271 HEX

## **EXAMPLE 2**

Assume that the clock frequency = 16 MHz.

TPERIOD = 1/16M = 62.5 nspreload value =  $[(10 \times 10^6)/32]/62.5$

> = 5000 DEC = 1388 HEX

## **External Clock Signal**

The 80C51SL clock source can be an externally generated clock signal instead of a crystal oscillator. Connect the clock signal to the XTAL1 input. When an external clock signal is the clock source for the 80C51SL, the reset pulse must last for at least 24 clock periods. The pulse-width requirement applies to both internally and externally generated reset signals. Preload 0000H into the Programmable Reset counter before entering Power-Down mode. This value will cause the Programmable Reset counter to deliver a 34-clock-period reset pulse to the 80C51SL core.

PRODUCT PREVIEW

T-52-33-15

#### Interrupts

The 80C51SL provides the five standard 8051 interrupts (Group 0) and five expansion interrupts (Group 1). Three of the five expansion interrupts are dedicated to internal functions. Two are available for serial interface interrupt sources. Table 9 describes the interrupts.

The Group 0 interrupts use the standard 8051 interrupt enable and priority structures. Each interrupt is individually enabled or disabled by setting or clearing a bit in the Interrupt Enable (IE) register (SFR location A8H). Each interrupt is programmed to one of two priority levels by setting or clearing a bit in the Interrupt Priority (IP) register (SFR location B8H). See the "Hardware Description of the 8051, 8052, and 80C51" in the 8-Bit Embedded Controller Handbook for more details.

Group 0 interrupts (which are identical to the standard 80C51 interrupts) are configurable as either level- or edge-sensitive. Consult the *Embedded Microcontroller and Processor Handbook* for a full description.

The Group 1 Interrupt Enable register (IE1) is a bitaddressable Special Function Register that resides at SFR address 0E8H. Bits 0 through 4 are the individual enable bits for the Group 1 Interrupts. Bit 7 is the global enable bit for the group. Figure 6 shows the contents of the IE1 register.

The Group 1 Priority Register (IP1) is a bit-addressable Special Function Register that occupies SFR address 0F8H. Setting or clearing individual bits in the IP1 register selects the priority level of each Group 1 interrupt source. Figure 7 shows the contents of the IP1 register.

KDINTL and SIF0INTL have been configured in hardware as edge-sensitive interrupts. A falling edge on any of the KSI7-0 or P10-6 inputs (assuming an appropriate configuration register setup) will cause KDINTL to go active. Similarly, a falling edge on P3.0 will cause SIF0INTL to go active. The other interrupts in Group 1 are configured as level-sensitive interrupts.

For those users who intend to generate their own 80C51SL firmware, care should be taken to ensure that all interrupts remain disabled during the "configuration setup," as spurious interrupts may be generated when Port 3 is configured.

**Table 9. Interrupt Sources**

| Interrupt | Description                     | Pin(1)     | Vector<br>Address | Polling<br>Order | Active |

|-----------|---------------------------------|------------|-------------------|------------------|--------|

| Group 1   |                                 |            |                   |                  |        |

| KDINTL    | Keystroke Detect                | ·          | 0043H             | 1                | E      |

| IBFINTL   | Input Buffer Full               | · —        | 004BH             | 2                |        |

| ADINTL    | A/D Conversion Complete         | <b>—</b> ; | 0053H             | 3                |        |

| SIFOINTL  | Serial Interface                | P30        | 005BH             | 4                | E      |

| INT2L     | External Interrupt              | P37        | 0063H             | 5                | L      |

| Group 0   |                                 |            |                   |                  |        |