# intطِ

#### **ADVANCE INFORMATION**

### SMART 5 BOOT BLOCK FLASH MEMORY FAMILY 2, 4, 8 MBIT

28F200B5, 28F400B5, 28F800B5, 28F004B5

- SmartVoltage Technology

- Smart 5 Flash: 5 V Reads,

- 5 V or 12 V Writes

- Increased Programming Throughput at 12 V VPP

- Very High-Performance Read

- \_ 2-, 4-Mbit: 60 ns Access Time

- 8-Mbit: 70 ns Access Time

- x8 or x8/x16-Configurable Data Bus

- Low Power Consumption

- Max 60 mA Read Current at 5 V

- Auto Power Savings: <1 mA Typical Standby Current

- Optimized Array Blocking Architecture

- 16-KB Protected Boot Block

- Two 8-KB Parameter Blocks

- 96-KB and 128-KB Main Blocks

- Top or Bottom Boot Locations

- **■** Extended Temperature Operation

- −40 °C to +85 °C

- Industry-Standard Packaging

40, 48-Lead TSOP, 44-Lead PSOP

- Extended Block Erase Cycling

- 100,000 Cycles at Commercial Temp

- 10,000 Cycles at Extended Temp

- Hardware Data Protection Feature

- Absolute Hardware-Protection for Boot Block

- Write Lockout during Power Transitions

- Automated Word/Byte Program and Block Erase

- Command User Interface

- Status Registers

- Erase Suspend Capability

- SRAM-Compatible Write Interface

- Reset/Deep Power-Down Input

- Provides Low-Power Mode and Reset for Boot Operations

- Pinout Compatible 2, 4, and 8 Mbit

- ETOX<sup>™</sup> Flash Technology

- 0.6 μ ETOX IV Initial Production

- 0.4  $\mu$  ETOX V Later Production

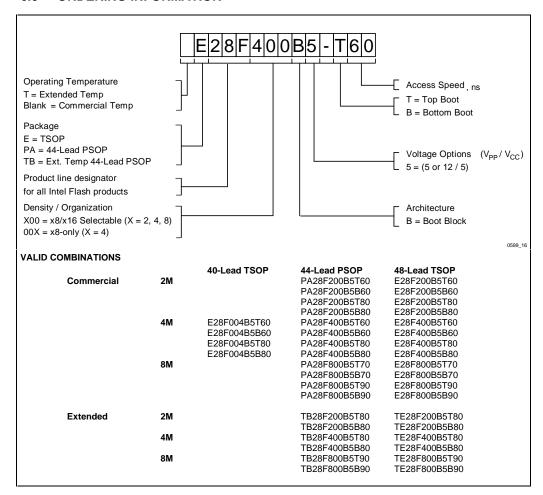

Intel's Smart 5 boot block flash memory family provides 2-, 4-, and 8-Mbit memories featuring high-density, low-cost, nonvolatile, read/write storage solutions for a wide range of applications. Their asymmetrically-blocked architecture, flexible voltage, and extended cycling provide highly flexible components suitable for embedded code execution applications, such as networking infrastructure and office automation.

Based on Intel's boot block architecture, the Smart 5 boot block memory family enables quick and easy upgrades for designs that demand state-of-the-art technology. This family of products comes in industry-standard packages: the 40-lead TSOP for very space-constrained 8-bit applications, 48-lead TSOP, ideal for board-constrained higher-performance 16-bit applications, and the rugged, easy to handle 44-lead PSOP.

December 1997 Order Number: 290599-004

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The 28F200B5, 28F400/004B5, 28F800B5 may contain design defects or errors known are errata. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

P.O. Box 5937

Denver, CO 80217-9808

or call 1-800-548-4725

or visit Intel's website at http://www.intel.com

COPYRIGHT © INTEL CORPORATION 1997, 1998

CG-041493

${}^{\star}\mathsf{Third}\text{-party}$  brands and names are the property of their respective owners.

# int<sub>el®</sub>

#### **SMART 5 BOOT BLOCK MEMORY FAMILY**

### **CONTENTS**

| PAGE                                                                                                                                | PAGE                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 1.0 INTRODUCTION5                                                                                                                   | 4.0 DESIGN CONSIDERATIONS24                                                       |

| 1.1 New Features in the Smart 5 Memory                                                                                              | 4.1 Power Consumption24                                                           |

| Products5                                                                                                                           | 4.1.1 Active Power24                                                              |

| 1.2 Product Overview5                                                                                                               | 4.1.2 Automatic Power Savings (APS)24                                             |

| 2.0 PRODUCT DESCRIPTION6                                                                                                            | 4.1.3 Standby Power25                                                             |

| 2.1 Pin Descriptions6                                                                                                               | 4.1.4 Deep Power-Down Mode25                                                      |

| 2.2 Pinouts8                                                                                                                        | 4.2 Power-Up/Down Operation25                                                     |

| 2.3 Memory Blocking Organization10                                                                                                  | 4.2.1 RP# Connected to System Reset25                                             |

| 2.3.1 One 16-KB Boot Block10                                                                                                        | 4.3 Board Design25                                                                |

| 2.3.2 Two 8-KB Parameter Blocks10                                                                                                   | 4.3.1 Power Supply Decoupling25                                                   |

| 2.3.3 Main Blocks - One 96-KB + Additional 128-KB Blocks                                                                            | 4.3.2 VPP Trace on Printed Circuit Boards25                                       |

| 120-ND DIOCKS10                                                                                                                     | 5.0 ELECTRICAL SPECIFICATIONS26                                                   |

| 3.0 PRINCIPLES OF OPERATION13                                                                                                       | 5.1 Absolute Maximum Ratings26                                                    |

| 3.1 Bus Operations13                                                                                                                | 5.2 Operating Conditions26                                                        |

| 3.1.1 Read13                                                                                                                        | 5.3 Capacitance27                                                                 |

| 3.1.2 Output Disable                                                                                                                | 5.4 DC Characteristics—Commercial and Extended Temperature27                      |

| 3.1.4 Word/Byte Configuration14                                                                                                     | 5.5 AC Characteristics—Read Operations—<br>Commercial and Extended Temperature31  |

| 3.1.5 Deep Power-Down/Reset14 3.1.6 Write14                                                                                         | 5.6 Erase and Program Timings—Commercial and Extended Temperature32               |

| 3.2 Modes of Operation                                                                                                              | 5.7 AC Characteristics—Write Operations—<br>Commercial and Extended Temperature33 |

| 3.2.2 Read Identifier       16         3.2.3 Read Status Register       16                                                          | 6.0 ORDERING INFORMATION35                                                        |

| 3.2.4 Word/Byte Program17                                                                                                           | 7.0 ADDITIONAL INFORMATION36                                                      |

| 3.2.5 Block Erase17                                                                                                                 | ADDENDIV A. Maita Ctata Maskins, Comment                                          |

| 3.3 Boot Block Locking23 3.3.1 $V_{PP} = V_{IL}$ for Complete Protection24                                                          | APPENDIX A: Write State Machine: Current-<br>Next State Chart37                   |

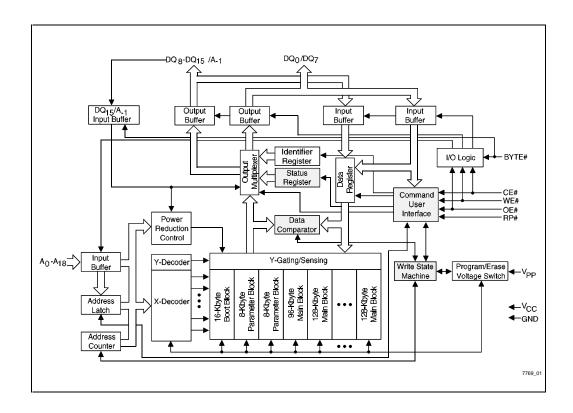

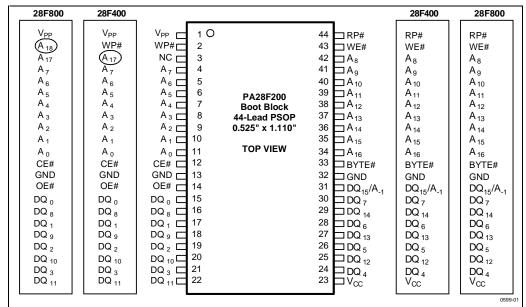

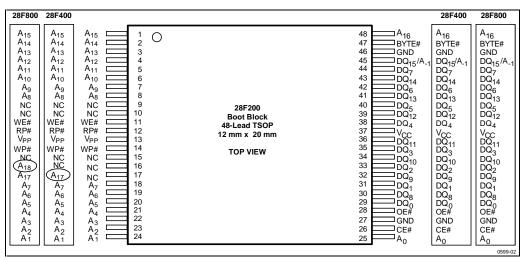

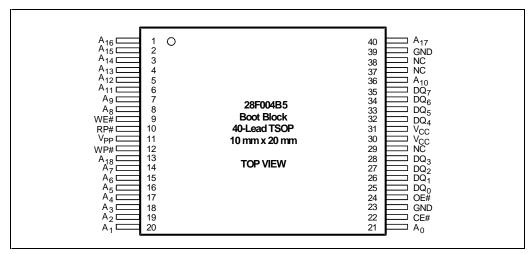

| 3.3.2 WP# = $V_{\parallel L}$ for Boot Block Locking24                                                                              | APPENDIX B: Product Block Diagram38                                               |

| 3.3.3 RP# = V <sub>II</sub> for Boot Block Locking24 3.3.3 RP# = V <sub>H</sub> or WP# = V <sub>II</sub> for Boot Block Unlocking24 | •                                                                                 |

| 3.3.4 Note for 8-Mbit 44-PSOP Package24                                                                                             |                                                                                   |

#### **REVISION HISTORY**

| Number | Description                                                                                                                                                                                                                                                                                                                                |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -001   | Original Version                                                                                                                                                                                                                                                                                                                           |

| -002   | Minor changes throughout document. Section 3.1.5 and Figure 14 redone to clarify program/erase operation abort. Information added to Table 2, Figure 1, and Section 3.3 to clarify WP# on 8-Mbit, 44-PSOP. Read and Write Waveforms changed to numbered format. Typical numbers removed from DC Characteristics and Erase/Program Timings. |

| -003   | Minor text changes throughout document. Figure 1, 44-PSOP pinout: mistake on pin 3 on 2-Mbit pinout corrected from A <sub>17</sub> to NC. Specs t <sub>EHQZ</sub> and t <sub>GHQZ</sub> improved. Explanations of program/erase abort commands reworked in Table 6, Command Codes.                                                         |

| -004   | Specifications for 28F004B5 40-TSOP version added; Erase suspend text and flowchart updated for clarity (Section 3.2.5.1, Table 6, Figure 10)                                                                                                                                                                                              |

#### 1.0 INTRODUCTION

This datasheet contains specifications for 2-, 4-, and 8-Mbit Smart 5 boot block flash memories. Section 1.0 provides a feature overview. Sections 2.0, 3.0, and 4.0 describe the product and functionality. Section 5.0 details the electrical and timing specifications for both commercial and extended temperature operation. Finally, Sections 6.0 and 7.0 provide ordering and reference information.

#### 1.1 New Features in the Smart 5 Memory Products

The Smart 5 boot block flash memory family offers identical features with the BV/CV/BE/CE SmartVoltage products, except the Smart 5 boot block -B5 parts only support 5 V V<sub>CC</sub> read voltage.

The following differences distinguish the Smart 5 boot block products from their predecessors:

#### **SMART 5 BOOT BLOCK MEMORY FAMILY**

- A delay is required if the part is reset during an in-progress program or erase operation.

- On the fly word-byte mode switching is no longer supported. Word-byte mode must be configured at power-up and remain stable during operation.

- Write operations are no longer specified as WE#- or CE#-controlled in favor of a simpler "unified" write method, which is compatible with either of the old methods.

#### 1.2 Product Overview

The Smart 5 boot block memory family provides pinout-compatible flash memories at the 2-, 4-, and 8-Mbit densities. The 28F200B5, 28F400B5, and 28F800B5 can be configured to operate either in 16-bit or 8-bit bus mode, with the data divided into individually erasable blocks. The 28F004B5 provides 8-bit operation in a compact package.

Table 1. Smart 5 Boot Block Family: Feature Summary

| Feature                  |             | 28F200B5                       | 28F400B5                       | 28F800B5                     | 28F004B5                | Reference    |  |  |  |

|--------------------------|-------------|--------------------------------|--------------------------------|------------------------------|-------------------------|--------------|--|--|--|

| V <sub>CC</sub> Read V   | oltage      |                                | 5 V ± 5%, 5 V ± 10%            |                              |                         |              |  |  |  |

| V <sub>PP</sub> Prog/Era | ase Voltage | 5 \                            | / ± 10% or 12 V :              | ± 5%, auto-detec             | ted                     | Section 5.2  |  |  |  |

| Bus-width                |             | 8- or 16-bit                   | 8- or 16-bit                   | 8- or 16-bit                 | 8-bit                   | Table 2      |  |  |  |

| Speed (ns)               | Commercial  | 60,                            | 80                             | 70, 90                       | 60, 80                  | Section 5.6  |  |  |  |

|                          | Extended    | 80                             | 80                             | 90                           | not available           | Section 5.6  |  |  |  |

| Memory Arrangement       |             | x8: 256K x 8<br>x16: 128K x 16 | x8: 512K x 8<br>x16: 256K x 16 | x8: 1M x 8<br>x16: 512K x 16 | x8: 512K x 8            |              |  |  |  |

| Blocking                 | Boot        | 1 x 16 KB                      | 1 x 16 KB                      | 1 x 16 KB                    | 1 x 16 KB               | Section 2.3, |  |  |  |

|                          | Parameter   | 2 x 8 KB                       | 2 x 8 KB                       | 2 x 8 KB                     | 2 x 8 KB                | Figs. 4-7    |  |  |  |

|                          | Main        | 1 x 96 KB<br>1 x 128 KB        | 1 x 96 KB<br>3 x 128 KB        | 1 x 96 KB<br>7 x 128 KB      | 1 x 96 KB<br>3 x 128 KB |              |  |  |  |

| Boot Locatio             | n           | To                             |                                |                              |                         |              |  |  |  |

| Locking                  |             | Boot<br>All ot                 | Section 3.3                    |                              |                         |              |  |  |  |

| Operating Te             | emperature  | Commerci                       | Section 5.2                    |                              |                         |              |  |  |  |

| Erase Cyclin             | g           | 100,000 cyc                    |                                |                              |                         |              |  |  |  |

| Packages                 |             | 4                              | Figs. 1-2                      |                              |                         |              |  |  |  |

SmartVoltage technology enables fast factory programming and low-power designs. Specifically designed for 5 V systems, Smart 5 components support read operations at 5 V V<sub>CC</sub> and internally configure to program/erase at 5 V or 12 V. The 12 V V<sub>PP</sub> option renders the fastest program and erase performance which will increase your factory throughput. With the 5 V V<sub>PP</sub> option, V<sub>CC</sub> and V<sub>PP</sub> can be tied together for a simple 5 V design. In addition, the dedicated V<sub>PP</sub> pin gives complete data protection when V<sub>PP</sub>  $\leq$  V<sub>PPLK</sub>.

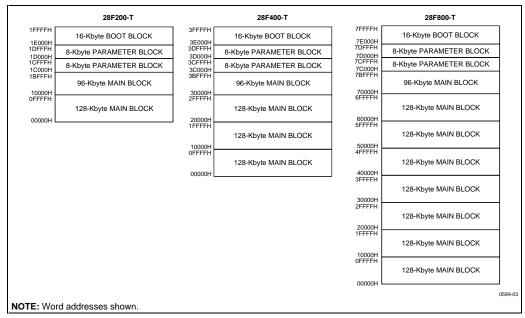

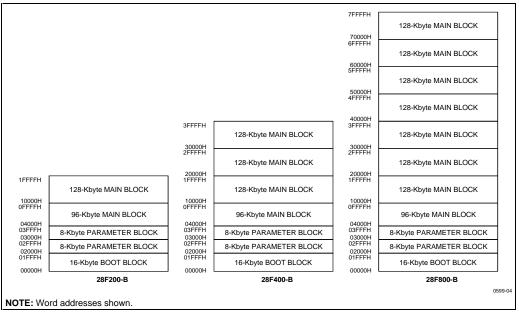

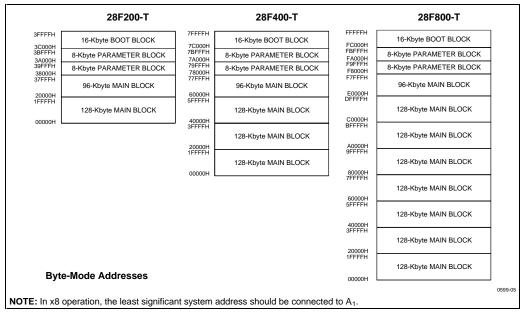

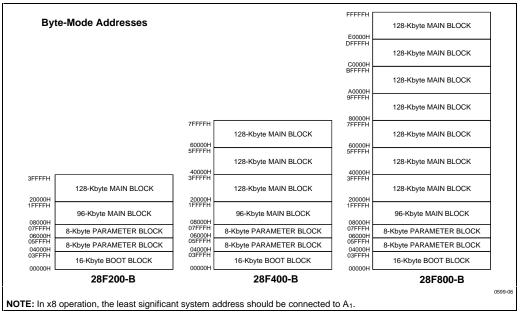

The memory array is asymmetrically divided into blocks in an asymmetrical architecture to accommodate microprocessors that boot from the top (denoted by -T suffix) or the bottom (-B suffix) of the memory map. The blocks include a hardware-lockable boot block (16,384 bytes), two parameter blocks (8,192 bytes each) and main blocks (one block of 98,304 bytes and additional block(s) of 131,072 bytes). See Figures 4–7 for memory maps. Each block can be independently erased and programmed 100,000 times at commercial temperature or 10,000 times at extended temperature. Unlike erase operations, which erase all locations within a block simultaneously, each byte or word in the flash memory can be programmed independently of other memory locations.

The hardware-lockable boot block provides complete code security for the kernel code required for system initialization. Locking and unlocking of the boot block is controlled by WP# and/or RP# (see Section 3.3 for details).

The system processor interfaces to the flash device through a Command User Interface (CUI), using valid command sequences to initiate device automation. An internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for program and erase operations. The Status Register (SR) indicates the status of the WSM and whether it successfully completed the desired program or erase operation.

The Automatic Power Savings (APS) feature substantially reduces active current when the device is in static mode (addresses not switching). In APS mode, the typical I<sub>CCR</sub> current is 1 mA.

When CE# and RP# pins are at  $V_{CC}$ , the component enters a CMOS standby mode. Driving RP# to GND enables a deep power-down mode which significantly reduces power consumption, provides write protection, resets the device, and clears the status register. A reset time ( $t_{PHCV}$ ) is required from RP# switching high until outputs are valid. Likewise, the device has a wake time ( $t_{PHEL}$ ) from RP#-high until writes to the CUI are recognized. See Section 4.2.

The deep power-down mode can also be used as a device reset, allowing the flash to be reset along with the rest of the system. For example, when the flash memory powers-up, it automatically defaults to the read array mode, but during a warm system reset, where power continues uninterrupted to the system components, the flash memory could remain in a non-read mode, such as erase. Consequently, the system Reset signal should be tied to RP# to reset the memory to normal read mode upon activation of the Reset signal. This also provides protection against unwanted command writes due to invalid system bus conditions during system reset or power-up/down sequences.

These devices are configurable at power-up for either byte-wide or word-wide input/output using the BYTE# pin. Please see Table 2 for a detailed description of BYTE# operations, especially the usage of the  $DQ_{15}/A_{-1}$  pin.

These Smart 5 memory products are available in the 44-lead PSOP (Plastic Small Outline Package), which is ROM/EPROM-compatible, and the 48-lead TSOP (Thin Small Outline Package, 1.2 mm thick) as shown in Figure 1, and 2, respectively.

#### 2.0 PRODUCT DESCRIPTION

This section describes the pinout and block architecture of the device family.

#### 2.1 Pin Descriptions

The pin descriptions table details the usage of each of the device pins.

Table 2. Pin Descriptions

| Symbol                            | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>18</sub>   | INPUT            | ADDRESS INPUTS for memory addresses. Addresses are internally latched during a write cycle. 28F200: A[0–16], 28F400: A[0–17], 28F800: A[0–18], 28F004: A[0–18]                                                                                                                                                                                                                                                                                               |

| A <sub>9</sub>                    | INPUT            | <b>ADDRESS INPUT:</b> When A <sub>9</sub> is at V <sub>HH</sub> the signature mode is accessed. During this mode, A <sub>0</sub> decodes between the manufacturer and device IDs. When BYTE# is at a logic low, only the lower byte of the signatures are read. $DQ_{15}/A_{-1}$ is a don't care in the signature mode when BYTE# is low.                                                                                                                    |

| DQ <sub>0</sub> -DQ <sub>7</sub>  | INPUT/<br>OUTPUT | DATA INPUTS/OUTPUTS: Inputs array data on the second CE# and WE# cycle during a Program command. Inputs commands to the Command User Interface when CE# and WE# are active. Data is internally latched during the write cycle. Outputs array, intelligent identifier and status register data. The data pins float to tri-state when the chip is de-selected or the outputs are disabled.                                                                    |

| DQ <sub>8</sub> -DQ <sub>15</sub> | INPUT/<br>OUTPUT | <b>DATA INPUTS/OUTPUTS:</b> Inputs array data on the second CE# and WE# cycle during a Program command. Data is internally latched during the write cycle. Outputs array data. The data pins float to tri-state when the chip is de-selected or the outputs are disabled as in the byte-wide mode (BYTE# = "0"). In the byte-wide mode $DQ_{15}/A_{-1}$ becomes the lowest order address for data output on $DQ_0-DQ_7$ . <b>Not applicable to 28F004B5.</b> |

| CE#                               | INPUT            | CHIP ENABLE: Activates the device's control logic, input buffers, decoders and sense amplifiers. CE# is active low. CE# high de-selects the memory device and reduces power consumption to standby levels. If CE# and RP# are high, but not at a CMOS high level, the standby current will increase due to current flow through the CE# and RP# input stages.                                                                                                |

| OE#                               | INPUT            | <b>OUTPUT ENABLE:</b> Enables the device's outputs through the data buffers during a read cycle. OE# is active low.                                                                                                                                                                                                                                                                                                                                          |

| WE#                               | INPUT            | WRITE ENABLE: Controls writes to the command register and array blocks. WE# is active low. Addresses and data are latched on the rising edge of the WE# pulse.                                                                                                                                                                                                                                                                                               |

| RP#                               | INPUT            | <b>RESET/DEEP POWER-DOWN:</b> Uses three voltage levels (V <sub>IL</sub> , V <sub>IH</sub> , and V <sub>HH</sub> ) to control two different functions: reset/deep power-down mode and boot block unlocking. It is backwards-compatible with the BX/BL/BV products.                                                                                                                                                                                           |

|                                   |                  | When RP# is at logic low, the device is in reset/deep power-down mode, which puts the outputs at High-Z, resets the Write State Machine, and draws minimum current.                                                                                                                                                                                                                                                                                          |

|                                   |                  | When RP# is at logic high, the device is in standard operation. When RP# transitions from logic-low to logic-high, the device defaults to the read array mode.                                                                                                                                                                                                                                                                                               |

|                                   |                  | When RP# is at V <sub>HH</sub> , the boot block is unlocked and can be programmed or erased. This overrides any control from the WP# input.                                                                                                                                                                                                                                                                                                                  |

Table 2. Pin Descriptions (Continued)

| Symbol          | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                       |

|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WP#             | INPUT | <b>WRITE PROTECT:</b> Provides a method for unlocking the boot block with a logic level signal in a system without a 12 V supply.                                                                                                                                                                                                       |

|                 |       | When WP# is at logic low, the boot block is locked, preventing program and erase operations to the boot block. If a program or erase operation is attempted on the boot block when WP# is low, the corresponding status bit (bit 4 for program, bit 5 for erase) will be set in the status register to indicate the operation failed.   |

|                 |       | When WP# is at logic high, the boot block is unlocked and can be programmed or erased.                                                                                                                                                                                                                                                  |

|                 |       | <b>NOTE:</b> This feature is overridden and the boot block unlocked when RP# is at $V_{HH}$ . This pin can not be left floating. Because the 8-Mbit 44-PSOP package does not have enough pins, it does not include this pin and thus 12 V on RP# is required to unlock the boot block. See Section 3.3 for details on write protection. |

| BYTE#           | INPUT | BYTE# ENABLE: Configures whether the device operates in byte-wide mode (x8) or word-wide mode (x16). This pin must be set at power-up or return from deep power-down and not changed during device operation. BYTE# pin must be controlled at CMOS levels to meet the CMOS current specification in standby mode.                       |

|                 |       | When BYTE# is at logic low, the byte-wide mode is enabled, where data is read and programmed on DQ0–DQ7 and DQ15/A-1 becomes the lowest order address that decodes between the upper and lower byte. DQ8–DQ14 are tri-stated during the byte-wide mode.                                                                                 |

|                 |       | When BYTE# is at logic high, the word-wide mode is enabled, where data is read and programmed on DQ0-DQ15.                                                                                                                                                                                                                              |

|                 |       | Not applicable to 28F004B5.                                                                                                                                                                                                                                                                                                             |

| V <sub>CC</sub> |       | DEVICE POWER SUPPLY: 5.0 V ± 10%                                                                                                                                                                                                                                                                                                        |

| V <sub>PP</sub> |       | <b>PROGRAM/ERASE POWER SUPPLY:</b> For erasing memory array blocks or programming data in each block, a voltage either of 5 V $\pm$ 10% or 12 V $\pm$ 5% must be applied to this pin. When V <sub>PP</sub> < V <sub>PPLK</sub> all blocks are locked and protected against Program and Erase commands.                                  |

| GND             |       | GROUND: For all internal circuitry.                                                                                                                                                                                                                                                                                                     |

| NC              |       | NO CONNECT: Pin may be driven or left floating.                                                                                                                                                                                                                                                                                         |

#### 2.2 Pinouts

Intel's Smart 5 boot block architecture provides upgrade paths in each package pinout up to the 8-Mbit density. The 44-lead PSOP pinout follows the industry-standard ROM/EPROM pinout, as shown in Figure 1. Designs with space concerns should consider the 48-lead pinout shown in Figure 2. Applications using an 8-bit bus can use the 40-lead TSOP, which is available for the 4-Mbit device only.

Pinouts for the corresponding 2-, 4-, and 8-Mbit components are provided on the same diagram for convenient reference. 2-Mbit pinouts are given on the chip illustration in the center, with 4-Mbit and 8-Mbit pinouts going outward from the center.

**NOTE:** Pin 2 is WP# on 2- and 4-Mbit devices but  $A_{18}$  on the 8-Mbit because no other pins were available for the high order address. Thus, the 8-Mbit in 44-PSOP cannot unlock the boot block without RP# =  $V_{HH}$ . See Section 3.3 for details. To allow upgrades to 8-Mbit from 2/4-Mbit in this package design pin 2 to control WP# at the 2/4-Mbit level and  $A_{18}$  at the 8-Mbit density.

Figure 1. 44-Lead PSOP Pinout Diagram

Figure 2. 48-Lead TSOP Pinout Diagram

Figure 3. 40-Lead TSOP Pinout Diagram (Available in 4-Mbit Only)

#### 2.3 Memory Blocking Organization

The boot block product family features an asymmetrically-blocked architecture providing system memory integration. Each erase block can be erased independently of the others up to 100,000 times for commercial temperature or up to 10,000 times for extended temperature. The block sizes have been chosen to optimize their functionality for common applications of nonvolatile storage. The combination of block sizes in the boot block architecture allow the integration of several memories into a single chip. For the address locations of the blocks, see the memory maps in Figures 4, 5, 6 and 7.

#### 2.3.1 ONE 16-KB BOOT BLOCK

The boot block is intended to replace a dedicated boot PROM in a microprocessor or microcontroller-based system. The 16-Kbyte (16,384 bytes) boot block is located at either the top (denoted by -T suffix) or the bottom (-B suffix) of the address map to accommodate different microprocessor protocols for boot code location. This boot block features hardware controllable write-protection to protect the crucial microprocessor boot code from accidental modification. The protection of the boot block is controlled using a combination of the V<sub>PP</sub>, RP#, and WP# pins, as is detailed in Section 3.3.

#### 2.3.2 TWO 8-KB PARAMETER BLOCKS

Each boot block component contains two parameter blocks of 8 Kbytes (8,192 bytes) each to facilitate storage of frequently updated small parameters that would normally require an EEPROM. By using software techniques, the byte-rewrite functionality of EEPROMs can be emulated. These techniques are detailed in Intel's application note, AP-604 Using Intel's Boot Block Flash Memory Parameter Blocks to Replace EEPROM. The parameter blocks are not write-protectable.

### 2.3.3 MAIN BLOCKS - ONE 96-KB + ADDITIONAL 128-KB BLOCKS

After the allocation of address space to the boot and parameter blocks, the remainder is divided into main blocks for data or code storage. Each device contains one 96-Kbyte (98,304 byte) block and additional 128-Kbyte (131,072 byte) blocks. The 2-Mbit has one 128-KB block; the 4-Mbit, three; and the 8-Mbit, seven.

Figure 4. Word-Wide x16-Mode Memory Maps (Top Boot)

Figure 5. Word-Wide x16-Mode Memory Maps (Bottom Boot)

Figure 6. Byte-Wide x8-Mode Memory Maps (Top Boot)

Figure 7. Byte-Wide x8-Mode Memory Maps (Bottom Boot)

#### 3.0 PRINCIPLES OF OPERATION

The system processor accesses the Smart 5 boot block memories through the Command User Interface (CUI), which accepts commands written with standard microprocessor write timings and TTL-level control inputs. The flash can be switched into each of its three read and two write modes through commands issued to the CUI. A comprehensive chart showing the state transitions is in Appendix A.

After initial device power-up or return from deep power-down mode, the device defaults to read array mode. In this mode, manipulation of the memory control pins allows array read, standby, and output disable operations. The other read modes, read identifier and read status register, can be reached by issuing the appropriate command to the CUI. Array data, identifier codes and status register results can be accessed using these commands independently from the  $V_{PP}$  voltage. Read identifier mode can also be accessed by PROM programming equipment by raising  $A_{9}$  to high voltage ( $V_{\text{ID}}$ ).

CUI commands sequences also control the write functions of the flash memory, Program and Erase. Issuing program or erase command sequences internally latches addresses and data and initiates Write State Machine (WSM) operations to execute the requested write function. The WSM internally regulates the program and erase algorithms, including pulse repetition, internal verification, and margining of data, freeing the host processor from these tasks and allowing precise control for high reliability. To execute Program or Erase commands, VPP must be at valid write voltage (5 V or 12 V).

While the WSM is executing a program operation, the device defaults to the read status register mode and all commands are ignored. Thus during the programming process, only status register data can be accessed from the device. While the WSM is executing a erase operation, the device also defaults to the read status register mode but one additional command is available, erase suspend to read, which will suspend the erase operation and allow reading of array data. The suspended erase operation can be completed by issuing the Erase Resume command. After the program or erase

#### **SMART 5 BOOT BLOCK MEMORY FAMILY**

operation has completed, the device remains in read status register mode. From this mode any of the other read or write modes can be reached with the appropriate command. For example, to read data, issue the Read Array command. Additional Program or Erase commands can also be issued from this state.

During program or erase operations, the array data is not available for reading or code execution, except during an erase suspend. Consequently, the software that initiates and polls progress of program and erase operations must be copied to and executed from system RAM during flash memory update. After successful completion, reads are again possible via the Read Array command.

Each of the device modes will be discussed in detail in the following sections.

#### 3.1 Bus Operations

The local CPU reads and writes flash memory insystem. All bus cycles to or from the flash memory conform to standard microprocessor bus cycles. Four control pins dictate the data flow in and out of the component: CE#, OE#, WE#, and RP#. These bus operations are summarized in Tables 3 and 4.

#### 3.1.1 READ

The flash memory has three read modes available, read array, read identifier, and read status. These read modes are accessible independent of the  $V_{PP}$  voltage. RP# can be at either  $V_{IH}$  or  $V_{HH}.$  The appropriate read-mode command must be issued to the CUI to enter the corresponding mode. Upon initial device power-up or after exit from deep power-down mode, the device automatically defaults to read array mode.

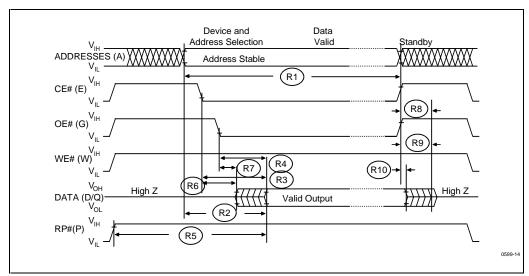

CE# and OE# must be driven active to obtain data at the outputs. CE# is the device selection control, and, when active, enables the selected memory device. OE# is the data output (DQ0–DQ15) control and when active drives the selected memory data onto the I/O bus. In read modes, WE# must be at  $V_{\rm IH}$  and RP# must be at  $V_{\rm IH}$  or  $V_{\rm HH}$ . Figure 15 illustrates a read cycle.

#### 3.1.2 OUTPUT DISABLE

With OE# at a logic-high level ( $V_{IH}$ ), the device outputs are disabled. Output pins (if available on the device) DQ<sub>0</sub>–DQ<sub>15</sub> are placed in a high-impedance state.

#### 3.1.3 STANDBY

Deselecting the device by bringing CE# to a logichigh level ( $V_{IH}$ ) places the device in standby mode which substantially reduces device power consumption. In standby, outputs DQ<sub>0</sub>–DQ<sub>15</sub> are placed in a high-impedance state independent of OE#. If deselected during program or erase operation, the device continues functioning and consuming active power until the operation completes.

#### 3.1.4 WORD/BYTE CONFIGURATION

The 16-bit devices can be configured for either an 8-bit or 16-bit bus width by setting the BYTE# pin before power-up. This is not applicable to the 8-bit only E28F004B5.

When BYTE# is set to logic low, the byte-wide mode is enabled, where data is read and programmed on  $DQ_0-DQ_7$  and  $DQ_{15}/A_{-1}$  becomes the lowest order address that decodes between the upper and lower byte.  $DQ_8-DQ_{14}$  are tri-stated during the byte-wide mode.

When BYTE# is at logic high, the word-wide mode is enabled, and data is read and programmed on DQ<sub>0</sub>-DQ<sub>15</sub>.

#### 3.1.5 DEEP POWER-DOWN/RESET

RP# at  $V_{\text{IL}}$  initiates the deep power-down mode, also referred to as reset mode.

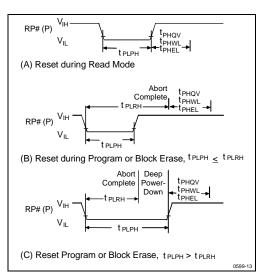

From read mode, RP# going low for time t<sub>PLPH</sub> deselects the memory, places output drivers in a high-impedance state, and turns off all internal circuits. After return from power-down, a time t<sub>PHQV</sub> is required until the initial memory access outputs are valid. A delay (t<sub>PHWL</sub> or t<sub>PHEL</sub>) is required after return from power-down before a write can be initiated. After this wake-up interval, normal

operation is restored. The CUI resets to read array mode, and the status register is set to 80H. This case is shown in Figure 14A.

If RP# is taken low for time  $t_{\text{PLPH}}$  during a program or erase operation, the operation will be aborted and the memory contents at the aborted location (for a program) or block (for an erase) are no longer valid, since the data may be partially erased or written. The abort process goes through the following sequence: When RP# goes low, the device shuts down the operation in progress, a process which takes time t<sub>PLRH</sub> to complete. After this time t<sub>PLRH</sub>, the part will either reset to read array mode (if RP# has gone high during tPLRH, Figure 14B) or enter deep power-down mode (if RP# is still logic low after t<sub>PLRH</sub>, Figure 14C). In both cases, after returning from an aborted operation, the relevant time tphQV or tphWL/tphEL must be waited before a read or write operation is initiated, as discussed in the previous paragraph. However, in this case, these delays are referenced to the end of tPLRH rather than when RP# goes high.

As with any automated device, it is important to assert RP# during system reset. When the system comes out of reset, processor expects to read from the flash memory. Automated flash memories provide status information when read during program or block erase operations. If a CPU reset occurs with no flash memory reset, proper CPU initialization may not occur because the flash memory may be providing status information instead of array data. Intel's Flash memories allow proper CPU initialization following a system reset through the use of the RP# input. In this application, RP# is controlled by the same RESET# signal that resets the system CPU.

#### 3.1.6 WRITE

The CUI does not occupy an addressable memory location. Instead, commands are written into the CUI using standard microprocessor write timings when WE# and CE# are low, OE# = V<sub>IH</sub>, and the proper address and data (command) are presented. The address and data for a command are latched on the rising edge of WE# or CE#, whichever goes high first. Figure 16 illustrates a write operation.

Table 3. Bus Operations for Word-Wide Mode (BYTE# = VIH)

| Mode                            | Notes | RP#             | CE#             | OE#             | WE#             | A <sub>9</sub>  | A <sub>0</sub>  | V <sub>PP</sub> | DQ <sub>0-15</sub> |

|---------------------------------|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------------|

| Read                            | 1,2,3 | $V_{IH}$        | $V_{IL}$        | $V_{IL}$        | V <sub>IH</sub> | Х               | Х               | Х               | D <sub>OUT</sub>   |

| Output Disable                  |       | $V_{IH}$        | $V_{IL}$        | V <sub>IH</sub> | V <sub>IH</sub> | Х               | Х               | Х               | High Z             |

| Standby                         |       | $V_{IH}$        | V <sub>IH</sub> | Х               | Х               | Х               | Х               | Х               | High Z             |

| Deep Power-Down                 | 9     | $V_{IL}$        | Х               | Х               | Х               | Х               | Х               | Х               | High Z             |

| Intelligent Identifier (Mfr.)   | 4     | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>ID</sub> | V <sub>IL</sub> | Х               | 0089 H             |

| Intelligent Identifier (Device) | 4,5   | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>ID</sub> | V <sub>IH</sub> | Х               | See<br>Table 4     |

| Write                           | 6,7,8 | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Х               | Х               | Х               | D <sub>IN</sub>    |

Table 4. Bus Operations for Byte-Wide Mode (BYTE# =  $V_{IL}$ )

| Mode                                  | Note  | RP#             | CE#             | OE#             | WE#             | A <sub>9</sub>  | A <sub>0</sub>  | A_1 | V <sub>PP</sub> | DQ <sub>0-7</sub> | DQ <sub>8-14</sub> (10) |

|---------------------------------------|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|-----------------|-------------------|-------------------------|

| Read                                  | 1,2,3 | $V_{IH}$        | $V_{IL}$        | $V_{IL}$        | V <sub>IH</sub> | Х               | Х               | Х   | Х               | D <sub>OUT</sub>  | High Z                  |

| Output<br>Disable                     |       | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Х               | Х               | Х   | Х               | High Z            | High Z                  |

| Standby                               |       | $V_{IH}$        | V <sub>IH</sub> | Х               | Х               | Х               | Х               | Х   | Х               | High Z            | High Z                  |

| Deep<br>Power-<br>Down                | 9     | V <sub>IL</sub> | Х               | Х               | Х               | Х               | Х               | Х   | Х               | High Z            | High Z                  |

| Intelligent<br>Identifier<br>(Mfr.)   | 4     | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>ID</sub> | $V_{IL}$        | Х   | Х               | 89H               | High Z                  |

| Intelligent<br>Identifier<br>(Device) | 4,5   | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>ID</sub> | V <sub>IH</sub> | Х   | Х               | See<br>Table 4    | High Z                  |

| Write                                 | 6,7,8 | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Х               | Х               | Х   | Х               | D <sub>IN</sub>   | High Z                  |

- 1. Refer to DC Characteristics.

- 2. X can be  $V_{\text{IL}},\,V_{\text{IH}}$  for control pins and addresses,  $V_{\text{PPLK}}$  or  $V_{\text{PPH}}$  for  $V_{\text{PP}}.$

- 3. See *DC Characteristics* for V<sub>PPLK</sub>, V<sub>PPH1</sub>, V<sub>PPH2</sub>, V<sub>HH</sub>, V<sub>ID</sub> voltages.

- 4. Manufacturer and device codes may also be accessed via a CUI write sequence,  $A_0$  selects, all other addresses = X.

- 5. See Table 4 for device IDs.

- 6. Refer to Table 6 for valid  $D_{\text{IN}}$  during a write operation.

- 7. Command writes for block erase or program are only executed when  $V_{PP} = V_{PPH1}$  or  $V_{PPH2}$ .

- 8. To program or erase the boot block, hold RP# at  $V_{HH}$  or WP# at  $V_{IH}$ . See Section 3.3.

- 9. RP# must be at GND  $\pm$  0.2 V to meet the maximum deep power-down current specified.

- 10. This column does not apply to the E28F004B5 since it is a x8-only device.

#### 3.2 Modes of Operation

The flash memory has three read modes and two write modes. The read modes are read array, read identifier, and read status. The write modes are program and block erase. An additional mode, erase suspend to read, is available only during block erasures. These modes are reached using the commands summarized in Table 5. A comprehensive chart showing the state transitions is in Appendix A.

#### 3.2.1 READ ARRAY

After initial device power-up or return from deep power-down mode, the device defaults to read array mode. This mode can also be entered by writing the Read Array command (FFH). The device remains in this mode until another command is written.

Data is read by presenting the address of the read location in conjunction with a read bus operation.

Once the WSM has started a program or block erase operation, the device will not recognize the Read Array command until the WSM completes its operation unless the WSM is suspended via an Erase Suspend command. The Read Array command functions independently of the  $V_{PP}$  voltage and RP# can be  $V_{IH}$  or  $V_{HH}$ .

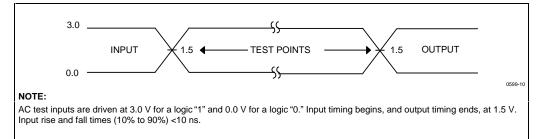

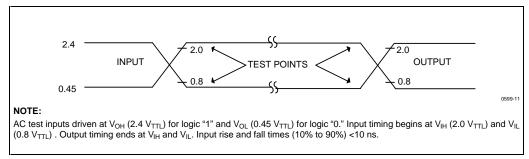

During system design, consideration should be taken to ensure address and control inputs meet required input slew rates of <10 ns as defined in Figures 11 and 12.

Table 4. Intelligent Identifier Codes

| Product | Mfr. ID | Device ID      |                   |  |  |  |

|---------|---------|----------------|-------------------|--|--|--|

|         |         | -T<br>Top Boot | -B<br>Bottom Boot |  |  |  |

| 28F004  | 89H     | 78H            | 79H               |  |  |  |

| 28F200  | 0089 H  | 2274 H         | 2275 H            |  |  |  |

| 28F400  | 0089 H  | 4470 H         | 4471 H            |  |  |  |

| 28F800  | 0089 H  | 889C H         | 889D H            |  |  |  |

#### NOTE:

In byte-mode, the upper byte will be tri-stated.

#### 3.2.2 READ IDENTIFIER

To read the manufacturer and device codes, the device must be in intelligent identifier read mode, which can be reached using two methods: by writing the intelligent identifier command (90H) or by taking the  $A_9$  pin to  $V_{\rm ID}.$  Once in intelligent identifier read mode,  $A_0=0$  outputs the manufacturer's identification code and  $A_0=1$  outputs the device code. In byte-wide mode, only the lower byte of the above signatures is read (DQ15/A $_{-1}$  is a "don't care" in this mode). See Table 4 for product signatures. To return to read array mode, write a Read Array command (FFH).

#### 3.2.3 READ STATUS REGISTER

The status register indicates when a program or erase operation is complete, and the success or failure of that operation. The status register is output when the device is read in read status register mode, which can be entered by issuing the Read Status (70H) command to the CUI. This mode is automatically entered when a program or erase operation is initiated, and the device remains in this mode after the operation has completed. Status register bit codes are defined in Table 7.

The status register bits are output on DQ0–DQ7, in both byte-wide (x8) or word-wide (x16) mode. In the word-wide mode, the upper byte, DQ8–DQ15, outputs 00H during a Read Status command. In the byte-wide mode, DQ8–DQ14 are tri-stated and DQ15/A $_1$  retains the low order address function.

Note that the contents of the status register are latched on the falling edge of OE# or CE#, whichever occurs last in the read cycle. This prevents possible bus errors which might occur if status register contents change while being read. CE# or OE# must be toggled with each subsequent status read, or the status register will not indicate completion of a program or erase operation.

Issue a Read Array (FFH) command to return to read array.

#### 3.2.3.1 Clearing the Status Register

Status register bits SR.5, SR.4, and SR.3 are set to "1"s when appropriate by the WSM but can only be reset by the Clear Status Register command. These bits indicate various failure conditions (see Table 7). By requiring system software to reset

these bits, several operations (such as cumulatively erasing multiple blocks or programming several bytes in sequence) may be performed before polling the status register to determine if an error occurred during the series.

Issue the Clear Status Register command (50H) to clear the status register. It functions independently of the applied  $V_{PP}$  voltage and RP# can be  $V_{IH}$  or  $V_{HH}.$  This command is not functional during block erase suspend modes. Resetting the part with RP# also clears the status register.

#### 3.2.4 WORD/BYTE PROGRAM

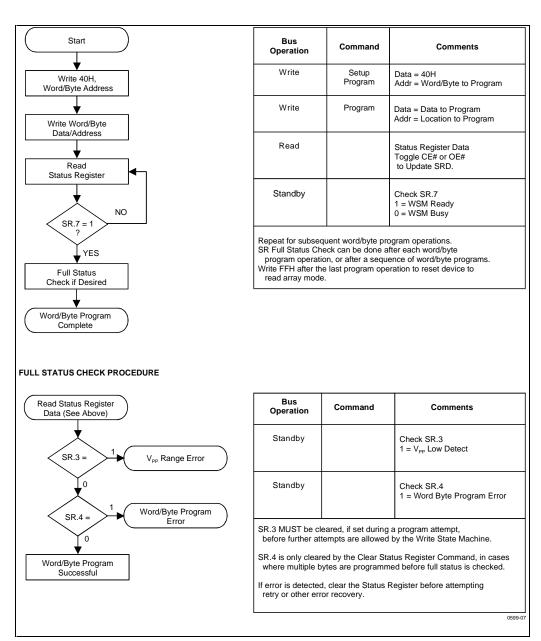

Word or byte program operations are executed by a two-cycle command sequence. Program Set-Up (40H) is issued, followed by a second write that specifies the address and data (latched on the rising edge of WE# or CE#, whichever comes first). The WSM then takes over, controlling the program and program verify algorithms internally. While the WSM is working, the device automatically enters read status register mode and remains there after the word/byte program is complete. (see Figure 8). The completion of the program event is indicated on status register bit SR.7.

When a word/byte program is complete, check status register bit SR.4 for an error flag ("1"). The cause of a failure may be found on SR.3, which indicates "1" if V<sub>PP</sub> was out of program/erase voltage range (V<sub>PPH1</sub> or V<sub>PPH2</sub>). The status register should be cleared before the next operation. The internal WSM verify only detects errors for "1"s that do not successfully write to "0"s.

Since the device remains in status register read mode after programming is completed, a command must be issued to switch to another mode before beginning a different operation.

#### 3.2.5 BLOCK ERASE

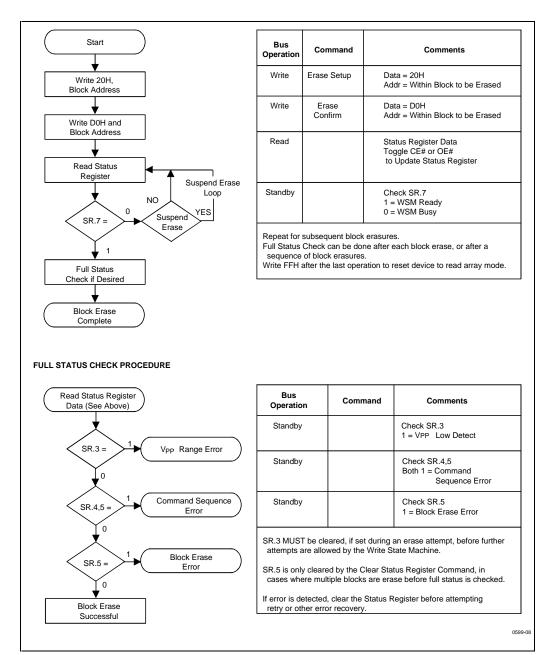

A block erase changes all block data to 1's (FFFFH) and is initiated by a two-cycle command. An Erase Set-Up command (20H) is issued first, followed by an Erase Confirm command (D0H) along with an address within the target block. The address will be latched at the rising edge of WE# or CE#, whichever comes first.

Internally, the WSM will program all bits in the block to "0," verify all bits are adequately programmed to

#### **SMART 5 BOOT BLOCK MEMORY FAMILY**

"0," erase all bits to "1," and verify that all bits in the block are sufficiently erased. After block erase command sequence is issued, the device automatically enters read status register mode and outputs status register data when read (see Figure 9). The completion of the erase event is indicated on status register bit SR.7.

When an erase is complete, check status register bit SR.5 for an error flag ("1"). The cause of a failure may be found on SR.3, which indicates "1" if  $V_{PP}$  was out of program/erase voltage range ( $V_{PPH1}$  or  $V_{PPH2}$ ). If an Erase Set-Up (20H) command is issued but not followed by an Erase Confirm (D0H) command, then both the program status (SR.4) and the erase status (SR.5) will be set to "1."

The status register should be cleared before the next operation. Since the device remains in status register read mode after erasing is completed, a command must be issued to switch to another mode before beginning a different operation.

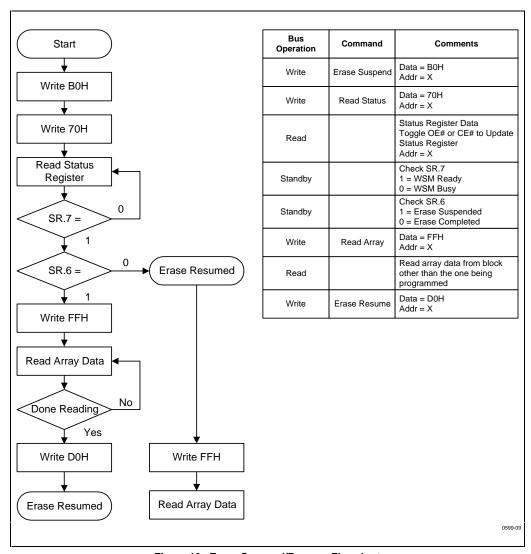

#### 3.2.5.1 Erase Suspend/Resume

The Erase Suspend command (B0H) interrupts an erase operation in order to read data in another block of memory. While the erase is in progress, issuing the Erase Suspend command requests that the WSM suspend the erase algorithm after a certain latency period. After issuing the Erase Suspend command, write the Read Status Register command, then check bit SR.7 and SR.6 to ensure the device is in the erase suspend mode (both will be set to "1"). This check is necessary because the WSM may have completed the erase operation before the Erase Suspend command was issued. If this occurs, the Erase Suspend command would switch the device into read array mode. See Appendix A for a comprehensive chart showing the state transitions

When erase has been suspended, a Read Array command (FFH) can be written to read from blocks other than that which is suspended. The only other valid commands at this time are Erase Resume (D0H) or Read Status Register.

During erase suspend mode, the chip can go into a pseudo-standby mode by taking CE# to  $V_{IH}$ , which reduces active current draw.  $V_{PP}$  must remain at  $V_{PPH1}$  or  $V_{PPH2}$  (the same  $V_{PP}$  level used for block erase) while erase is suspended. RP# must also remain at  $V_{IH}$  or  $V_{HH}$  (the same RP# level used for block erase).

To resume the erase operation, enable the chip by taking CE# to  $V_{\rm IL}$ , then issue the Erase Resume command, which continues the erase sequence to

completion. As with the end of a standard erase operation, the status register must be read, cleared, and the next instruction issued in order to continue.

**Table 5. Command Codes and Descriptions**

| Code | Device Mode                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00   | Invalid/<br>Reserved                 | Unassigned commands that should not be used. Intel reserves the right to redefine these codes for future functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FF   | Read Array                           | Places the device in read array mode, so that array data will be output on the data pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 40   | Program<br>Set-Up                    | Sets the CUI into a state such that the next write will load the Address and Data registers. The next write after the Program Set-Up command will latch addresses and data on the rising edge and begin the program algorithm. The device then defaults to the read status mode, where the device outputs status register data when OE# is enabled. To read the array, issue a Read Array command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |                                      | To cancel a program operation after issuing a Program Set-Up command, write all 1's (FFH for x8, FFFFH for x16) to the CUI. This will return to read status register mode after a standard program time without modifying array contents. If a program operation has already been initiated to the WSM this command cannot cancel that operation in progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10   | Alternate<br>Prog Set-Up             | (See 40H/Program Set-Up)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 20   | Erase<br>Set-Up                      | Prepares the CUI for the Erase Confirm command. If the next command is not an Erase Confirm command, then the CUI will set both the program status (SR.4) and erase status (SR.5) bits of the status register to a "1," place the device into the read status register state, and wait for another command without modifying array contents. This can be used to cancel an erase operation after the Erase Set-Up command has been issued. If an operation has already been initiated to the WSM this can not cancel that operation in progress.                                                                                                                                                                                                                                                                                                                                       |

| D0   | Erase<br>Resume/<br>Erase<br>Confirm | If the previous command was an Erase Set-Up command, then the CUI will latch address and data, and begin erasing the block indicated on the address pins. During erase, the device will respond only to the Read Status Register and Erase Suspend commands and will output status register data when OE# is toggled low. Status register data is updated by toggling either OE# or CE# low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| В0   | Erase<br>Suspend                     | Issuing this command will begin to suspend erase operation. The status register will indicate when the device reaches erase suspend mode. In this mode, the CUI will respond only to the Read Array, Read Status Register, and Erase Resume commands and the WSM will also set the WSM status bit to a "1" (ready). The WSM will continue to idle in the SUSPEND state, regardless of the state of all input control pins except RP#, which will immediately shut down the WSM and the remainder of the chip, if it is made active. During a suspend operation, the data and address latches will remain closed, but the address pads are able to drive the address into the read path. See Section 3.2.5.1. This command is useful only while an erase operation is in progress and may reset to read array mode in other circumstances. (See Appendix A for state transition table.) |

| 70   | Read Status<br>Register              | Puts the device into the read status register mode, so that reading the device outputs status register data, regardless of the address presented to the device. The device automatically enters this mode after program or erase has completed. This is one of the two commands that is executable while the WSM is operating. See Section 3.2.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 5. Command Codes and Descriptions (Continued)

| Code | Device Mode               | Description                                                                                                                                                                                                                                                                                                                                                                      |

|------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50   | Clear Status<br>Register  | The WSM can only set the program status and erase status bits in the status register to "1"; it cannot clear them to "0."                                                                                                                                                                                                                                                        |

|      |                           | The status register operates in this fashion for two reasons. The first is to give the host CPU the flexibility to read the status bits at any time. Second, when programming a string of bytes, a single status register query after programming the string may be more efficient, since it will return the accumulated error status of the entire string. See Section 3.2.3.1. |

| 90   | Intelligent<br>Identifier | Puts the device into the intelligent identifier read mode, so that reading the device will output the manufacturer and device codes. ( $A_0 = 0$ for manufacturer, $A_0 = 1$ for device, all other address inputs are ignored). See Section 3.2.2.                                                                                                                               |

**Table 6. Command Bus Definitions**

|                        |      | First Bus Cycle |      | Second Bus Cycle |       |      |      |

|------------------------|------|-----------------|------|------------------|-------|------|------|

| Command                | Note | Oper            | Addr | Data             | Oper  | Addr | Data |

| Read Array             |      | Write           | Х    | FFH              |       |      |      |

| Intelligent Identifier | 2,4  | Write           | Х    | 90H              | Read  | IA   | IID  |

| Read Status Register   | 3    | Write           | Х    | 70H              | Read  | Х    | SRD  |

| Clear Status Register  | 3    | Write           | Х    | 50H              |       |      |      |

| Word/Byte Program      | 6,7  | Write           | PA   | 40H/10H          | Write | PA   | PD   |

| Block Erase/Confirm    | 5    | Write           | ВА   | 20H              | Write | BA   | D0H  |

| Erase Suspend          |      | Write           | Х    | вон              |       |      |      |

| Erase Resume           |      | Write           | Х    | D0H              |       |      |      |

#### **ADDRESS**

DATA BA = Block Address SRD = Status Register Data IA = Identifier Address IID = Identifier Data PA = Program Address PD = Program Data

X = Don't Care

- 1. Bus operations are defined in Tables 3 and 4.

- 2.  $IA = Identifier Address: A_0 = 0$  for manufacturer code,  $A_0 = 1$  for device code.

- 3. SRD Data read from Status Register.

- 4. IID = Intelligent Identifier Data. Following the Intelligent Identifier command, two read operations access manufacturer and device codes.

- 5. BA = Address within the block being erased.

- 6. PA = Address to be programmed. PD = Data to be programmed at location PA.

- 7. Either 40H or 10H commands is valid.

- 8. When writing commands to the device, the upper data bus  $[DQ_8-DQ_{15}] = X$  which is either  $V_{IL}$  or  $V_{IH}$ , to minimize current

Table 7. Status Register Bit Definition

| WSMS | ESS | ES | DWS | VPPS | R | R | R |

|------|-----|----|-----|------|---|---|---|

| 7    | 6   | 5  | 4   | 3    | 2 | 1 | 0 |

|                                                                                                               | NOTES:                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SR.7 WRITE STATE MACHINE STATUS  1 = Ready (WSMS)  0 = Busy                                                   | Check WSM bit first to determine word/byte program or block erase completion, before checking program or erase status bits.                                                                                                                                                                                                                             |  |  |  |  |  |

| SR.6 = ERASE-SUSPEND STATUS (ESS)  1 = Erase Suspended  0 = Erase In Progress/Completed                       | When Erase Suspend is issued, WSM halts execution and sets both WSMS and ESS bits to "1." ESS bit remains set to "1" until an Erase Resume command is issued.                                                                                                                                                                                           |  |  |  |  |  |

| SR.5 = ERASE STATUS (ES) 1 = Error In Block Erasure                                                           | When this bit is set to "1," one of the following has occurred:                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0 = Successful Block Erase                                                                                    | 1. V <sub>PP</sub> out of range.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                                                                                               | <ol><li>WSM has applied the max number of erase<br/>pulses to the block and is still unable to verify<br/>successful block erasure.</li></ol>                                                                                                                                                                                                           |  |  |  |  |  |

|                                                                                                               | <ol><li>Erase Set-Up command was followed by a<br/>command other than Erase Confirm.</li></ol>                                                                                                                                                                                                                                                          |  |  |  |  |  |

| SR.4 = PROGRAM STATUS (DWS)  1 = Error in Byte/Word Program                                                   | When this bit is set to "1," one of the following has occurred:                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0 = Successful Byte/Word Program                                                                              | 1. V <sub>PP</sub> out of range.                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                                                                                               | <ol><li>WSM has applied the max number of program<br/>pulses and is still unable to verify a successful<br/>program.</li></ol>                                                                                                                                                                                                                          |  |  |  |  |  |

|                                                                                                               | <ol><li>Erase Set-Up command was followed by a<br/>command other than Erase Confirm.</li></ol>                                                                                                                                                                                                                                                          |  |  |  |  |  |