HS-3182

March 1997

## **ARINC 429 Bus Interface Line Driver Circuit**

#### **Features**

- TTL and CMOS Compatible Inputs

- Adjustable Rise and Fall Times via Two External Capacitors

- Programmable Output Differential Voltage via V<sub>REF</sub> Input

- Operates at Data Rates Up to 100 Kilobits/Sec

- Output Short Circuit Proof and Contains Over-Voltage Protection

- Outputs are Inhibited (0 Volts) If DATA (A) and DATA (B) Inputs are Both in the "Logic One" State

- DATA (A) and DATA (B) Signals are "AND'd" with Clock and Sync Signals

- Full Military Temperature Range

## Ordering Information

| PACKAGE | TEMPERATURE<br>RANGE | PART NUMBER    | PKG.<br>NO |

|---------|----------------------|----------------|------------|

| SBDIP   | -40°C to +85°C       | HS1-3182-9+    | D16.3      |

|         | -55°C to +125°C      | HS1-3182-8     | D16.3      |

| SMD#    | -55°C to +125°C      | 5962-8687901EA | D16.3      |

| CLCC    | -55°C to +125°C      | HS4-3182-8     | J28.A      |

| SMD#    | -55°C to +125°C      | 5962-86879013A | J28.A      |

## Description

The HS-3182 is a monolithic dielectrically isolated bipolar differential line driver designed to meet the specifications of ARINC 429. This Device is intended to be used with a companion chip, HS-3282 CMOS ARINC Bus Interface Circuit, which provides the data formatting and processor interface function.

All logic inputs are TTL and CMOS compatible. In addition to the DATA (A) and DATA (B) inputs, there are also inputs for CLOCK and SYNC signals which are AND'd with the DATA inputs. This feature enhances system performance and allows the HS-3182 to be used with devices other than the HS-3182.

Three power supplies are necessary to operate the HS-3182:  $+V = +15V \pm 10\%$ ,  $-V = -15V \pm 10\%$ , and  $V_1 = 5V \pm 5\%$ .  $V_{REF}$  is used to program the differential output voltage swing such that  $V_{OUT}$  (DIFF) =  $\pm$  2 $V_{REF}$ . Typically,  $V_{REF} = V_1 = 5V \pm 5\%$ , but a separate power supply may be used for  $V_{REF}$  which should not exceed 6V.

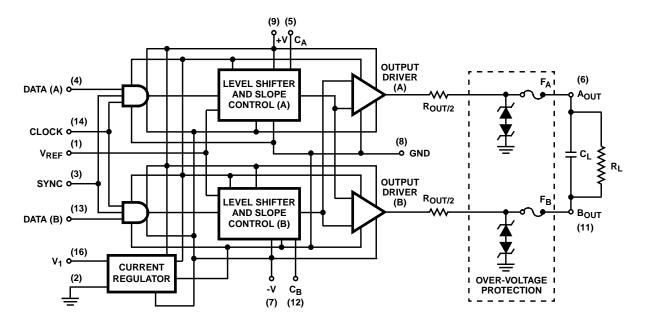

The driver output impedance is  $75\Omega\pm20\%$  at  $25^{o}C$ . Driver output rise and fall times are independently programmed through the use of two external capacitors connected to the  $C_A$  and  $C_B$  inputs. Typical capacitor values are  $C_A=C_B=75 \mathrm{pF}$  for high-speed operation (100KBPS), and  $C_A=C_B=300 \mathrm{pF}$  for low-speed operation (12 to 14.5KBPS). The outputs are protected against over-voltage and short circuit as shown in the Block Diagram. The HS-3182 is designed to operate with a case temperature range of -55°C to +125°C, or  $0^{o}C$  to  $+70^{o}C$ .

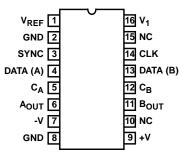

# Pinouts

#### **TRUTH TABLE**

| SYNC | CLK | DATA (A) | DATA (B) | A <sub>OUT</sub>  | B <sub>OUT</sub>  | COMMENTS |

|------|-----|----------|----------|-------------------|-------------------|----------|

| Х    | L   | Х        | Х        | 0V                | 0V                | Null     |

| L    | Х   | Х        | Х        | 0V                | 0V                | Null     |

| Н    | Н   | L        | L        | 0V                | 0V                | Null     |

| Н    | Н   | L        | Н        | -V <sub>REF</sub> | +V <sub>REF</sub> | Low      |

| Н    | Н   | Н        | L        | +V <sub>REF</sub> | -V <sub>REF</sub> | High     |

| Н    | Н   | Н        | Н        | 0V                | 0V                | Null     |

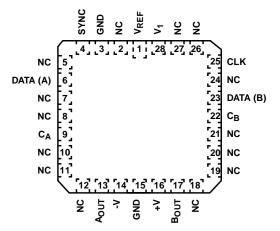

#### HS-3182 (CLCC) TOP VIEW

## **Block Diagram**

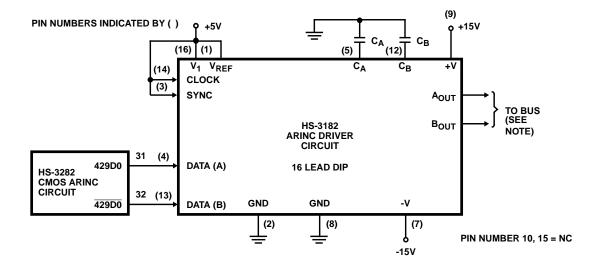

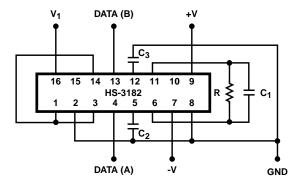

## **Typical Application**

NOTE: The rise and fall time of the outputs are set to ARINC specified values by  $C_A$  and  $C_B$ . Typical  $C_A = C_B = 75$ pF for high speed and 300pF for low speed operation. The output HI and low levels are set to ARINC specifications by  $V_{REF}$ .

#### HS-3182

#### **Absolute Maximum Ratings Thermal Information** Voltage Between +V and -V Terminals . . . . . . . . . . . . . . . . . 40V Thermal Resistance (Typical) $\theta_{\mathsf{JA}}$ $\theta$ JC 18<sup>0</sup>C/W CLCC Package . . . . . . . . . . . 60°C/W Logic Input Voltage . . . . . . . . . . . . . . . . . GND -0.3V to V<sub>1</sub> +0.3V Storage Temperature Range.....-65°C to +150°C Output Short Circuit Duration . . . . . . . . . . See Note 1 Maximum Lead Temperature (Soldering 10s)....+300°C Output Over-Voltage Protection . . . . . . . . . . See Note 2 Die Characteristics **Recommended Operating Conditions** Operating Voltage Operating Temperature Range HS-3182-8.....55°C to +125°C

#### NOTES:

- 1. Heat sink may be required for 100K bits/s at  $+125^{\circ}$ C and output short circuit at  $+125^{\circ}$ C.

- 2. The fuses used for output over-voltage protection may be blown by a fault at each output of greater than  $\pm$  6.5V relative to GND.

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **DC Electrical Performance Specifications**

| DC PARAMETER                                  | SYMBOL                                | (NOTE 1)<br>CONDITIONS  | MIN                           | MAX                           | UNITS |

|-----------------------------------------------|---------------------------------------|-------------------------|-------------------------------|-------------------------------|-------|

| Supply Current +V (Operating)                 | I <sub>CCOP</sub> (+V)                | No Load (0-100K bits/s) | -                             | 16                            | mA    |

| Supply Current -V (Operating)                 | I <sub>CCOP</sub> (-V)                | No Load (0-100K bits/s) | -16                           | -                             | mA    |

| Supply Current V <sub>1</sub> (Operating)     | I <sub>CCOP</sub> (V <sub>1</sub> )   | No Load (0-100K bits/s) | -                             | 975                           | μΑ    |

| Supply Current V <sub>REF</sub> (Operating)   | I <sub>CCOP</sub> (V <sub>REF</sub> ) | No Load (0-100K bits/s) | -1.0                          | -                             | mA    |

| Logic "1" Input Voltage                       | V <sub>IH</sub>                       |                         | 2.0                           | -                             | V     |

| Logic "0" Input Voltage                       | V <sub>IL</sub>                       |                         | -                             | 0.5                           | V     |

| Output Voltage High (Output to GND)           | V <sub>OH</sub>                       | No Load (0-100K bits/s) | V <sub>REF</sub><br>(-250mV)  | V <sub>REF</sub><br>(+250mV)  |       |

| Output Voltage Low (Output to GND)            | V <sub>OL</sub>                       | No Load (0-100K bits/s) | -V <sub>REF</sub><br>(-250mV) | -V <sub>REF</sub><br>(+250mV) |       |

| Output Voltage Null                           | V <sub>NULL</sub>                     | No Load (0-100K bits/s) | -250                          | +250                          | mV    |

| Input Current (Input Low)                     | I <sub>IL</sub>                       |                         | -20                           | -                             | μΑ    |

| Input Current (Input High)                    | I <sub>IH</sub>                       |                         | -                             | 10                            | μΑ    |

| Output Short Circuit Current<br>(Output High) | loнsс                                 | Short to GND            | -                             | -80                           | mA    |

| Output Short Circuit Current (Output Low)     | l <sub>OLSC</sub>                     | Short to GND            | 80                            | -                             | mA    |

| Output Impedance                              | z <sub>O</sub>                        | $T_A = +25^{\circ}C$    | 60                            | 90                            | Ω     |

#### NOTE:

<sup>1.</sup>  $+V = +15V \pm 10\%$ ,  $-V = -15V \pm 10\%$ ,  $V_1 = V_{REF} = 5V \pm 5\%$ , unless otherwise specified  $T_A = 0^{O}C$  to  $+70^{O}C$  for HS-3182-5 and  $T_A = -55^{O}C$  to  $+125^{O}C$  for HS-3182-8.

## **AC Electrical Performance Specifications**

| AC PARAMETER                                     | SYMBOL           | (NOTE 1)<br>CONDITIONS                          | MIN | MAX | UNITS |

|--------------------------------------------------|------------------|-------------------------------------------------|-----|-----|-------|

| Rise Time (A <sub>OUT</sub> , B <sub>OUT</sub> ) | t <sub>R</sub>   | C <sub>A</sub> = C <sub>B</sub> = 75pF, Note 2  | 1   | 2   | μS    |

|                                                  |                  | (at T <sub>A</sub> = -55°C Only)                | 0.9 | 2.4 | μS    |

|                                                  |                  | C <sub>A</sub> = C <sub>B</sub> = 300pF, Note 2 | 3   | 9   | μS    |

| Fall Time (A <sub>OUT</sub> , B <sub>OUT</sub> ) | t <sub>F</sub>   | C <sub>A</sub> = C <sub>B</sub> = 75pF, Note 3  | 1   | 2   | μS    |

|                                                  |                  | (at T <sub>A</sub> = -55°C Only)                | 0.9 | 2.4 | μS    |

|                                                  |                  | C <sub>A</sub> = C <sub>B</sub> = 300pF, Note 3 | 3   | 9   | μS    |

| Propagation Delay Input to Output                | t <sub>PLH</sub> | C <sub>A</sub> = C <sub>B</sub> = 75pF, No Load | -   | 3.3 | μS    |

| Propagation Delay Input to Output                | t <sub>PHL</sub> | C <sub>A</sub> = C <sub>B</sub> = 75pF, No Load | -   | 3.3 | μS    |

#### NOTES:

- 1. +V = +15V, -V = -15V,  $V_1 = V_{REF} = 5V$ , unless otherwise specified  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  for HS-3182-5 and  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$  for HS-3182-8.

- 2. t<sub>R</sub> measured 50% to 90% times 2, no load.

- 3.  $t_F$  measured 50% to 10% times 2, no load.

## **Electrical Performance Specifications**

| PARAMETER                         | SYMBOL               | (NOTE 1)<br>CONDITIONS                            | MIN  | MAX | UNITS |

|-----------------------------------|----------------------|---------------------------------------------------|------|-----|-------|

| Input Capacitance                 | C <sub>IN</sub>      | $T_A = +25^{\circ}C$                              | -    | 15  | pF    |

| Supply Current +V (Short Circuit) | I <sub>SC</sub> (+V) | Short to GND, $T_A = +25^{\circ}C$                | -    | 150 | mA    |

| Supply Current -V (Short Circuit) | I <sub>SC</sub> (-V) | Short to GND, T <sub>A</sub> = +25 <sup>o</sup> C | -150 | -   | mA    |

#### NOTE:

## Power Specifications Nominal Power at +25°C, +V = +15V, -V = -15V, V1 = V<sub>REF</sub> = 5V, Notes 1, 3

| DATA RATE<br>(K BITS/s) | LOAD              | +V   | V-    | V <sub>1</sub> | CHIP POWER | POWER DISSIPATION<br>IN LOAD |

|-------------------------|-------------------|------|-------|----------------|------------|------------------------------|

| 0-100                   | No Load           | 11mA | -10mA | 600μΑ          | 325mW      | 0                            |

| 12.5-14                 | Full Load, Note 2 | 24mW | -24mW | 600μΑ          | 660mW      | 60mW                         |

| 100                     | Full Load, Note 2 | 46mW | -46mW | 600μΑ          | 1 Watt     | 325mW                        |

#### NOTES:

1. Heat sink may be required for 100K bits/s at +125°C and output short circuit at +125°C.

Thermal characteristics:  $T_{(CASE)} = T_{(Junction)} - \theta_{(Junction - Case)} P_{(Dissipation)}$

Where:  $T_{(Junction Max)} = +175^{\circ}C$

$\theta_{\text{(Junction - Case)}} = 10.9^{\circ}\text{C/W} (6.1^{\circ}\text{C/W for LCC})$

$\theta$ (Junction - Ambient) = 73.5°C/W (54.0°C/W for LCC)

- 2. Full Load for ARINC 429:  $R_L = 400\Omega$  and  $C_L = 30,000 pF$  in parallel between  $A_{OUT}$  and  $B_{OUT}$  (see block diagram).

- 3. Output Over-Voltage Protection: The fuses used for output over-voltage protection may be blown by a fault at each output of greater than ±6.5V relative to GND.

<sup>1.</sup> The parameters listed in Table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design and after major process and/or design changes affecting these parameters.

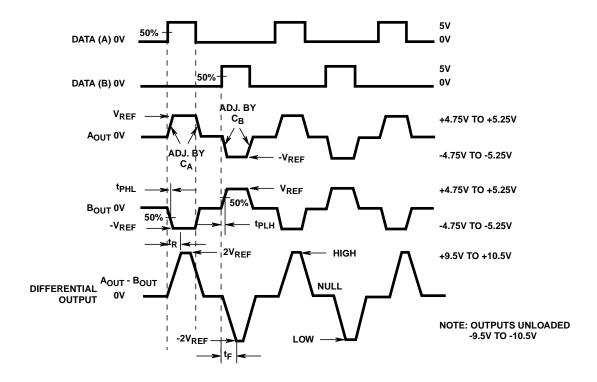

#### **Driver Waveforms**

NOTES:  $t_R$  measured 50% to 90% times 2

t<sub>F</sub> measured 50% to 10% times 2

$V_{IH} = 5V$   $V_{OL} = -4.75V$  to -5.25V

$V_{IL} = 0V$   $V_{OH} = 4.75V \text{ to } 5.25V$

When the Data (A) input is in the Logic One state and the Data (B) input is in the Logic Zero state,  $A_{OUT}$  is equal to  $V_{REF}$  and  $B_{OUT}$  is equal to - $V_{REF}$ . This constitutes the Output High state. Data (A) and Data (B) both in the Logic Zero state causes both  $A_{OUT}$  and  $B_{OUT}$  to be equal to 0V which designates the output Null state. Data (A) in the Logic Zero state and Data (B) in the Logic One state causes  $A_{OUT}$  to be equal to - $V_{REF}$  and  $B_{OUT}$  to be equal to  $V_{REF}$  which is the Output Low state.

$V_{IH}$

٧<sub>IL</sub>

$V_{IH}$

٧<sub>IL</sub>

#### Burn-In Schematic

В\_\_\_\_\_

NOTES:  $R = 400\Omega \pm 5\%$

$C_1 = 0.03 \mu F \pm 20\%$

$C_2 = C_3 = 500 pF, NPO$

$+V = +15.5V \pm 0.5V$

$-V = -15.5V \pm 0.5V$

$V_1 = +5.5V \pm 0.5V$

A  $0.0\mu F$  decoupling capacitor is required on each of the three supply lines (+V, -V and V<sub>1</sub>) at every 3rd Burn-In socket.

Ambient Temp. Max. =  $+125^{\circ}$ C.

Package = 16 Lead Side Brazed DIP.

Pulse Conditions = A & B = 6.25kHz  $\pm$  10%. B is delayed one-half cycle and in sync with A.

$V_{IH} = 2.0V Min.$

$V_{IL} = 0.5V Max.$

| All Intersil semiconductor pro                                                      | ducts are manufactured, assembled                                                                         | and tested under ISO9000 quality systems                                                                                                                                             | certification.    |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| notice. Accordingly, the reader is caution and reliable. However, no responsibility | ned to verify that data sheets are current before<br>is assumed by Intersil or its subsidiaries for its u | make changes in circuit design and/or specifications a<br>placing orders. Information furnished by Intersil is believ<br>se; nor for any infringements of patents or other rights of | ed to be accurate |

|                                                                                     | anted by implication or otherwise under any pate<br>mation regarding Intersil Corporation and its proc    | <u> </u>                                                                                                                                                                             |                   |

| Sales Office Headqua                                                                |                                                                                                           | ,                                                                                                                                                                                    |                   |

| NORTH AMERICA                                                                       | EUROPE                                                                                                    | ASIA                                                                                                                                                                                 |                   |

| Intersil Corporation                                                                | Intersil SA                                                                                               | Intersil (Taiwan) Ltd.                                                                                                                                                               |                   |

P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000

FAX: (407) 724-7240

Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

Taiwan Limited 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029