February 1998

### **Binary Correlator**

#### Features

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- Reconfigurable 256 Stage Binary Correlator

- 1-Bit Reference x 1, 2, 4, or 8-Bit Data

- Separate Control and Reference Interfaces

- Configurable for 1-D and 2-D Operation

- Double Buffered Mask and Reference

- · Programmable Output Delay

- Cascadable

- Standard Microprocessor Interface

### **Applications**

- · Radar/Sonar

- Spread Spectrum Communications

- · Pattern/Character Recognition

- Error Correction Coding

#### Ordering Information

| PART NUMBER       | TEMP.<br>RANGE (°C) | PACKAGE   | PKG.<br>NO. |

|-------------------|---------------------|-----------|-------------|

| HSP45256GM-20/883 | -55 to 125          | 85 Ld PGA |             |

| HSP45256GM-25/883 | -55 to 125          | 85 Ld PGA |             |

#### Description

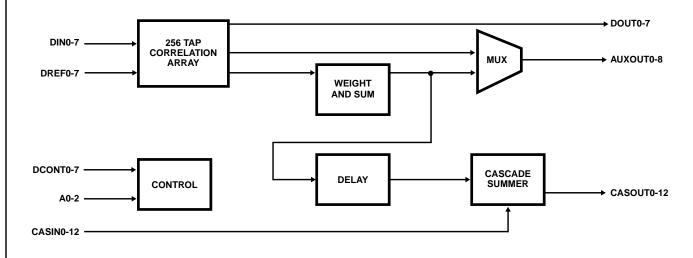

The Intersil HSP45256/883 is a high-speed, 256 tap binary correlator. It can be configured to perform one-dimensional or two-dimensional correlations of selectable data precision and length. Multiple HSP45256's can be cascaded for increased correlation length. Unused taps can be masked out for reduced correlation length.

The correlation array consists of eight 32-tap stages. These may be cascaded internally to compare 1, 2, 4 or 8-bit input data with a 1-bit reference. Depending on the number of bits in the input data, the length of the correlation can be up to 256, 128, 64, or 32 taps. The HSP45256 can also be configured as two separate correlators with window sizes from 4 by 32 to 1 by 128 each. The Mask Register can be used to prevent any subset of the 256 bits from contributing to the correlation score.

The9- output of the correlation array (correlation score) feeds the weight and sum logic, which gives added flexibility to the data format. In addition, an offset register is provided so that a preprogrammed value can be added to the correlation score. This result is then passed through a user programmable delay stage to the cascade summer. The delay stage simplifies the cascading of multiple correlators by compensating for the latency of previous correlators.

The Binary Correlator is configured by writing a set of control registers via a standard microprocessor interface. To simplify operation, both the Control and Reference Registers are double buffered. This allows the user to load new mask and reference data while the current correlation is in progress.

### Block Diagram

| uts |     |            |                       |                       |            |             |                    |                 |                 |                 |                 |                  |

|-----|-----|------------|-----------------------|-----------------------|------------|-------------|--------------------|-----------------|-----------------|-----------------|-----------------|------------------|

| นเร |     |            |                       |                       |            |             | PIN PG             |                 |                 |                 |                 |                  |

|     | г   | 1          | 2                     | 3                     | 4          | 5           | 6                  | 7               | 8<br>CAS        | 9               | 10              | 11<br>CAS        |

|     | A C | CASIN<br>2 | CASIN<br>4            | CASIN<br>5            | CASIN<br>7 | CASIN<br>10 | CASIN<br>11        | CAS<br>OUT<br>0 | OUT<br>3        | CAS<br>OUT<br>5 | GND             | OUT<br>8         |

|     | В   | GND        | CASIN<br>1            | CASIN<br>3            | CASIN<br>6 | CASIN<br>9  | CAS<br>OUT<br>2    | CAS<br>OUT<br>1 | CAS<br>OUT<br>4 | CAS<br>OUT<br>6 | CAS<br>OUT<br>7 | CAS<br>OUT<br>10 |

|     | С   | CLK        | CASIN<br>0            | INDEX<br>PIN          |            | CASIN<br>8  | CASIN<br>12        | OEC             |                 |                 | CAS<br>OUT<br>9 | CAS<br>OUT<br>11 |

|     | D   | DIN7       | v <sub>cc</sub>       |                       |            |             |                    |                 |                 |                 | GND             | CAS<br>OUT<br>12 |

|     | E   | DIN4       | DIN5                  | DIN6                  |            |             |                    |                 |                 | DOUT0           | DOUT1           | DOUT2            |

|     | F   | DREF<br>6  | DIN3                  | DIN2                  |            |             |                    |                 |                 | DOUT<br>4       | DOUT<br>7       | DOUT<br>3        |

|     | G   | DIN0       | DREF<br>7             | DIN1                  |            |             |                    |                 |                 | v <sub>cc</sub> | DOUT<br>6       | DOUT<br>5        |

|     | н   | DREF<br>5  | DREF<br>4             |                       | ı          |             |                    |                 |                 |                 | AUX<br>OUT<br>1 | AUX<br>OUT<br>0  |

|     | J   | DREF<br>3  | DREF<br>1             |                       |            | <b>A</b> 1  | DCONT<br>5         | DCONT<br>4      |                 | ,               | GND             | AUX<br>OUT<br>2  |

|     | ĸ l | DREF<br>2  | v <sub>cc</sub>       | R<br>LOAD             | C<br>LOAD  | Α0          | DCONT<br>6         | DCONT<br>2      | ŌĒĀ             | AUX<br>OUT<br>6 | AUX<br>OUT<br>4 | AUX<br>OUT<br>3  |

|     | ַ ן | DREF<br>0  | GND                   | TXFR                  | A2         | DCONT<br>7  | DCONT<br>1         | DCONT<br>3      | DCONT<br>0      | ALIV            | AUX<br>OUT<br>7 | AUX<br>OUT<br>5  |

|     | L   |            |                       |                       |            |             | PIN PGA<br>Fom Vie |                 |                 |                 |                 |                  |

|     |     |            | $\overline{\bigcirc}$ | $\overline{\bigcirc}$ |            |             |                    |                 |                 |                 |                 |                  |

| L   | DRE |            | GND                   | TXFR                  | O<br>A2    | DCONT<br>7  | DCONT              | DCONT<br>3      | DCONT           | 0 AUXOU         | T AUXO          | UT AUXOU         |

| К   | DRE |            | O<br>Vcc F            | CLOAD                 | CLOAD      | O<br>A0     | DCONT<br>6         | DCONT 2         | OEA             | AUXOUT          | AUXO            | UT AUXOL         |

| J   | DRE | -          | OREF1                 |                       |            | O<br>A1     | DCONT              | DCONT           |                 |                 | GND             |                  |

| н   | DRE | )          | O<br>REF4             |                       |            |             | 5                  | 4               |                 |                 | AUXO            | UT AUXO          |

| G   | c   |            | 0                     | 0                     |            |             |                    |                 |                 | 0               | O               | Ô                |

| F   | C   | )          | 0                     | DIN1                  |            |             |                    |                 |                 | v <sub>cc</sub> | О               | 0                |

| E   | DRE | )          | 0                     | OIN2                  |            |             |                    |                 |                 | DOUT4           | 0               | 0                |

| D   | C   | )          | 0                     | DIN6                  |            |             |                    |                 |                 | DOUT0           | 0               | 0                |

| С   | DIN | _          | v <sub>cc</sub>       | $\cap$                |            | $\circ$     | $\circ$            | $\bigcirc$      |                 |                 | GND             | CASÕU<br>12      |

|     | CL  | K C        | ASINO I               | NDEX<br>PIN           | _          | CASIN<br>8  | CASIN<br>12        | OEC             | _               | _               | CASOL<br>9      | T CASOL          |

| В   | GN  |            |                       | ASIN3                 | CASIN6     | CASIN 9     | CASOUT 2           | CASOUT          | CASOU 4         | T CASOU         | r CASOL         | T CASOL          |

| А   | CAS | SIN C      |                       |                       | CASIN      | CASIN       | CASIN              | CASOUT          | CASOUT          | CASOU           | T GND           |                  |

|     | 1   |            | 2                     | 3                     | 7<br>4     | 10<br>5     | 11<br>6            | 7               | 8               | 9               | 10              | 11               |

## Pin Description

| SYMBOL          | PIN NUMBER                              | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|-----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> | D2, G9, K2                              |      | The +5V power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GND             | A10, B1, D10,<br>J10, L2                |      | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DIN0-7          | D1, E1-E3, F2,<br>F3, G1, G3            | I    | The DIN0-7 bus consists of eight single data input pins. The assignment of the active pins is determined by the configuration. Data is loaded synchronous to the rising edge of CLK. DIN0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DOUT0-7         | E9-E11, F9-F11,<br>G10, G11             | 0    | The DOUT0-7 bus is the data output of the correlation array. The format of the output is dependent on the window configuration and bit weighting. DOUT0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CLK             | C1                                      | I    | System Clock. Positive edge triggered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CASIN0-12       | A1-A6, B2-B5,<br>C2, C5, C6             | I    | CASIN0-12 allows multiple correlators to be cascaded by connecting CASOUT0-12 of one correlator to CASIN0-12 of another. The CASIN bus is added internally to the correlation score to form CASOUT. CASIN0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CASOUT0-12      | A7-A9, A11,<br>B6-B11, C10,<br>C11, D11 | O    | CASOUT0-12 is the output correlation score. This value is the delayed sum of all the 256 taps of one chip and CASIN0-12. When the part is configured to act as two independent correlators, CASOUT0-8 represents the correlation score for the first correlator while the second correlation score is available on the AUXOUT0-8 bus. In this configuration, the cascading feature is no longer an option. CASOUT0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                             |

| ŌĒĊ             | C7                                      | I    | OEC is the output enable for CASOUT0-12. When OEC is high, the output is three-stated. Processing is not interrupted by this pin (active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TXFR            | L3                                      | I    | TXFR is a synchronous clock enable signal that allows the loading of the reference and mask inputs from the preload register to the correlation array. Data is transferred on the rising edge of CLK while TXFR is low (active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DREF0-7         | F1, G2, H1, H2,<br>J1, J2, K1, L1       | I    | DREF0-7 is an 8-bit wide data reference input. This is the input data bus used to load the reference data. RLOAD going active initiates the loading of the reference registers. This input bus is used to load the reference registers of the correlation array. The manner in which the reference data is loaded is determined by the window configuration. If the window configuration is 1 x 256, the reference bits are loaded one at a time over DREF7. When the HSP45256 is configured as an 8 x 32 array, the data is loaded into all stages in parallel. In this case, DREF7 is the reference data for the first stage and DREF0 is the reference data for the eighth stage. The contents of the reference data registers are not affected by changing the window configuration. DREF0 is the LSB. |

| RLOAD           | К3                                      | I    | RLOAD enables loading of the reference registers. Data on DREF0-7 is loaded into the preload registers on the rising edge of RLOAD. This data is transferred into the correlation array by TXFR (active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DCONT0-7        | J6, J7, K6, K7,<br>L5-L8                | I    | DCONT0-7 is the control data input, which is used to load the mask bit for each tap as well as the configuration registers. The mask data is sequentially loaded into the eight stages in the same manner as the reference data. DCONT0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CLOAD#          | K4                                      | I    | CLOAD enables the loading of the data on DCONT0-7. The destination of this data is controlled by A0-2 (active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A0-2            | J5, K5, L4                              | I    | A0-2 is a 3-bit address that determines what function will be performed when CLOAD is active. This address bus is set up with respect to the rising edge of the load signal, CLOAD. A0 is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AUXOUT0-8       | H10, H11, J11,<br>K9-K11, L9-L11        | 0    | AUXOUT0-8 is a 9-bit bus that provides either the data reference output or the 9-bit correlation score of the second correlator, depending on the configuration. When the user programs the chip to be two separate correlators, the score of the second correlator is output on this bus. When the user has programmed the chip to be one correlator, AUXOUT0-7 represents the reference data out, with the state of AUXOUT0-8 undefined. AUXOUT0 is the LSB.                                                                                                                                                                                                                                                                                                                                             |

| ŌĒĀ             | K8                                      | I    | The OEA signal is the output enable for the AUXOUT0-8 output. When OEA is high, the output is disabled. Processing is not interrupted by this pin (active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Index Pin       | C3                                      |      | Used for orienting pin in socket or printed circuit board. Must be left as a no connect in circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### **Absolute Maximum Ratings**

###

#### **Operating Conditions**

| Temperature Range       | 55°C to 125°C    |

|-------------------------|------------------|

| Voltage Range (Typical) | . +4.5V to +5.5V |

#### **Reliability Information**

|                                         | $\theta_{JA}$     | $\theta_{JC}$                          |

|-----------------------------------------|-------------------|----------------------------------------|

| PGA Package                             | 36°C/W            | <sup>θ</sup> JC<br>10 <sup>o</sup> C/W |

| Maximum Package Power Dissipation at 1: | 25 <sup>0</sup> C |                                        |

| PGA Package                             |                   | 1.39W                                  |

| Maximum Storage Temperature Range       |                   | -65°C to 150°C                         |

| Maximum Junction Temperature            |                   | 175 <sup>0</sup> C                     |

| Maximum Lead Temperature (Soldering 10  | Os)               | 300°C                                  |

| Gate Count                              |                   | . 13,000 Gates                         |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

#### TABLE 1. DC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested

| PARAMETER                           | SYMBOL            | CONDITIONS                                                                                  | GROUP A<br>SUB-<br>GROUPS | TEMPERATURE<br>(°C)        | MIN | MAX | UNITS |

|-------------------------------------|-------------------|---------------------------------------------------------------------------------------------|---------------------------|----------------------------|-----|-----|-------|

| Logical One Input<br>Voltage        | V <sub>IH</sub>   | V <sub>CC</sub> = 5.5V                                                                      | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | 2.2 | -   | V     |

| Logical Zero Input<br>Voltage       | V <sub>IL</sub>   | V <sub>CC</sub> = 4.5V                                                                      | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 0.8 | V     |

| Logical One Input<br>Voltage Clock  | V <sub>IHC</sub>  | V <sub>CC</sub> = 5.5V                                                                      | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | 3.0 | -   | V     |

| Logical Zero Input<br>Voltage Clock | V <sub>ILC</sub>  | V <sub>CC</sub> = 4.5V                                                                      | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 0.8 | V     |

| Output HIGH Voltage                 | V <sub>ОН</sub>   | I <sub>OH</sub> = -400μA<br>V <sub>CC</sub> = 4.5V (Note 2)                                 | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | 2.6 | -   | V     |

| Output LOW<br>Voltage               | V <sub>OL</sub>   | I <sub>OL</sub> = +2.0mA<br>V <sub>CC</sub> = 4.5V (Note 2)                                 | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 0.4 | V     |

| Input Leakage Current               | lį                | $V_{IN} = V_{CC}$ or GND<br>$V_{CC} = 5.5V$                                                 | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | -10 | +10 | μА    |

| Output Leakage Current              | Io                | $V_{IN} = V_{CC}$ or GND $V_{CC} = 5.5V$                                                    | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | -10 | +10 | μΑ    |

| Standby Power Supply<br>Current     | I <sub>CCSB</sub> | $V_{IN} = V_{CC}$ or GND $V_{CC} = 5.5V$ , Outputs Open                                     | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 500 | μΑ    |

| Operating Power Supply<br>Current   | Іссор             | f = 20 MHz, V <sub>IN</sub> = V <sub>CC</sub><br>or GND, V <sub>CC</sub> = 5.5V<br>(Note 3) | 1, 2, 3                   | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 140 | mA    |

| Functional Test                     | FT                | (Note 4)                                                                                    | 7, 8                      | -55 ≤ T <sub>A</sub> ≤ 125 | -   | -   | -     |

#### NOTES:

- 2. Interchanging of force and sense conditions is permitted.

- 3. Operating Supply Current is proportional to frequency, typical rating is 7mA/MHz.

- 4. Tested as follows: f = 1MHz,  $V_{IH}$  (clock inputs) = 3.4V,  $V_{IH}$  (all other inputs) = 2.6V,  $V_{IL} = 0.4V$ ,  $V_{OH} \ge 1.5V$ , and  $V_{OL} \le 1.5V$ .

#### TABLE 2. AC ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Guaranteed and 100% Tested (Note 5)

|                                                |                   | (11077 -)         | GROUP A        |                            | -25 (25 | .6MHz) | -20 (2 | 0MHz) |       |

|------------------------------------------------|-------------------|-------------------|----------------|----------------------------|---------|--------|--------|-------|-------|

| PARAMETER                                      | SYMBOL            | (NOTE 5)<br>NOTES | SUB-<br>GROUPS | TEMPERATURE<br>(°C)        | MIN     | МАХ    | MIN    | мах   | UNITS |

| CLK Period                                     | t <sub>CP</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 39      | -      | 50     | -     | ns    |

| CLK High                                       | t <sub>CH</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 15      | -      | 20     | -     | ns    |

| CLK Low                                        | t <sub>CL</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 15      | -      | 20     | -     | ns    |

| CLOAD Cycle Time                               | tCLC              |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 39      | -      | 50     | -     | ns    |

| CLOAD High                                     | tCLH              |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 15      | -      | 20     | -     | ns    |

| CLOAD Low                                      | t <sub>CLL</sub>  |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 15      | -      | 20     | -     | ns    |

| RLOAD Cycle Time                               | t <sub>RLC</sub>  |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 39      | -      | 50     | -     | ns    |

| RLOAD High                                     | t <sub>RLH</sub>  |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 15      | -      | 20     | -     | ns    |

| RLOAD Low                                      | t <sub>RLL</sub>  |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 15      | -      | 20     | -     | ns    |

| Set-up Time; DIN to CLK<br>High                | t <sub>DS</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 13      | -      | 15     | -     | ns    |

| Hold Time; DIN to CLK<br>High                  | t <sub>DH</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 1       | -      | 1      | -     | ns    |

| Set-up Time; DREF to<br>RLOAD High             | t <sub>RS</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 14      | -      | 15     | -     | ns    |

| Hold Time; DREF to<br>RLOAD High               | t <sub>RH</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 1       | -      | 1      | -     | ns    |

| DCONT Set up Time                              | t <sub>DCS</sub>  |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 13      | -      | 15     | -     | ns    |

| DCONT Hold Time                                | t <sub>DCH</sub>  |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 1       | -      | 1      | -     | ns    |

| Address Set up Time                            | t <sub>AS</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 13      | -      | 15     | -     | ns    |

| Address Hold Time                              | t <sub>AH</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 1       | -      | 1      | -     | ns    |

| TXFR Set up Time                               | t <sub>TS</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 13      | -      | 15     | -     | ns    |

| TXFR Hold Time                                 | t <sub>TH</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 1       | -      | 1      | -     | ns    |

| CLK to Output Delay<br>DOUT, AUXOUT,<br>CASOUT | t <sub>DO</sub>   |                   | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | -       | 20     | -      | 25    | ns    |

| Output Enable Time                             | tOE               | Note 6            | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | -       | 20     | -      | 20    | ns    |

| TXFR High to CLK Low                           | tTHCL             | Note 7            | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 3       | -      | 4      | -     | ns    |

| CLK Low to RLOAD, CLOAD High                   | <sup>t</sup> CLLH | Note 7            | 9, 10, 11      | -55 ≤ T <sub>A</sub> ≤ 125 | 1       | -      | 1      | -     | ns    |

#### NOTES:

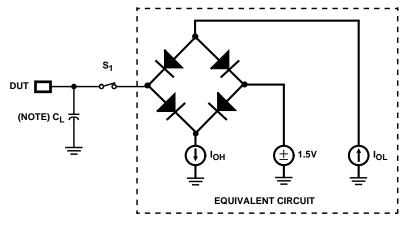

<sup>5.</sup> AC testing is performed as follows:  $V_{CC}$  = 4.5V and 5.5V. Input levels (CLK input) 4.0V and 0V; input levels (all other inputs) 3.0V and 0V; Timing reference levels (CLK) 2.0V; all others 1.5V. Output load per test load circuit with  $C_L$  = 40pF. Output transition is measured at  $V_{OH} \ge 1.5$ V and  $V_{OL} \le 1.5$ V.

<sup>6.</sup> Transition is measured at  $\pm 200$ mV from steady state voltage, Output loading per test load circuit,  $C_L = 40$ pF.

<sup>7.</sup> Applicable only when  $\overline{\text{TXFR}}$  and  $\overline{\text{RLOAD}}$  or  $\overline{\text{CLOAD}}$  are active on the same cycle of CLK.

TABLE 3. ELECTRICAL PERFORMANCE SPECIFICATIONS

|                         |                  |                                                          |       | TEMPERATURE                | -25 |     | -20 |     |       |

|-------------------------|------------------|----------------------------------------------------------|-------|----------------------------|-----|-----|-----|-----|-------|

| PARAMETER               | SYMBOL           | CONDITIONS                                               | NOTES | (°C)                       | MIN | MAX | MIN | MAX | UNITS |

| Input Capacitance       | C <sub>IN</sub>  | V <sub>CC</sub> = Open, f = 1MHz<br>All measurements are | 8     | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 10  | -   | 10  | pF    |

| Output Capaci-<br>tance | C <sub>OUT</sub> | referenced to device GND.                                | 8     | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 10  | -   | 10  | pF    |

| Output Disable<br>Time  | t <sub>OD</sub>  |                                                          | 8, 9  | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 20  | -   | 20  | ns    |

| Output Rise Time        | t <sub>R</sub>   | From 0.8V to 2.0V                                        | 8, 9  | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 8   | -   | 8   | ns    |

| Output Fall Time        | t <sub>F</sub>   | From 2.0V to 0.8V                                        | 8, 9  | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 8   | -   | 8   | ns    |

#### NOTES:

- 8. The parameters in Table 3 are controlled via design or process parameters and not directly tested. Characterized upon initial design and after major process and/or design changes.

- 9. Loading is as specified in the test load circuit with  $C_L$  = 40pF.

**TABLE 4. APPLICABLE SUBGROUPS**

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |

|--------------------|--------------|-------------------------------|

| Initial Test       | 100%/5004    | -                             |

| Interim Test       | 100%/5004    | -                             |

| PDA                | 100%         | 1                             |

| Final Test         | 100%         | 2, 3, 8A, 8B, 10, 11          |

| Group A            | -            | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |

| Groups C and D     | Samples/5005 | 1, 7, 9                       |

### Test Load Circuit

SWITCH  $\text{S}_{1}$  OPEN FOR  $\text{I}_{\text{CCSB}}$  AND  $\text{I}_{\text{CCOP}}$  TEST

NOTE: Includes stray and jig capacitance.

### **Burn-In Circuits**

# **85 PIN PGA** TOP VIEW

|   | 1          | 2               | 3            | 4          | 5           | 6               | 7               | 8               | 9               | 10              | 11               |

|---|------------|-----------------|--------------|------------|-------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| A | CASIN<br>2 | CASIN<br>4      | CASIN<br>5   | CASIN<br>7 | CASIN<br>10 | CASIN<br>11     | CAS<br>OUT<br>0 | CAS<br>OUT<br>3 | CAS<br>OUT<br>5 | GND             | CAS<br>OUT<br>8  |

| В | GND        | CASIN<br>1      | CASIN<br>3   | CASIN<br>6 | CASIN<br>9  | CAS<br>OUT<br>2 | CAS<br>OUT<br>1 | CAS<br>OUT<br>4 | CAS<br>OUT<br>6 | CAS<br>OUT<br>7 | CAS<br>OUT<br>10 |

| С | CLK        | CASIN<br>0      | INDEX<br>PIN |            | CASIN<br>8  | CASIN<br>12     | OEC             |                 |                 | CAS<br>OUT<br>9 | CAS<br>OUT<br>11 |

| D | DIN7       | V <sub>CC</sub> |              |            |             |                 |                 |                 |                 | GND             | CAS<br>OUT<br>12 |

| E | DIN4       | DIN5            | DIN6         |            |             |                 |                 |                 | DOUT0           | DOUT1           | DOUT2            |

| F | DREF<br>4  | DIN3            | DIN2         |            |             |                 |                 |                 | DOUT<br>4       | DOUT<br>7       | DOUT<br>3        |

| G | DIN0       | DREF<br>7       | DIN1         |            |             |                 |                 |                 | v <sub>cc</sub> | DOUT<br>6       | DOUT<br>5        |

| Н | DREF<br>5  | DREF<br>4       |              |            |             |                 |                 |                 |                 | AUX<br>OUT<br>1 | AUX<br>OUT<br>0  |

| J | DREF<br>3  | DREF<br>1       |              |            | A1          | DCONT<br>5      | DCONT<br>4      |                 |                 | GND             | AUX<br>OUT<br>2  |

| K | DREF<br>2  | v <sub>cc</sub> | R<br>LOAD    | C<br>LOAD  | A0          | DCONT<br>6      | DCONT<br>2      | OEA             | AUX<br>OUT<br>6 | AUX<br>OUT<br>4 | AUX<br>OUT<br>3  |

| L | DREF<br>0  | GND             | TXFR         | A2         | DCONT<br>7  | DCONT<br>1      | DCONT<br>3      | DCONT<br>0      | AUX<br>OUT<br>8 | AUX<br>OUT<br>7 | AUX<br>OUT<br>5  |

| PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL  | PGA<br>PIN | PIN<br>NAME     | BURN-IN<br>SIGNAL  | PGA<br>PIN | PIN<br>NAME     | BURN-IN<br>SIGNAL  | PGA<br>PIN | PIN<br>NAME     | BURN-IN<br>SIGNAL  |

|------------|-------------|--------------------|------------|-----------------|--------------------|------------|-----------------|--------------------|------------|-----------------|--------------------|

| A1         | CASIN2      | F3                 | B11        | CASOUT10        | V <sub>CC</sub> /2 | F9         | DOUT4           | V <sub>CC</sub> /2 | K2         | V <sub>CC</sub> | V <sub>CC</sub>    |

| A2         | CASIN4      | F5                 | C1         | CLK             | F0                 | F10        | DOUT7           | V <sub>CC</sub> /2 | K3         | RLOAD           | F3                 |

| A3         | CASIN5      | F6                 | C2         | CASIN0          | F1                 | F11        | DOUT3           | V <sub>CC</sub> /2 | K4         | CLOAD           | F3                 |

| A4         | CASIN7      | F1                 | C5         | CASIN8          | F2                 | G1         | DIN0            | F1                 | K5         | A0              | F9                 |

| A5         | CASIN10     | F4                 | C6         | CASIN12         | F6                 | G2         | DREF7           | F8                 | K6         | DCONT6          | F7                 |

| A6         | CASIN11     | F5                 | C7         | OEC             | F11                | G3         | DIN1            | F2                 | K7         | DCONT2          | F6                 |

| A7         | CASOUT0     | V <sub>CC</sub> /2 | C10        | CASOUT9         | V <sub>CC</sub> /2 | G9         | V <sub>CC</sub> | V <sub>CC</sub>    | K8         | ŌĒĀ             | F11                |

| A8         | CASOUT3     | V <sub>CC</sub> /2 | C11        | CASOUT11        | V <sub>CC</sub> /2 | G10        | DOUT6           | V <sub>CC</sub> /2 | K9         | AUXOUT6         | V <sub>CC</sub> /2 |

| A9         | CASOUT5     | V <sub>CC</sub> /2 | D1         | DIN7            | F8                 | G11        | DOUT5           | V <sub>CC</sub> /2 | K10        | AUXOUT4         | V <sub>CC</sub> /2 |

| A10        | GND         | GND                | D2         | V <sub>CC</sub> | V <sub>CC</sub>    | H1         | DREF5           | F6                 | K11        | AUXOUT3         | V <sub>CC</sub> /2 |

| A11        | CASOUT8     | V <sub>CC</sub> /2 | D10        | GND             | GND                | H2         | DREF4           | F8                 | L1         | DREF0           | F4                 |

| B1         | GND         | GND                | D11        | CASOUT12        | V <sub>CC</sub> /2 | H10        | AUXOUT1         | V <sub>CC</sub> /2 | L2         | GND             | GND                |

| B2         | CASIN1      | F2                 | E1         | DIN4            | F5                 | H11        | AUXOUT0         | V <sub>CC</sub> /2 | L3         | TXFR            | F2                 |

#### (Continued)

| PGA<br>PIN | PIN<br>NAME | BURN-IN<br>SIGNAL  |

|------------|-------------|--------------------|------------|-------------|--------------------|------------|-------------|--------------------|------------|-------------|--------------------|

| В3         | CASIN3      | F4                 | E2         | DIN5        | F6                 | J1         | DREF3       | F7                 | L4         | A2          | F11                |

| B4         | CASIN6      | F7                 | E3         | DIN6        | F7                 | J2         | DREF1       | F5                 | L5         | DCONT7      | F8                 |

| B5         | CASIN9      | F3                 | E9         | DOUT0       | V <sub>CC</sub> /2 | J5         | A1          | F10                | L6         | DCONT1      | F5                 |

| В6         | CASOUT2     | V <sub>CC</sub> /2 | E10        | DOUT1       | V <sub>CC</sub> /2 | J6         | DCONT5      | F6                 | L7         | DCONT3      | F7                 |

| B7         | CASOUT1     | V <sub>CC</sub> /2 | E11        | DOUT2       | V <sub>CC</sub> /2 | J7         | DCONT4      | F8                 | L8         | DCONT0      | F4                 |

| B8         | CASOUT4     | V <sub>CC</sub> /2 | F1         | DREF6       | F7                 | J10        | GND         | GND                | L9         | AUXOUT8     | V <sub>CC</sub> /2 |

| В9         | CASOUT6     | V <sub>CC</sub> /2 | F2         | DIN3        | F4                 | J11        | AUXOUT2     | V <sub>CC</sub> /2 | L10        | AUXOUT7     | V <sub>CC</sub> /2 |

| B10        | CASOUT7     | V <sub>CC</sub> /2 | F3         | DIN2        | F3                 | K1         | DREF2       | F6                 | L11        | AUXOUT5     | V <sub>CC</sub> /2 |

#### NOTES:

- 10.  $V_{CC}/2$  (2.7V ±10%) used for outputs only.

- 11. 47k $\!\Omega$  (±20%) resistor connected to all pins except VCC and GND.

- 12.  $V_{CC} = 5.5 \pm 0.5 V$ .

- 13.  $0.1 \mu F$  (min) capacitor between  $V_{\mbox{\footnotesize{CC}}}$  and GND per position.

- 14. FO =  $100kHz \pm 10\%$ , F1 = F0/2, F2 = F1/2 . . . F11 = F10/2, 40 60% Duty Cycle.

- 15. Input Voltage Limits:  $V_{IL}$  = 0.8V max,  $V_{IH}$  = 4.5  $\pm$  10%.

### Metal Topology

**DIE DIMENSIONS:**

254 mils x 214 mils x 19  $\pm$  1 mil

**METALLIZATION:**

Type: Si - Al or Si-Al-Cu

Thickness: 8kA

**GLASSIVATION:**

Type: Nitrox Thickness: 10kÅ

**WORST CASE CURRENT DENSITY:**

$0.96 \times 10^5 \text{ A/cm}^2$

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com