## RLD03N06CLE, RLD03N06CLESM, RLP03N06CLE

Built in Current Limit I<sub>LIMIT</sub> 0.140 to 0.210A at 150<sup>o</sup>C

- TB334 "Guidelines for Soldering Surface Mount

D

s

JEDEC TO-252AA

DRAIN (FLANGE)

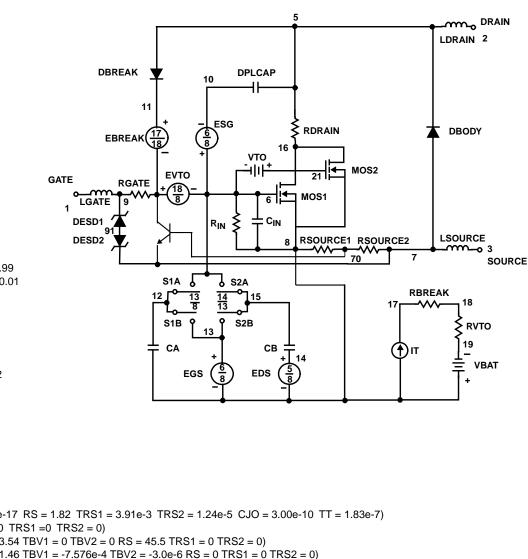

Temperature Compensating PSPICE<sup>®</sup> Model

· Controlled Switching Limits EMI and RFI

Components to PC Boards"

Features

0.30A, 60V

r<sub>DS(ON)</sub> = 6.0Ω

Built in Voltage Clamp

2kV ESD Protected

Related Literature

Symbol

Data Sheet

July 1999 File Number 3948.5

#### 0.3A, 60V, 6 Ohm, ESD Rated, Current Limited, Voltage Clamped, Logic Level N-Channel Power MOSFETs

These are intelligent monolithic power circuits which incorporate a lateral bipolar transistor, resistors, zener diodes and a power MOS transistor. The current limiting of these devices allow it to be used safely in circuits where a shorted load condition may be encountered. The drain to source voltage clamping offers precision control of the circuit voltage when switching inductive loads. The "Logic Level" gate allows this device to be fully biased on with only 5V from gate to source, thereby facilitating true on-off power control directly from logic level (5V) integrated circuits.

These devices incorporate ESD protection and are designed to withstand 2kV (Human Body Model) of ESD.

Formerly developmental type TA49028.

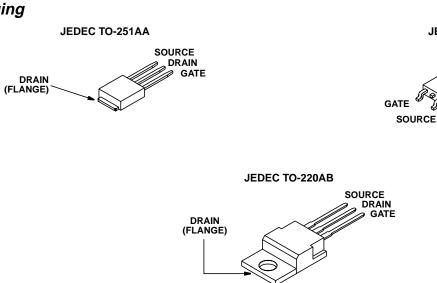

#### Ordering Information

| PART NUMBER   | PACKAGE  | BRAND    |

|---------------|----------|----------|

| RLD03N06CLE   | TO-251AA | 03N06C   |

| RLD03N06CLESM | TO-252AA | 03N06C   |

| RLP03N06CLE   | TO-220AB | 03N06CLE |

NOTE: When ordering, use the entire part number. Add the suffix 9A to obtain the TO-252AA variant in tape and reel, i.e. RLD03N06CLESM9A.

#### Packaging

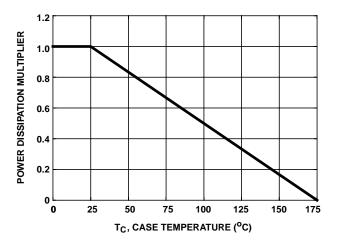

#### **Absolute Maximum Ratings** $T_C = 25^{\circ}C$ , Unless Otherwise Specified

| •                                                              | RLD03N06CLE, RLD03N06CLESM, |                   |

|----------------------------------------------------------------|-----------------------------|-------------------|

|                                                                | RLP03N06CLE                 | UNITS             |

| Drain to Source Voltage (Note 1)V <sub>DSS</sub>               | 60                          | V                 |

| Drain to Gate Voltage                                          | 60                          | V                 |

| Gate to Source Voltage (Reverse Voltage Gate Bias Not Allowed) | +5.5                        | V                 |

| Continuous Drain CurrentID                                     | Self Limited                |                   |

| Power Dissipation                                              | 30                          | W                 |

| Derate Above 25 <sup>o</sup> C                                 | 0.2                         | W/ <sup>o</sup> C |

| Electrostatic Discharge Rating MIL-STD-883, Category B(2)ESD   | 2                           | KV                |

| Operating and Storage Temperature                              | -55 to 175                  | °C                |

| Maximum Temperature for Soldering                              |                             |                   |

| Leads at 0.063in (1.6mm) from Case for 10s                     | 300                         | °C                |

| Package Body for 10s, See Techbrief 334                        | 260                         | °C                |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $T_J = 25^{\circ}C$  to  $150^{\circ}C$ .

| PARAMETER                              | SYMBOL                 | I <sub>D</sub> = 250μA, V <sub>GS</sub> = 0V                                           |                                     | MIN | TYP | MAX  | UNITS |

|----------------------------------------|------------------------|----------------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

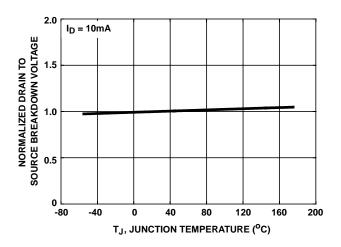

| Drain to Source Breakdown Voltage      | BV <sub>DSS</sub>      |                                                                                        |                                     | 60  | -   | 85   | V     |

| Gate Threshold Voltage                 | V <sub>GS(TH)</sub>    |                                                                                        |                                     | 1   | -   | 2.5  | V     |

| Zero Gate Voltage Drain Current        | I <sub>DSS</sub>       | $V_{DS} = 45V,$<br>$V_{GS} = 0V$                                                       | $T_J = 25^{\circ}C$                 | -   | -   | 25   | μA    |

|                                        |                        |                                                                                        | T <sub>J</sub> = 150 <sup>0</sup> C | -   | -   | 250  | μΑ    |

| Gate to Source Leakage Current         | I <sub>GSS</sub>       | V <sub>GS</sub> = 5V                                                                   | $T_J = 25^{\circ}C$                 | -   | -   | 5    | μΑ    |

|                                        |                        |                                                                                        | $T_J = 150^{\circ}C$                | -   | -   | 20   | μΑ    |

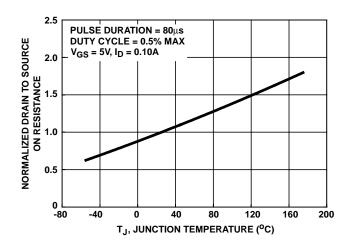

| Drain to Source On Resistance (Note 2) | rDS(ON)                | I <sub>D</sub> = 0.100A,<br>V <sub>GS</sub> = 5V                                       | $T_J = 25^{\circ}C$                 | -   | -   | 6.0  | Ω     |

|                                        |                        |                                                                                        | $T_J = 150^{\circ}C$                | -   | -   | 12.0 | Ω     |

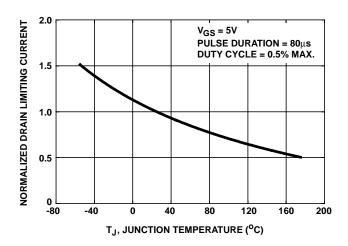

| Limiting Current                       | I <sub>DS(LIMIT)</sub> | $V_{DS} = 15V,$<br>$V_{GS} = 5V$                                                       | $T_J = 25^{\circ}C$                 | 280 | -   | 420  | mA    |

|                                        |                        |                                                                                        | $T_J = 150^{O}C$                    | 140 | -   | 210  | mA    |

| Turn-On Time                           | ton                    | $V_{DD} = 30V, I_D = 0.10A,$<br>$R_L = 300\Omega, V_{GS} = 5V,$<br>$R_{GS} = 25\Omega$ |                                     | -   | -   | 7.5  | μs    |

| Turn-On Delay Time                     | t <sub>d(ON)</sub>     |                                                                                        |                                     | -   | -   | 2.5  | μs    |

| Rise Time                              | tr                     |                                                                                        |                                     | -   | -   | 5.0  | μs    |

| Turn-Off Delay Time                    | td(OFF)                |                                                                                        |                                     | -   | -   | 7.5  | μs    |

| Fall Time                              | t <sub>f</sub>         |                                                                                        |                                     | -   | -   | 5.0  | μs    |

| Turn-Off Time                          | tOFF                   |                                                                                        |                                     | -   | -   | 12.5 | μs    |

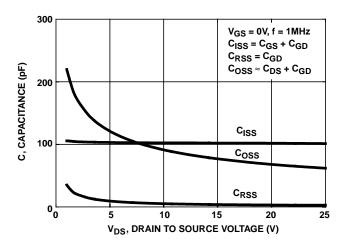

| Input Capacitance                      | C <sub>ISS</sub>       | $V_{DS} = 25V, V_{GS} = 0V,$<br>f = 1MHz                                               |                                     | -   | 100 | -    | pF    |

| Output Capacitance                     | C <sub>OSS</sub>       |                                                                                        |                                     | -   | 65  | -    | pF    |

| Reverse Transfer Capacitance           | C <sub>RSS</sub>       |                                                                                        |                                     | -   | 3.0 | -    | pF    |

| Thermal Resistance Junction to Case    | R <sub>θJC</sub>       |                                                                                        |                                     | -   | -   | 5.0  | °C/W  |

| Thermal Resistance Junction to Ambient | R <sub>θJA</sub>       | TO-220 Package                                                                         | )                                   | -   | -   | 80   | °C/W  |

|                                        | TO-251 and T           |                                                                                        | 252 Packages                        | -   | -   | 100  | °C/W  |

#### **Electrical Specifications** $T_C = 25^{\circ}C$ , Unless Otherwise Specified

#### Source to Drain Diode Specifications

| PARAMETER                     | SYMBOL          | TEST CONDITIONS                                                | MIN | ТҮР | MAX | UNITS |

|-------------------------------|-----------------|----------------------------------------------------------------|-----|-----|-----|-------|

| Source to Drain Diode Voltage | V <sub>SD</sub> | I <sub>SD</sub> = 0.1A                                         | -   | -   | 1.5 | V     |

| Diode Reverse Recovery Time   | t <sub>rr</sub> | $I_{\text{SD}} = 0.1$ A, d $I_{\text{SD}}$ /dt = 100A/ $\mu$ s | -   | -   | 1.0 | ms    |

NOTES:

2. Pulsed: pulse duration =  $\leq 300 \mu s$  maximum, duty cycle =  $\leq 2\%.$

3. Repititive rating: pulse width limited by maximum junction temperature.

#### Typical Performance Curves Unless Otherwise Specified

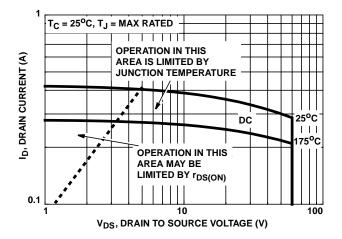

FIGURE 2. FORWARD BIAS SAFE OPERATING AREA

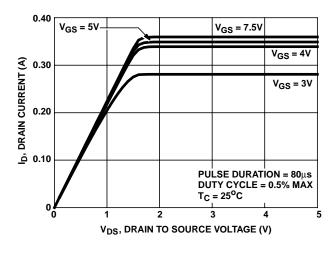

FIGURE 5. SATURATION CHARACTERISTICS

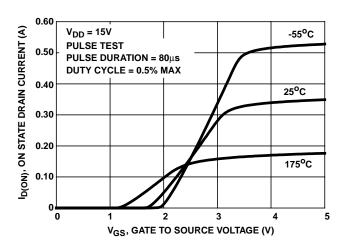

#### Typical Performance Curves Unless Otherwise Specified (Continued)

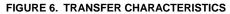

FIGURE 8. NORMALIZED GATE THRESHOLD VOLTAGE vs JUNCTION TEMPERATURE

FIGURE 10. CAPACITANCE vs DRAIN TO SOURCE VOLTAGE

FIGURE 7. NORMALIZED DRAIN TO SOURCE ON RESISTANCE vs JUNCTION TEMPERATURE

FIGURE 9. NORMALIZED DRAIN TO SOURCE BREAKDOWN VOLTAGE vs TEMPERATURE

FIGURE 11. NORMALIZED DRAIN LIMITING CURRENT vs JUNCTION TEMPERATURE

#### Typical Performance Curves Unless Otherwise Specified (Continued)

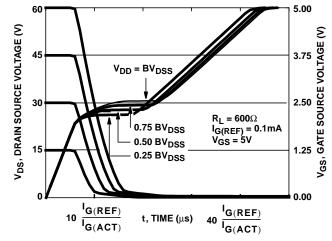

NOTE: Refer to Intersil Application Notes AN7254 and AN7260. FIGURE 12. NORMALIZED SWITCHING WAVEFORMS FOR CONSTANT GATE CURRENT.

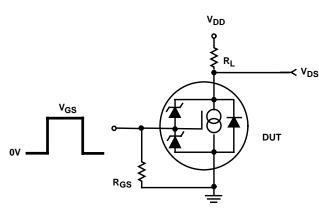

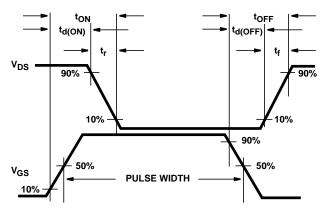

#### Test Circuits and Waveforms

FIGURE 13. RESISTIVE SWITCHING TEST CIRCUIT

### **Detailed Description**

# *Temperature Dependence of Current Limiting and Switching Speed Performance*

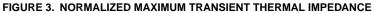

The RLD03N06CLE, CLESM and RLP03N06CLE are monolithic power devices which incorporate a Logic Level power MOSFET transistor with a current sensing scheme and control circuitry to enable the device to self limit the drain source current flow. The current sensing scheme supplies current to a resistor that is connected across the base to emitter of a bipolar transistor in the control section. The collector of this bipolar transistor is connected to the gate of the power MOSFET transistor. When the ratiometric current from the current sensing reaches the value required to forward bias the base emitter junction of this bipolar transistor, the bipolar "turns on". A resistor is incorporated in series with the gate of the power MOSFET transistor allowing the bipolar transistor to adjust the drive on the gate of the power MOSFET transistor to a voltage which then maintains a constant current in the power MOSFET transistor. Since both the ratiometric current sensing scheme and the base emitter unction

FIGURE 14. RESISTIVE SWITCHING WAVEFORMS

voltage of the bipolar transistor vary with temperature, the current at which the device limits is a function of temperature. This dependence is shown in Figure 3.

The resistor in series with the gate of the power MOSFET transistor also results in much slower switching performance than in standard power MOSFET transistors. This is an advantage where fast switching can cause EMI or RFI. The switching speed is very predictable.

#### DC Operation

D

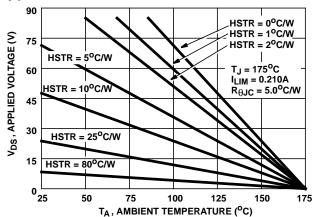

The limit on the drain to source voltage for operation in current limiting on a steady state (DC) basis is shown in the equation below. The dissipation in the device is simply the applied drain to source voltage multiplied by the limiting current. This device, like most power MOSFET devices today, is limited to 175°C. The maximum voltage allowable can, therefore, be expressed as shown in Equation 1:

$$S = \frac{(150^{\circ}C - T_{AMBIENT})}{I_{LM} \cdot (R\theta JC + R\theta JA)}$$

(EQ.1)

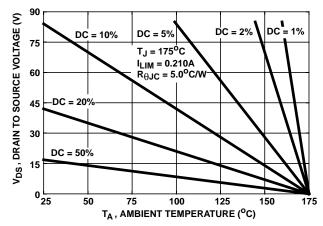

The results of this equation are plotted in Figure 15 for various heatsinks.

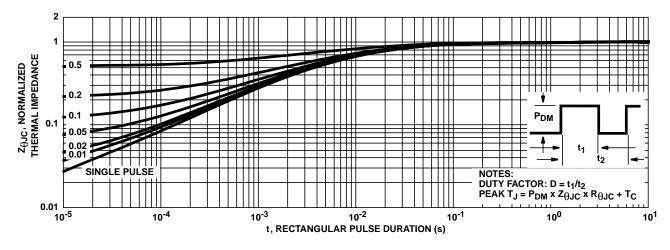

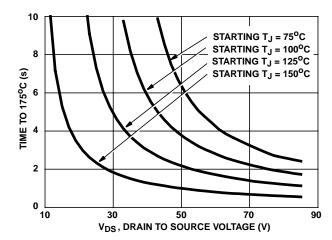

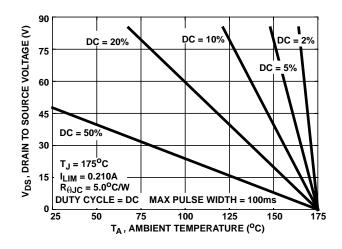

#### **Duty Cycle Operation**

In many applications either the drain to source voltage or the gate drive is not available 100% of the time. The copper header on which the RLD03N06CLE, CLESM and RLP03N06CLE is mounted has a very large thermal storage capability, so for pulse widths of less then 1ms, the temperature of the header can be considered a constant, thereby the junction temperature can be calculated simply as shown in Equation 2:

$$T_{C} = (V_{DS} \bullet I_{D} \bullet D \bullet R_{\theta CA}) + T_{AMBIENT}$$

(EQ.2)

Generally the heat storage capability of the silicon chip in a power transistor is ignored for duty cycle calculations. Making this assumption, limiting junction temperature to 175°C and using the T<sub>C</sub> calculated in Equation 2, the expression for maximum V<sub>DS</sub> under duty cycle operation is shown in Equation 3

$$V_{DS} = \frac{150^{\circ}C - T_{C}}{I_{LM} \bullet D \bullet R_{\theta JC}}$$

(EQ.3)

#### Typical Performance Curves

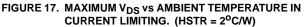

NOTE: Heat Sink Thermal Resistance = HSTR.

FIGURE 15. DC OPERATION IN CURRENT LIMITING

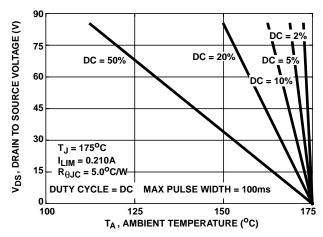

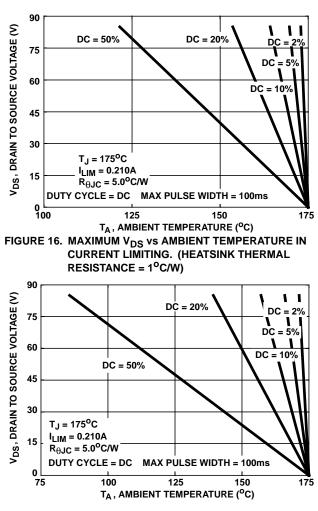

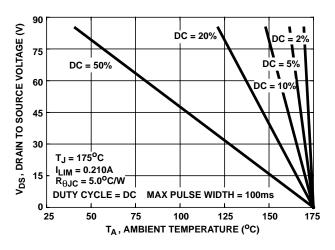

These values are plotted as Figures 16 through 21 for various heatsink thermal resistances.

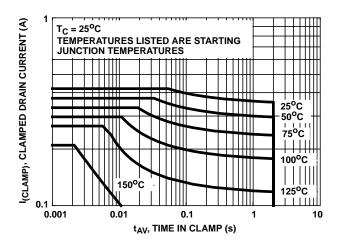

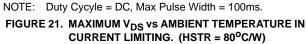

#### Limited Time Operations

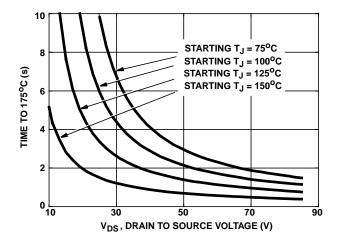

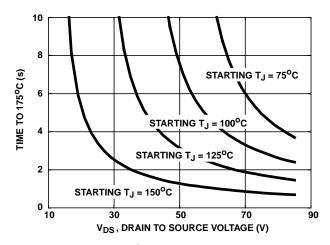

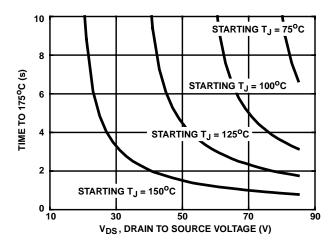

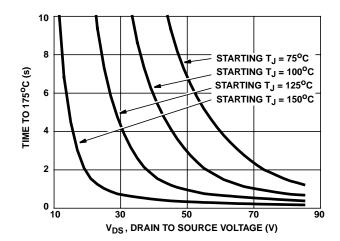

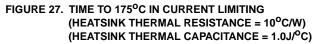

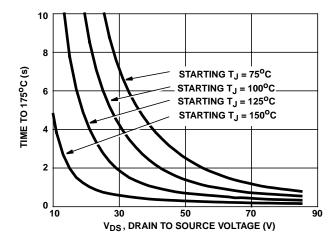

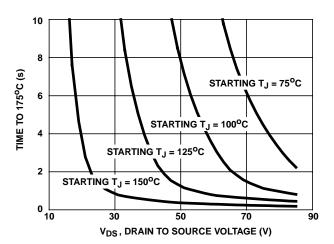

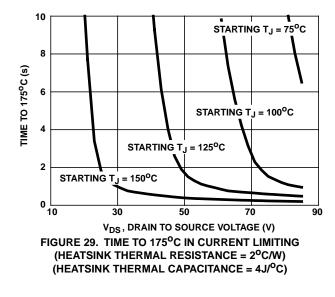

Protection for a limited period of time is sufficient for many applications. As stated above the heat storage in the silicon chip can usually be ignored for computations of over 10 ms, thereby the thermal equivalent circuit reduces to a simple enough circuit to allow easy computation on the limiting conditions. The variation in limiting current with temperature complicates the calculation of junction temperature, but a simple straight line approximation of the variation is accurate enough to allow meaningful computations. The curves shown as Figures 22 through 25 (RLP03N06CLE) and Figure 26 through 29 (RLD03N06CLE and RLD03N06CLESM) give an accurate indication of how long the specified voltage can be applied to the device in the current limiting mode without exceeding the maximum specified 175°C junction temperature. In practice this tells you how long you have to alleviate the condition causing the current limiting to occur.

FIGURE 18. MAXIMUM  $V_{DS}$  vs AMBIENT TEMPERATURE IN CURRENT LIMITING. (HSTR = 5°C/W)

#### Typical Performance Curves (Continued)

FIGURE 19. MAXIMUM V<sub>DS</sub> vs AMBIENT TEMPERATURE IN CURRENT LIMITING. (HSTR = 10<sup>o</sup>C/W)

FIGURE 23. TIME TO 175<sup>o</sup>C IN CURRENT LIMITING (HEATSINK THERMAL RESISTANCE = 10<sup>o</sup>C/W) (HEATSINK THERMAL CAPACITANCE = 1.0J/<sup>o</sup>C)

FIGURE 20. MAXIMUM  $V_{DS}$  vs AMBIENT TEMPERATURE IN CURRENT LIMITING. (HSTR =  $25^{\circ}$ C/W)

FIGURE 22. TIME TO 175°C IN CURRENT LIMITING (HEATSINK THERMAL RESISTANCE = 25°C/W) (HEATSINK THERMAL CAPACITANCE = 0.5J/°C)

FIGURE 24. TIME TO  $175^{\circ}$ C IN CURRENT LIMITING (HEATSINK THERMAL RESISTANCE =  $5^{\circ}$ C/W) (HEATSINK THERMAL CAPACITANCE =  $2.0J/^{\circ}$ C)

#### Typical Performance Curves (Continued)

FIGURE 25. TIME TO  $175^{\circ}$ C IN CURRENT LIMITING (HEATSINK THERMAL RESISTANCE =  $2^{\circ}$ C/W) (HEATSINK THERMAL CAPACITANCE =  $4J/^{\circ}$ C)

FIGURE 26. TIME TO 175<sup>o</sup>C IN CURRENT LIMITING (HEATSINK THERMAL RESISTANCE = 25<sup>o</sup>C/W) (HEATSINK THERMAL CAPACITANCE = 0.5J/<sup>o</sup>C)

FIGURE 28. TIME TO  $175^{\circ}$ C IN CURRENT LIMITING (HEATSINK THERMAL RESISTANCE =  $5^{\circ}$ C/W) (HEATSINK THERMAL CAPACITANCE =  $2.0J/^{\circ}$ C)

#### **PSPICE Electrical Model**

SUBCKT RLD03N06CLE 2 1 3; rev 4/18/94 CA 12 8 0.547e-9 CB 15 14 0.547e-9 CIN 6 8 0.301e-9

DBODY 7 5 DBDMOD DBREAK 5 11 DBKMOD DESD1 91 9 DESD1MOD DESD2 91 7 DESD2MOD DPLCAP 10 5 DPLCAPMOD

EBREAK 11 20 17 18 66.5 EDS 14 8 5 8 1 EGS 13 8 6 8 1 ESG 6 10 6 8 1 EVTO 20 6 18 8 1

IT 8 17 1

LDRAIN 2 5 1e-9 LGATE 1 9 2.96e-9 LSOURCE 3 7 2.96e-9

MOS1 16 6 8 8 MOSMOD M = 0.99 MOS2 16 21 8 8 MOSMOD M = 0.01

QCONTROL 20 70 7 QMOD 1

RBREAK 17 18 RBKMOD 1 RDRAIN 5 16 RDSMOD 1.123 RGATE 9 20 3200 RIN 6 8 1e9 RSOURCE1 8 70 RDSMOD 1.12 RSOURCE2 70 7 RSMOD 2.16 RVTO 18 19 RVTOMOD 1

S1A 6 12 13 8 S1AMOD S1B 13 12 13 8 S1BMOD S2A 6 15 14 13 S2AMOD S2B 13 15 14 13 S2BMOD

VBAT 8 19 DC 1 VTO 21 6 0.22

$\begin{aligned} & \text{MODEL DBDMOD D (IS = 7.97e-17 \ RS = 1.82 \ TRS1 = 3.91e-3 \ TRS2 = 1.24e-5 \ CJO = 3.00e-10 \ TT = 1.83e-7) \\ & \text{MODEL DBKMOD D (RS = 3150 \ TRS1 = 0 \ TRS2 = 0) \\ & \text{MODEL DESD1MOD D (BV = 13.54 \ TBV1 = 0 \ TBV2 = 0 \ RS = 45.5 \ TRS1 = 0 \ TRS2 = 0) \\ & \text{MODEL DESD2MOD D (BV = 11.46 \ TBV1 = -7.576e-4 \ TBV2 = -3.0e-6 \ RS = 0 \ TRS1 = 0 \ TRS2 = 0) \\ & \text{MODEL DPLCAPMOD D (CJO = 74.2e-12 \ IS = 1e-30 \ N = 10) \\ & \text{MODEL MOSMOD NMOS (VTO = 1.67 \ KP = 3.40 \ IS = 1e-30 \ N = 10 \ TOX = 1 \ L = 1u \ W = 1u) \\ & \text{MODEL QMOD NPN (BF = 5) } \\ & \text{MODEL RBKMOD RES (TC1 = 4e-4 \ TC2 = 1.13e-8) } \\ & \text{MODEL RDSMOD RES (TC1 = 2.95e-3 \ TC2 = -1e-6) } \\ & \text{MODEL RSMOD RES (TC1 = 2.95e-3 \ TC2 = -1e-6) } \\ & \text{MODEL RSMOD RES (TC1 = 2.92e-3 \ TC2 = -1.95e-6) } \\ & \text{MODEL S1AMOD VSWITCH (RON = 1e-5 \ ROFF = 0.1 \ VON = -3 \ VOFF = -1) } \\ & \text{MODEL S1BMOD VSWITCH (RON = 1e-5 \ ROFF = 0.1 \ VON = -2.85 \ VOFF = 2.15) } \\ & \text{MODEL S2BMOD VSWITCH (RON = 1e-5 \ ROFF = 0.1 \ VON = 2.15 \ VOFF = -2.85) } \end{aligned}$

.ENDS

NOTE: For further discussion of the PSPICE model consult **A New PSPICE Sub-Circuit for the Power MOSFET Featuring Global Temperature Options**; IEEE Power Electronics Specialist Conference Records 1991.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

6-426 intersil