# **HA4344B**

# 350MHz, 4 x 1 Video Crosspoint Switch with Synchronous Controls

June 1998

## Features

| Low Power Dissipation                         |

|-----------------------------------------------|

| • Symmetrical Slew Rates 1400V/ $\mu$ s       |

| • 0.1dB Gain Flatness                         |

| • -3dB Bandwidth                              |

| • Off Isolation (100MHz)                      |

| Crosstalk Rejection (30MHz) 80dB              |

| Differential Gain and Phase 0.01%/0.01Degrees |

| • High ESD Rating>2000V                       |

| TTI Compatible Control Signals                |

- TTL Compatible Control Signals

- · Latched Control Lines for Synchronous Switching

## **Applications**

- · Professional Video Switching and Routing

- RGB Video Distribution Systems

- Computer Graphics

- RF Switching and Routing

## Description

The HA4344B is a very wide bandwidth 4 x 1 crosspoint switch ideal for professional video switching, HDTV, computer display routing, and other high performance applications. This circuit features very low power dissipation, excellent differential gain and phase, high off isolation, symmetric slew rates, fast switching, and latched control signals. When disabled, the output is switched to a high impedance state, making the HA4344B ideal for matrix routers.

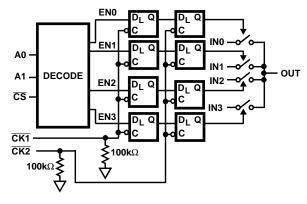

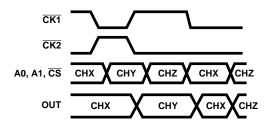

The latched control signals allow for synchronized channel switching. When  $\overline{CK1}$  is low the master control latch loads the next switching address (A0, A1,  $\overline{CS}$ ), while the closed (assuming  $\overline{CK2}$  is the inverse of  $\overline{CK1}$ ) slave control latch maintains the crosspoint in its current state.  $\overline{CK2}$  switching low closes the master latch (with previous assumption), loads the now open slave latch, and switches the crosspoint to the newly selected channel. Channel selection is asynchronous (changes with any control signal change) if both  $\overline{CK1}$  and  $\overline{CK2}$  are low.

## **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE                     | PKG.<br>NO. |

|-------------|---------------------|-----------------------------|-------------|

| HA4344BCB   | 0 to 70             | 16 Ld SOIC                  | M16.15      |

| HA4344BCB96 | 0 to 70             | 16 Ld SOIC Tape<br>and Reel | M16.15      |

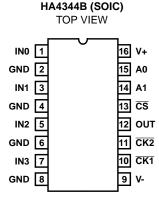

## **Pinout**

# Functional Diagram

## Timing Diagram

#### HA4344B

#### **Thermal Information Absolute Maximum Ratings** Thermal Resistance (Typical, Note 1) $\theta_{JA}$ (oC/W) Input Voltage......VSUPPLY SOIC Package..... Maximum Junction Temperature (Die)......175°C Analog Input Current (Note 2) . . . . . . . . . . . . . . . . ±5mA Maximum Junction Temperature (Plastic Package) . . . . . . . . 150°C Maximum Storage Temperature Range . . . . . -65°C to 150°C ESD Rating Maximum Lead Temperature (Soldering 10s)............. 300°C Human Body Model (Per MIL-STD-883 Method 3015.7) . . 2000V (SOIC - Lead Tips Only) **Operating Conditions** Temperature Range . . . . . . . . . . . . . . . . 0 °C to 70 °C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1.  $\theta_{1A}$  is measured with the component mounted on an evaluation PC board in free air.

- 2. If an input signal is applied before the supplies are powered up, the input current must be limited to these maximum values.

### **Electrical Specifications** $V_{SUPPLY} = \pm 5V$ , $R_L = 10k\Omega$ , $V_{\overline{CS}} = 0.8V$ , Unless Otherwise Specified

| PARAMETER                                  | TEST CONDITIONS                                | (NOTE 4) TEMP. (°C) | MIN  | ТҮР    | MAX    | UNITS |

|--------------------------------------------|------------------------------------------------|---------------------|------|--------|--------|-------|

| DC SUPPLY CHARACTERISTICS                  |                                                | •                   | -    | -      |        |       |

| Supply Voltage                             |                                                | Full                | ±4.5 | ±5.0   | ±5.5   | V     |

| Supply Current (V <sub>OUT</sub> = 0V)     | V <del>CS</del> = 0.8V                         | 25, 70              | -    | 10.5   | 13     | mA    |

|                                            | V <sub>CS</sub> = 0.8V                         | 0                   | -    | -      | 15.5   | mA    |

|                                            | V <sub>CS</sub> = 2.0V                         | 25, 70              | -    | 400    | 450    | μΑ    |

|                                            | V <sub>CS</sub> = 2.0V                         | 0                   | -    | 400    | 580    | μΑ    |

| ANALOG DC CHARACTERISTICS                  |                                                | •                   | •    | •      |        |       |

| Output Voltage Swing Without               | $V_{OUT} = V_{IN} \pm V_{IO} \pm 20 \text{mV}$ | 25, 70              | ±2.7 | ±2.8   | -      | V     |

| Clipping                                   |                                                | 0                   | ±2.4 | ±2.5   | -      | V     |

| Output Current                             |                                                | Full                | 15   | 20     | -      | mA    |

| Input Bias Current                         |                                                | Full                | -    | 30     | 50     | μΑ    |

| Output Offset Voltage                      |                                                | Full                | -10  | -      | 10     | mV    |

| Output Offset Voltage Drift (Note 3)       |                                                | Full                | -    | 25     | 50     | μV/°C |

| SWITCHING CHARACTERISTICS                  | •                                              | •                   | •    | •      |        | •     |

| Turn-On Time                               |                                                | 25                  | -    | 160    | -      | ns    |

| Turn-Off Time                              |                                                | 25                  | -    | 320    | -      | ns    |

| Output Glitch During Switching             |                                                | 25                  | -    | ±10    | -      | mV    |

| DIGITAL DC CHARACTERISTICS                 | •                                              | •                   | •    | •      |        | •     |

| Input Logic High Voltage                   |                                                | Full                | 2    | -      | -      | V     |

| Input Logic Low Voltage                    |                                                | Full                | -    | -      | 0.8    | V     |

| CLK1, CLK2 Input Current                   | 0 to 4V                                        | Full                | -    | 40     | 50     | μΑ    |

| CS, A0, A1 Input Current                   | 0 to 4V                                        | Full                | -2   | -      | 2      | μΑ    |

| AC CHARACTERISTICS                         | •                                              | •                   | •    | •      | •      | •     |

| Insertion Loss                             | 1V <sub>P-P</sub>                              | 25                  | -    | 0.055  | 0.063  | dB    |

|                                            |                                                | Full                | -    | 0.07   | 0.08   | dB    |

| Channel-to-Channel Insertion Loss<br>Match |                                                | Full                | -    | ±0.004 | ±0.006 | dB    |

$\textbf{Electrical Specifications} \ \ V_{SUPPLY} = \pm 5 \text{V}, \ R_L = 10 \text{k}\Omega, \ V_{\overline{CS}} = 0.8 \text{V}, \ \text{Unless Otherwise Specified} \ \ \textbf{(Continued)}$

| PARAMETER                                 | TEST CONDITIONS                                    | (NOTE 4)<br><b>TEMP. (°C)</b> | MIN | TYP       | MAX  | UNITS   |

|-------------------------------------------|----------------------------------------------------|-------------------------------|-----|-----------|------|---------|

| -3dB Bandwidth                            | $R_S = 47\Omega$ , $C_L = 10pF$                    | 25                            | -   | 350       | -    | MHz     |

|                                           | $R_S = 29\Omega$ , $C_L = 20pF$                    | 25                            | -   | 300       | -    | MHz     |

|                                           | $R_S = 16\Omega$ , $C_L = 33pF$                    | 25                            | -   | 220       | ı    | MHz     |

|                                           | $R_S = 9\Omega$ , $C_L = 52pF$                     | 25                            | -   | 160       | ı    | MHz     |

| ±0.1dB Flat Bandwidth                     | $R_S = 47\Omega$ , $C_L = 10pF$                    | 25                            | -   | 150       | -    | MHz     |

|                                           | $R_S = 29\Omega$ , $C_L = 20pF$                    | 25                            | -   | 110       | ı    | MHz     |

|                                           | $R_S = 16\Omega$ , $C_L = 33pF$                    | 25                            | -   | 100       | -    | MHz     |

|                                           | $R_S = 9\Omega$ , $C_L = 52pF$                     | 25                            | -   | 70        | -    | MHz     |

| Input Resistance                          |                                                    | Full                          | 200 | 400       | -    | kΩ      |

| Input Capacitance                         |                                                    | Full                          | -   | 1.5       | -    | pF      |

| Enabled Output Resistance                 |                                                    | Full                          | -   | 15        | -    | Ω       |

| Disabled Output Capacitance               | V <del>CS</del> = 2.0V                             | Full                          | -   | 2.5       | -    | pF      |

| Differential Gain                         | 4.43MHz, Note 3                                    | 25                            | -   | 0.01      | 0.02 | %       |

| Differential Phase                        | 4.43MHz, Note 3                                    | 25                            | -   | 0.01      | 0.02 | Degrees |

| Off Isolation                             | $1V_{P-P}$ , $100MHz$ , $V_{\overline{CS}} = 2.0V$ | Full                          | -   | 70        | -    | dB      |

| Crosstalk Rejection                       | 1V <sub>P-P</sub> , 30MHz                          | Full                          | -   | 80        | -    | dB      |

| Slew Rate (1.5V <sub>P-P</sub> , +SR/-SR) | $R_S = 47\Omega$ , $C_L = 10pF$                    | 25                            | -   | 1400/1490 | -    | V/μs    |

|                                           | $R_S = 29\Omega$ , $C_L = 20pF$                    | 25                            | -   | 1200/1260 | -    | V/μs    |

|                                           | $R_S = 16\Omega$ , $C_L = 33pF$                    | 25                            | -   | 870/940   | -    | V/μs    |

|                                           | $R_S = 9\Omega$ , $C_L = 52pF$                     | 25                            | -   | 750/710   | -    | V/μs    |

| Total Harmonic Distortion (Note 3)        |                                                    | Full                          | -   | 0.01      | 0.1  | %       |

| Disabled Output Resistance                | V <sub>CS</sub> = 2.0V                             | Full                          | -   | 12        | -    | МΩ      |

## NOTES:

- 3. This parameter is not tested. The limits are guaranteed based on lab characterization, and reflect lot-to-lot variation.

- 4. Units are 100% tested at 25°C; guaranteed, but not tested at 0°C and 70°C.

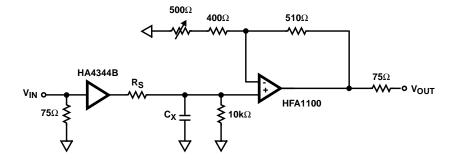

# **AC Test Circuit**

NOTE:  $C_L = C_X + Test$  Fixture Capacitance.

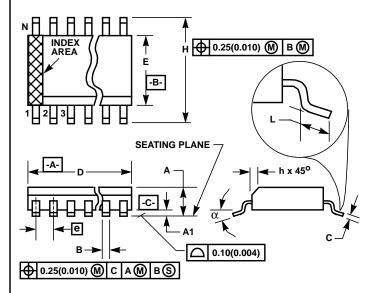

# Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M16.15 (JEDEC MS-012-AC ISSUE C)

16 LEAD NARROW BODY SMALL OUTLINE PLASTIC

PACKAGE

|        | INCHES    |                | MILLIM   |       |       |

|--------|-----------|----------------|----------|-------|-------|

| SYMBOL | MIN       | MAX            | MIN      | MAX   | NOTES |

| Α      | 0.0532    | 0.0688         | 1.35     | 1.75  | -     |

| A1     | 0.0040    | 0.0098         | 0.10     | 0.25  | -     |

| В      | 0.013     | 0.020          | 0.33     | 0.51  | 9     |

| С      | 0.0075    | 0.0098         | 0.19     | 0.25  | -     |

| D      | 0.3859    | 0.3937         | 9.80     | 10.00 | 3     |

| Е      | 0.1497    | 0.1574         | 3.80     | 4.00  | 4     |

| е      | 0.050 BSC |                | 1.27 BSC |       | -     |

| Н      | 0.2284    | 0.2440         | 5.80     | 6.20  | -     |

| h      | 0.0099    | 0.0196         | 0.25     | 0.50  | 5     |

| L      | 0.016     | 0.050          | 0.40     | 1.27  | 6     |

| N      | 1         | 6              | 16       |       | 7     |

| α      | 0°        | 8 <sup>0</sup> | 0° 8°    |       | -     |

Rev. 0 12/93

## All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

# Sales Office Headquarters

### **NORTH AMERICA**

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (321) 724-7000

FAX: (321) 724-7000 FAX: (321) 724-7240

#### **EUROPE**

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### **ASIA**

Intersil (Taiwan) Ltd.

Taiwan Limited

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029