# HI2315

# 10-Bit, 80 MSPS D/A Converter (Ultra-Low Glitch Version)

## August 1997

## Features

- Throughput Rate ...... 80MHz

- Low Power ......150mW

- Single Power Supply .....+5V

- Differential Linearity Error ..... ±0.5 LSB

- TTL/CMOS Compatible Inputs

- Built in Bandgap Voltage Reference

- Power Down and Blanking Control Pins

- Low Glitch

- Pin Compatible with Sony CXD2306

- Direct Replacement for Sony CXD2315Q

## Applications

- Wireless Communications

- Direct Digital Frequency Synthesis

- Signal Reconstruction

- Test Equipment

- High Resolution Imaging and Graphics Systems

## Description

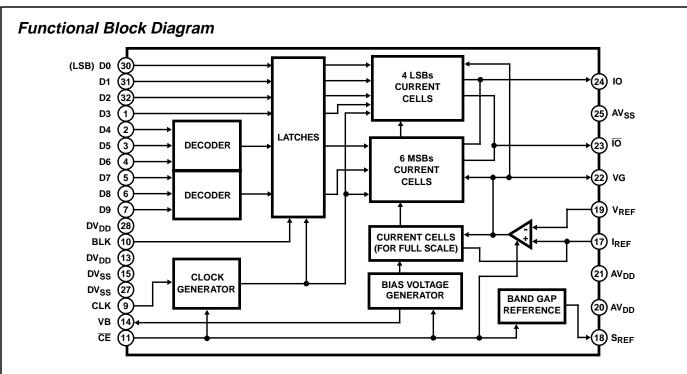

The HI2315 is a 10-bit, 80MHz, high speed, low power CMOS D/A converter. The converter incorporates a 10-bit input data register with current outputs. The HI2315 includes a power down feature that reduces power consumption and a blanking control. The on-chip bandgap reference can be used to set the output current range of the D/A.

## **Ordering Information**

| PART<br>NUMBER | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE    | PKG. NO.  |

|----------------|----------------------------------|------------|-----------|

| HI2315JCQ      | -20 to 75                        | 32 Ld MQFP | Q32.7x7-S |

#### CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999 10-1

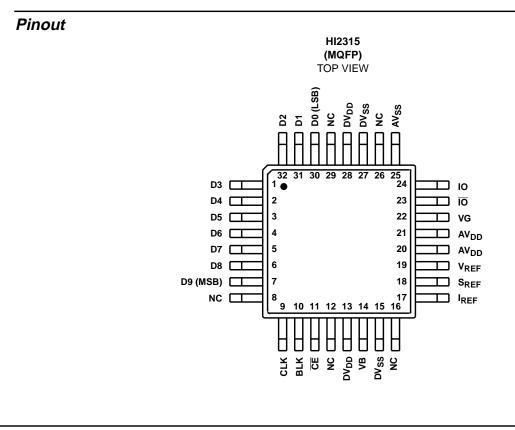

# **Pin Descriptions**

| PIN NO.            | SYMBOL   | EQUIVALENT CIRCUIT                                                                                                                                                 | DESCRIPTION                                                          |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 30 to 32<br>1 to 7 | D0 to D9 | 30<br>TO<br>TO<br>TO<br>DV <sub>DD</sub>                                                                                                                           | Digital Input.                                                       |

| 10                 | BLK      |                                                                                                                                                                    | Blanking pin. No signal (0V output) at high and output state at low. |

| 14                 | VB       | 14<br>DV <sub>DD</sub><br>DV <sub>DD</sub><br>DV <sub>DD</sub><br>DV <sub>DD</sub><br>DV <sub>DD</sub><br>DV <sub>DD</sub><br>DV <sub>DD</sub><br>DV <sub>DD</sub> | Connect a capacitor of approximately 0.1µF.                          |

| 9                  | CLK      | 3<br>DV <sub>DD</sub><br>DV <sub>DD</sub><br>DV <sub>DD</sub>                                                                                                      | Clock pin.                                                           |

| PIN NO. SYMBOL |                  | EQUIVALENT CIRCUIT                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                                   |  |  |

|----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15, 27         | DV <sub>SS</sub> |                                                                                                                                                                                                                 | Digital GND.                                                                                                                                                                                                                                  |  |  |

| 25             | AV <sub>SS</sub> |                                                                                                                                                                                                                 | Analog GND.                                                                                                                                                                                                                                   |  |  |

| 17             | I <sub>REF</sub> |                                                                                                                                                                                                                 | Connect resistance "16R" which is 16 times output resistance "R".                                                                                                                                                                             |  |  |

| 19             | V <sub>REF</sub> |                                                                                                                                                                                                                 | Sets output full scale value.                                                                                                                                                                                                                 |  |  |

| 22             | VG               | AV <sub>DD</sub><br>(1)<br>AV <sub>SS</sub><br>(1)<br>AV <sub>SS</sub><br>(1)<br>AV <sub>SS</sub><br>(1)<br>AV <sub>DD</sub><br>(1)<br>AV <sub>DD</sub><br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | Connect a capacitor of approximately 0.1µF.                                                                                                                                                                                                   |  |  |

| 20, 21         | AV <sub>DD</sub> |                                                                                                                                                                                                                 | Analog V <sub>DD</sub> .                                                                                                                                                                                                                      |  |  |

| 24             | IO               |                                                                                                                                                                                                                 | Current Output pin. Output can be retrieved be connecting resistance. The standard is $200\Omega$ .                                                                                                                                           |  |  |

| 23             | ĪŌ               |                                                                                                                                                                                                                 | Inverted Current Output pin. Connect to GN normally.                                                                                                                                                                                          |  |  |

| 13, 28         | DV <sub>DD</sub> |                                                                                                                                                                                                                 | Digital V <sub>DD</sub> .                                                                                                                                                                                                                     |  |  |

| 11             | CE               |                                                                                                                                                                                                                 | Chip Enable pin. No signal (0V output) at high make<br>power consumption minimum.                                                                                                                                                             |  |  |

| 18             | S <sub>REF</sub> |                                                                                                                                                                                                                 | Independent Constant-Voltage Source Output pi<br>using band gap reference. Stable voltag<br>independent of the fluctuation for supply voltage ca<br>be obtained by connecting to V <sub>REF</sub> . See Application<br>Circuit 2 for details. |  |  |

## Absolute Maximum Ratings T<sub>A</sub> = 25°C

## **Operating Conditions**

Supply Voltage

| • • • • • • • • • • • • • • • • • • • | ~9°                                          |                |                                        |

|---------------------------------------|----------------------------------------------|----------------|----------------------------------------|

| AV <sub>DD</sub> , AV                 | / <sub>SS</sub>                              |                | $5.0V \pm 0.25V$                       |

| DV <sub>DD</sub> , D                  | V <sub>SS</sub>                              |                | .5.0V ±0.25V                           |

| Reference I                           | nput Voltage (V <sub>REF</sub> )             |                | .0.5V to 2.0V                          |

| Clock Pulse                           | Width (t <sub>PW1</sub> , t <sub>PW0</sub> ) |                | 6.25ns (Min)                           |

| Temperature                           | e Range (T <sub>OPR</sub> )                  | <del>-</del> 2 | 20 <sup>0</sup> C to 75 <sup>0</sup> C |

|                                       |                                              |                |                                        |

## **Thermal Information**

| Thermal Resistance (Typical, Note 1) $\theta_{JA}$ ( | °C/W)              |

|------------------------------------------------------|--------------------|

| MQFP Package 1                                       | 22                 |

| Maximum Junction Temperature (MQFP Package)          |                    |

| Maximum Storage Temperature Range65°C to             | 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering 10s)             | 300 <sup>0</sup> C |

| (MQFP - Lead Tips Only)                              |                    |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

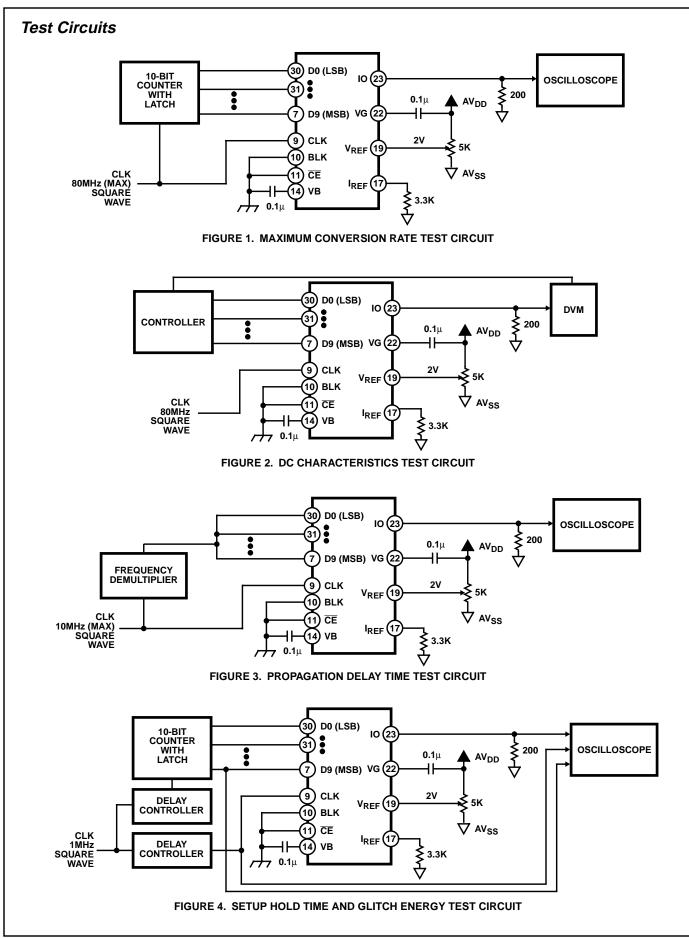

| <b>Electrical Specifications</b> | $T_A = 25^{o}C$ , $f_{CLK} = 80MHz$ , $V_{DD} = 5V$ , $R = 200\Omega$ , $V_{REF} = 2.0V$ , $16R = 3.3k\Omega$ |

|----------------------------------|---------------------------------------------------------------------------------------------------------------|

|----------------------------------|---------------------------------------------------------------------------------------------------------------|

| PARA                            | METER              | SYMBOL           | TEST CONDITIONS                            | MIN  | ТҮР  | МАХ  | UNITS   |

|---------------------------------|--------------------|------------------|--------------------------------------------|------|------|------|---------|

| Resolution                      |                    | n                |                                            | -    | 10   | -    | Bit     |

| Maximum Conversion Rate         |                    | f <sub>MAX</sub> |                                            | 80   | -    | -    | MHz     |

| Linearity Error                 |                    | EL               |                                            | -1.5 | -    | 1.5  | LSB     |

| Differential Linearity Erro     | or                 | ED               |                                            | -0.5 | -    | 0.5  | LSB     |

| Output Full-Scale Voltag        | je                 | V <sub>FS</sub>  |                                            | 1.8  | 1.94 | 2.0  | V       |

| Output Full-Scale Curren        | nt                 | I <sub>FS</sub>  |                                            | 9.0  | 9.7  | 10   | mA      |

| Output Off-Set Voltage          |                    | V <sub>OS</sub>  |                                            | -    | -    | 1    | mV      |

| Output Impedance                |                    |                  |                                            | -    | 300  | -    | kΩ      |

| Supply Current                  |                    | I <sub>DD</sub>  |                                            | -    | -    | 30   | mA      |

| Digital Input Current           | High Level         | Чн               |                                            | -    | -    | 5    | μΑ      |

|                                 | Low Level          | Ι <sub>IL</sub>  |                                            | -5   | -    | -    | μΑ      |

| Digital Input Voltage           | High Level         | VIH              |                                            | 2.45 | -    | -    | V       |

|                                 | Low Level          | VIL              |                                            | -    | -    | 0.85 | V       |

| Accuracy Guarantee Ou           | tput Voltage Range | V <sub>OC</sub>  |                                            | 1.8  | 1.94 | 2.0  | V       |

| Setup Time                      |                    | ts               |                                            | 3.0  | -    | -    | ns      |

| Hold Time                       |                    | t <sub>H</sub>   |                                            | 3.0  | -    | -    | ns      |

| Rise Time                       |                    | t <sub>r</sub>   |                                            | 5.0  | -    | -    | ns      |

| Propagation Delay Time          |                    | t <sub>PD</sub>  |                                            | -    | 5    | -    | ns      |

| Glitch Energy                   |                    | GE               | R <sub>OUT</sub> = 200Ω, 2V <sub>P-P</sub> | -    | -    | 30   | pV/s    |

| Differential Gain               |                    | DG               |                                            | -    | -    | 1.0  | %       |

| Differential Phase              |                    | DP               |                                            | -    | -    | 1.0  | Degrees |

| S <sub>REF</sub> Output Voltage |                    | S <sub>REF</sub> | $T_A = 25^{\circ}C$                        | 1.0  | 1.2  | 1.4  | V       |

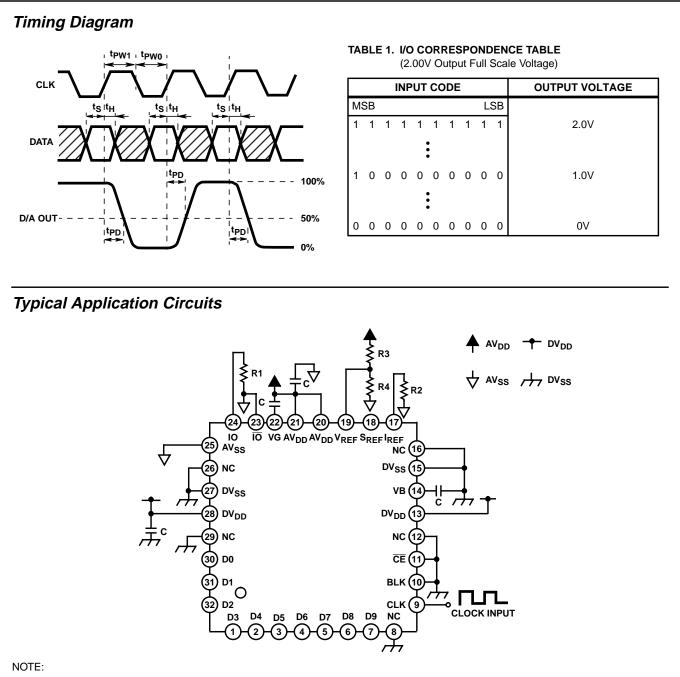

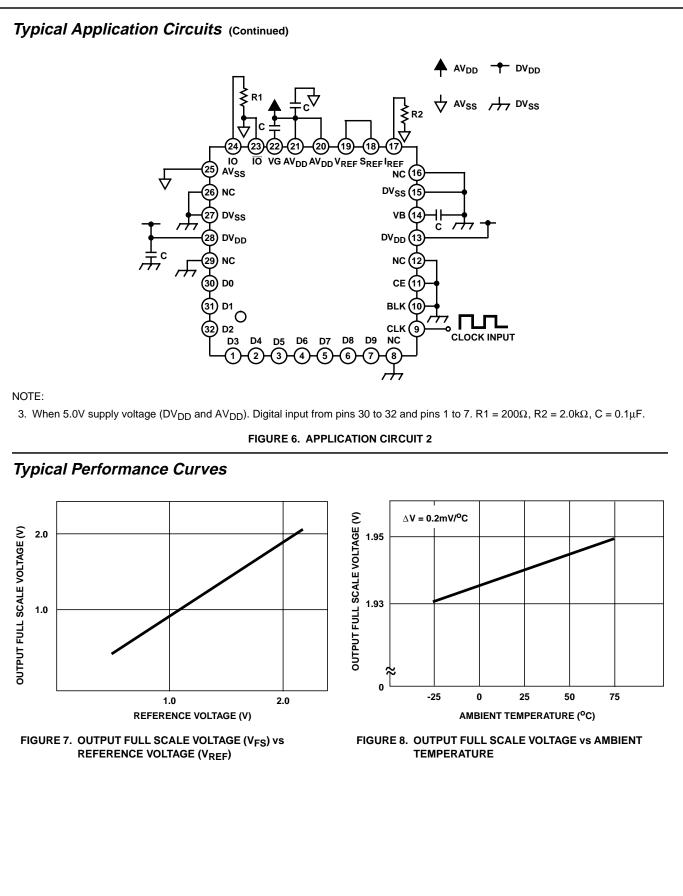

2. When 5.0V supply voltage (DV<sub>DD</sub> and AV<sub>DD</sub>). Digital input from pins 30 to 32 and pins 1 to 7. Pin 18 is Left Open When Using Normally. R1 =  $200\Omega$ , R2 =  $3.3\Omega$  (Resistance 16 Times R1), R3 =  $3.0k\Omega$ , R4 =  $2.0k\Omega$ , C =  $0.1\mu$ F.

## FIGURE 5. APPLICATION CIRCUIT 1

NOTE:

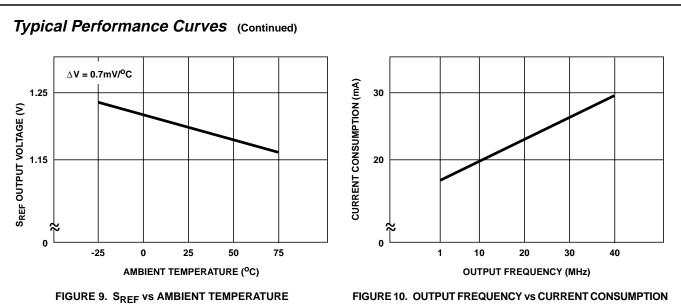

Standard Measurement Conditions and Description: V<sub>DD</sub> = 5.0V, V<sub>REF</sub> = 2.0V, R = 200Ω, 16R - 3.3kΩ, T<sub>A</sub> = 25<sup>o</sup>C. The temperature characteristics of external input data in Figure 10 = all "0" and "1" of rectangular wave; clock frequency = 80MHz.

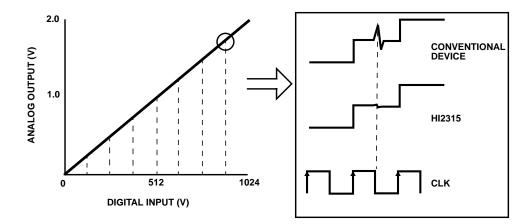

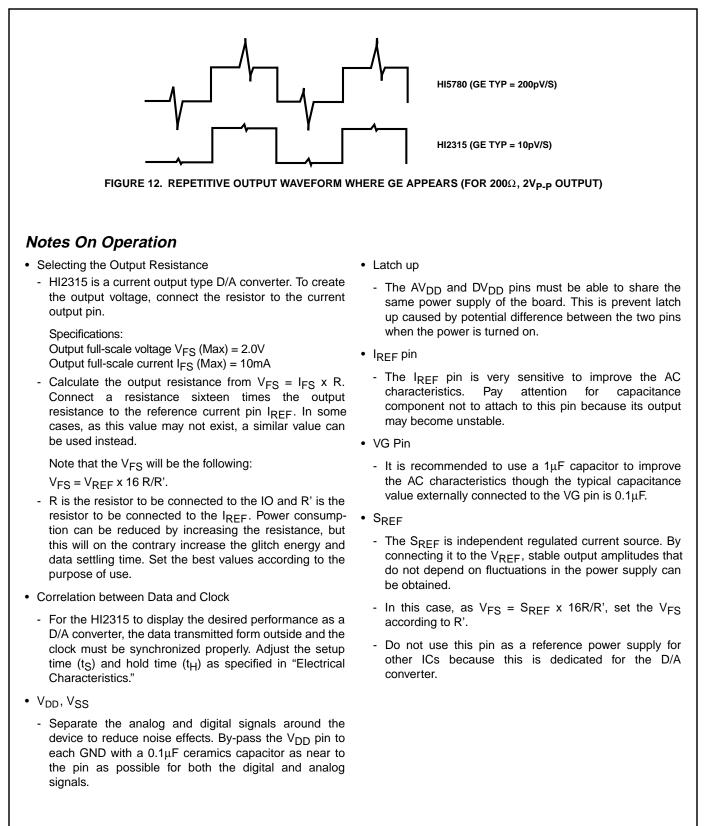

# GE (Glitch Energy)

GE, as described in the HI2315, is a spike noise which appears synchronizing with the clock falling edge when the input data (for 1 to 1024 input) changes to 128, 256, 384, 512, 640, 768, 896, and 1024. Figure 11 shows the change state of GE for the staircase wave output, and Figure 12

shows the repetitive output waveform where the GE appears. These figures exhibit the difference of this IC from the convention device.

The HI2315 reduces the GE as shown in Figures 11 and 12.

FIGURE 11. CHANGE OF GE FOR STAIRCASE WAVE OUTPUT

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com