## International **TOR** Rectifier

# IR2128

### **CURRENT SENSING SINGLE CHANNEL DRIVER**

#### Features

- Floating channel designed for bootstrap operation Fully operational to +600V

Tolerant to negative transient voltage dV/dt immune

- Gate drive supply range from 10 to 20V

- Undervoltage lockout

- 5V Schmitt-triggered input logic

- FAULT lead indicates shutdown has occured

- Output out of phase with input

#### Description

The IR2128 is a high voltage, high speed power MOSFET and IGBT driver. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The logic input is compatible with standard CMOS or LSTTL outputs. The protection circuity detects over-current in the driven power transistor and terminates the gate drive voltage. An open drain FAULT signal is provided to indicate that an over-current shutdown has occurred. The output driver features a high pulse current buffer stage designed for minimum crossconduction. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high side or low side configuration which operates up to 600 volts.

#### **Product Summary**

| VOFFSET                    | 600V max.       |

|----------------------------|-----------------|

| I <sub>O</sub> +/-         | 200 mA / 420 mA |

| Vout                       | 10 - 20V        |

| V <sub>CSth</sub>          | 250 mV          |

| t <sub>on/off</sub> (typ.) | 150 & 100 ns    |

#### Packages

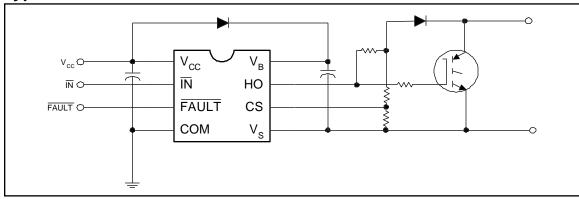

#### **Typical Connection**

#### **Absolute Maximum Ratings**

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The Thermal Resistance and Power Dissipation ratings are measured under board mounted and still air conditions.

|                     | Parameter                                          |               | Va                   | lue                   |       |

|---------------------|----------------------------------------------------|---------------|----------------------|-----------------------|-------|

| Symbol              | Definition                                         |               | Min.                 | Max.                  | Units |

| VB                  | High Side Floating Supply Voltage                  |               | -0.3                 | 625                   |       |

| VS                  | High Side Floating Offset Voltage                  |               | V <sub>B</sub> - 25  | V <sub>B</sub> + 0.3  |       |

| V <sub>HO</sub>     | High Side Floating Output Voltage                  |               | V <sub>S</sub> - 0.3 | V <sub>B</sub> + 0.3  |       |

| V <sub>CC</sub>     | Logic Supply Voltage                               |               | -0.3                 | 25                    | V     |

| VIN                 | Logic Input Voltage                                |               | -0.3                 | V <sub>CC</sub> + 0.3 |       |

| V <sub>FLT</sub>    | FAULT Output Voltage                               |               | -0.3                 | V <sub>CC</sub> + 0.3 |       |

| V <sub>CS</sub>     | Current Sense Voltage                              |               | V <sub>S</sub> - 0.3 | V <sub>B</sub> + 0.3  |       |

| dV <sub>s</sub> /dt | Allowable Offset Supply Voltage Transient          |               | —                    | 50                    | V/ns  |

| PD                  | Package Power Dissipation @ $T_A \le +25^{\circ}C$ | (8 Lead DIP)  | —                    | 1.0                   | w     |

|                     |                                                    | (8 Lead SOIC) | —                    | 0.625                 | vv    |

| $R_{\theta JA}$     | Thermal Resistance, Junction to Ambient            | (8 Lead DIP)  | —                    | 125                   | °C/W  |

|                     |                                                    | (8 Lead SOIC) | _                    | 200                   | °C/vv |

| Тj                  | Junction Temperature                               |               | _                    | 150                   |       |

| Τ <sub>S</sub>      | Storage Temperature                                |               | -55                  | 150                   | °C    |

| ΤL                  | Lead Temperature (Soldering, 10 seconds)           |               | _                    | 300                   |       |

#### **Recommended Operating Conditions**

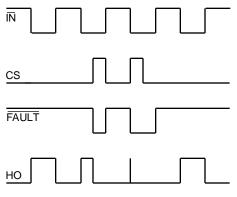

The Input/Output logic timing diagram is shown in Figure 1. For proper operation the device should be used within the recommended conditions. The  $V_S$  offset rating is tested with all supplies biased at 15V differential.

| Parameter        |                                                | Va                                |                     |       |

|------------------|------------------------------------------------|-----------------------------------|---------------------|-------|

| Symbol           | Definition                                     | Min.                              | Max.                | Units |

| VB               | High Side Floating Supply Voltage              | V <sub>S</sub> + 10               | V <sub>S</sub> + 20 |       |

| Vs               | High Side Floating Offset Voltage              | Note 1                            | 600                 |       |

| V <sub>HO</sub>  | High Side Floating Output Voltage              |                                   | VB                  |       |

| V <sub>CC</sub>  | Logic Supply Voltage 11.8                      |                                   | 20                  | V     |

| V <sub>IN</sub>  | Logic Input Voltage 0 V <sub>CC</sub>          |                                   | V <sub>CC</sub>     |       |

| V <sub>FLT</sub> | FAULT Output Voltage     0     V <sub>CC</sub> |                                   | V <sub>CC</sub>     |       |

| V <sub>CS</sub>  | Current Sense Signal Voltage                   | V <sub>S</sub> V <sub>S</sub> + 5 |                     |       |

| TA               | Ambient Temperature                            | -40                               | 125                 | °C    |

Note 1: Logic operational for V\_S of -5 to +600V. Logic state held for V\_S of -5V to -V\_BS.

#### **Dynamic Electrical Characteristics**

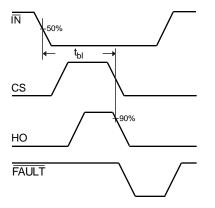

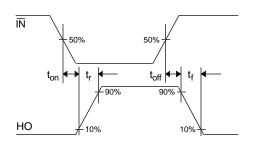

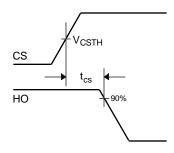

$V_{BIAS}$  (V<sub>CC</sub>, V<sub>BS</sub>) = 15V, C<sub>L</sub> = 1000 pF and T<sub>A</sub> = 25°C unless otherwise specified. The dynamic electrical characteristics are measured using the test circuit shown in Figure 3.

| Parameter        |                                       | Value |      |      |       |                          |

|------------------|---------------------------------------|-------|------|------|-------|--------------------------|

| Symbol           | Definition                            | Min.  | Тур. | Max. | Units | Test Conditions          |

| t <sub>on</sub>  | Turn-On Propagation Delay             | _     | 150  | 200  |       | $V_{\rm S} = 0V$         |

| t <sub>off</sub> | Turn-Off Propagation Delay            | _     | 100  | 150  |       | $V_{\rm S} = 600 V$      |

| t <sub>r</sub>   | Turn-On Rise Time                     | _     | 80   | 120  |       | C <sub>L</sub> = 1000 pF |

| t <sub>f</sub>   | Turn-Off Fall Time                    | —     | 40   | 60   | ns    | C <sub>L</sub> = 1000 pF |

| t <sub>bl</sub>  | Start-Up Blanking Time                | 500   | 750  | 900  |       |                          |

| t <sub>cs</sub>  | CS Shutdown Propagation Delay         | _     | 240  | 360  |       |                          |

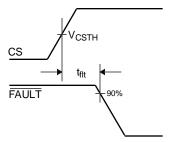

| t <sub>flt</sub> | CS to FAULT Pull-Up Propagation Delay | _     | 340  | 510  |       |                          |

#### **Static Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 15V and  $T_A$  = 25°C unless otherwise specified. The  $V_{IN}$ ,  $V_{TH}$  and  $I_{IN}$  parameters are referenced to COM. The  $V_O$  and  $I_O$  parameters are referenced to  $V_S$ .

| Parameter          |                                                                 |     | Value |      |               |                                                   |

|--------------------|-----------------------------------------------------------------|-----|-------|------|---------------|---------------------------------------------------|

| Symbol             | I Definition                                                    |     | Тур.  | Max. | Units         | Test Conditions                                   |

| V <sub>IH</sub>    | Logic "0" Input Voltage (OUT = LO)                              |     | _     | _    | V             | $V_{CC} = 10V \text{ to } 20V$                    |

| V <sub>IL</sub>    | Logic "1" Input Voltage (OUT = HI)                              | _   | _     | 0.8  | v             | $V_{\rm CC}$ = 10V to 20V                         |

| V <sub>CSTH+</sub> | CS Input Positive Going Threshold                               | 180 | 250   | 320  |               | $V_{CC}$ = 10V to 20V                             |

| V <sub>OH</sub>    | High Level Output Voltage, V <sub>BIAS</sub> - VO               | —   | —     | 100  | mV            | IO = 0A                                           |

| V <sub>OL</sub>    | Low Level Output Voltage, VO                                    | —   | —     | 100  |               | IO = 0A                                           |

| I <sub>LK</sub>    | Offset Supply Leakage Current                                   | —   | —     | 50   |               | $V_B = V_S = 600V$                                |

| I <sub>QBS</sub>   | Quiescent V <sub>BS</sub> Supply Current                        | —   | 150   | 300  |               | $V_{IN} = 0V \text{ or } 5V$                      |

| IQCC               | Quiescent V <sub>CC</sub> Supply Current                        | —   | 60    | 120  |               | $V_{IN} = 0V \text{ or } 5V$                      |

| I <sub>IN+</sub>   | Logic "1" Input Bias Current                                    | —   | 7.0   | 15   | μA            | $V_{IN} = 0V$                                     |

| I <sub>IN-</sub>   | Logic "0" Input Bias Current                                    | —   | —     | 1.0  |               | $V_{IN} = 5V$                                     |

| I <sub>CS+</sub>   | "High" CS Bias Current                                          | —   | —     | 1.0  |               | $V_{CS} = 3V$                                     |

| I <sub>CS-</sub>   | "High" CS Bias Current                                          | —   | —     | 1.0  | $V_{CS} = 0V$ |                                                   |

| V <sub>BSUV+</sub> | V <sub>BS</sub> Supply Undervoltage Positive Going<br>Threshold | 8.8 | 10.3  | 11.8 | V             |                                                   |

| V <sub>BSUV-</sub> | V <sub>BS</sub> Supply Undervoltage Negative Going<br>Threshold | 7.5 | 9.0   | 10.6 | v             |                                                   |

| I <sub>O+</sub>    | Output High Short Circuit Pulsed Current                        | 200 | 250   | _    | mA            | $V_{O} = 0V, V_{IN} = 0V$<br>PW $\leq 10 \ \mu s$ |

| I <sub>O-</sub>    | Output Low Short Circuit Pulsed Current                         | 420 | 500   | —    | IIIA          | $V_{O}$ = 15V, $V_{IN}$ = 5V<br>PW $\leq$ 10 µs   |

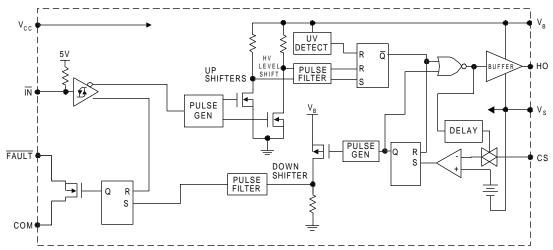

#### **Functional Block Diagram**

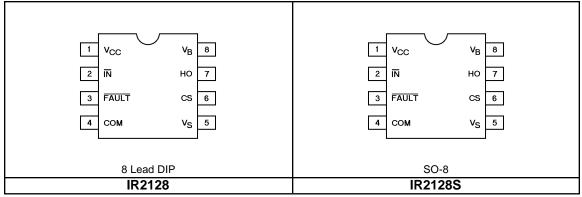

#### Lead Definitions

| Le                    | ad                                                            |  |

|-----------------------|---------------------------------------------------------------|--|

| Symbol                | Description                                                   |  |

| V <sub>CC</sub><br>IN | Logic and gate drive supply                                   |  |

| ĪN                    | Logic input for gate driver output (HO), out of phase with HO |  |

| FAULT                 | Indicates over-current shutdown has occurred, negative logic  |  |

| COM                   | Logic ground                                                  |  |

| V <sub>B</sub>        | High side floating supply                                     |  |

| HO                    | High side gate drive output                                   |  |

| V <sub>S</sub>        | High side floating supply return                              |  |

| CS                    | Current sense input to current sense comparator               |  |

#### Lead Assignments

B-132 CONTROL INTEGRATED CIRCUIT DESIGNERS' MANUAL

#### **Device Information**

| Process & Design Rule |         |              | HVDCMOS 4.0 µm           |  |  |

|-----------------------|---------|--------------|--------------------------|--|--|

| Transistor Count      |         |              | 206                      |  |  |

| Die Size              |         |              | 77 X 85 X 26 (mil)       |  |  |

| Die Outline           |         |              |                          |  |  |

| Thickness of Gat      | e Oxide |              | 800Å                     |  |  |

| Connections           |         | Material     | Poly Silicon             |  |  |

| Firs                  | st      | Width        | 4 µm                     |  |  |

| Lay                   |         | Spacing      | 6 µm                     |  |  |

|                       | -       | Thickness    | 5000Å                    |  |  |

|                       |         | Material     | Al - Si (Si: 1.0% ±0.1%) |  |  |

| Sec                   | cond    | Width        | 6 µm                     |  |  |

| Lay                   |         | Spacing      | 7 µm                     |  |  |

|                       | -       | Thickness    | 20,000Å                  |  |  |

| Contact Hole Din      | nension |              | 8 µm X 8 µm              |  |  |

| Insulation Layer      |         | Material     | PSG (SiO <sub>2</sub> )  |  |  |

|                       |         | Thickness    | 1.5 µm                   |  |  |

| Passivation           |         | Material     | PSG (SiO <sub>2</sub> )  |  |  |

|                       |         | Thickness    | 1.5 µm                   |  |  |

| Method of Saw         |         |              | Full Cut                 |  |  |

| Method of Die Bo      | ond     |              | Ablebond 84 - 1          |  |  |

| Wire Bond             |         | Method       | Thermo Sonic             |  |  |

|                       |         | Material     | Au (1.0 mil / 1.3 mil)   |  |  |

| Leadframe             |         | Material     | Cu                       |  |  |

|                       |         | Die Area     | Ag                       |  |  |

|                       |         | Lead Plating | Pb : Sn (37 : 63)        |  |  |

| Package Types         |         |              | 8 Lead PDIP / SO-8       |  |  |

|                       |         | Materials    | EME6300 / MP150 / MP190  |  |  |

| Remarks:              |         |              |                          |  |  |

Figure 1. Input/Output Timing Diagram

Figure3. Start-up Blanking Time Waveform Definitions

Figure 2. Switching Time Waveform Definition

Figure 4. CS Shutdown Waveform Definitions

Figure 5. CS to FAULT Waveform Definitions