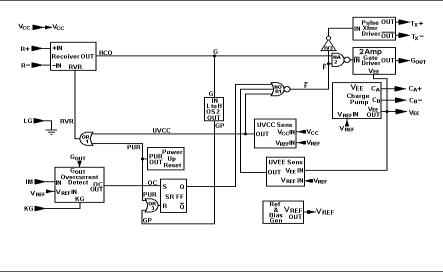

## IXBD4410 / IXBD4411 ISOSMART™ Half Bridge Driver Chipset

| Туре       | Description                   | Package      | Temperature Range |

|------------|-------------------------------|--------------|-------------------|

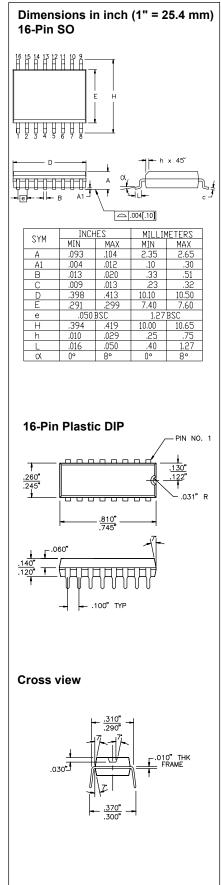

| IXBD4410PI | Full-Feature Low-Side Driver  | 16-Pin P-DIP |                   |

| IXBD4411PI | Full-Feature High-Side Driver | 16-Pin P-DIP |                   |

| IXBD4410SI | Full-Feature Low-Side Driver  | 16-Pin SO    | -40 to +85°C      |

| IXBD4411SI | Full-Feature High-Side Driver | 16-Pin SO    | -40 to +85°C      |

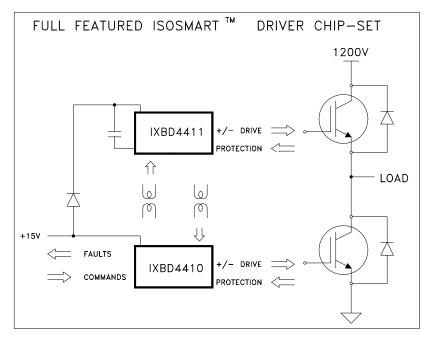

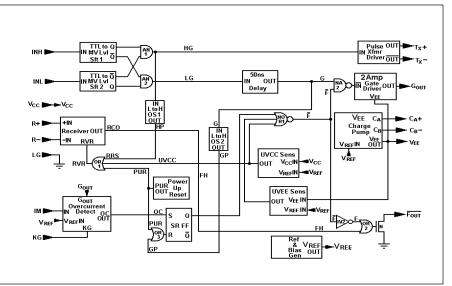

#### The IXBD4410/IXBD4411

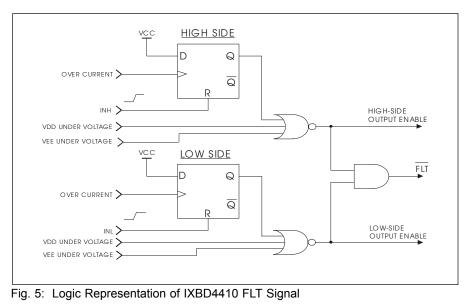

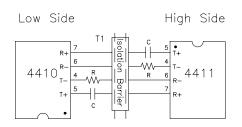

ISOSMART chipset is designed to control the gates of two Power MOSFETs or Power IGBTs that are connected in a half-bridge (phaseleg) configuration for driving multiple-phase motors, or used in applications that require half-bridge power circuits. The IXBD4410/ IXBD4411 is a full-feature chipset consisting of two 16-Pin DIP or SO devices interfaced and isolated by two small-signal ferrite pulse transformers. The small-signal transformers provide greater than 1200 V isolation.

Even with commutating noise ambients greater than ±50 V/ns and up to 1200 V potentials, this chipset establishes error-free two-way communications between the system ground-referenced IXBD4410 and the inverter outputreferenced IXBD4411. They incorporate undervoltage  $V_{\text{DD}}$  or  $V_{\text{EE}}$  lockout and overcurrent or desaturation shutdown to protect the IGBT or Power MOSFET devices from damage.

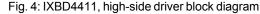

The chipset provides the necessary gate drive signals to fully control the grounded-source low-side power device as well as the floatingsource high-side power device. Additionally, the IXBD4410/4411 chipset provides a negative-going, off-state gate drive signal for improved turn-off of IGBTs or Power MOSFETs and a system logiccompatible status fault output FLT to indicate overcurrent or desaturation, and undervoltage  $V_{DD}$  or  $V_{EE}$ . During a status fault, both devices drive their respective gate outputs at V<sub>EE</sub>, and keep their driven MOSFETs or IGBTs off.

IXYS reserves the right to change limits, test conditions and dimensions.

#### Features

- 1200 V or greater low-to-high side isolation.

- Drives Power Systems Operating on up to 575 V AC mains

- dv/dt immunity of greater than ±50V/ns

- Proprietary low-to-high side level translation and communication

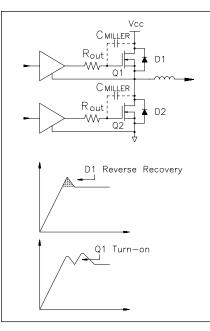

- On-chip negative gate-drive supply to ensure Power MOSFET or IGBT turn-off and to prevent gate noise interference

- 5 V logic compatible HCMOS inputs with hysteresis

- Available in either the 16-Pin DIP or the 16-Pin wide-body, small-outline plastic package

- 20 ns switching time with 1000 pF load; 100 ns switching time with 10,000 pF load

- 100 ns propagation delay time

- 2 A peak output drive capability

- Self shut-down of output in response to over-current or short-circuit

- Under-voltage and over-voltage V<sub>DD</sub> lockout protection

- Protection from cross conduction of the half bridge

- Logic compatible fault indication from both low and high-side driver

#### Applications

- 1- or 3-Phase Motor Controls

- Switch Mode Power Supplies (SMPS)

- Uninterruptible Power Supplies (UPS)

- Induction Heating and Welding Systems

- Switching Amplifiers

- General Power Conversion Circuits

#

## IXBD4410 / IXBD4411

| Symbol                                                  | Definition                                                          |                       | Maximum Ratings       |                      |           |  |

|---------------------------------------------------------|---------------------------------------------------------------------|-----------------------|-----------------------|----------------------|-----------|--|

|                                                         | Supply Voltage                                                      |                       | -0.5                  |                      | V         |  |

| V <sub>in</sub>                                         | Input Voltage (INH, INL)                                            |                       | -0.5 to \             | √ <sub>DD</sub> +0.5 | 5 V       |  |

| l<br>in                                                 | Input Current (INL, INH, IM)                                        |                       | 0                     | mA                   |           |  |

| l <sub>o</sub> (rev)                                    | Peak Reverse Output Current (OUT)                                   |                       | 2                     | 2                    | A         |  |

| P <sub>D</sub>                                          | Maximum Power Dissipation ( $T_A \le 2$                             | 25°C)                 |                       | •                    |           |  |

|                                                         | 16 Pin PDIP (PI)<br>16 Pin SOIC (SI)                                |                       |                       | .6<br>.2             | W<br>W    |  |

| θ <sub>JA</sub>                                         | Thermal Impedance (Junction To A                                    | mbient)               | 1.                    | 2                    | vv        |  |

| JA                                                      | 16 Pin PDIP (PI)                                                    | ,                     | 7                     | 5 °                  | C/W       |  |

|                                                         | 16 Pin SOIC (SI)                                                    |                       | 10                    | ° 00                 | C/W       |  |

| T <sub>A</sub>                                          | Operating Ambient Temperature                                       |                       | -40 to                |                      | °C        |  |

| T_<br>⊤                                                 | Maximum Junction Temperature                                        |                       |                       | 50                   | °C<br>℃   |  |

| T <sub>stg</sub>                                        | Storage Temperature Range<br>Lead Soldering Temperature for 10      | e                     | -55 to<br>30          |                      | °C<br>°C  |  |

| T                                                       |                                                                     | 3                     | 50                    |                      | 0         |  |

|                                                         | ended Operating Conditions                                          |                       |                       |                      |           |  |

|                                                         | Supply Voltage                                                      |                       |                       | 20 16 F              | V         |  |

| V <sub>DD</sub> /LG<br>L <sub>Gh</sub> /L <sub>GI</sub> | Maximum Common Mode dv/dt                                           |                       | 10 to<br>±5           |                      | V<br>V/ns |  |

| Gh' Gl                                                  |                                                                     |                       | <u> </u>              |                      | v/115     |  |

| Symbol                                                  | Definition/Condition                                                | C                     | haracteri             | stic Va              | alues     |  |

|                                                         | (T <sub>A</sub> = 25°C, V <sub>DD</sub> = 1                         |                       | s otherwis            | e spec               | ified)    |  |

|                                                         |                                                                     | min.                  | typ.                  | max.                 |           |  |

| INL, INH In                                             | puts (referred to LG)                                               |                       | 1                     |                      |           |  |

| <b>V</b> <sub>t+</sub>                                  | Positive-Going Threshold                                            | 3.65                  |                       |                      | V         |  |

| V <sub>t-</sub>                                         | Negative-Going Threshold                                            |                       |                       | 1.5                  | V         |  |

| V <sub>ih</sub>                                         | Input Hysteresis                                                    |                       | .6                    |                      | V         |  |

| l <sub>in</sub>                                         | Input Leakage Current/ $V_{in} = V_{DD}$ or LG                      | -1                    |                       | 1                    | μA        |  |

| C <sub>in</sub>                                         | InputCapacitance                                                    |                       | 10                    |                      | pF        |  |

| Open Draii                                              | n Fault Output (referred to LG)                                     |                       |                       |                      |           |  |

| V <sub>oh</sub>                                         | HI Output/R <sub>pu</sub> = 10 k $\Omega$ to V <sub>DD</sub>        | V <sub>DD</sub> -0.05 |                       |                      | V         |  |

| V <sub>ol</sub>                                         | $LO Output/I_0 = 4 mA$                                              | 00                    | 0.4                   | 0.7                  | V         |  |

|                                                         | ut (referred to LG)                                                 |                       |                       |                      |           |  |

|                                                         | · · ·                                                               | V 0.05                |                       |                      | V         |  |

| V <sub>oh</sub><br>V <sub>ol</sub>                      | HI Output/I <sub>o</sub> = -5 mA<br>LO Output/I <sub>o</sub> = 5 mA | V <sub>DD</sub> -0.05 | V <sub>EE</sub> +0.05 |                      | v         |  |

| °₀ı<br>R <sub>o</sub>                                   | Output HI Res./ $I_{o}$ = -0.1 A                                    |                       | 3                     | 5                    | Ω         |  |

| R                                                       | Output LO Res./ $I_0 = 0.1 \text{ A}$                               |                       | 3                     | 4                    | Ω         |  |

| l <sub>pk</sub>                                         | Peak Output Current/C <sub>1</sub> = 10 nF                          | 1.5                   | 2                     | •                    | A         |  |

|                                                         | eferred to KG)                                                      |                       |                       |                      |           |  |

| V <sub>t+</sub>                                         | Positive-Going Threshold                                            | 0.24                  | 0.3                   | 0.36                 | V         |  |

| C <sub>in</sub>                                         | Input Capacitance                                                   | 0.27                  | 10                    | 0.00                 | pF        |  |

| о <sub>іп</sub><br>R <sub>s</sub>                       | Shorting Device Output Resistance                                   | 80                    | 120                   | 150                  | Ω         |  |

|                                                         |                                                                     |                       |                       |                      |           |  |

|                                                         | y (referred to LG)                                                  |                       |                       |                      |           |  |

| V                                                       | Output Voltage/I <sub>o</sub> = 1 mA, C <sub>o</sub> = 1 $\mu$ F    | -5                    | -5.5                  | -6.5                 | V         |  |

| out                                                     | Output Current/V <sub>out</sub> = $0.70 \cdot V_{EE}$               | -20                   | -25                   |                      | mA        |  |

| f <sub>inv</sub>                                        | Inverting Frequency                                                 |                       | 350                   |                      | kHz       |  |

| V <sub>EEF</sub>                                        | Undervoltage Fault Indication                                       | -4                    |                       | -4.8                 | V         |  |

## **TIXYS**

| Symbol                 | Definition/Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | = 25°C, V <sub>DD</sub> = 15 V, unle                   | Characte |                                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------|--------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | (1.9. <i>i</i> , i <sub>A</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | min.                                                   | typ.     | max.                                                               |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>DD</sub> Underv | voltage Lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        |          |                                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>uv</sub>        | Drop Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9.5                                                    | 10.5     | 11.5                                                               | V                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>uh</sub>        | Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.1                                                    | 0.3      | 0.5                                                                | V                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Quiescent              | Power Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |          |                                                                    |                                       | IXBD4410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I <sub>DD</sub>        | $V_{DD}$ Current/ $V_{in}$ = $V_{DD}$ or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LG, I <sub>o</sub> = 0                                 | 3        | 8                                                                  | mA                                    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

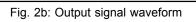

| INL and IN             | <b>H Inputs</b> (Fig. 2a, 2b))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        |          |                                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| t <sub>d(on)</sub>     | Turn-on delay time;<br>4410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C <sub>L</sub> =1nF                                    | 250      | 275                                                                | ns                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| t <sub>r</sub>         | Rise time;<br>4410 or 4411                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C <sub>L</sub> =10 nF<br>C <sub>L</sub> =1 nF          | 70<br>15 | 100<br>20                                                          | ns<br>ns                              | Fig. 1a Overcurrent Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| t <sub>d(off)</sub>    | Turn-off delay time<br>4410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C <sub>L</sub> =1nF                                    | 150      | 175                                                                | ns                                    | Γ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| t <sub>r</sub>         | Fall time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | С <sub>L</sub> =10nF<br>С <sub>L</sub> =1nF            | 70<br>15 | 150<br>20                                                          | ns<br>ns                              | VOUT 15V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| t <sub>dlh(off)</sub>  | 4410 to 4411<br>Turn-off delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C <sub>L</sub> =1nF                                    | 250      | 275                                                                | ns                                    | IXBD4411 -5V<br>5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| t <sub>dlh(on)</sub>   | 4410 to 4411<br>Turn-on delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C <sub>L</sub> =1nF                                    | 270      | 300                                                                | ns                                    | Fig. 1b Overcurrent Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fault Outp             | ut Delay for any Fault Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | onditions (4410/4411)                                  |          |                                                                    |                                       | ng. Ib Overcuirent Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| t <sub>FLT</sub>       | $\overline{FLT}$ Delay/ $R_{pu}$ = 2 k $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C <sub>L</sub> = 20 pF                                 | 2        | 3                                                                  | us                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Overcurre              | nt Protection Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        | - I      |                                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| t <sub>oc</sub>        | Driver-Off delay time<br>(Fig. 1a, 1b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C <sub>L</sub> = 10 nF                                 | 200      | 300                                                                | ns                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

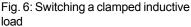

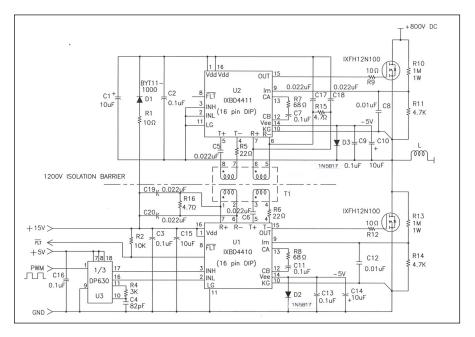

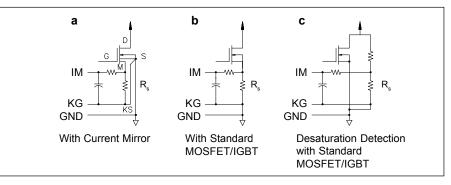

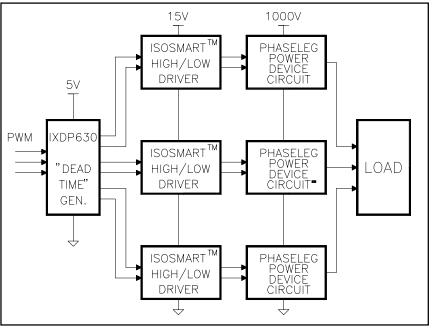

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                        |          |                                                                    |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |