## **Description**

The KL5KUSB110from Kawasaki , is a low cost, high speed Universal Serial Bus (USB) to ATAPI/IDE Controller. It's 16 bit RISC processor and built in BIOS ROM translates USB ATAPI host commands to a wide variety IDE storage devices such as, HDD, FD, CD-ROM, CD-WR, ZIP Drives LS120 drives. The KL5KUSB110's unique interface architecture to external serial flash EEPROM allows flexibility to upgrade and support a variety of IDE/ATAPI based disk drives, without changing peripheral hardware. This is accomplished when new functions are uploaded into the Serial EEPROM from the USB Host PC. The KL5KUSB110's Memory/GPIO bi-directional Port supports both 8 and 16 bit PIO modes. The USB port supports up to the maximum 12 Mbits/sec USB transfer rate. All USB protocol modes are supported; Isochronous ( up to 1024 bytes ), Bulk, Interrupt and Control. The KL5KUSB110 uses IDE as a physical interface, but commands to the external disk can be either IDE or ATAPI commands. ATA-1,2&3 based disk drives are also supported. The KL5KUSB110 device supports a wide variety of Disk drive solutions due to it's Maximum Disk drive throughput rate up to 1Mbytes/sec and comprehensive PnP USB/ATAPI drivers.

#### **Features**

- Advanced 16 Bit processor for USB transaction processing and control data processing

- Compliant with the USB 1.0/1.1 (Universal Serial Bus)

- Compatible to a wide variety of Storage devices.

- Data transfer in PIO mode, 8 or 16 bit

- Plug and Play compatible

- Maximum disk throughput up to 1MBytes/sec

- I<sup>2</sup>C interface

- Utilizes low cost external crystal circuitry

- 3K x 8 internal general purpose buffer.

- USB host device drivers available

- Suspend, resume and low power modes

- 3.3 Vdd operation

- Single-chip solution in a 100 pin LQFP

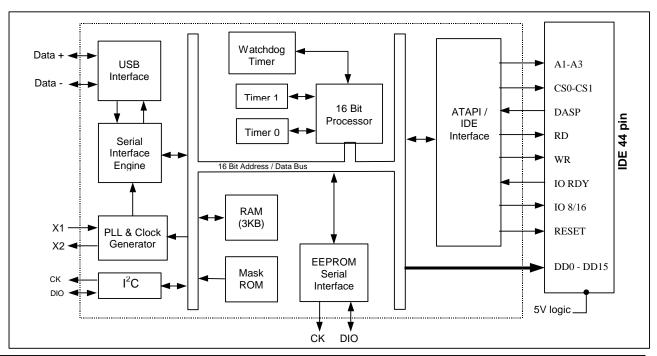

## **Block Diagram**

## **Function Description**

#### 16 Bit Processor

The integrated 16 bit processor serves as a micro controller for USB peripherals. The processor can execute approximately five million instructions per second. With this processing power it allows the design of intelligent peripherals that can process data prior to passing it on to the host PC, thus improving overall performance of the system. The masked ROM in the this device or external memory contains a specialized instruction set that has been designed for highly efficient coding of processing algorithms and USB transaction processing.

The 16-bit processor is designed for efficient data execution by having direct access to the RAM Buffer, external memory, I/O interfaces, and all the control and status registers

The processor supports prioritized vectored hardware interrupts and has as many as 240 software interrupt vectors.

The processor provides six addressing modes, supporting memory-to-memory, memory-to-register, register-to-register, immediate-to-register or immediate-to-memory operations. Register, direct, immediate, indirect, and indirect indexed addressing modes are supported. In addition, there is an auto-increment mode in which a register, used as an address pointer is automatically incremented after each use, making repetitive operations more efficient both from a programming and a performance standpoint.

The processor features a full set of program control, logical, and integer arithmetic instructions. All instructions are sixteen bits wide, although some instructions require operands, which may occupy another one or two words. Several special "short immediate" instructions are available, so that certain frequently used operations with small constant operand will fit into a 16-bit instruction.

#### **RAM Buffer**

The USB controller contains internal buffer memory. The memory is used to buffer data and USB packets and accessed by the 16 Bit processor and the SIE. USB transactions are automatically routed to the memory buffer. The 16-bit processor has the ability to set up pointers and block sizes in buffer memory for USB transactions. Data is read from the interface and is processed and packetized by the 16-bit I/O processor. Memory buffer can also be configured as "Double port buffer" multiple sector data buffer, 512 bytes or 1024 bytes simultaneously transferred from Disk to USB port and via versa

### **ROM**

3Kx16 internal Mask BIOS ROM, supports USB to ATAPI/IDE macros, USB functions, serial EEPROM programmability, DRAM, UART, and other functions. Executable code can run from either internal RAM, ROM, or external ROM. Also, available extended external SRAM or DRAM to store disk cash data.

#### **IDE Port**

8 or 16 bits, data port, supports Master/Slave multiple disks. Either ATAPI or IDE commands, Supports ATA-1, 2 &3 standards. Max Disk operation throughput rate is up to 1 Mbytes/sec

#### WDM ATAPI/IDE Drivers

Development Kit includes generic PnP USB mini-port driver, ATAPI Driver for Windows 98 /NT2000 and Mac8.5 for IDE Disk Drive class devices . Development time is significantly reduced.

### **PLL Clock Generator**

The PLL circuitry is provided to generate the internal 48MHz clock requirements. This circuitry is designed to allow use of a low cost 12 MHz external crystal which is connected to the USB3 pins X1 and X2. If an external 12 MHz clock is available in the application, it may be used in lieu of the crystal circuit and connected directly to the X1 input pin.

#### **USB** Interface

The USB controller meets the Universal Serial Bus (USB) specification ver 1.0 and 1.1. The transceiver is capable of transmitting and receiving serial data at the USB's full speed, 12 Mbits/sec data rate. The driver portion of the transceiver is differential, while the receive section is comprised of a differential receiver and two single ended receivers. Internally, the transceiver interfaces to the SIE logic. Externally, the transceiver connects to the physical layer of the USB.

#### **UART Serial Interface**

The UART can be configured for a wide selection of baud rates, 300 to 230.4 K baud, and support a set of control signals. Each UART provides a means for external serial devices to access the USB.

### Serial EEPROM Support

The USB Controller serial interface is used to provide access to external EEPROM's. The interface can support a variety of serial EEPROM formats.

#### **Development Kit**

- For all of its products, Kawasaki offers Development Kits (DVKs), USB to IDE reference

design board, training, and integration assistance from an experienced staff of engineers. By

using the DVKs, Kawasaki customers can have a working USB product within 3 weeks.

The following items are included in the KL5KUSB110Development Kit:

- WDM Windows 98/NT2000 and Mac8.5 drivers, and ATAPI to USB driver object code, optional source code

- USB to ATAPI/IDE protocol translator firmware source code example

- PnP USB ATAPI Disk Drive Demo object code, optional source code examples is available

- Application notes

### **Electrical Characteristics**

#### ABSOLUTE MAXIMUM RATINGS

| Parameter           | Symbol                        | Ratings                       | Unit |

|---------------------|-------------------------------|-------------------------------|------|

| Supply Voltage      | $V_{DD5}$                     | -0.6 to 6.0                   | V    |

|                     | $V_{DD}$                      | -0.3 to 4.0                   | V    |

| Input Voltage       | V <sub>IN</sub> (Normal)      | -0.6 to V <sub>DD5</sub> +0.6 | V    |

|                     |                               | -0.3 to V <sub>DD</sub> +0.3  | V    |

|                     | V <sub>IN</sub> (5V Tolerant) | -0.3 to 7.3                   | V    |

| DC Output Current   | I <sub>OUT</sub>              | ±30                           | mA   |

| Storage Temperature | TSTG                          | -55 to 125 **                 | °C   |

<sup>\*\*</sup>Plastic Package

DC Characteristics and conditions (V<sub>DD5</sub> @ 3V±.3V)

| Symbol          | Parameter               | Condition          | Value |      |      | Unit |

|-----------------|-------------------------|--------------------|-------|------|------|------|

|                 |                         |                    | Min   | Тур  | Max  |      |

| $V_{DD5}$       | Supply Voltage          | =                  | 3.0   | 3.3  | 3.6  | V    |

| V <sub>IH</sub> | Input high voltage      | CMOS               | 2.15  | -    | -    | V    |

| $V_{IL}$        | Input low voltage       | CMOS               | -     | ı    | 0.95 | V    |

| V+              | Input high voltage      | TTL Schmitt        |       | 1.32 | 1.75 | V    |

|                 |                         | CMOS Schmitt       |       | 2.17 | 2.65 | V    |

| V-              | Input low voltage       | TTL Schmitt        | 0.45  | 0.86 | -    | V    |

|                 |                         | CMOS Schmitt       | 0.50  | 1.03 | -    | V    |

| $V_{H}$         | Hysteresis voltage      | TTL Schmitt        | 0.25  | -    | -    | V    |

|                 |                         | CMOS Schmitt       | 0.56  | ı    | -    | V    |

| I <sub>IH</sub> | Input high current      | $V_{IN} = V_{DD5}$ | -10   | -    | 10   | μΑ   |

| I <sub>IL</sub> | Input low current       | $V_{IN} = V_{ss}$  | -10   | -    | 10   | μΑ   |

| V <sub>OH</sub> | Output high voltage     | $I_{OH} = -4mA$    | 2.4   | -    | -    | V    |

| V <sub>OL</sub> | Output low voltage      | $I_{OL} = 4mA$     | -     | -    | 0.4  | V    |

| l <sub>OZ</sub> | 3-state leakage current | $V_{OL}=V_{DD5}$   | -10   | -    | 10   | μΑ   |

|                 |                         | $V_{IN}=V_{SS}$    | -12   | -34  | -100 | μΑ   |

<sup>\*</sup>IDDS is design dependent

Kawasaki LSI assumes no responsibility or liability for (1) any errors or inaccuracies contained in the information herein and (2) the use of the information or a portion thereof in any application, including any claim for (a) copyright or patent infringement or (b) direct, indirect, special or consequential damages. There are no warranties extended or granted by this document. The information herein is subject to change without notice form Kawasaki LSI