###

# 400ksps, +5V, 8-/4-Channel, 10-Bit ADCs with +2.5V Reference and Parallel Interface

### **General Description**

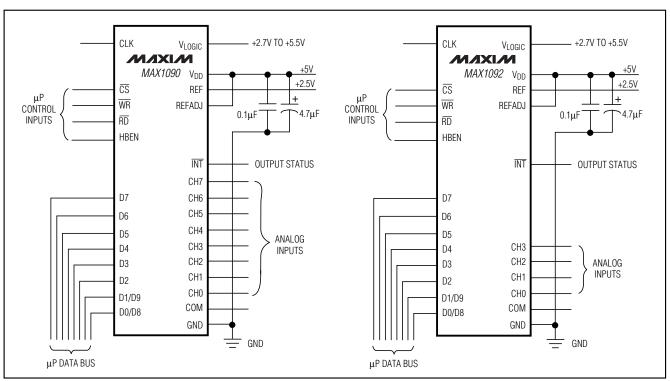

The MAX1090/MAX1092 low-power, 10-bit analog-to-digital converters (ADCs) feature a successive-approximation ADC, automatic power-down, fast wake-up (2µs), on-chip clock, +2.5V internal reference, and high-speed, byte-wide parallel interface. The devices operate with a single +5V analog supply and feature a VLOGIC pin that allows them to interface directly with a +2.7V to +5.5V digital supply.

Power consumption is only 10mW (VDD = VLOGIC) at a 400ksps max sampling rate. Two software-selectable power-down modes enable the MAX1090/MAX1092 to be shut down between conversions; accessing the parallel interface returns them to normal operation. Powering down between conversions can cut supply current to under  $10\mu A$  at reduced sampling rates.

Both devices offer software-configurable analog inputs for unipolar/bipolar and single-ended/pseudo-differential operation. In single-ended mode, the MAX1090 has eight input channels and the MAX1092 has four input channels (four and two input channels, respectively, when in pseudo-differential mode).

Excellent dynamic performance and low power combined with ease of use and small package size make these converters ideal for battery-powered and data-acquisition applications or for other circuits with demanding power consumption and space requirements.

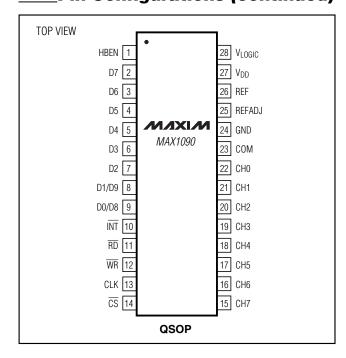

The MAX1090 is available in a 28-pin QSOP package, while the MAX1092 comes in a 24-pin QSOP. For pincompatible +3V, 10-bit versions, refer to the MAX1091/MAX1093 data sheet.

#### **Applications**

| Industrial Control Systems | Data Logging       |

|----------------------------|--------------------|

| Energy Management          | Patient Monitoring |

| Data-Acquisition Systems   | Touchscreens       |

### **Ordering Information**

| PART        | TEMP. RANGE    | PIN-PACKAGE | INL<br>(LSB) |

|-------------|----------------|-------------|--------------|

| MAX1090ACEI | 0°C to +70°C   | 28 QSOP     | ±0.5         |

| MAX1090BCEI | 0°C to +70°C   | 28 QSOP     | ±1           |

| MAX1090AEEI | -40°C to +85°C | 28 QSOP     | ±0.5         |

| MAX1090BEEI | -40°C to +85°C | 28 QSOP     | ±1           |

Ordering Information continued at end of data sheet.

#### **Features**

- ♦ 10-Bit Resolution, ±0.5LSB Linearity

- ♦ +5V Single-Supply Operation

- ♦ User-Adjustable Logic Level (+2.7V to +5.5V)

- ♦ Internal +2.5V Reference

- ♦ Software-Configurable Analog Input Multiplexer

- 8-Channel Single-Ended/

- 4-Channel Pseudo-Differential (MAX1090)

- 4-Channel Single-Ended/

- 2-Channel Pseudo-Differential (MAX1092)

- ♦ Software-Configurable Unipolar/Bipolar Analog Inputs

- Low Current: 2.2mA (400ksps)

1.0mA (100ksps)

400μA (10ksps)

2μA (shutdown)

- ♦ Internal 6MHz Full-Power Bandwidth Track/Hold

- ♦ Byte-Wide Parallel (8+2) Interface

- ♦ Small Footprint: 28-Pin QSOP (MAX1090) 24-Pin QSOP (MAX1092)

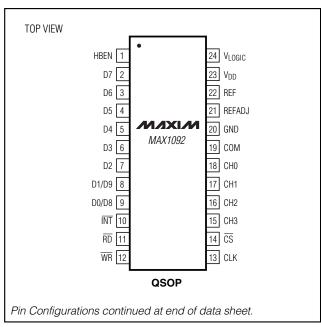

### Pin Configurations

Typical Operating Circuits appear at end of data sheet.

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to GND       | 0.3V to +6V                         |

|------------------------------|-------------------------------------|

| VLOGIC to GND                | 0.3V to +6V                         |

| CH0-CH7, COM to GND          | 0.3V to $(V_{DD} + 0.3V)$           |

| REF, REFADJ to GND           | 0.3V to (V <sub>DD</sub> + 0.3V)    |

|                              | 0.3V to +6V                         |

| Digital Outputs (D0-D9, INT) |                                     |

| to GND                       | 0.3V to (V <sub>LOGIC</sub> + 0.3V) |

| Continuous Power Dissipation (TA = + |                   |

|--------------------------------------|-------------------|

| 24-Pin QSOP (derate 9.5mW/°C a       | above +70°C)762mW |

| 28-Pin QSOP (derate 8.00mW/°C        | above +70°C)667mW |

| Operating Temperature Ranges         |                   |

| MAX1090_C/MAX1092_C                  | 0°C to +70°C      |

| MAX1090_E/MAX1092_E                  | 40°C to +85°C     |

| Storage Temperature Range            |                   |

| Lead Temperature (soldering, 10s)    | +300°C            |

|                                      |                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{LOGIC} = +5V \pm 10\%, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu F$  capacitor at REF pin,  $f_{CLK} = 7.6MHz$  (50% duty cycle),  $f_{CLK} = 7.6MHz$

| PARAMETER                                                | SYMBOL       | CONDITIONS                                                          | MIN       | TYP        | MAX      | UNITS  |

|----------------------------------------------------------|--------------|---------------------------------------------------------------------|-----------|------------|----------|--------|

| DC ACCURACY (Note 1)                                     | '            |                                                                     | 1         |            |          |        |

| Resolution                                               | RES          |                                                                     | 10        |            |          | Bits   |

| Deletive Assurance (Nets O)                              | INL          | MAX109_A                                                            |           |            | ±0.5     | LSB    |

| Relative Accuracy (Note 2)                               | IINL         | MAX109_B                                                            |           |            | ±1       | LOD    |

| Differential Nonlinearity                                | DNL          | No missing codes over temperature                                   |           |            | ±1       | LSB    |

| Offset Error                                             |              |                                                                     |           |            | ±2       | LSB    |

| Gain Error (Note 3)                                      |              |                                                                     |           |            | ±2       | LSB    |

| Gain Temperature Coefficient                             |              |                                                                     |           | ±2.0       |          | ppm/°C |

| Channel-to-Channel Offset<br>Matching                    |              |                                                                     |           | ±0.1       |          | LSB    |

| DYNAMIC SPECIFICATIONS (file                             | N(sine wave) | = $50$ kHz, $V_{IN}$ = $2.5$ Vp-p, $400$ ksps, external $f_{CLK}$ = | = 7.6MHz, | bipolar in | out mode | )      |

| Signal-to-Noise Plus Distortion                          | SINAD        |                                                                     |           | 60         |          | dB     |

| Total Harmonic Distortion (including 5th-order harmonic) | THD          |                                                                     |           | -72        |          | dB     |

| Spurious-Free Dynamic Range                              | SFDR         |                                                                     |           | 72         |          | dB     |

| Intermodulation Distortion                               | IMD          | $f_{\text{IN1}} = 49\text{kHz}$ , $f_{\text{IN2}} = 52\text{kHz}$   |           | 76         |          | dB     |

| Channel-to-Channel Crosstalk                             |              | $f_{IN} = 175kHz$ , $V_{IN} = 2.5Vp-p$ (Note 4)                     |           | -78        |          | dB     |

| Full-Linear Bandwidth                                    |              | SINAD > 56dB                                                        |           | 350        |          | kHz    |

| Full-Power Bandwidth                                     |              | -3dB rolloff                                                        |           | 6          |          | MHz    |

| CONVERSION RATE                                          | •            |                                                                     |           |            |          |        |

|                                                          |              | External clock mode                                                 | 2.1       |            |          |        |

| Conversion Time (Note 5)                                 | tconv        | External acquisition/internal clock mode                            | 2.5       | 3.0        | 3.5      | μs     |

|                                                          |              | Internal acquisition/internal clock mode                            | 3.2       | 3.6        | 4        |        |

| T/H Acquisition Time                                     | tACQ         |                                                                     |           |            | 400      | ns     |

| Aperture Delay                                           |              | External acquisition or external clock mode                         |           | 25         |          | ns     |

| Aperture Jitter                                          |              | External acquisition or external clock mode                         | <50       |            |          | ps     |

| Aporture viller                                          |              | Internal acquisition/internal clock mode                            |           | <200       |          | ρs     |

| External Clock Frequency                                 | fCLK         |                                                                     | 0.1       |            | 7.6      | MHz    |

| Duty Cycle                                               |              |                                                                     | 30        |            | 70       | %      |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{LOGIC} = +5V \pm 10\%, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu F$  capacitor at REF pin,  $f_{CLK} = 7.6MHz$  (50% duty cycle),  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                    | SYMBOL           | CONDITIONS                                                     | MIN                   | TYP   | MAX                       | UNITS  |

|--------------------------------------------------------------|------------------|----------------------------------------------------------------|-----------------------|-------|---------------------------|--------|

| ANALOG INPUTS                                                | 1                |                                                                |                       |       |                           |        |

| Analog Input Voltage Range,<br>Single Ended and Differential | V <sub>IN</sub>  | Unipolar, V <sub>COM</sub> = 0                                 | 0                     |       | V <sub>REF</sub>          | V      |

| (Note 6)                                                     | - 111            | Bipolar, V <sub>COM</sub> = V <sub>REF</sub> / 2               | -V <sub>REF</sub> /2  |       | +V <sub>REF</sub> /2      | ·      |

| Multiplexer Leakage Current                                  |                  | On/off-leakage current, V <sub>IN</sub> = 0 or V <sub>DD</sub> |                       | ±0.01 | ±1                        | μΑ     |

| Input Capacitance                                            | CIN              |                                                                |                       | 12    |                           | рF     |

| INTERNAL REFERENCE                                           | •                |                                                                |                       |       |                           |        |

| REF Output Voltage                                           |                  |                                                                | 2.49                  | 2.5   | 2.51                      | V      |

| REF Short-Circuit Current                                    |                  |                                                                |                       | 15    |                           | mA     |

| REF Temperature Coefficient                                  | TCREF            | $T_A = 0$ °C to +70°C                                          |                       | ±20   |                           | ppm/°C |

| REFADJ Input Range                                           |                  | For small adjustments                                          |                       | ±100  |                           | mV     |

| REFADJ High Threshold                                        |                  | To power down the internal reference                           | V <sub>DD</sub> - 1.0 |       |                           | V      |

| Load Regulation (Note 7)                                     |                  | 0 to 0.5mA output load                                         |                       | 0.2   | 0.5                       | mV/mA  |

| Capacitive Bypass at REFADJ                                  |                  |                                                                |                       | 0.01  | 1                         | μF     |

| Capacitive Bypass at REF                                     |                  |                                                                | 4.7                   |       | 10                        | μF     |

| EXTERNAL REFERENCE AT RE                                     | F                |                                                                |                       |       |                           |        |

| REF Input Voltage Range                                      | VREF             |                                                                | 1.0                   |       | V <sub>DD</sub> +<br>50mV | V      |

| Object of the second Occurrent                               |                  | V <sub>REF</sub> = 2.5V, f <sub>SAMPLE</sub> = 400ksps         |                       | 200   | 300                       | ^      |

| Shutdown REF Input Current                                   | I <sub>REF</sub> | Shutdown mode                                                  |                       |       | 2                         | μΑ     |

| DIGITAL INPUTS AND OUTPUT                                    | S                |                                                                | 1                     |       |                           |        |

| Innut Valtage Lligh                                          | 1/               | V <sub>LOGIC</sub> = 4.5V                                      | 4.0                   |       |                           | V      |

| Input Voltage High                                           | VIH              | V <sub>LOGIC</sub> = 2.7V                                      | 2.0                   |       |                           | V      |

| Input Voltage Low                                            | VIL              | V <sub>LOGIC</sub> = 4.5V or 2.7V                              |                       |       | 0.8                       | V      |

| Input Hysteresis                                             | VHYS             |                                                                |                       | 200   |                           | mV     |

| Input Leakage Current                                        | I <sub>IN</sub>  | V <sub>IN</sub> = 0 or V <sub>DD</sub>                         |                       | ±0.1  | ±1                        | μΑ     |

| Input Capacitance                                            | CIN              |                                                                |                       | 15    |                           | рF     |

| Output Voltage Low                                           | V <sub>OL</sub>  | I <sub>SINK</sub> = 1.6mA                                      |                       |       | 0.4                       | V      |

| Output Voltage High                                          | Voh              | ISOURCE = 1mA                                                  | VLOGIC - (            | 0.5   |                           | V      |

| Three-State Leakage Current                                  | ILEAKAGE         | $\overline{\text{CS}} = V_{\text{DD}}$                         |                       | ±0.1  | ±1                        | μΑ     |

| Three-State Output Capacitance                               | Cout             | CS = V <sub>DD</sub>                                           |                       | 15    |                           | pF     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = V_{LOGIC} = +5V \pm 10\%, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu F$  capacitor at REF pin,  $f_{CLK} = 7.6MHz$  (50% duty cycle),  $T_{A} = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .)

| PARAMETER               | SYMBOL          | CONDITIONS                                                                  |                    | MIN | TYP  | MAX                   | UNITS |  |

|-------------------------|-----------------|-----------------------------------------------------------------------------|--------------------|-----|------|-----------------------|-------|--|

| POWER REQUIREMENTS      | '               |                                                                             |                    | 1   |      |                       |       |  |

| Analog Supply Voltage   | V <sub>DD</sub> |                                                                             |                    | 4.5 |      | 5.5                   | V     |  |

| Digital Supply Voltage  | VLOGIC          |                                                                             |                    | 2.7 |      | V <sub>DD</sub> + 0.3 | V     |  |

|                         |                 | Operating mode, fsample = 400ksps   Internal reference   External reference | Internal reference |     | 2.6  | 2.9                   |       |  |

|                         |                 |                                                                             |                    | 2.2 | 2.5  | m A                   |       |  |

| Positive Supply Current | I <sub>DD</sub> | Cton dlay mad da                                                            | Internal reference |     | 1.0  | 1.2                   | - mA  |  |

|                         |                 | Standby mode                                                                | External reference |     | 0.5  | 0.8                   |       |  |

|                         |                 | Shutdown mode                                                               |                    |     | 2    | 10                    | μΑ    |  |

| VLOGIC Current          | luggio          | C: 00mF                                                                     | fsample = 400ksps  |     |      | 200                   | μA    |  |

| VLOGIC Current          | ILOGIC          | $C_L = 20pF$                                                                | Nonconverting      |     | 2    | 10                    | μΑ    |  |

| Power-Supply Rejection  | PSR             | V <sub>DD</sub> = 5V ±10%, full-scale input                                 |                    |     | ±0.3 | ±0.7                  | mV    |  |

#### **TIMING CHARACTERISTICS**

$(V_{DD} = V_{LOGIC} = +5V \pm 10\%, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu F$  capacitor at REF pin, f<sub>CLK</sub> = 7.6MHz (50% duty cycle), T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                       | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------------|-----------------|------------|-----|-----|-----|-------|

| CLK Period                      | tcp             |            | 132 |     |     | ns    |

| CLK Pulse Width High            | tcH             |            | 40  |     |     | ns    |

| CLK Pulse Width Low             | t <sub>CL</sub> |            | 40  |     |     | ns    |

| Data Valid to WR Rise Time      | tDS             |            | 40  |     |     | ns    |

| WR Rise to Data Valid Hold Time | t <sub>DH</sub> |            | 0   |     |     | ns    |

| WR to CLK Fall Setup Time       | tcws            |            | 40  |     |     | ns    |

| CLK Fall to WR Hold Time        | tcwH            |            | 40  |     |     | ns    |

| CS to CLK or WR Setup Time      | tcsws           |            | 60  |     |     | ns    |

| CLK or WR to CS Hold Time       | tcswh           |            | 0   |     |     | ns    |

| CS Pulse Width                  | tcs             |            | 100 |     |     | ns    |

| WR Pulse Width (Note 8)         | twR             |            | 60  |     |     | ns    |

### **TIMING CHARACTERISTICS (continued)**

$(V_{DD} = V_{LOGIC} = +5V \pm 10\%, COM = GND, REFADJ = V_{DD}, V_{REF} = +2.5V, 4.7\mu F$  capacitor at REF pin,  $f_{CLK} = 7.6MHz$  (50% duty cycle),  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                      | SYMBOL            | CONDITIONS                         | MIN | TYP | MAX | UNITS |

|--------------------------------|-------------------|------------------------------------|-----|-----|-----|-------|

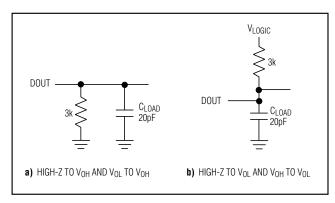

| CS Rise to Output Disable      | tTC               | C <sub>LOAD</sub> = 20pF, Figure 1 | 10  |     | 60  | ns    |

| RD Rise to Output Disable      | t <sub>TR</sub>   | C <sub>LOAD</sub> = 20pF, Figure 1 | 10  |     | 40  | ns    |

| RD Fall to Output Data Valid   | t <sub>DO</sub>   | C <sub>LOAD</sub> = 20pF, Figure 1 | 10  |     | 50  | ns    |

| HBEN Rise to Output Data Valid | t <sub>DO1</sub>  | C <sub>LOAD</sub> = 20pF, Figure 1 | 10  |     | 50  | ns    |

| HBEN Fall to Output Data Valid | t <sub>DO1</sub>  | C <sub>LOAD</sub> = 20pF, Figure 1 | 10  |     | 80  | ns    |

| RD Fall to INT High Delay      | t <sub>INT1</sub> | C <sub>LOAD</sub> = 20pF, Figure 1 |     |     | 50  | ns    |

| CS Fall to Output Data Valid   | t <sub>DO2</sub>  | C <sub>LOAD</sub> = 20pF, Figure 1 |     |     | 100 | ns    |

- **Note 1:** Tested at  $V_{DD} = +5V$ , COM = GND, unipolar single-ended input mode.

- **Note 2:** Relative accuracy is the deviation of the analog value at any code from its theoretical value after offset and gain errors have been removed.

- Note 3: Offset nulled.

- Note 4: On channel is grounded; sine wave applied to off channels.

- Note 5: Conversion time is defined as the number of clock cycles times the clock period; clock has 50% duty cycle.

- Note 6: Input voltage range referenced to negative input. The absolute range for the analog inputs is from GND to VDD.

- Note 7: External load should not change during conversion for specified accuracy.

- Note 8: When bit 5 is set low for internal acquisition, WR must not return low until after the first falling clock edge of the conversion.

Figure 1. Load Circuits for Enable/Disable Times

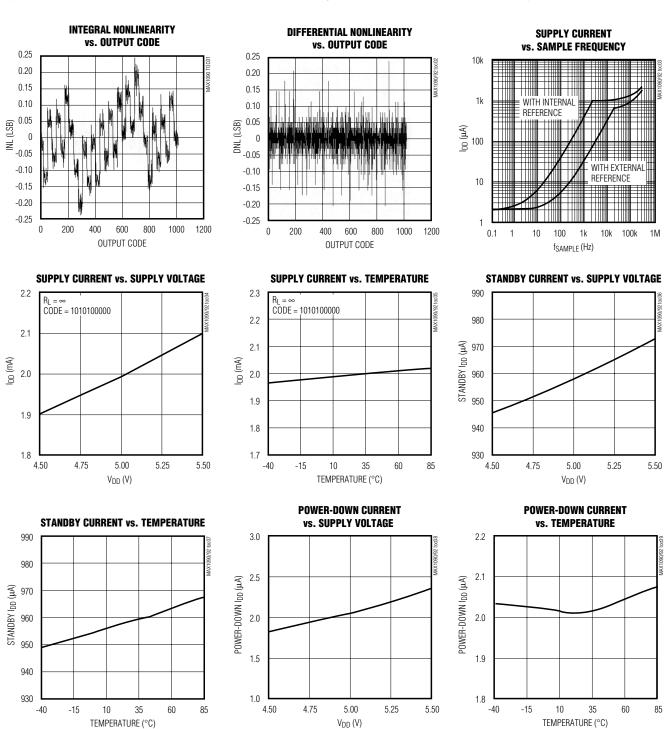

### Typical Operating Characteristics

(VDD = VLOGIC = +5V, VREF = +2.500V, fCLK = 7.6MHz, CL = 20pF, TA = +25°C, unless otherwise noted.)

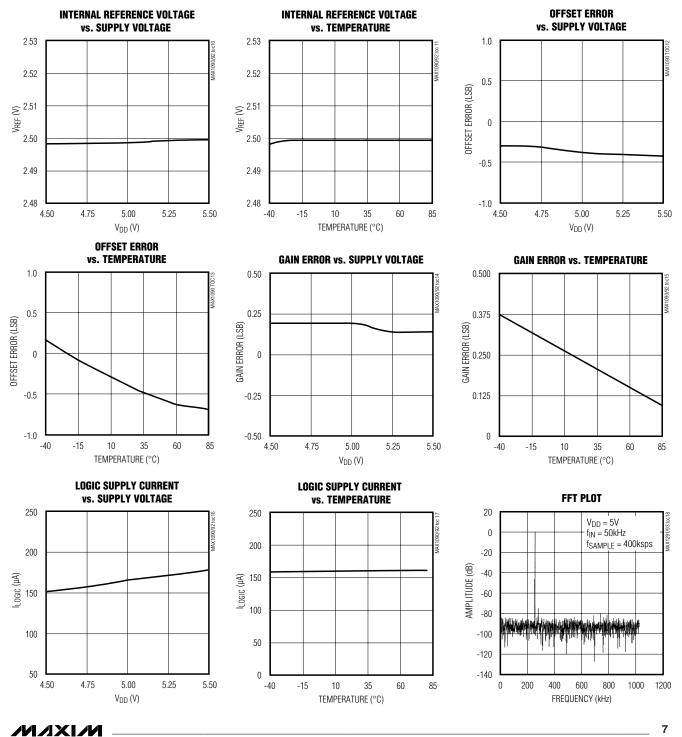

### **Typical Operating Characteristics (continued)**

(VDD = VLOGIC = +5V, VREF = +2.500V, fCLK = 7.6MHz, CL = 20pF, TA = +25°C, unless otherwise noted.)

### Pin Description

| PIN     |         |                 |                                                                                                                                                                                                                                                                                                                                                   |

|---------|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1090 | MAX1092 | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                          |

| 1       | 1       | HBEN            | High Byte Enable. Used to multiplex the 10-bit conversion result. 1: 2 MSBs are multiplexed on the data bus. 0: 8 LSBs are available on the data bus.                                                                                                                                                                                             |

| 2       | 2       | D7              | Three-State Digital I/O Line (D7)                                                                                                                                                                                                                                                                                                                 |

| 3       | 3       | D6              | Three-State Digital I/O Line (D6)                                                                                                                                                                                                                                                                                                                 |

| 4       | 4       | D5              | Three-State Digital I/O Line (D5)                                                                                                                                                                                                                                                                                                                 |

| 5       | 5       | D4              | Three-State Digital I/O Line (D4)                                                                                                                                                                                                                                                                                                                 |

| 6       | 6       | D3              | Three-State Digital I/O Line (D3)                                                                                                                                                                                                                                                                                                                 |

| 7       | 7       | D2              | Three-State Digital I/O Line (D2)                                                                                                                                                                                                                                                                                                                 |

| 8       | 8       | D1/D9           | Three-State Digital I/O Line (D1, HBEN = 0; D9, HBEN = 1)                                                                                                                                                                                                                                                                                         |

| 9       | 9       | D0/D8           | Three-State Digital I/O Line (D0, HBEN = 0; D8, HBEN = 1)                                                                                                                                                                                                                                                                                         |

| 10      | 10      | ĪNT             | INT goes low when the conversion is complete and the output data is ready.                                                                                                                                                                                                                                                                        |

| 11      | 11      | RD              | Active-Low Read Select. If $\overline{\text{CS}}$ is low, a falling edge on $\overline{\text{RD}}$ will enable the read operation on the data bus.                                                                                                                                                                                                |

| 12      | 12      | WR              | Active-Low Write Select. When $\overline{CS}$ is low in internal acquisition mode, a rising edge on $\overline{WR}$ latches in configuration data and starts an acquisition plus a conversion cycle. When $\overline{CS}$ is low in external acquisition mode, the first rising edge on $\overline{WR}$ ends acquisition and starts a conversion. |

| 13      | 13      | CLK             | Clock Input. In external clock mode, drive CLK with a TTL/CMOS-compatible clock. In internal clock mode, connect this pin to either V <sub>DD</sub> or GND.                                                                                                                                                                                       |

| 14      | 14      | CS              | Active-Low Chip Select. When $\overline{\text{CS}}$ is high, digital outputs ( $\overline{\text{INT}}$ , D7–D0) are high impedance.                                                                                                                                                                                                               |

| 15      | _       | CH7             | Analog Input Channel 7                                                                                                                                                                                                                                                                                                                            |

| 16      |         | CH6             | Analog Input Channel 6                                                                                                                                                                                                                                                                                                                            |

| 17      |         | CH5             | Analog Input Channel 5                                                                                                                                                                                                                                                                                                                            |

| 18      |         | CH4             | Analog Input Channel 4                                                                                                                                                                                                                                                                                                                            |

| 19      | 15      | CH3             | Analog Input Channel 3                                                                                                                                                                                                                                                                                                                            |

| 20      | 16      | CH2             | Analog Input Channel 2                                                                                                                                                                                                                                                                                                                            |

| 21      | 17      | CH1             | Analog Input Channel 1                                                                                                                                                                                                                                                                                                                            |

| 22      | 18      | CH0             | Analog Input Channel 0                                                                                                                                                                                                                                                                                                                            |

| 23      | 19      | COM             | Ground Reference for Analog Inputs. Sets zero-code voltage in single-ended mode and must be stable to ±0.5LSB during conversion.                                                                                                                                                                                                                  |

| 24      | 20      | GND             | Analog and Digital Ground                                                                                                                                                                                                                                                                                                                         |

| 25      | 21      | REFADJ          | Bandgap Reference Output/Bandgap Reference Buffer Input. Bypass to GND with a 0.01µF capacitor. When using an external reference, connect REFADJ to V <sub>DD</sub> to disable the internal bandgap reference.                                                                                                                                    |

| 26      | 22      | REF             | Bandgap Reference Buffer Output/External Reference Input. Add a 4.7µF capacitor to GND when using the internal reference.                                                                                                                                                                                                                         |

| 27      | 23      | V <sub>DD</sub> | Analog +5V Power Supply. Bypass with a 0.1µF capacitor to GND.                                                                                                                                                                                                                                                                                    |

| 28      | 24      | VLOGIC          | Digital Power Supply. $V_{LOGIC}$ powers the digital outputs of the data converter and can range from +2.7V to $V_{DD}$ + 300mV.                                                                                                                                                                                                                  |

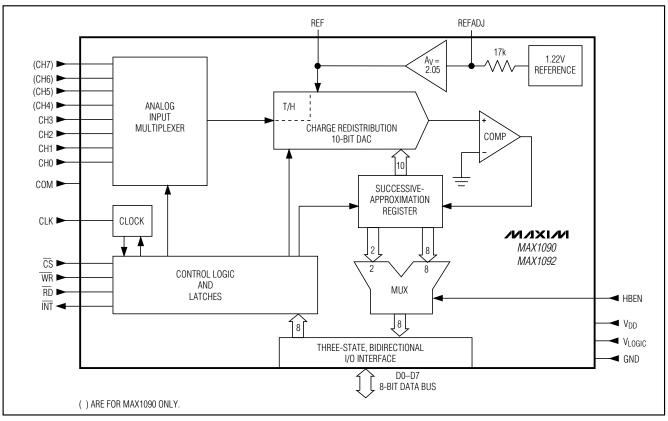

Figure 2. Simplified Functional Diagram of 8-/4-Channel MAX1090/MAX1092

### Detailed Description

#### **Converter Operation**

The MAX1090/MAX1092 ADCs use a successive-approximation (SAR) conversion technique and an input track-and-hold (T/H) stage to convert an analog input signal to a 10-bit digital output. Their parallel 8+2 output format provides an easy interface to standard microprocessors (µPs). Figure 2 shows the simplified internal architecture of the MAX1090/MAX1092.

#### Single-Ended and Pseudo-Differential Operation

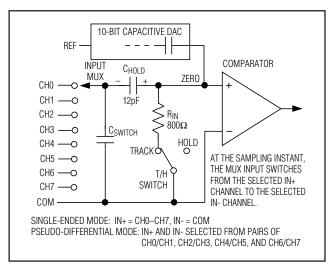

The sampling architecture of the ADC's analog comparator is illustrated in the equivalent input circuits in Figures 3a and 3b. In single-ended mode, IN+ is internally switched to channels CH0-CH7 for the MAX1090 (Figure 3a) and to CH0-CH3 for the MAX1092 (Figure 3b), while IN- is switched to COM (Table 3). In differential mode, IN+ and IN- are selected from analog input pairs (Table 4).

In differential mode, IN- and IN+ are internally switched to either of the analog inputs. This configuration is pseudo-differential in that only the signal at IN+ is sampled. The return side (IN-) must remain stable within  $\pm 0.5 LSB$  ( $\pm 0.1 LSB$  for best performance) with respect to GND during a conversion. To accomplish this, connect a  $0.1 \mu F$  capacitor from IN- (the selected input) to GND.

During the acquisition interval, the channel selected as the positive input (IN+) charges capacitor  $C_{HOLD}$ . At the end of the acquisition interval, the T/H switch opens, retaining the charge on  $C_{HOLD}$  as a sample of the signal at IN+.

The conversion interval begins with the input multiplexer switching CHOLD from the positive input (IN+) to the negative input (IN-). This unbalances node ZERO at the comparator's positive input. The capacitive digital-to-analog converter (DAC) adjusts during the remainder of the conversion cycle to restore node ZERO to 0V within the limits of 10-bit resolution. This action is equivalent to transferring a 12pF [(V<sub>IN+</sub>) - (V<sub>IN-</sub>)] charge from C<sub>HOLD</sub> to the binary-weighted capacitive DAC, which in turn forms a digital representation of the analog input signal.

Figure 3a. MAX1090 Simplified Input Structure

#### 10-BIT CAPACITIVE DAC REF COMPARATOR INPUT $\mathsf{C}_{\mathsf{HOLD}}$ ZER0 CH<sub>0</sub> 12pF CH1 -2008 C<sub>SWITCH</sub> CH2 -HOLD TRACKO AT THE SAMPLING INSTANT, CH3 ----O THE MUX INPUT SWITCHES T/H FROM THE SELECTED IN+ **SWITCH** CHANNEL TO THE SELECTED COM IN- CHANNEL. SINGLE-ENDED MODE: IN+ = CH0-CH3, IN- = COM PSEUDO-DIFFERENTIAL MODE: IN+ AND IN- SELECTED FROM PAIRS OF CH0/CH1 AND CH2/CH3

Figure 3b. MAX1092 Simplified Input Structure

#### **Analog Input Protection**

Internal protection diodes, which clamp the analog input to  $V_{DD}$  and GND, allow each input channel to swing within (GND - 300mV) to ( $V_{DD}$  + 300mV) without damage. However, for accurate conversions near full scale, neither input should exceed ( $V_{DD}$  + 50mV) or be less than (GND - 50mV).

If an off-channel analog input voltage exceeds the supplies by more than 50mV, limit the forward-bias input current to 4mA.

#### Track/Hold

The MAX1090/MAX1092 T/H stage enters its tracking mode on the rising edge of  $\overline{\text{WR}}$ . In external acquisition mode, the part enters its hold mode on the next rising edge of  $\overline{\text{WR}}$ . In internal acquisition mode, the part enters its hold mode on the fourth falling edge of the clock after writing the control byte. Note that in internal clock mode, this is approximately 1 $\mu$ s after writing the control byte.

In single-ended operation, IN- is connected to COM and the converter samples the positive (+) input. In pseudo-differential operation, IN- connects to the negative input (-) and the difference of I(IN+) - (IN-)I is sampled. At the beginning of the next conversion, the positive input connects back to IN+ and CHOLD charges to the input signal.

The time required for the T/H stage to acquire an input signal depends on how quickly its input capacitance is charged. If the input signal's source impedance is high, the acquisition time lengthens and more time must be

allowed between conversions. The acquisition time, tACQ, is the maximum time the device takes to acquire the signal and is also the minimum time required for the signal to be acquired. Calculate this with the following equation:

$$t_{ACQ} = 7 (R_S + R_{IN}) C_{IN}$$

where Rs is the source impedance of the input signal, RlN (800 $\Omega$ ) is the input resistance, and ClN (12pF) is the input capacitance of the ADC. Source impedances below 3k $\Omega$  have no significant impact on the MAX1090/MAX1092's AC performance.

Higher source impedances can be used if a  $0.01\mu F$  capacitor is connected to the individual analog inputs. Along with the input impedance, this capacitor forms an RC filter, limiting the ADC's signal bandwidth.

#### Input Bandwidth

The MAX1090/MAX1092 T/H stage offers a 350kHz full-linear and a 6MHz full-power bandwidth. These features make it possible to digitize high-speed transients and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques. To avoid aliasing high-frequency signals into the frequency band of interest, anti-alias filtering is recommended.

#### Starting a Conversion

Initiate a conversion by writing a control byte that selects the multiplexer channel and configures the MAX1090/MAX1092 for either unipolar or bipolar operation. A write pulse  $(\overline{WR} + \overline{CS})$  can either start an acqui-

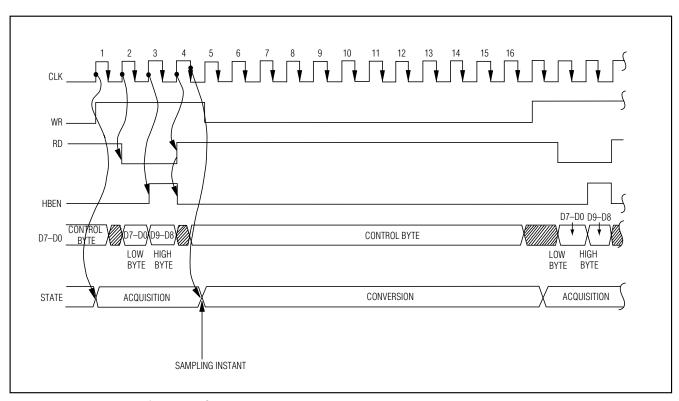

sition interval or initiate a combined acquisition plus conversion. The sampling interval occurs at the end of the acquisition interval. The ACQMOD (acquisition mode) bit in the input control byte (Table 1) offers two options for acquiring the signal: an internal and an external acquisition. The conversion period lasts for 13 clock cycles in either the internal or external clock or acquisition mode. Writing a new control byte during a conversion cycle will abort the conversion and start a new acquisition interval.

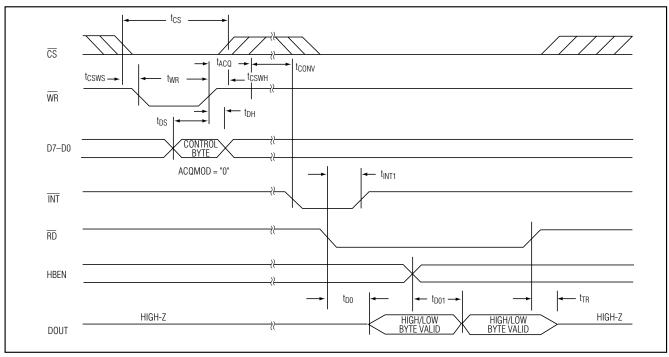

#### Internal Acquisition

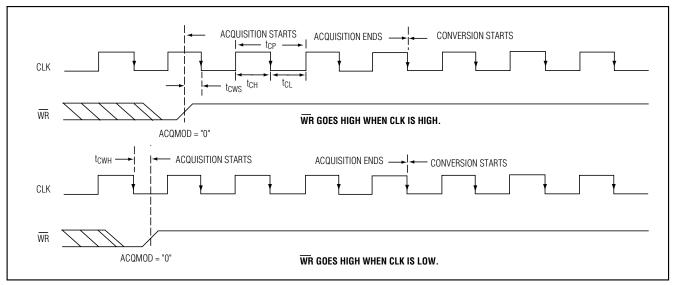

Select internal acquisition by writing the control byte with the ACQMOD bit cleared (ACQMOD = 0). This causes the write pulse to initiate an acquisition interval whose duration is internally timed. Conversion starts when this acquisition interval (three external clock cycles or approximately 1µs in internal clock mode) ends (Figure 4). When the internal acquisition is combined with the internal clock, the aperture jitter can be as high as 200ps. Internal clock users wishing to achieve the 50ps jitter specification should always use external acquisition mode.

#### **External Acquisition**

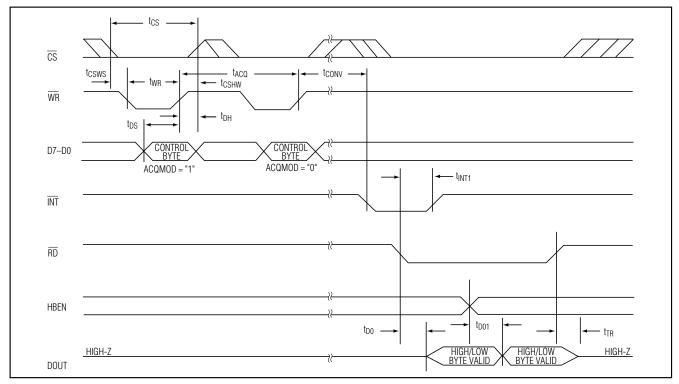

Use external acquisition mode for precise control of the sampling aperture and/or dependent control of acquisition and conversion times. The user controls acquisition

and start-of-conversion with two separate write pulses. The first pulse, written with ACQMOD = 1, starts an acquisition interval of indeterminate length. The second write pulse, written with ACQMOD = 0 (all other bits in the control byte are unchanged), terminates acquisition and starts conversion on  $\overline{WR}$  rising edge (Figure 5).

The address bits for the input multiplexer must have the same values on the first and second write pulses. Power-down mode bits (PD0, PD1) can assume new values on the second write pulse (see the *Power-Down Modes* section). Changing other bits in the control byte will corrupt the conversion.

#### Reading a Conversion

A standard interrupt signal,  $\overline{\text{INT}}$ , is provided to allow the MAX1090/MAX1092 to flag the  $\mu\text{P}$  when the conversion has ended and a valid result is available.  $\overline{\text{INT}}$  goes low when the conversion is complete and the output data is ready (Figures 4 and 5).  $\overline{\text{INT}}$  returns high on the first read cycle or if a new control byte is written.

#### **Selecting Clock Mode**

The MAX1090/MAX1092 operate with an internal or external clock. Control bits D6 and D7 select either internal or external clock mode. The part retains the last-requested clock mode if a power-down mode is selected in the current input word. For both internal and external clock modes, internal or external acquisition

**Table 1. Control Byte Functional Description**

| BIT        | NAME       |                   | FUNCTION                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                   |  |  |  |  |  |

|------------|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|            |            | PD1 an            | PD1 and PD0 select the various clock and power-down modes.                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |  |  |  |  |  |

|            |            | 0                 | Full Power-Down Mode. Clock mode is unaffected.                                                                                                                                                                                                                                     |                                                                                                                                                                                                                   |  |  |  |  |  |

| D7, D6     | PD1, PD0   | 0                 | 1                                                                                                                                                                                                                                                                                   | Standby Power-Down Mode. Clock mode is unaffected.                                                                                                                                                                |  |  |  |  |  |

|            |            | 1                 | 0                                                                                                                                                                                                                                                                                   | Normal Operation Mode. Internal clock mode is selected.                                                                                                                                                           |  |  |  |  |  |

|            |            | 1                 | 1                                                                                                                                                                                                                                                                                   | Normal Operation Mode. External clock mode is selected.                                                                                                                                                           |  |  |  |  |  |

| D5         | ACQMOD     |                   | ACQMOD = 0: Internal Acquisition Mode ACQMOD = 1: External Acquisition Mode                                                                                                                                                                                                         |                                                                                                                                                                                                                   |  |  |  |  |  |

| D4         | SGL/DIF    | SGL/D<br>In sing  | IF = 1: S<br>le-ende                                                                                                                                                                                                                                                                | Pseudo-Differential Analog Input Mode<br>Single-Ended Analog Input Mode<br>d mode, input signals are referred to COM. In pseudo-differential mode, the voltage<br>ween two channels is measured (Tables 2 and 3). |  |  |  |  |  |

| D3         | UNI/BIP    | UNI/BI<br>In unip | UNI/ $\overline{\text{BIP}}$ = 0: Bipolar Mode<br>UNI/ $\overline{\text{BIP}}$ = 1: Unipolar Mode<br>In unipolar mode, an analog input signal from 0 to V <sub>REF</sub> can be converted; in bipolar mode, the signal can range from -V <sub>REF</sub> /2 to +V <sub>REF</sub> /2. |                                                                                                                                                                                                                   |  |  |  |  |  |

| D2, D1, D0 | A2, A1, A0 |                   | Address bits A2–A0 select which of the 8/4 (MAX1090/MAX1092) channels is to be converted (Tables 3 and 4).                                                                                                                                                                          |                                                                                                                                                                                                                   |  |  |  |  |  |

Figure 4. Conversion Timing Using Internal Acquisition Mode

Figure 5. Conversion Timing Using External Acquisition Mode

can be used. At power-up, the MAX1090/MAX1092 enter the default external clock mode.

#### Internal Clock Mode

Select internal clock mode to release the  $\mu P$  from the burden of running the SAR conversion clock. To select this mode, bit D7 of the control byte must be set to 1 and bit D6 must be set to 0; the internal clock frequency is then selected, resulting in a 3.6 $\mu$ s conversion time. When using the internal clock mode, connect the

CLK pin either high or low to prevent the pin from floating.

#### External Clock Mode

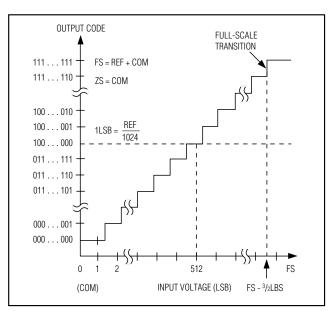

To select the external clock mode, bits D6 and D7 of the control byte must be set to one. Figure 6 shows the clock and  $\overline{\text{WR}}$  timing relationship for internal (Figure 6a) and external (Figure 6b) acquisition modes with an external clock. Proper operation requires a 100kHz to 7.6MHz clock frequency with 30% to 70% duty cycle. Operating the MAX1090/MAX1092 with clock frequency

Figure 6a. External Clock and WR Timing (Internal Acquisition Mode)

Figure 6b. External Clock and WR Timing (External Acquisition Mode)

cies lower than 100kHz is not recommended because it will cause a voltage droop across the hold capacitor in the T/H stage that will result in degraded performance.

#### **Digital Interface**

Input (control byte) and output data are multiplexed on a three-state parallel interface. This parallel interface (I/O) can easily be interfaced with standard  $\mu Ps$ . The signals  $\overline{CS}$ , WR, and  $\overline{RD}$  control the write and read operations.  $\overline{CS}$  represents the chip-select signal, which enables a  $\mu P$  to address the MAX1090/MAX1092 as an I/O port. When high,  $\overline{CS}$  disables the CLK,  $\overline{WR}$ , and  $\overline{RD}$  inputs and forces the interface into a high-impedance (high-Z) state.

#### Input Format

The control byte is latched into the device on pins D7–D0 during a write command. Table 2 shows the control byte format.

#### **Output Format**

The output format for the MAX1090/MAX1092 is binary in unipolar mode and two's complement in bipolar mode. When reading the output data,  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  must be low. When HBEN = 0, the lower 8 bits are read. With HBEN = 1, the upper 2 bits are available and the output data bits D7–D2 are set either low in unipolar mode or to the value of the MSB in bipolar mode (Table 5).

Table 2. Control Byte Format

| D7 (MSB) | D6  | D5     | D4      | D3      | D2 | D1 | D0 (LSB) |

|----------|-----|--------|---------|---------|----|----|----------|

| PD1      | PD0 | ACQMOD | SGL/DIF | UNI/BIP | A2 | A1 | A0       |

Table 3. Channel Selection for Single-Ended Operation (SGL/DIF = 1)

| A2 | <b>A</b> 1 | A0 | CH0 | CH1 | CH2 | СНЗ | CH4* | CH5* | CH6* | CH7* | СОМ |

|----|------------|----|-----|-----|-----|-----|------|------|------|------|-----|

| 0  | 0          | 0  | +   |     |     |     |      |      |      |      | -   |

| 0  | 0          | 1  |     | +   |     |     |      |      |      |      | -   |

| 0  | 1          | 0  |     |     | +   |     |      |      |      |      | -   |

| 0  | 1          | 1  |     |     |     | +   |      |      |      |      | -   |

| 1  | 0          | 0  |     |     |     |     | +    |      |      |      | -   |

| 1  | 0          | 1  |     |     |     |     |      | +    |      |      | -   |

| 1  | 1          | 0  |     |     |     |     |      |      | +    |      | -   |

| 1  | 1          | 1  |     |     |     |     |      |      |      | +    | -   |

<sup>\*</sup>Channels CH4-CH7 apply to MAX1090 only.

Table 4. Channel Selection for Pseudo-Differential Operation (SGL/DIF = 0)

| A2 | A1 | A0 | CH0 | CH1 | CH2 | СНЗ | CH4* | CH5* | CH6* | CH7* |

|----|----|----|-----|-----|-----|-----|------|------|------|------|

| 0  | 0  | 0  | +   | -   |     |     |      |      |      |      |

| 0  | 0  | 1  | -   | +   |     |     |      |      |      |      |

| 0  | 1  | 0  |     |     | +   | -   |      |      |      |      |

| 0  | 1  | 1  |     |     | -   | +   |      |      |      |      |

| 1  | 0  | 0  |     |     |     |     | +    | -    |      |      |

| 1  | 0  | 1  |     |     |     |     | -    | +    |      |      |

| 1  | 1  | 0  |     |     |     |     |      |      | +    | -    |

| 1  | 1  | 1  |     |     |     |     |      |      | -    | +    |

<sup>\*</sup>Channels CH4-CH7 apply to MAX1090 only.

### Table 5. Data-Bus Output (8+2 Parallel Interface)

| PIN | HBEN = 0    | HBEN = 1                 |                           |  |  |  |

|-----|-------------|--------------------------|---------------------------|--|--|--|

| D0  | Bit 0 (LSB) | Bit 8                    |                           |  |  |  |

| D1  | Bit 1       | Bit 9 (MSB)              |                           |  |  |  |

|     |             | BIPOLAR<br>(UNI/BIP = 0) | UNIPOLAR<br>(UNI/BIP = 1) |  |  |  |

| D2  | Bit 2       | Bit 9                    | 0                         |  |  |  |

| D3  | Bit 3       | Bit 9                    | 0                         |  |  |  |

| D4  | Bit 4       | Bit 9                    | 0                         |  |  |  |

| D5  | Bit 5       | Bit 9                    | 0                         |  |  |  |

| D6  | Bit 6       | Bit 9                    | 0                         |  |  |  |

| D7  | Bit 7       | Bit 9                    | 0                         |  |  |  |

### Applications Information

#### **Power-On Reset**

When power is first applied, internal power-on reset circuitry activates the MAX1090/MAX1092 in external clock mode and sets INT high. After the power supplies stabilize, the internal reset time is 10µs, and no conversions should be attempted during this phase. When using the internal reference, 500µs are required for VREF to stabilize.

#### Internal and External Reference

The MAX1090/MAX1092 can be used with an internal or external reference voltage. An external reference can be connected directly to REF or REFADJ.

An internal buffer is designed to provide +2.5V at REF for both devices. The internally trimmed +1.22V reference is buffered with a +2.05V/V gain.

#### Internal Reference

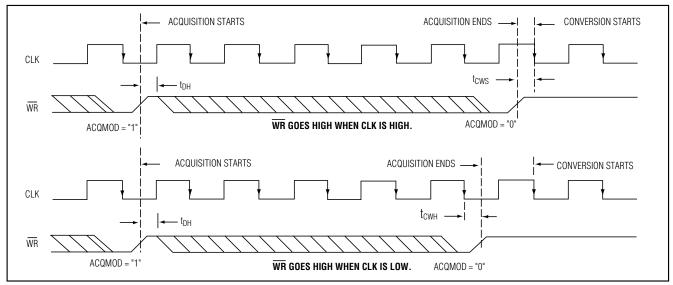

The full-scale range with the internal reference is  $\pm 2.5V$  with unipolar inputs and  $\pm 1.25V$  with bipolar inputs. The internal reference buffer allows for small adjustments ( $\pm 100$ mV) in the reference voltage (Figure 7).

**Note:** The reference buffer must be compensated with an external capacitor (4.7 $\mu$ F min) connected between REF and GND to reduce reference noise and switching spikes from the ADC. To further minimize reference noise, connect a 0.01 $\mu$ F capacitor between REFADJ and GND.

#### External Reference

With the MAX1090/MAX1092, an external reference can be placed at either the input (REFADJ) or the output (REF) of the internal reference-buffer amplifier.

Figure 7. Reference Voltage Adjustment with External Potentiometer

Using the REFADJ input makes buffering the external reference unnecessary. The REFADJ input impedance is typically  $17k\Omega$ .

When applying an external reference to REF, disable the internal reference buffer by connecting REFADJ to  $V_{DD}$ . The DC input resistance at REF is  $25k\Omega$ . Therefore, an external reference at REF must deliver up to  $200\mu A$  DC load current during a conversion and have an output impedance less than  $10\Omega$ . If the reference has higher output impedance or is noisy, bypass it close to the REF pin with a  $4.7\mu F$  capacitor.

#### **Power-Down Modes**

To save power, place the converter in a low-current shutdown state between conversions. Select standby mode or shutdown mode through bits D6 and D7 of the control byte (Tables 1 and 2). In both software power-down modes, the parallel interface remains active, but the ADC does not convert.

#### Standby Mode

While in standby mode, the supply current is 1mA (typ). The part will power up on the next rising edge on  $\overline{WR}$  and is ready to perform conversions. This quick turn-on time allows the user to realize significantly reduced power consumption for conversion rates below 400ksps.

#### Shutdown Mode

Shutdown mode turns off all chip functions that draw quiescent current, reducing the typical supply current to  $2\mu A$  immediately after the current conversion is completed. A rising edge on  $\overline{WR}$  causes the MAX1090/MAX1092 to exit shutdown mode and return to normal operation. To achieve full 10-bit accuracy with a 4.7 $\mu$ F reference bypass capacitor, 500 $\mu$ s is required after power-up. Waiting this 500 $\mu$ s in standby mode instead of in full-power mode can reduce power consumption by a factor of 3 or more. When using an external reference,

only 50µs are required after power-up. Enter standby mode by performing a dummy conversion with the control byte specifying standby mode.

**Note:** Bypass capacitors larger than 4.7µF between REF and GND will result in longer power-up delays.

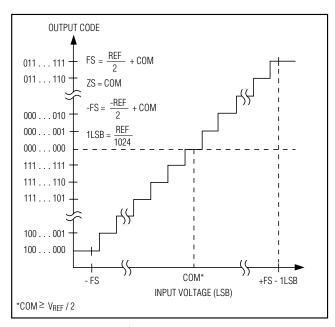

#### **Transfer Function**

Table 6 shows the full-scale voltage ranges for unipolar and bipolar modes.

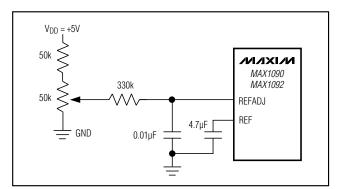

Figure 8 depicts the nominal, unipolar input/output (I/O) transfer function, and Figure 9 shows the bipolar I/O transfer function. Code transitions occur halfway between successive-integer LSB values. Output coding is binary, with 1LSB = V<sub>REF</sub> / 1024.

#### Maximum Sampling Rate/ Achieving 475ksps

When running at the maximum clock frequency of 7.6MHz, the specified 400ksps throughput is achieved by completing a conversion every 19 clock cycles: 1 write cycle, 3 acquisition cycles, 13 conversion cycles, and 2 read cycles. This assumes that the results of the last conversion are read before the next control byte is written. It's possible to achieve higher throughputs (Figure 10), up to 475ksps, by first writing a control word to begin the acquisition cycle of the next conversion, then reading the results of the previous conversion from the bus. This technique allows a conversion to be completed every 16 clock cycles. Note that switching the data bus during acquisition or conversion can cause additional supply noise that may make it difficult to achieve true 10-bit performance.

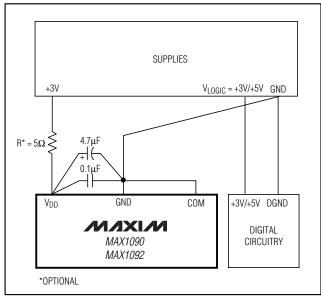

#### Layout, Grounding, and Bypassing

For best performance, use printed circuit boards. Wirewrap configurations are not recommended since the layout should ensure proper separation of analog and digital traces. Do not run analog and digital lines parallel to each other, and do not lay out digital signal paths underneath the ADC package. Use separate analog and digital PC board ground sections with only one star point (Figure 11) connecting the two ground systems (analog and digital). For lowest noise operation, ensure the ground return to the star ground's power supply is low impedance and as short as possible. Route digital signals far away from sensitive analog and reference inputs.

Figure 8. Unipolar Transfer Function

Figure 9. Bipolar Transfer Function

### Table 6. Full Scale and Zero Scale for Unipolar and Bipolar Operation

| UNIPOLA    | AR MODE                | BIPOLAR MODE        |                            |  |  |

|------------|------------------------|---------------------|----------------------------|--|--|

| Full Scale | V <sub>REF</sub> + COM | Positive Full Scale | V <sub>REF</sub> /2 + COM  |  |  |

| Zero Scale | COM                    | Zero Scale          | COM                        |  |  |

| _          | _                      | Negative Full Scale | -V <sub>REF</sub> /2 + COM |  |  |

High-frequency noise in the power supply (V<sub>DD</sub>) could influence the proper operation of the ADC's fast comparator. Bypass V<sub>DD</sub> to the star ground with a network of two parallel capacitors, 0.1µF and 4.7µF, located as close as possible to the MAX1090/MAX1092 power-supply pin. Minimize capacitor lead length for best supply-noise rejection, and add an attenuation resistor (5 $\Omega$ ) if the power supply is extremely noisy.

#### **Definitions**

#### **Integral Nonlinearity**

Integral nonlinearity (INL) is the deviation of the values on an actual transfer function from a straight line. This straight line can be either a best-straight-line fit or a line drawn between the end points of the transfer function, once offset and gain errors have been nullified. The MAX1090/MAX1092's INL is measured using the endpoint method.

#### **Differential Nonlinearity**

Differential nonlinearity (DNL) is the difference between an actual step width and the ideal value of 1LSB. A DNL error specification of less than 1LSB guarantees no missing codes and a monotonic transfer function.

#### **Aperture Jitter**

Aperture jitter (t<sub>A</sub>J) is the sample-to-sample variation in the time between the samples.

#### **Aperture Delay**

Aperture delay (tAD) is the time between the rising edge of the sampling clock and the instant when an actual sample is taken.

Figure 10. Timing Diagram for Fastest Conversion

Figure 11. Power-Supply and Grounding Connections

#### Signal-to-Noise Ratio

For a waveform perfectly reconstructed from digital samples, signal-to-noise ratio (SNR) is the ratio of full-scale analog input (RMS value) to the RMS quantization error (residual error). The ideal theoretical minimum analog-to-digital noise is caused by quantization error only and results directly from the ADC's resolution (N bits):

$$SNR = (6.02 \cdot N + 1.76)dB$$

In reality, there are other noise sources besides quantization noise, including thermal noise, reference noise, clock jitter, etc. Therefore, SNR is computed by taking the ratio of the RMS signal to the RMS noise, which includes all spectral components minus the fundamental, the first five harmonics, and the DC offset.

#### Signal-to-Noise Plus Distortion

Signal-to-noise plus distortion (SINAD) is the ratio of the fundamental input frequency's RMS amplitude to RMS equivalent of all other ADC output signals.

SINAD (dB) = 20 · log (Signal RMS / Noise RMS)

#### **Effective Number of Bits**

Effective number of bits (ENOB) indicates the global accuracy of an ADC at a specific input frequency and sampling rate. An ideal ADC's error consists of quantization noise only. With an input range equal to the ADC's full-scale range, calculate the ENOB as follows:

#### **Total Harmonic Distortion**

Total harmonic distortion (THD) is the ratio of the RMS sum of the input signal's first five harmonics to the fundamental itself. This is expressed as:

THD = 20 ·

$$\log \left( \sqrt{\left( V_2^2 + V_3^2 + V_4^2 + V_5^2 \right)} / V_1 \right)$$

where  $V_1$  is the fundamental amplitude, and  $V_2$  through  $V_5$  are the amplitudes of the 2nd- through 5th-order harmonics.

#### **Spurious-Free Dynamic Range**

Spurious-free dynamic range (SFDR) is the ratio of RMS amplitude of the fundamental (maximum signal component) to the RMS value of the next-largest distortion component.

**Chip Information**

**TRANSISTOR COUNT: 5781**

### **Typical Operating Circuits**

### Pin Configurations (continued)

### \_Ordering Information (continued)

| PART        | TEMP. RANGE    | PIN-PACKAGE | INL<br>(LSB) |

|-------------|----------------|-------------|--------------|

| MAX1092ACEG | 0°C to +70°C   | 24 QSOP     | ±0.5         |

| MAX1092BCEG | 0°C to +70°C   | 24 QSOP     | ±1           |

| MAX1092AEEG | -40°C to +85°C | 24 QSOP     | ±0.5         |

| MAX1092BEEG | -40°C to +85°C | 24 QSOP     | ±1           |

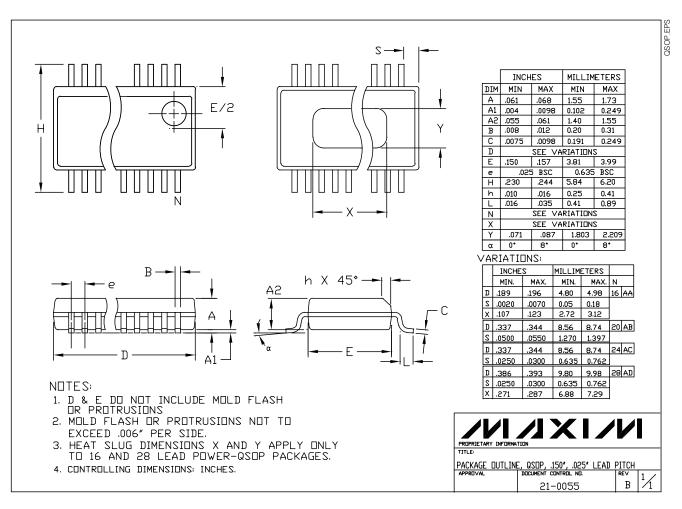

### **Package Information**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.