##

## 2.125Gbps/1.063Gbps, 3.3V Fibre Channel Repeaters

## **General Description**

The MAX3770 is a 2.125Gbps Fibre Channel repeater IC. The MAX3771 provides a pin-compatible solution for 1.063Gbps Fibre Channel. Both devices are optimized for use in Fibre Channel arbitrated-loop applications and operate from a 3.3V supply.

The MAX3770 is compatible with Fibre Channel jitter tolerance requirements and can recover data signals with up to 0.7 unit interval (UI) jitter. The circuit's fully integrated phase-locked loop (PLL) provides a frequency lock indication and does not need an external reference clock.

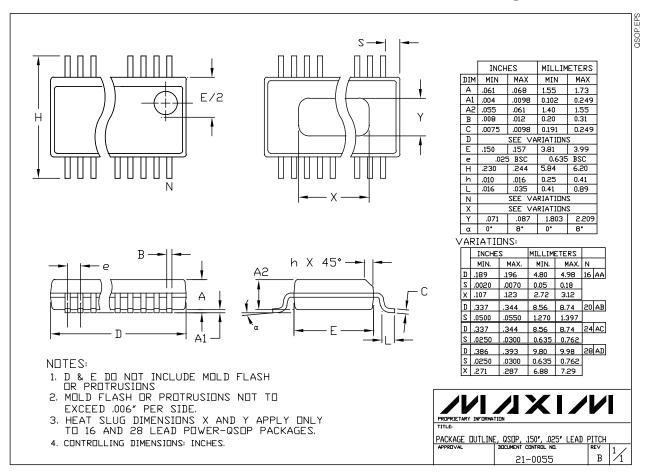

The MAX3770 provides low-jitter CML clock and data outputs. To reduce the external parts count, all signal inputs and outputs are internally terminated. The MAX3770/MAX3771 are available in 16-pin QSOP packages.

## \_Applications

2.125Gbps Fibre Channel 1.063Gbps Fibre Channel Storage Area Networks Fibre Channel Hubs

Fibre Channel Storage Systems

## **Ordering Information**

| PART        | TEMP. RANGE  | PIN-PACKAGE |  |

|-------------|--------------|-------------|--|

| MAX3770CEE  | 0°C to +70°C | 16 QSOP     |  |

| MAX3771CEE* | 0°C to +70°C | 16 QSOP     |  |

<sup>\*</sup>Future product—contact factory for availability.

## **Features**

- **♦ Meet Fibre Channel Jitter Tolerance Requirements**

- ♦ 3.0V to 3.6V Operation

- ♦ Internally Terminated Data and Clock I/O

- **♦ Reference Clock Not Required**

- **♦ Frequency Lock Indication**

- ♦ Low Power Consumption 215mW at 3.3V (MAX3770) 190mW at 3.3V (MAX3771)

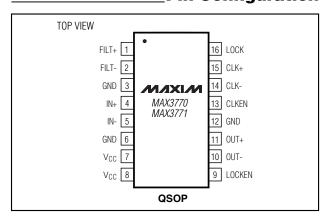

## **Pin Configuration**

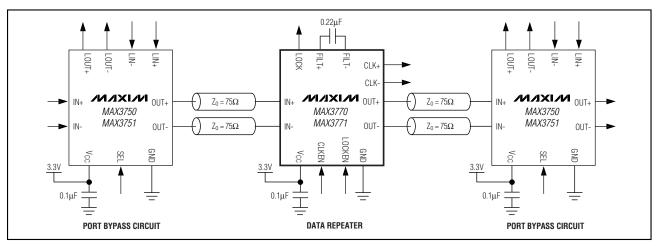

## Typical Application Circuit

MIXIM

Maxim Integrated Products

1

For free samples and the latest literature, visit www.maxim-ic.com or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>CC</sub> 0.5V to +5.0V        | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|------------------------------------------------------|-------------------------------------------------------|

| Pin Voltage Levels (IN+, IN-, FILT+, FILT-,          | 16-Pin TQFP (derate 6.7mW/°C above +70°C)533mW        |

| LOCKEN, CLKEN, LOCK)0.5V to (V <sub>CC</sub> + 0.5V) | Operating Temperature Range0°C to +70°C               |

| LOCK Output Current1mA to +10mA                      | Storage Temperature Range55°C to +150°C               |

| CML Output Currents OUT+, OUT-,                      | Processing Temperature (die)+400°C                    |

| CLK+, CLK22mA to +22mA                               | Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0V \text{ to } +3.6V, T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C.})$

| PARAMETER                                   | CONDITIONS                        |         | MIN | TYP                    | MAX  | UNITS |

|---------------------------------------------|-----------------------------------|---------|-----|------------------------|------|-------|

|                                             | CLKEN = V <sub>CC</sub>           | MAX3771 |     | 63                     |      |       |

| Supply Current (Note 1)                     |                                   | MAX3770 |     | 81                     | 112  | mA    |

|                                             | CLKEN = GND                       | MAX3771 |     | 57                     |      |       |

|                                             |                                   | MAX3770 |     | 67.5                   | 91   |       |

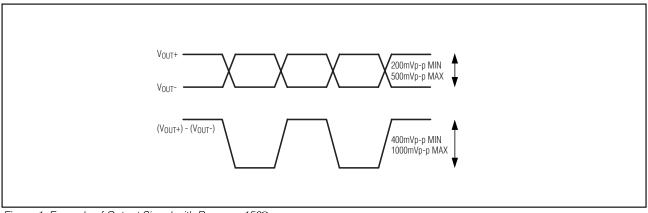

| Differential Voltage Signal at OUT or CLOCK | $R_{LOAD} = 150\Omega$ , Figure 1 |         | 400 | 780                    | 1000 | mVp-p |

| Output Current at OUT or CLOCK              | Sum of IOUT+ and IOUT-            |         |     | 10.5                   |      | mA    |

| LOCK Output Low                             | $I_{OL} = +1mA$                   |         |     |                        | 0.7  | V     |

| LOCK Output High                            | I <sub>OH</sub> = -100μA          |         | 2.4 |                        |      | V     |

| Differential Input Voltage Swing            |                                   |         | 200 |                        | 2200 | mVp-p |

| Input Common-Mode Voltage                   |                                   |         |     | Vcc - 0.45             | 5    | V     |

| Voltage at FILT+, FILT-                     |                                   |         |     | V <sub>CC</sub> - 1.03 | 3    | V     |

| CLOCKEN and LOCKEN Input Current            |                                   |         | -5  |                        | +5   | μA    |

| Differential Input Resistance               |                                   |         | 132 | 150                    | 181  | Ω     |

| Differential Output Resistance              | OUT+, OUT-, CLK+, C               | CLK-    | 132 | 150                    | 181  | Ω     |

Note 1: Supply current includes output currents.

#### AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = 0 ^{\circ} \text{C to } +70 ^{\circ} \text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ} \text{C.})$

| PARAMETER                                  | CONDITIONS                                                                  |                            |     | TYP  | MAX  | UNITS               |  |

|--------------------------------------------|-----------------------------------------------------------------------------|----------------------------|-----|------|------|---------------------|--|

| OPERATION AT 2.125Gbps                     |                                                                             |                            |     |      |      |                     |  |

| Edge Speed                                 | 20% to 80%                                                                  |                            |     | 135  | 170  | ps                  |  |

| Random Jitter Generation at<br>Data Output | T <sub>A</sub> = +25°C                                                      | Input = K28.7+ (Note 2)    |     | 3.4  | 5.3  | ps <sub>RMS</sub>   |  |

|                                            |                                                                             | Input = CRPAT (Note 3)     |     | 2.3  | 3.1  |                     |  |

|                                            |                                                                             | Input = CRPAT (Notes 3, 5) |     | 3.9  | 7.3  |                     |  |

| Deterministic Jitter Generation            | T <sub>A</sub> = +25°C                                                      | Input = K28.5± (Note 4)    |     | 15.6 | 22   | - ps <sub>p-p</sub> |  |

|                                            |                                                                             | Input = CRPAT (Notes 3, 5) |     | 27   | 48   |                     |  |

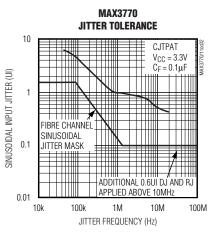

| Jitter Tolerance                           | T <sub>A</sub> = +25°C (Note 5),<br>input = CJTPAT (Note 6)                 | f = 85kHz (Note 7)         | 1.5 | 4.22 |      | UI                  |  |

|                                            |                                                                             | f = 1270kHz (Note 7)       | 0.1 | 0.89 |      |                     |  |

|                                            |                                                                             | f = 10MHz                  |     | 0.36 |      |                     |  |

| CDR Lock Time from Start                   | Input = CJTPAT (Note 6)                                                     |                            | 4.4 |      | ms   |                     |  |

| Propagation Delay                          |                                                                             |                            |     | 1000 | 1500 | ps                  |  |

| Clock to Q Delay                           |                                                                             |                            | 50  | 240  | 300  | ps                  |  |

| OPERATION AT 1.063Gbps                     |                                                                             |                            |     |      |      |                     |  |

| Random Jitter Generation at<br>Data Output |                                                                             | Input = K28.7+ (Note 2)    |     | 3.9  |      | psRMS               |  |

|                                            | T <sub>A</sub> = +25°C                                                      | Input = CRPAT (Note 3)     |     | 2.3  |      |                     |  |

|                                            |                                                                             | Input = CRPAT (Notes 3, 5) |     | 3.4  |      |                     |  |

| Deterministic Jitter Generation            | T <sub>A</sub> = +25°C                                                      | Input = K28.5± (Note 4)    |     | 17   |      | ps <sub>p-p</sub>   |  |

|                                            |                                                                             | Input = CRPAT (Notes 3, 5) |     | 36   |      | ps <sub>p-p</sub>   |  |

| Jitter Tolerance                           | T <sub>A</sub> = +25°C (Note 5),<br>input = CJTPAT (Note 6),<br>BER = IE-12 | f = 42.5kHz                |     | 3.1  |      | UI                  |  |

|                                            |                                                                             | f = 635kHz                 |     | 0.54 |      |                     |  |

|                                            |                                                                             | f = 5MHz                   |     | 0.3  |      |                     |  |

Note 2: K28.7+ pattern: 0011111000

Note 3: Compliant random pattern (CRPAT) in hex:

Pattern

No. of Occurrences

3EAA2AAAAA

6

3EAA6A5A9

1

86BA6C6475 D0E8DCA8B4 7949EAA665

16

72319A95AB

1

C16AAA9AA6

1

**Note 4:** K28.5± pattern: 00111110101100000101

Note 5: Random and deterministic jitter generation at 2.125Gbps is measured with 0.38UI deterministic jitter, and 0.22UI random jitter (BER = 1 x 10-12) applied to the input. Random and deterministic jitter generation at 1.063Gbps is measured with 0.18UI deterministic jitter, and 0.08UI random jitter (BER = 1 x 10-12) applied to the input.

Jitter tolerance at 2.125Gbps is measured with 0.38UI deterministic jitter and 0.22UI random jitter (BER =  $1 \times 10^{-12}$ ) applied to the input. Jitter tolerance at 1.063Gbps is measured with 0.18UI deterministic jitter, and 0.08UI jitter (BER =  $1 \times 10^{-12}$ ) applied to the input.

**Note 6:** Compliant jitter tolerance pattern in hex (CJTPAT):

Pattern

No. of Occurrences

3EAA2AAAAA

6

3EAAA6A5A9

1

871E3871E3

41

871E3870BC78F4AAAAAA

1

AAAAAAAAAAA

12

AAA15555E3 871E3871E1

1

AB9C9686E6

1

C16AAA9AA6

1

Note 7: Jitter tolerance measurements at 85kHz and 1270kHz are limited by test equipment. Actual jitter tolerance > indicated.

## **Pin Description**

| PIN      | NAME   | FUNCTION                                                                                                                                                                                          |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | FILT+  | PLL Loop Filter Connection. Connect a 0.22µF capacitor between FILT+ and FILT                                                                                                                     |

| 2        | FILT-  | PLL Loop Filter Connection. Connect a 0.22µF capacitor between FILT+ and FILT                                                                                                                     |

| 3, 6, 12 | GND    | Ground                                                                                                                                                                                            |

| 4        | IN+    | Positive CML Data Input (Figure 3)                                                                                                                                                                |

| 5        | IN-    | Negative CML Data Input (Figure 3)                                                                                                                                                                |

| 7, 8     | Vcc    | Supply Voltage                                                                                                                                                                                    |

| 9        | LOCKEN | When this input is forced high, the lock indicator is enabled. Ground for normal operation.                                                                                                       |

| 10       | OUT-   | Negative 75Ω CML Data Output (Figure 4)                                                                                                                                                           |

| 11       | OUT+   | Positive 75Ω CML Data Output (Figure 4)                                                                                                                                                           |

| 13       | CLKEN  | When this input is forced high, the clock output is enabled. Ground for normal operation.                                                                                                         |

| 14       | CLK-   | Negative 75 $\Omega$ CML Clock Output (Figure 4). Enabled when CLKEN is forced high; disabled when CLKEN is forced low.                                                                           |

| 15       | CLK+   | Positive $75\Omega$ CML Clock Output (Figure 4). Enabled when CLKEN is forced high; disabled when CLKEN is forced low.                                                                            |

| 16       | LOCK   | Frequency Lock Indicator. High level indicates the PLL is frequency-locked. Disabled when LOCKEN is forced low. The output of the LOCK pin may chatter when large jitter is applied to the input. |

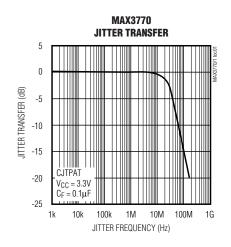

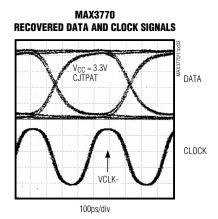

## **Typical Operating Characteristics**

( $V_{CC}$  = +3.3V,  $T_A$  = +25 $^{\circ}C$ , unless otherwise noted.)

Figure 1. Example of Output Signal with  $R_{LOAD} = 150\Omega$

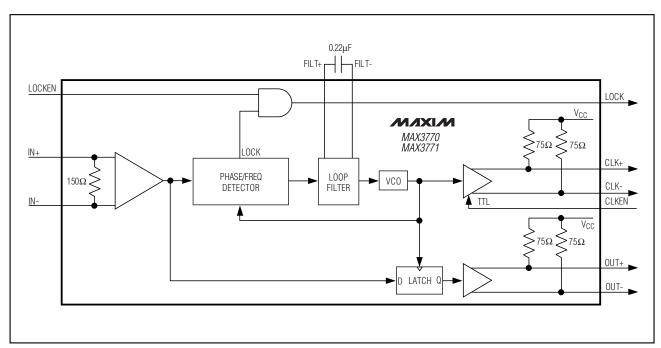

Figure 2. Functional Diagram

## **Detailed Description**

Figure 2 shows the functional diagram of the MAX3770 Fibre Channel repeater IC. The MAX3770 consists of a fully integrated phased-lock loop (PLL), CML input and output buffers, and a data latch. The PLL consists of a phase/frequency detector (PFD), a loop filter, and a voltage-controlled oscillator (VCO). The input and output signal buffers employ low-noise CML architecture and are terminated on-chip.

### **Phase and Frequency Detector**

The phase/frequency detector generates an output signal that reflects the phase relationship between the incoming data and the internal clock generated by the VCO. Data recovery is accomplished by feedback in the PLL, which drives the error voltage to zero, aligning the falling edge of the recovered clock to the center of the data eye.

The phase frequency detector generates a frequency lock indication that can be monitored at the LOCK pin (Table 1). When the PLL is frequency-locked onto the incoming data, lock transitions high.

#### **VCO** and Latch

The fully integrated VCO contains an internal current reference and filter circuitry to minimize the influence of VCC noise. The VCO is trimmed to 2.125GHz (MAX3770) and creates a clock output with frequency proportional to the control voltage applied by the loop filter. Data recovery is accomplished by using the recovered clock signal to latch the incoming data to the CML output buffers, significantly reducing the output jitter.

### Applications Information

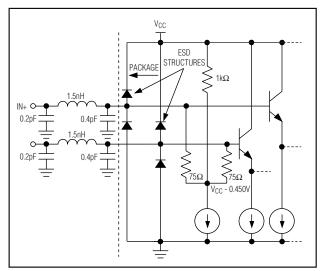

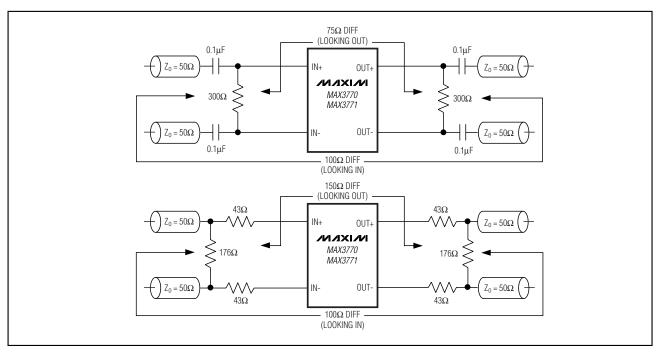

Figures 3 and 4 show models for the MAX3770/MAX3771 inputs and outputs, including package parasitics. Figure 5 shows typical  $50\Omega$  termination applications.

#### Design Procedure

The MAX3770's performance can be greatly affected by circuit board layout and design. Use good high-frequency design techniques, including minimizing ground inductance and using fixed-impedance transmission lines on the data and clock signals. All IN, OUT, and CLK pins can be connected with 0.1µF or 0.01µF coupling capacitors. If DC coupling is desired, pay particular attention to the DC voltage and current requirements at the pins of interest (see *DC Electrical Characteristics*). The MAX3750/MAX3751 port bypass circuit can be DC-coupled to the MAX3770/MAX3771 repeater. A 0.22µF capacitor should be used for the loop filter.

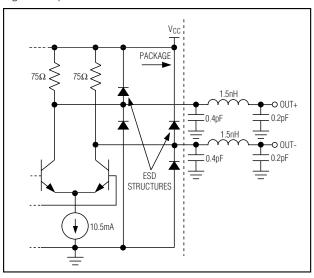

Figure 3. Input Structure

Figure 4. Output Structure

#### **Control Functions**

The lock enable (LOCKEN) and clock enable (CLKEN) pins can be configured to control the PLL's clock. Table 1 shows the operational modes available.

Figure 5.  $50\Omega$  Termination Applications

## **Table 1. Output States When Using Control Functions**

| INPUT PIN LEVEL |       | OUTPUT FUNCTION |          |  |

|-----------------|-------|-----------------|----------|--|

| LOCKEN          | CLKEN | LOCK            | CLOCK    |  |

| GND             | GND   | Disabled        | Disabled |  |

| GND             | Vcc   | Disabled        | Enabled  |  |

| Vcc             | GND   | Enabled         | Disabled |  |

| Vcc             | Vcc   | Enabled         | Enabled  |  |

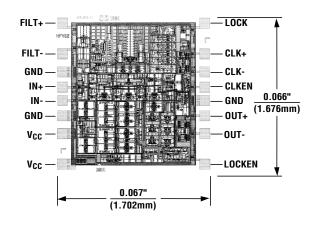

## Chip Topography

TRANSISTOR COUNT: 1217

SUBSTRATE CONNECTED to GND

## **Package Information**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.