### Quad, 12-Bit, µP-Compatible DAC

### General Description

The MX390 contains four 12-bit, voltage-output digital-toanalog converters (DACs) in a compact 28-pin package. The design is based on a double-buffered, 12-bit DAC that reduces chip count and provides high reliability. The MX390 is ideal for systems requiring digital control of many analog voltages where board space is critical.

The monolithic voltage-output DACs inside the MX390 are laser-trimmed to  $\pm 1/2$ LSB max nonlinearity (MX390KD/TD) and absolute accuracy of  $\pm 0.05\%$  of full scale. The internal buried-zener voltage reference provides excellent temperature drift characteristics (20ppm/°C max) and 5mV accuracy. The internal reference buffer provides a high input impedance (>1000M $\Omega$ ) so that multiple MX390 devices can be driven by a single reference voltage.

The individual DACs are accessed by four chip-select inputs and the A0 and A1 lines. These control signals allow the registers of the four DACs to be loaded individually and the outputs to be updated simultaneously.

### \_Applications

Military Products

Minimum Component Count Analog Systems

Control Systems

Test Equipment

MIXIM

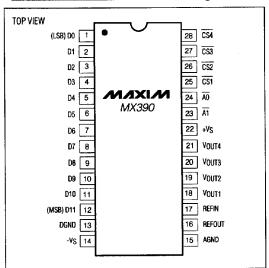

### Pin Configuration

### Features

- ♦ Pin-Compatible Upgrade to AD390 Lower Power: 1W MIL-STD-883B Qualified\*

- ♦ INL ±1/2LSB Max over Military Temperature

- **♦ Monotonicity Guaranteed Over Temperature**

- **♦ Double-Buffered Data Latches**

- ♦ Includes Precision Reference and Buffer

- ♦ Fast Settling: 8µs Max to 1/2LSB

### **Ordering Information**

| PART    | TEMP. RANGE   | PIN-PACKAGE   | INL<br>(LSBs) |

|---------|---------------|---------------|---------------|

| MX390JD | 0℃ to +70℃    | 28 Ceramic SB | ±3/4          |

| MX390KD | 0°C to +70°C  | 28 Ceramic SB | ±1/2          |

| MX390SD | -55℃ to +125℃ | 28 Ceramic SB | ±3/4          |

| MX390TD | -55℃ to +125℃ | 28 Ceramic SB | ±1/2          |

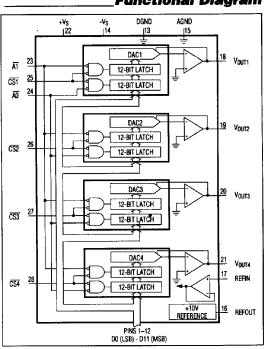

### **Functional Diagram**

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

<sup>\*</sup> Contact factory for availability.

# DEEXM

### Quad, 12-Bit, µP-Compatible DAC

##

| +vs to DGIND                                        | Continuous rower Dissipation (TA = +70°C)           |

|-----------------------------------------------------|-----------------------------------------------------|

| -Vs to DGND                                         | 28-Pin Ceramic SB (derate 33mW/°C above +70°C) 3.5W |

| Digital Inputs (pins 1-12 and 23-28) to DGND0.3V to | Operating Temperature Ranges:                       |

| (+Vs + 0.3V DC)                                     | MX390JD/KD                                          |

| REFIN to AGND                                       | MX390SD/TD55℃ to +125℃                              |

| AGND to DGND                                        | Storage Temperature Range65℃ to +150℃               |

| Outputs (pins 16, 18-21)                            | Junction Temperature Range (Tj) +175℃               |

| Shorted to AGND or DGND Continuous                  | Lead Temperature (soldering, 10sec) +300℃           |

| Shorted to ±Vs Momentary                            |                                                     |

|                                                     |                                                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(Vs =  $\pm 15$ V, T<sub>A</sub> = +25°C, unless otherwise noted.)

| D. D. L. L. T. T. D.         | CAMBO      | CONDITIONS                                | MX390JD/SD |            |       | MX390KD/TD |        |            | UNITS  |

|------------------------------|------------|-------------------------------------------|------------|------------|-------|------------|--------|------------|--------|

| PARAMETER                    | SYMBOL     | CONDITIONS                                | MIN        | TYP        | MAX   | MIN        | TYP    | MAX        | UNIS   |

| DATA INPUTS (Pins 1-12 a     | and 23-28) |                                           |            |            |       |            |        |            |        |

| Input Voltage High           | ViH        |                                           | 2.0        |            |       | 2.0        |        |            | V      |

| Input Voltage Low            | VIL        |                                           |            |            | 8.0   |            |        | 0.8        | V      |

| Input Current High           | ltн        | VIN = 5V                                  |            | 10         | 1200  |            | 10     | 1200       | μА     |

| Input Current Low            | ΙιL        | Vin = 0V                                  |            | 10         | 400   |            | 10     | 400        | μА     |

| Resolution                   |            |                                           |            |            | 12    |            |        | 12         | Bits   |

| OUTPUT (Note 1)              |            |                                           |            |            |       |            |        |            |        |

| Voltage Range (Note 2)       | Vout       | External 10.000V reference                |            |            | ±10   |            |        | ±10        | V      |

| Current                      |            |                                           | ±5         |            |       | ±5         |        |            | mA     |

| Settling Time                | tSETT      | To ±1/2LSB                                |            | 4          | 8     |            | 4      | 8          | μs     |

| ACCURACY                     |            |                                           |            |            |       |            |        |            |        |

| Gain Error (Note 3)          | Ae         | External 10.000V reference, all bits high |            | ±0.05      | ±0.1  |            | ±0.025 | ±0.05      | % FSR  |

| Offset Error                 | Vos        | External 10.000V reference, all bits low  |            | ±0.025     | ±0.05 |            | ±0.012 | ±0.025     | % FSR  |

| Integral Linearity Error     | LE         |                                           |            | ±0.25      | ±0.75 |            | ±0.125 | ±0.5       | LSB    |

| Differential Linearity Error | DLE        |                                           |            | ±0.5       | ±0.75 |            | ±0.25  | ±0.5       | LSB    |

| TEMPERATURE DRIFT            |            |                                           |            | ·          |       |            |        |            |        |

| Onin                         | T-/A-      | Internal reference                        |            |            | ±40   |            |        | ±20        | ppm/°C |

| Gain                         | TC/AE      | External 10.000V reference                |            |            | ±10   |            |        | <b>±</b> 5 | ppity  |

| Bipolar Zero                 | TC/PBZ     |                                           |            |            | ±10   |            |        | ±5         | ppm/°C |

| Integral Linearity Error     | LE         | TA = TMIN to TMAX                         |            | ±0.5       | ±0.75 |            | ±0.25  | ±0.5       | LSB    |

| Differential Linearity Error | DLE        | Monotonicity guaranteed over              | full temp  | oerature r | ange  |            |        |            |        |

| CROSSTALK (Note 4)           |            |                                           |            | 0.1        |       |            | 0.1    |            | LSB    |

### Quad, 12-Bit, µP-Compatible DAC

### **ELECTRICAL CHARACTERISTICS (continued)**

(Vs =  $\pm 15$ V, TA = +25°C, unless otherwise noted.)

| DADAMETED                              | CVIIDOI    | 001101710110                   | MX390JD/SD |                  |        | MX390KD/TD |                  |        |            |  |

|----------------------------------------|------------|--------------------------------|------------|------------------|--------|------------|------------------|--------|------------|--|

| PARAMETER                              | SYMBOL     | CONDITIONS                     | MIN        | TYP              | MAX    | MIN        | TYP              | MAX    | UNITS      |  |

| REFERENCE OUTPUT                       |            |                                |            |                  |        |            |                  |        |            |  |

| Voltage                                |            | No load                        | 9.995      | 10.000           | 10.005 | 9.995      | 10.000           | 10.005 | V          |  |

| Current                                |            | Available externally           | 2.5        | 3.5              |        | 2.5        | 3.5              |        | mA         |  |

| REFERENCE INPUT                        | •          |                                |            |                  |        |            |                  |        | ,          |  |

| Input Resistance                       |            |                                |            | 10 <sup>10</sup> |        |            | 10 <sup>10</sup> |        | Ω          |  |

| Voltage Range                          |            |                                | 5          |                  | 11     | 5          |                  | 11     | ٧          |  |

| POWER REQUIREMEN                       | TS         |                                |            |                  |        |            |                  |        |            |  |

|                                        | 12.4-      | 10V reference ±13.5 ±15 ±16    |            | ±16.5            | ±13.5  | ±15        | ±16.5            | V      |            |  |

| Voltages                               | ±Vs        | External 8.192V reference      | ±11.4      |                  | ±16.5  | ±11.4      |                  | ±16.5  | <b>`</b> _ |  |

| Currents<br>+Vs                        | lcc        |                                |            | 38               | 50     |            | 38               | 50     | mA         |  |

| -Vs                                    | IEE        |                                |            | -26              | -40    |            | -26              | -40    | mA         |  |

| Power Dissipation                      |            | Vs = ±15V                      |            | 0.96             | 1.35   |            | 0.96             | 1.35   | w          |  |

| POWER-SUPPLY GAIN                      | SENSITIVIT | Y                              | -          |                  |        |            |                  | ,      |            |  |

| +Vs                                    | PSRR+      | +Vs = +15c ±10%,<br>-Vs = -15V |            | ±0.002           | ±0.006 |            | ±0.002           | ±0.006 | %FSR/%     |  |

| -Vs                                    | PSRR-      | -Vs = -15V ±10%,<br>+Vs = 15V  |            | ±0.002           | ±0.006 |            | ±0.002           | ±0.006 | %FSR/%     |  |

| TIMING SPECIFICATIO                    | NS         | ****                           |            |                  |        |            |                  |        |            |  |

| CS1-CS4 Valid Before<br>A0 Rising Edge | taw        |                                | 100        |                  |        | 100        |                  |        | ns         |  |

| A0, A1 Low Time                        | twp        |                                | 100        |                  |        | 100        |                  |        | ns         |  |

| Data Valid Before A0<br>Rising Edge    | tow        |                                | 50         |                  |        | 50         |                  |        | ns         |  |

| Data Valid After A0<br>Rising Edge     | tDH        |                                | 10         |                  |        | 10         |                  |        | ns         |  |

| CS1-CS4 Valid Before<br>A1 Low         | tas        | ·                              | 0          |                  |        | ٥          |                  |        | ns         |  |

Note 1: The MX390 outputs are guaranteed stable for load capacitances up to 500pF. Note 2:  $\pm 10V$  range is standard. Contact factory for 0V to  $\pm 10V$  range. Note 3: Full-scale range (FSR)  $\pm 20V$  for the  $\pm 10V$  bipolar range. Note 4: Crosstalk is defined as the change in any one output as a result of any other output being driven from -10V to  $\pm 10V$ ,  $\pm 10$

### Quad, 12-Bit, µP-Compatible DAC

# MX390 Digital Circuit Details Data and Control Signal Format

The MX390 data input format is 12-bit parallel. The DAC register is selected by control signals CS1-CS4, while the latches are controlled by the signals AO and A1. The input registers are double-buffered, allowing any register to be updated independently of the others. As detailed in Table 1, the four chip-select lines address the DAC register of interest. More than one chip select may be active at any time. The first-rank register of a given DAC is loaded by bringing the appropriate chip select and A0 both low. The second-rank register of any DAC is then loaded by bringing the appropriate chip select and A1 both low. If CS1-CS4 are all brought low coincident with A1 low, all four DAC outputs will be updated to the value in the corresponding first-rank registers. All control inputs are level-sensitive and may be hard-wired low to render any register (or group of registers) transparent.

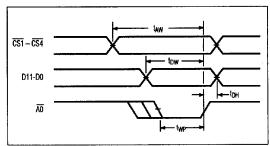

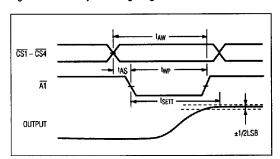

#### Timing

The MX390 control-signal timing is fairly straightforward. The desired control signals from  $\overline{A0}$ ,  $\overline{A1}$ , and  $\overline{CS1-CS4}$  must be concurrently valid for at least 100ns for an operation to occur. Data is latched on the rising edge of  $\overline{A0}$  and

Figure 1a. Write-Cycle Timing Diagram

Figure 1b. Write-Cycle Timing Diagram

A1. When loading data from a bus into the first-rank register, the data setup time is 50ns and the data hold time is zero. When loading the second-rank registers, it is possible to excerise the chip-select inputs simultaneously with A1. DAC settling time is measured from the falling edge of the last control signal to be asserted.

#### **Reference Connections**

The MX390 is equipped with an internal reference of 10V ±5mV. This reference is available for external use and can typically source up to 3.5mA. In normal operation, this reference is connected to REFIN, which establishes the ±10V output scale. If higher accuracy or a range other than ±10V is desired, an external reference such as the MAX671 (1ppm/°C) may be used.

#### **Power-Supply Decoupling**

Decouple +Vs and -Vs to AGND using a 10µF capacitor in parallel with a 0.1µF ceramic capacitor with short leads. AGND and DGND should be returned separately to the system ground.

Table 1. MX390 Truth Table

| CS1 | CS2 | CS3 | CS4 | Ā1 | AO | OPERATION                             |

|-----|-----|-----|-----|----|----|---------------------------------------|

| 1   | 1   | 1   | 1   | Х  | Х  | No operation                          |

| Х   | Х   | Х   | Х   | 1  | 1  | No operation                          |

| 0   | 1   | 1   | 1   | 1  | 0  | Enable first rank of DAC1             |

| 1   | 0   | 1   | 1   | 1  | 0  | Enable first rank of DAC2             |

| 1   | 1   | 0   | 1   | 1  | 0  | Enable first rank of DAC3             |

| 1   | 1   | 1   | 0   | 1  | 0  | Enable first rank of DAC4             |

| 0   | 1   | 1   | 1   | 0  | 1  | Load DAC1 second rank from first rank |

| 1   | 0   | 1   | 1   | 0  | 1  | Load DAC2 second rank from first rank |

| 1   | 1   | 0   | 1   | 0  | 1  | Load DAC3 second rank from first rank |

| 1   | 1   | 1   | 0   | 0  | 1  | Load DAC4 second rank from first rank |

| 0   | 0   | 0   | 0   | 0  | 0  | All latches transparent               |

Table 2. MX390 Analog Output vs. Digital Input (±10V Scale)

| Digital Input Code |      |      | Analog Output Voltage |                     |  |

|--------------------|------|------|-----------------------|---------------------|--|

| 0000               | 0000 | 0000 | -10.00V               | - Full Scale        |  |

| 0100               | 0000 | 0000 | -5.000V               | - 1/2 Scale         |  |

| 1000               | 0000 | 0000 | 0.000V                | Zero                |  |

| 1000               | 0000 | 0001 | +4.88mV               | + 1LSB              |  |

| 1100               | 0000 | 0000 | +5.000V               | + 1/2 Scale         |  |

| 1111               | 1111 | 1111 | +9.9951V              | + Full Scale - 1LSB |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.