### **General Description**

Maxim's MAX310 and MAX311 are CMOS monolithic analog multiplexer/demultiplexers designed for use with signal frequencies ranging from DC through video. The MAX310 is a 1-of-8 multiplexer while the MAX311 is for 2-of-8 (4 channel differential) applications.

A key feature of the MAX310/311 is extremely high off isolation at high frequencies. The isolation of each off channel to the output is guaranteed to be -66dB at 5MHz. The input signal range is +12V to -15V with  $\pm15V$  power supplies while power consumption is typically 1.1mW.

All control inputs are fully compatible with TTL and CMOS logic. Decoding is in standard BCD format and an Enable input is also provided to simplify cascading of devices. The MAX310 and MAX311 will operate with nearly any power supply combination which totals less than 36V (V<sup>+</sup> – V<sup>-</sup>) including single supply operation at +12V, +15V, and +28V with V-connected to GND.

### **Applications**

Video Switching and Crosspoint Systems Automatic Test Equipment Medical Ultrasound Phased Array Systems Data Logging of High Frequency Signals Digital Signal Processing

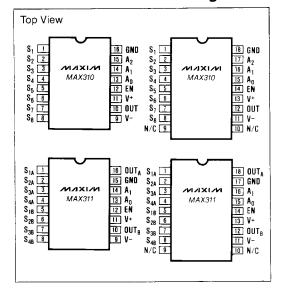

### Pin Configuration

#### \_ Features

- → -76dB Typical Off Isolation at 5MHz

- ♦ -63dB Typical "All Channel Off" Isolation at 5MHz

- Phase Shift Match Between Channels, <1° at 5MHz

- ◆ Break-Before-Make Switching

- ► Wide Supply Range, ±4.5V to ±16.5V and Single Supply

- Symmetrical, Bi-directional Operation

- ♦ Latch-Up Proof Construction

### **Ordering Information**

| PART      | TEMP. RANGE       | PACKAGE             |

|-----------|-------------------|---------------------|

| MAX310C/D | 0°C to + 70°C     | Dice                |

| MAX310CPE | 0°C to + 70°C     | 16 Lead Plastic DIP |

| MAX310CWN | 0°C to + 70°C     | 18 Lead Wide SO     |

| MAX310EPE | 40°C to +85°C     | 16 Lead Plastic DIP |

| MAX310EWN | -40°C to +85°C    | 18 Lead Wide SO     |

| MAX310EJE | -40°C to +85°C    | 16 Lead CERDIP      |

| MAX310MJE | - 55°C to + 125°C | 16 Lead CERDIP      |

| MAX311C/D | 0°C to +70°C      | Dice                |

| MAX311CPE | 0°C to +70°C      | 16 Lead Plastic DIP |

| MAX311CWN | 0°C to - 70°C     | 18 Lead Wide SO     |

| MAX311EPE | - 40°C to + 85°C  | 16 Lead Plastic DIP |

| MAX311EWN | - 40°C to +85°C   | 18 Lead Wide SO     |

| MAX311EJE | - 40°C to +85°C   | 16 Lead CERDIP      |

| MAX311MJE | - 55°C to + 125°C | 16 Lead CERDIP      |

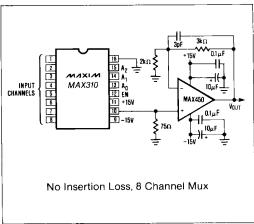

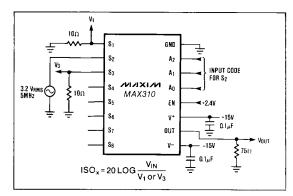

### Typical Operating Circuit

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage referenced to V <sup>-</sup> | Operating Temperature Range                      |

|--------------------------------------|--------------------------------------------------|

| V <sup>+</sup> +36V                  | MAX310C, MAX311C 0°C to +70°C                    |

| GND +24V                             | MAX310E, MAX311E40°C to +85°C                    |

| Digital Inputs V- to V+              | MAX310M, MAX311M55°C to +125°C                   |

| Input Current                        | Power Dissipation (16-Pin packages)              |

| S and COMMON OUT ±50mA               | CERDIP (derate 10mW/°C above +75°C)              |

| All pins except S and COM. OUT ±30mA | Plastic DIP (derate 7.35mW/°C above +75°C) 550mW |

| Lead Temperature +300°C              | Small Outline (derate 9mW/°C above +75°C) 550mW  |

| Storage Temperature65°C to +150°C    |                                                  |

Stresses listed under "Absolute Maximum Ratings" may be applied (one at a time) to devices without resulting in permanent damage. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

**ELECTRICAL CHARACTERISTICS**(Over Temperature. V<sup>+</sup> = +15V, V<sup>-</sup> = -15V, GND = 0V unless otherwise indicated)

| PARAMETER                                           | SYMBOL                                    | CONDITIONS                                                                                 | MIN.      | TYP.                 | MAX.             | UNIT |

|-----------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------|-----------|----------------------|------------------|------|

| Analog Signal Range                                 |                                           | V <sup>+</sup> , V <sup>-</sup> = ±15V<br>V <sup>+</sup> , V <sup>-</sup> = ±5V            | -15<br>-5 |                      | +12<br>+2        | v    |

| Channel ON Resistance                               | Ron                                       | V <sub>IN</sub> = ±5V, I <sub>OUT</sub> = 10mA<br>T <sub>A</sub> = +25°C<br>Over Temp.     |           | 150                  | 250<br>300       | Ω    |

| ON Resistance Match                                 | ΔR <sub>ON</sub>                          | V <sub>IN</sub> = ±5V, I <sub>OUT</sub> = 10mA                                             |           | 6                    |                  | %    |

| OFF Input Leakage Current                           | S(OFF)                                    | Figure 10, T <sub>A</sub> = +25°C<br>Over Temp                                             |           | 0.4<br>3             | 10<br>100        | nA   |

| OFF Output<br>Leakage Current                       | I <sub>D(OFF)</sub>                       | Figure 11, T <sub>A</sub> = +25°C<br>MAX310 Over Temp.<br>MAX311 Over Temp.                |           | 0.8<br>20<br>10      | 10<br>100<br>50  | nA   |

| ON Channel<br>Leakage Current                       | I <sub>D(ON)</sub>                        | Figure 12, T <sub>A</sub> = +25°C<br>MAX310 Over Temp.<br>MAX311 Over Temp.                |           | 1<br>30<br>15        | 10<br>200<br>100 | nA   |

| Input Low Threshold                                 | V <sub>AL</sub>                           | V <sup>+</sup> /V <sup>-</sup> = ±15V, ±5V                                                 |           |                      | 0.8              | V    |

| Input High Threshold                                | V <sub>AH</sub>                           | V <sup>+</sup> /V <sup>-</sup> = ±15V, ±5V                                                 | 2.4       |                      |                  | ٧    |

| Input Current (Logic)                               | IA                                        | V <sub>A</sub> = 0V or 5V                                                                  |           |                      | ±10              | μА   |

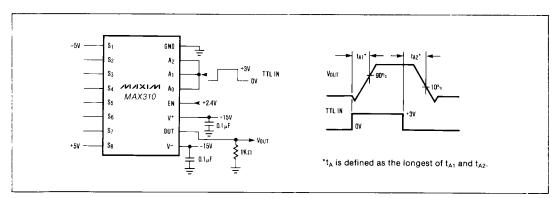

| Access Time                                         | tacc                                      | Figure 7; T <sub>A</sub> = +25°C<br>Over Temp.                                             |           | 0.6                  | 1.5<br>2.0       | μS   |

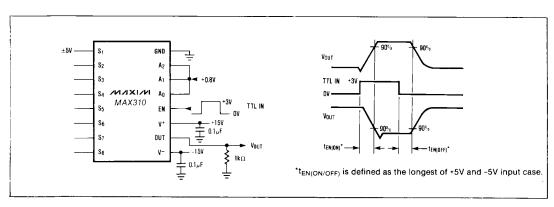

| Enable Delay ON or OFF                              | ten(ON/OFF)                               | Figure 8; T <sub>A</sub> = +25°C<br>Over Temp.                                             |           | 0.3                  | 1.0<br>2.0       | μS   |

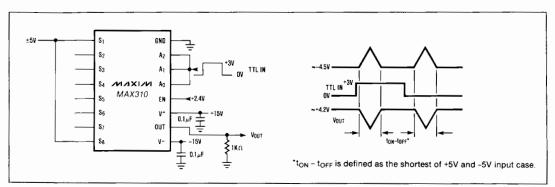

| Break-Before-Make Delay                             | ton-toff                                  | Figure 9                                                                                   | 30        | 100                  |                  | ns   |

| OFF Isolation, Single<br>Channel to OUT             | ISO <sub>SC</sub>                         | Figure 3; T <sub>A</sub> = +25°C                                                           | -66       | -76                  |                  | dB   |

| OFF Isolation, All<br>Channels to OUT               | ISO <sub>AC</sub>                         | Figure 4, 5, T <sub>A</sub> = +25°C<br>MUX Disabled, EN = +0.8V<br>MUX Enabled, EN = +2.4V |           | -63<br>-58           |                  | dB   |

| Adjacent Channel Crosstalk                          | ISO <sub>X</sub>                          | Figure 6, T <sub>A</sub> = +25°C                                                           |           | -72                  | -                | dB   |

| Channel Input Capacitance<br>OFF State<br>ON State  | C <sub>S(OFF)</sub><br>C <sub>S(ON)</sub> | T <sub>A</sub> = +25°C, V <sub>IN</sub> = 10mV <sub>RMS</sub> 10 MHz                       |           | 5<br>45              |                  | pF   |

| Channel Output Capacitance<br>OFF State<br>ON State | C <sub>D(OFF)</sub>                       | T <sub>A</sub> = +25°C;<br>EN = +0.8V, MAX310<br>MAX311<br>EN = +2.4V, MAX310<br>MAX311    |           | 38<br>20<br>57<br>40 |                  | pF   |

| Charge Injection                                    | Q                                         | Figure 13, T <sub>A</sub> = +25°C                                                          |           | 110                  |                  | рС   |

| Supply Current; V <sup>+</sup><br>V <sup>-</sup>    | +<br> -                                   | EN, A0, A1, A2 = 0V or +5V                                                                 |           | 75<br>0.1            | 200<br>100       | μА   |

| Supply Voltage Range                                |                                           | T <sub>A</sub> = +25°C                                                                     | ±4.5      |                      | ±16.5            | V    |

### **Detailed Description**

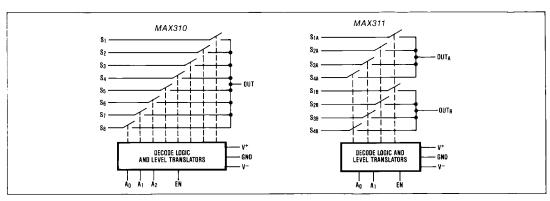

Figure 1. Functional Block Diagrams

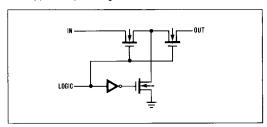

The Maxim MAX310 and MAX311 contain 8 video switches combined with an address decoder and level translators (Figure 1). Each of the 8 video switches consists of 3 N-channel FETs configured as shown in Figure 2. This "T" configuration provides the high frequency OFF isolation required when switching wide-band video, audio, or digital signals.

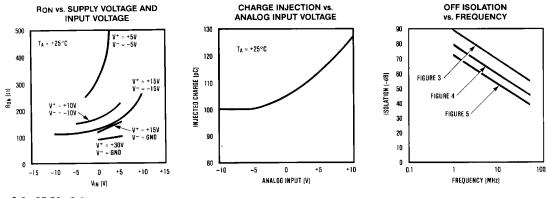

N-channel FETs are used in the MAX310/311's "T" switches because of their low capacitance and consequently superior isolation characteristics. A side effect is that the N-channel ON resistance varies somewhat with the voltage difference between the analog input signal and V<sup>+</sup>. This effect is shown in the Typical Operating Characteristics section.

Figure 2. N-channel T Switch

Channel selection is performed by applying a binary input to the address inputs  $A_0$ ,  $A_1$  and  $A_2$  ( $A_0$  and  $A_1$  only for MAX311). The address decoder selects channels as shown in the truth tables (Table 1). All digital inputs are compatible with TTL and CMOS logic

Break-before-make switch timing is guaranteed for both multiplexers. This prevents momentary shorting of inputs when changing multiplexer channels. The MAX310 and MAX311 are also fully bilateral and so can be used "backwards", as demultiplexers, with no loss in performance. Specifically, one input signal can be routed to one of several outputs.

## TABLE 1. CHANNEL SELECTION INPUT CODES

| MAX310         |    |       | MAX311 |            |                |                  |    |            |

|----------------|----|-------|--------|------------|----------------|------------------|----|------------|

| A <sub>2</sub> | Αı | $A_0$ | EN     | ON Channel | A <sub>1</sub> | $\mathbf{A}_{0}$ | EN | ON Channel |

| 0              | 0  | 0     | 1      | 1          | 0              | 0                | 1  | 1A + 1B    |

| 0              | 0  | 1     | 1      | 2          | 0              | 1                | 1  | 2A + 2B    |

| 0              | ħ  | 0     | 1      | 3          | 1              | 0                | 1  | 3A + 3B    |

| 0              | 1  | 1     | 1      | 4          | 1              | 1                | 1  | 4A + 4B    |

| 1              | 0  | 0     | 1      | 5          | X              | Х                | 0  | ALL OFF    |

| 1              | 0  | 1     | 1      | 6          |                |                  |    |            |

| 1              | 1  | 0     | 1      | 7          |                |                  |    |            |

| 1              | 1  | 1     | 1      | 8          | i              |                  |    |            |

| Х              | Χ  | Χ     | 0      | ALL OFF    | i              |                  |    |            |

# Application Hints Maximizing Isolation

With all high frequency circuits, careful printed circuit board layout is essential for optimum performance. To maintain the high frequency isolation of the MAX310/311, signal paths should be of minimum length and ground plane should be used where possible, including between adjacent input pins. A ground or power supply trace between adjacent inputs will markedly improve isolation between channels.

Both V<sup>+</sup> and V<sup>-</sup> should be bypassed to ground with  $0.1\mu F$  ceramic capacitors. The leads of the capacitors should be kept as short as possible to minimize

series inductance. The bypass capacitors should also be located as physically close to the multiplexer as possible.

### Input Capacitance

The capacitance of an input channel changes from about 5pF in the OFF state to around 45pF when ON. To minimize bandwidth reduction due to input capacitance, the inputs should be driven from a low impedance source. A  $75\Omega$  source impedance results in a 3dB frequency response of 47MHz when loaded with 45pF.

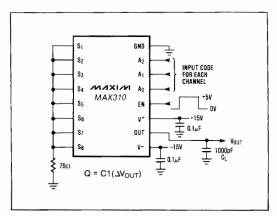

#### Charge Injection

With  $\pm 15 \mathrm{V}$  supplies, injected charge from the internal switch drive circuitry to the analog signal path is typically 110 picocoulombs. As shown in the Typical Characteristics graph, charge injection is relatively independent of the analog signal voltage.

### Insertion Loss

With  $\pm 15 V$  supplies and  $\pm 2 V$  video signals, the  $120 \Omega$  typical ON resistance of the MAX310/311 results in -8.3dB insertion loss when used with a  $75 \Omega$  output load. This insertion loss is virtually constant from DC to over 20MHz.

**TABLE 2. PHASE SHIFT AT 10MHz**

| INPUT CHANNEL                    | OUTPUT - INPUT PHASE SHIFT |                      |  |  |

|----------------------------------|----------------------------|----------------------|--|--|

| MAX311                           | R <sub>L</sub> = 10kΩ      | R <sub>L</sub> = 75Ω |  |  |

| S <sub>1</sub>                   | -22°                       | -12°                 |  |  |

| S <sub>2</sub>                   | -21°                       | -11.5°               |  |  |

| S <sub>2</sub><br>S <sub>3</sub> | -20°                       | -11.5°               |  |  |

| S <sub>4</sub>                   | -20°                       | -11.2°               |  |  |

| S <sub>5</sub>                   | -20°                       | -11.2°               |  |  |

| S <sub>6</sub>                   | -20.5°                     | -11.4°               |  |  |

| S <sub>7</sub>                   | -20.7°                     | -11.5°               |  |  |

| S <sub>8</sub>                   | -20.4°                     | -11.5°               |  |  |

Test Conditions:  $V^+ = +15V$ ,  $V^- = -15V$ ,  $V_{IN} = 1.25V_{RMS}$  at 10MHz, OFF inputs terminated with 75(1).

#### Operation with Power Supplies Other Than ±15V

Table 3 shows how different power supply voltages affect the MAX310/311's analog signal range and channel ON resistance (R<sub>ON</sub>). This data is also shown graphically in the Typical Operating Characteristics section. Since N-channel FETs are used in the switches, R<sub>ON</sub> is determined by the voltage difference between V<sup>+</sup> and the input voltage. For lowest R<sub>ON</sub>, use a negative power supply (V<sup>-</sup>) equal to the most negative input voltage, and a positive power supply (V<sup>+</sup>) 30V above the negative supply. For example, if only positive signals need to be switched, use 0V for V<sup>-</sup> and +30V for V<sup>+</sup> to achieve minimum R<sub>ON</sub>. This also reduces ON resistance variation with analog signal level and input voltage dependent changes in insertion loss, which minimizes differential gain errors.

The digital input thresholds are nearly independent of V<sup>+</sup>, remaining near +1.4V over the entire operating supply voltage range of  $\pm 4.5V$  to  $\pm 18V$  (9V to 36V single supply).

The MAX310/311 switching delay times vary somewhat with power supply voltage. Access time (see Figure 2) increases from typically 600ns with  $\pm 15V$  supplies to  $3\mu s$  with  $\pm 5V$  supplies. Other switching times are also proportionately longer with  $\pm 5V$  power supplies.

### **Propagation Delay and Phase Shift**

In Table 2, the typical phase shift for each channel is shown. Note that both the phase shift and the phase shift difference between channels are reduced with a  $75\Omega$  output load. At 10MHz, the channel-to-channel match is better than 1° with a  $75\Omega$  load and improves as the frequency is reduced.

Phase shift measurements for the MAX311 are similar to those in Table 2. The data for the MAX310 channels 1 to 4 corresponds to MAX311 channels 1A to 4A, Channels 5 to 8 correspond to MAX311 channels 1B to 4B.

## TABLE 3. SIGNAL RANGE AND RON VS SUPPLY VOLTAGE

| SUPPLY VOLTAGE |      | CIONAL DANCE | TYPICAL RON AT VIN |              |  |  |

|----------------|------|--------------|--------------------|--------------|--|--|

| V- V+          |      | SIGNAL RANGE | NEGATIVE           | POSITIVE     |  |  |

| -15            | +15V | -15V to +12V | 104Ω at -10V       | 265Ω at +10V |  |  |

|                |      | -5V to +5V   | 115Ω at -5V        | 150Ω at +5V  |  |  |

| GND            | +15V | 0V to +12V   | 120Ω at 0V         | 150Ω at +5V  |  |  |

| GND            | +30V | 0V to +27V   | 90Ω at 0V          | 100Ω at +5V  |  |  |

| -5V            | +5V  | -5V to +2V   | 240Ω at -2V        | 480Ω at +2V  |  |  |

| -10V           | +10V | -10V to +7V  | 140Ω at -5V        | 220Ω at +5V  |  |  |

| -5V            | +15V | -5V to +12V  | 115Ω at -5V        | 150Ω at +5V  |  |  |

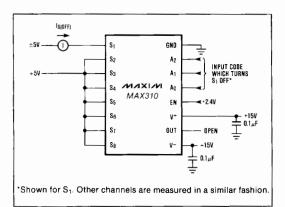

#### **OFF Isolation Measurements**

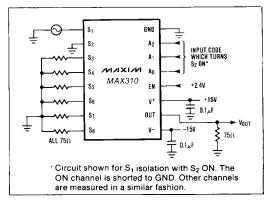

Figure 3 is used to test and specify the MAX310/311's single channel OFF isolation. In the case illustrated, channel S<sub>1</sub> has signal applied while all other inputs are grounded through  $75\Omega$  except for the ON channel (S<sub>2</sub> in Figure 3). This is shorted directly to ground to prevent pickup from external wiring. Each channel meets this test to an isolation limit of –66dB at 5MHz.

Figure 3. Single Channel OFF Isolation (ISO<sub>SC</sub>) Test Circuit

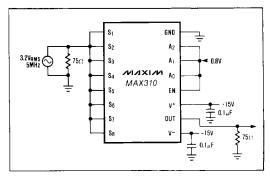

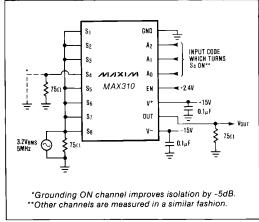

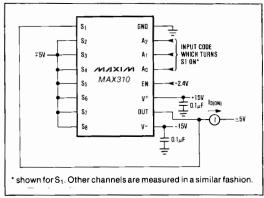

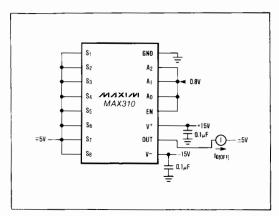

Figure 4 shows the test circuit for OFF isolation with all channels driven. The impedance of the source connected to the selected channel (in this case,  $S_4$ ) significantly affects feedthrough. With a  $75\Omega$  source impedance the typical measured OFF isolation is -58dB at 5MHz. This increases to -63dB if the source impedance is reduced to  $10\Omega$  or less. OFF isolation also increases with decreasing frequency. For example, when the frequency is reduced from 10MHz to 1MHz the isolation improvement is typically -20dB. Figure 5 shows a similar circuit for testing all-channel isolation with the multiplexer disabled (EN low).

Figure 4. All Channel OFF Isolation (ISO<sub>AC</sub>) Test Circuit (MUX Disabled)

Figure 5. All Channel OFF Isolation (ISO<sub>AC</sub>) Test Circuit (MUX Enabled)

### Typical Operating Characteristics

/VI/IXI/VI

ł

Figure 6. Adjacent Channel Crosstalk (ISO<sub>X</sub>) Test Circuit

Figure 7. Access Time  $(t_A)$  Test Circuit.

Figure 8. Enable Delay  $(t_{EN(ON/OFF)})$  Test Circuit.

Figure 9. Break-Before-Make Delay ( $t_{\rm ON}$ - $t_{\rm OFF}$ ) Test Circuit.

Figure 10. OFF Input Leakage Current Test Circuit.

Figure 12. ON Output Leakage Current Test Circuit.

Figure 11. OFF Output Leakage Current Test Circuit.

Figure 13. Charge Injection (Q) Test Circuit