# **MX98728EC**

**GMAC**

# SINGLE CHIP 10/100 FAST ETHERNET CONTROLLER FOR GENERIC APPLICATION

#### 1.0 Features

- 32 bits general purpose asynchronous bus architecture up to 33Mhz for easy system application

- Single chip solution integrating 10/100 TP transceiver to reduce overall cost

- · Optional MII interface for external tranceiver.

- Fully compliant with the IEEE 802.3u spec.

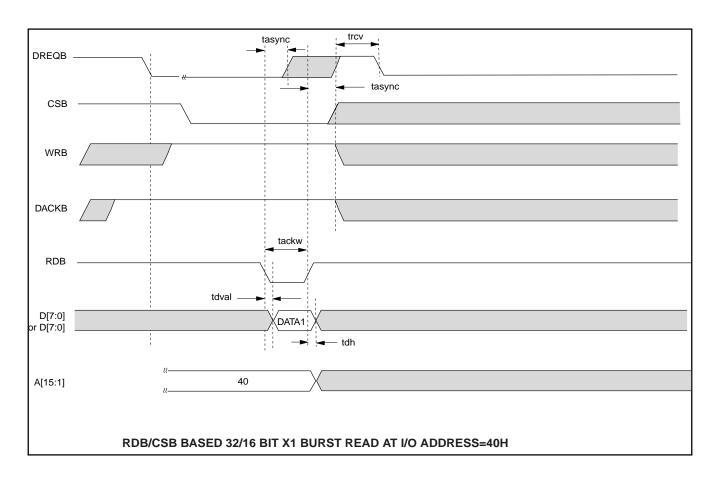

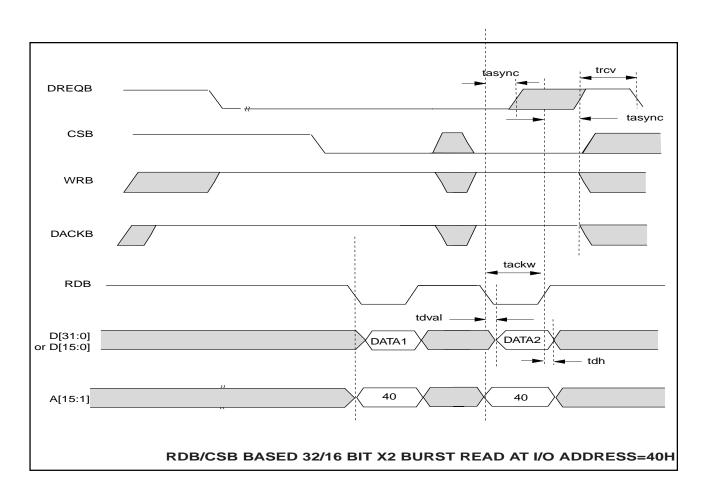

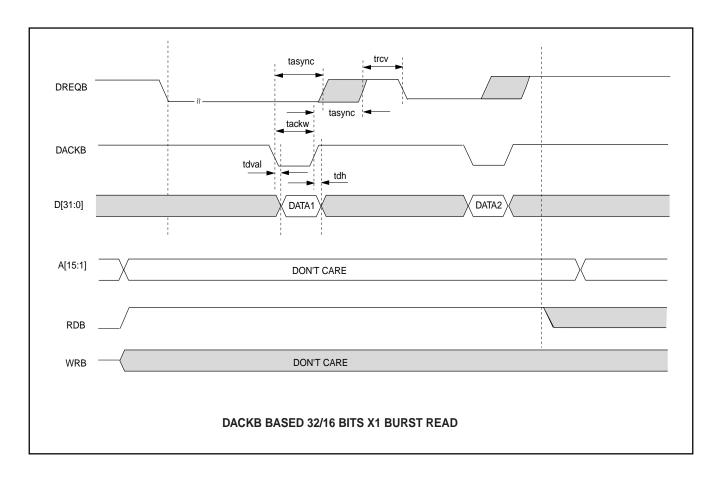

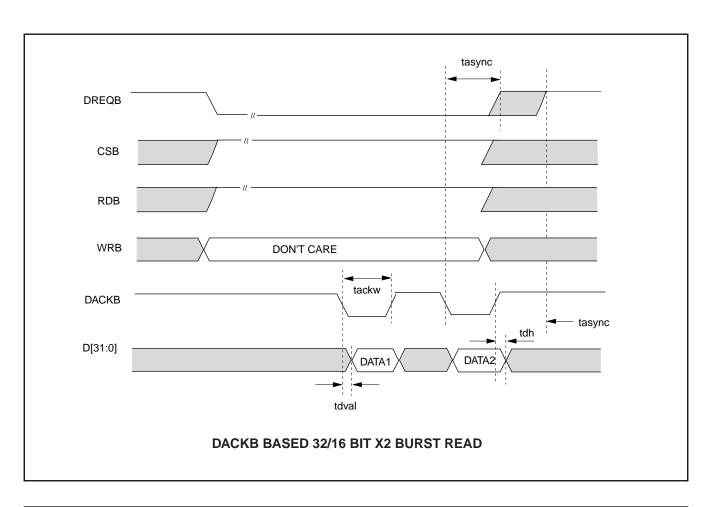

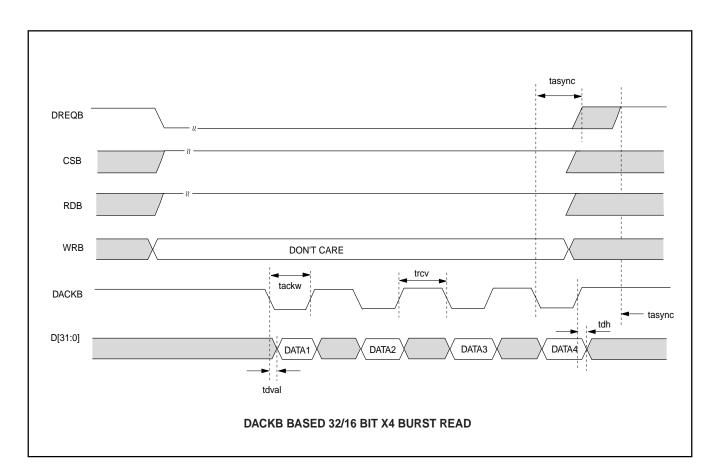

- Supports 32/16 bits x1, x2, x4 burst read transfers for the receive packet buffer

- Packet buffer access through an IO mapped port or host DMA for a wide variety of bus applications

- Programmable bus integrity check timer and interrupt assertion scheme

- Supports 16/8 bits packet buffer data width and 32/ 16 bits host bus data width

- Separated TX and RX FIFOs to support the full duplex mode, independent TX and RX channel

- Rich on-chip registers to support a wide variety of network management functions

- 1.6KBTX FIFO to support maximum network throughput in the full duplex mode

- 16/8 bits SRAM interface of the packet buffer supporting burst DMA for on-chip FIFOs

- Flexible packet buffer partition and addressing space for up to 1MB

- NWAY autonegotiation function to automatically set up network speed and protocol

- · 3 loop back modes for system level diagnosis

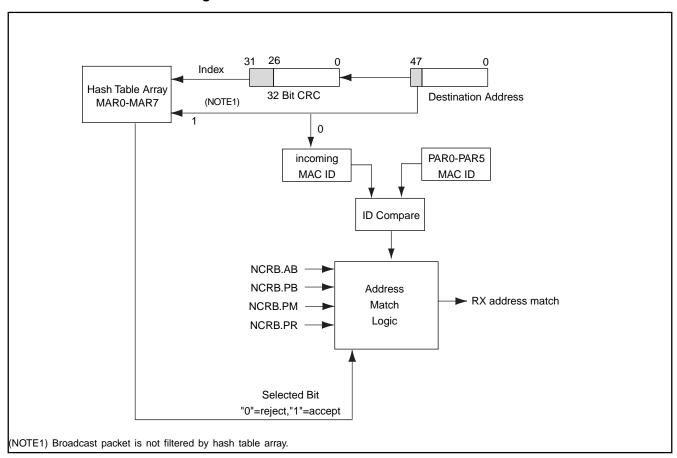

- Supports 64 bits hash table for multicast addressing, broadcast control.

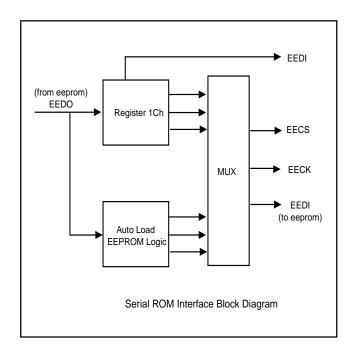

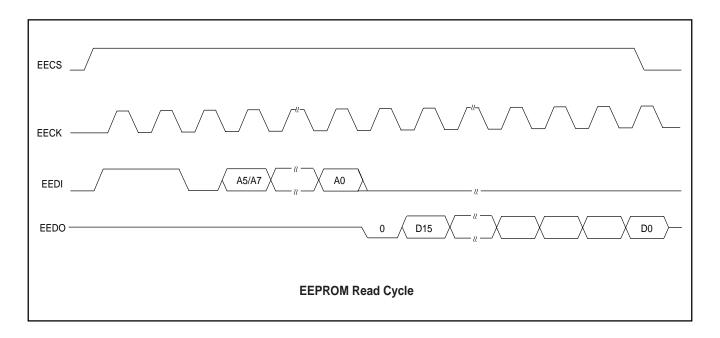

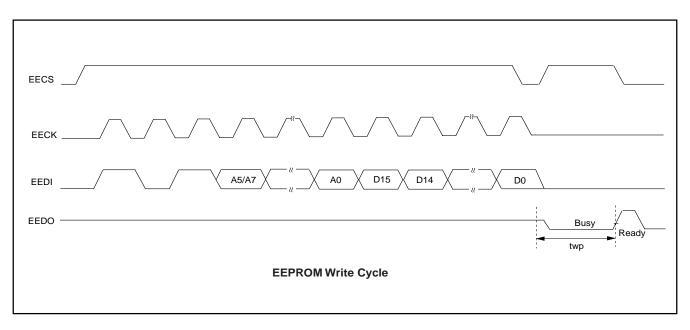

- Optional EEPROM configuration, supports 1K bits and 4K bits EEPROM interface

- Supports software EEPROM interface for easy upgrade of EEPROM contents

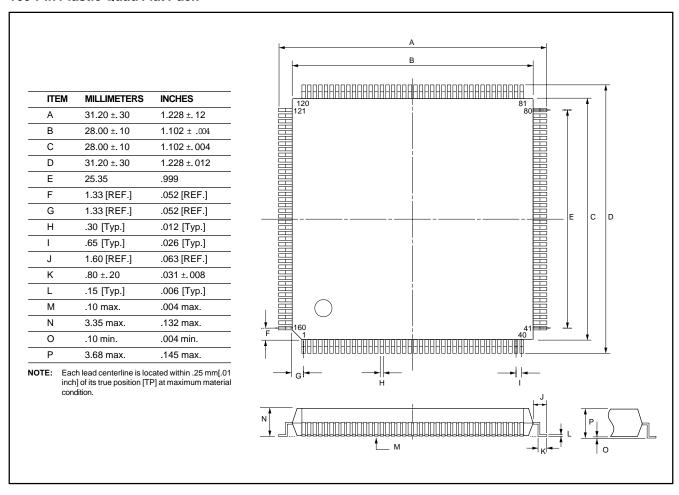

- 5V CMOS in an 160 PQFP package

#### 1.1 Introduction

MX98728EC (GMAC) is a general purpose single chip 10/100 Fast Ethernet controller. With no glue logic or very little extra logic, it can be used in a variety of system applications through its host bus interface. Single chip solution will help reduce system cost, not only on the IC count but also on the board size. Full NWAY function with 10/100 transceiver will ease the field installation. Simply plug the chip in and it will connect itself with the best protocol available.

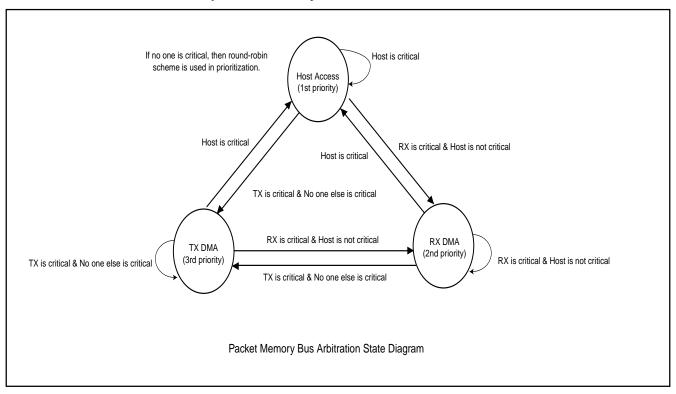

A data cache is also used on the host bus to deliver the 32 /16 bits burst read on the host data port up to 4 data transfers in a single cycle. Two hand shake signals to communicate to the host bus interface during the data port transfer are simple and fast for the system integrator. An intelligent built-in SRAM bus arbiter will manage all SRAM access requests from the host bus access, the transmit local DMA and the receive local DMA.

The 16/8 bit SRAM interface with local DMAs help system developers to optimize the performance. The behavior of these local DMAs can be easily adjusted by the optional bits on the chip. (The term "packet buffer" and "packet memory" are used interchangeably in this document).

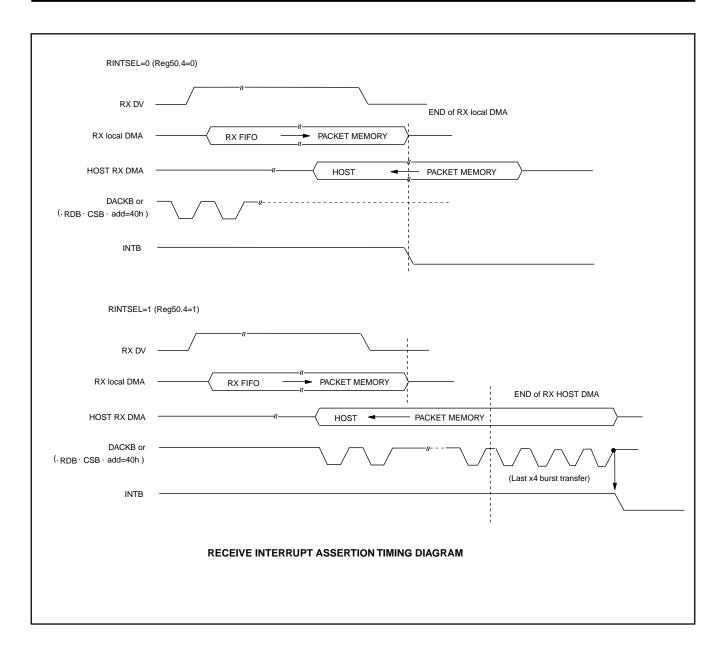

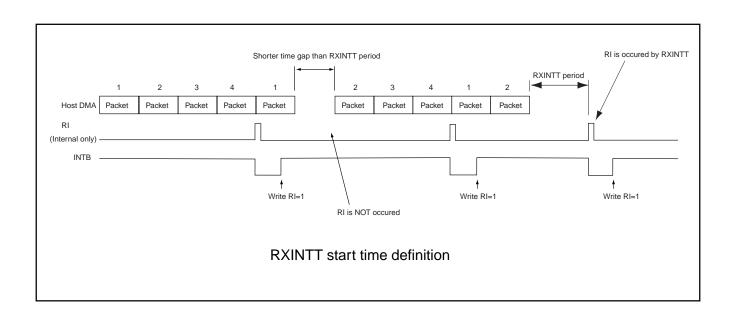

A programmable receive packet interrupt scheme using a timer (RXINTT) and a packet counter (RXINTC) allows system developers to adjust the interrupt traffic. The receive interrupt assertion timing is also programmable for different system applications. A general purpose host receive packet counter (HRPKTCNT) is also provided to the host for the buffer management purpose.

Bus integrity check feature allows the system to recover from a bus hang or an excessively long bus access. BICT (Bus integrity check timer) can be programmed to abort any bus access that runs abnormally long. Based multicast and broadcast frame filtering is supported to minimize the unnecessary network traffic.

MX98728EC is also equipped with the back-to-back transmit capability which allows the software to fire as many transmit packets as needed in a single command. The receive FIFO also allows the back-to-back reception. Optional EEPROM can be used to store the MAC ID and the other configuration information. All options including MAC ID can be programmed through the host interface.

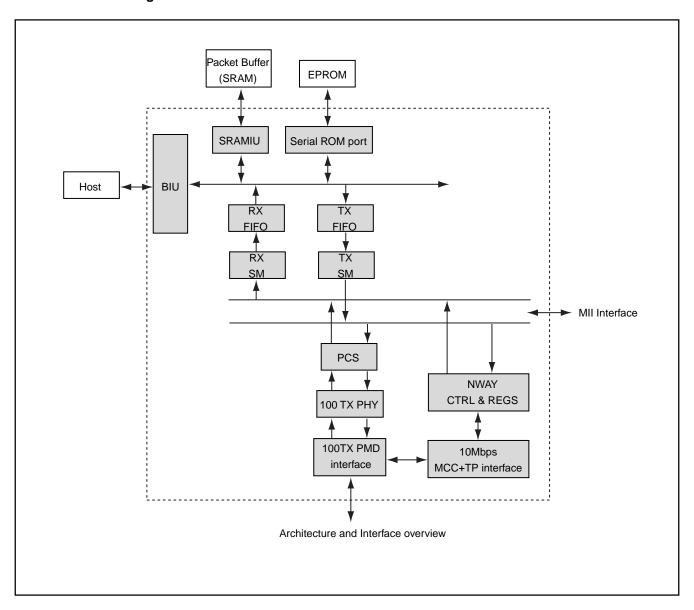

## 1.2 Internal Block Diagram

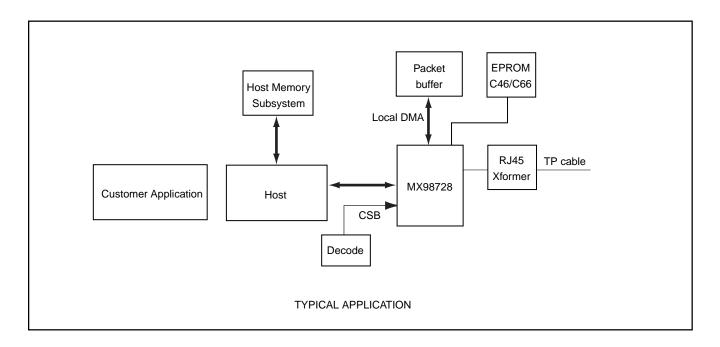

## 1.3 Typical Application

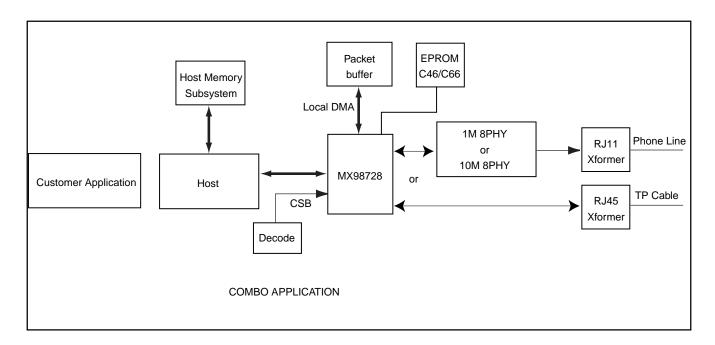

#### 1.4 Combo Application

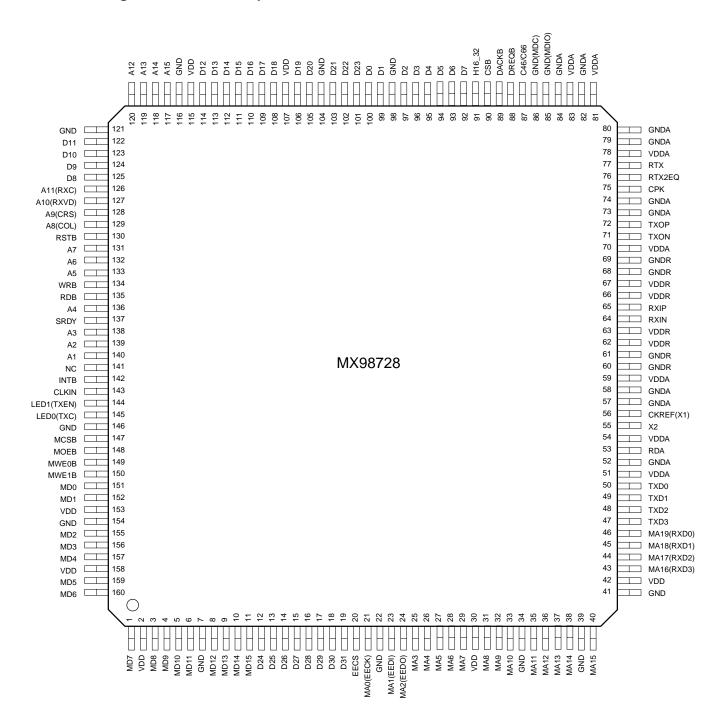

#### 2.0 Pin Configuration and Description:

# 2.1 Pin Description: ( all internal pull-up is 168K ohm, pull-down is 70K ohm )

#### **Host Bus Interface**

| PIN#        | Pin Name  | Туре     | Description                                                                                                                                                                                                                                                                                             |

|-------------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 143         | CLKIN     | I, TTL   | Not used, NC pin.                                                                                                                                                                                                                                                                                       |

| 19-12,      | D[31:0]   | I/O, 4ma | Host Data Bit [31:0]:                                                                                                                                                                                                                                                                                   |

| 101-103,    |           |          |                                                                                                                                                                                                                                                                                                         |

| 105-106,    |           |          |                                                                                                                                                                                                                                                                                                         |

| 108-114,    |           |          |                                                                                                                                                                                                                                                                                                         |

| 122-125,    |           |          |                                                                                                                                                                                                                                                                                                         |

| 92-97,      |           |          |                                                                                                                                                                                                                                                                                                         |

| 99, 100     |           |          |                                                                                                                                                                                                                                                                                                         |

| 117-120,    | A[15:1]   | I, 4ma   | Host Bus Address Bit [15:1]: In 32 bit mode, H16_32=0                                                                                                                                                                                                                                                   |

| 126-129,    |           |          | all host accesses are 32 bit wide. When H16_32=1, all                                                                                                                                                                                                                                                   |

| 131-133,    |           |          | host accesses are 16 bit wide. (Internal pull-up).                                                                                                                                                                                                                                                      |

| 136,138-140 |           |          | A11, A10, A9, A8 has other definition in MII mode.                                                                                                                                                                                                                                                      |

| 126         | A11(RXC)  | I, TTL   | Host Bus Address Bit11, when on-chip tranceiver is used it is used in A[15:1], when in MII mode, it is defined as receive clock RXC (25MHz or 2.5MHz) When this pin is used as address bit, it is internally grounded until Reg50.6 (A11A8EN bit) is set to enable decoding of this pin as address bit. |

| 127         | A10(RXDV) | I,TTL    | Host Bus Address Bit10, when on-chip tranceiver is used, it is used in A[15:1], when in MII mode, it is defined as receive data valid RXDV signal. When this pin is used as address bit, it is internally grounded until Reg50.6 (A11A8EN bit) is set to enable decoding of this pin as address bit.    |

| 128         | A9(CRS)   | I,TTL    | Host Bus Address Bit9, when on-chip tranceiver is used, it is used in A[15:1], when in MII mode, it is defined as carrier same CRS signal. When this pin is used as address bit, it is internally grounded until Reg50.6 (A11A8EN bit) is set to enable decoding of this pin as address bit.            |

| 129         | A8(COL)   | I,TTL    | Host Bus Address Bit8, when on-chip tranceiver is used it is used in A[15:1], when in MII mode, it is defined as collision COL signal. When this pin is used as address bit, it is internally grounded until Reg50.6 (A11A8EN bit) is set to enable decoding of this pin as address bit.                |

| 141         | NC        |          | NC pin : Not connected.                                                                                                                                                                                                                                                                                 |

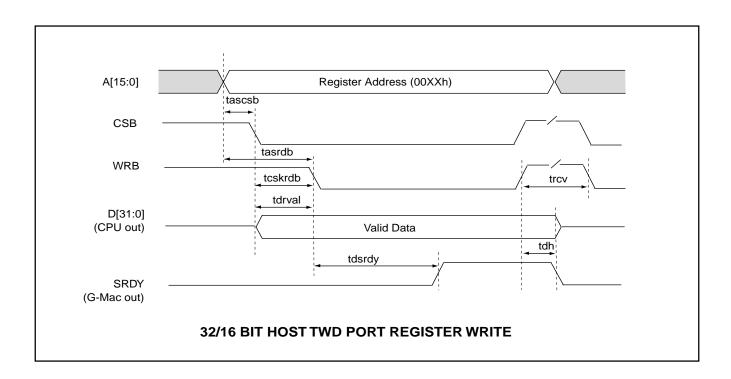

| 137         | SRDY      | O, 4ma   | Synchronous Ready: Active high for the write cycle to indicate the data is secured and the cycle can be finished.                                                                                                                                                                                       |

| 135 | RDB    | I, TTL   | Host Bus Read Indicator : Active low. (Internal pull-up)     |

|-----|--------|----------|--------------------------------------------------------------|

| 134 | WRB    | I, TTL   | Host Bus Write Indicator : Active low. (Internal pull-up)    |

| 142 | INTB   | O/D, 4ma | Host Bus Interrupt Output : Active low.                      |

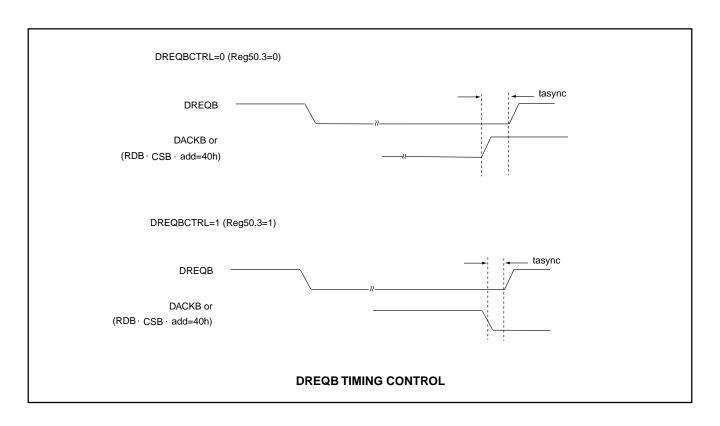

| 88  | DREQB  | O, 4ma   | DMA Burst Read Request : Active low to request a burst       |

|     |        |          | read transfer.                                               |

| 89  | DACKB  | I, TTL   | DMA Read Acknowledge : Active low during the burst           |

|     |        |          | read cycle.                                                  |

| 130 | RSTB   | I,TTL    | Host Bus Reset Input: Active low. (Schmidt trigger input,    |

|     |        |          | Internal pull-up) Input delay is typically 7ns, minimum      |

|     |        |          | RSTB pulse width must be 5 Tclk, Tclk=1/50MHz.               |

| 90  | CSB    | I,TTL    | Host Bus Chip Select Input: Active low to enable access      |

|     |        |          | to GMAC, set to disable access to GMAC. But the net-         |

|     |        |          | work activity is independent of this signal. (Internal pull- |

|     |        |          | down)                                                        |

| 91  | H16_32 | I,TTL    | Host Bus Width 16 bit / 32 bit select : Set for the 16 bit   |

|     |        |          | host bus, reset for the 32 bit host bus.                     |

# **Packet Memory Interface**

| PIN#   | Pin Name   | Type     | Description                                                     |

|--------|------------|----------|-----------------------------------------------------------------|

| 46-43, | MA[19:3]   | O,4ma    | Memory Address Bits 19-3:                                       |

| 40,    |            |          |                                                                 |

| 38-35, |            |          |                                                                 |

| 33-31, |            |          |                                                                 |

| 29-25  |            |          |                                                                 |

| 46     | MA19(RXD0) | I/O, 4ma | Memory Address Bit19, when on-chip tranceiver is used,          |

|        |            |          | it is defined as MA19, while in MII mode, it is used as receive |

|        |            |          | data bit RXD0 pin.                                              |

| 45     | MA18(RXD1) | I/O, 4ma | Memory Address Bit18, when on-chip tranceiver is used,          |

|        |            |          | it is defined as MA18, while in MII mode, it is used as receive |

|        |            |          | data bit RXD1 pin.                                              |

| 44     | MA17(RXD2) | I/O, 4ma | Memory Address Bit17, when on-chip tranceiver is used,          |

|        |            |          | it is defined as MA17, while in MII mode, it is used as receive |

|        |            |          | data bit RXD2 pin.                                              |

| 43     | MA16(RXD3) | I/O, 4ma | Memory Address Bit16, when on-chip tranceiver is used,          |

|        |            |          | it is defined as MA16, while in MII mode, it is used as receive |

|        |            |          | data bit RXD3 pin.                                              |

| 24     | MA2(EEDO)  | I/O,4ma  | Memory Address Bit 2 or EEPROM Data Out bit: Right after the    |

|        |            |          | host reset, GMAC automatically load the configuration informa-  |

|        |            |          | tion from the external EEPROM. During this period, MA2 pin      |

|        |            |          | acts as an EEDO pin that reads in the output data stream from   |

|        |            |          | the EEPROM. After the EEPROM auto load sequence is done,        |

|        |            |          | this pin becomes MA2. Together with MA[19:3], they form the     |

|        |            |          | packet buffer address lines 19 - 0.                             |

| 23        | MA1(EEDI) | I/O,4ma | Memory Address Bit 1 or EEPROM Data In bit: During the              |

|-----------|-----------|---------|---------------------------------------------------------------------|

|           |           |         | EEPROM auto load sequence, the MA1 pin acts as the EEDI             |

|           |           |         | pin that writes the data stream into the EEPROM. After the          |

|           |           |         | EEPROM auto load sequence is done, this pin becomes MA1.            |

|           |           |         | Together with MA[19:2], they form the packet buffer address         |

|           |           |         | lines.                                                              |

| 21        | MA0(EECK) | I/O,4ma | Memory Address Bit 0 or EEPROM Clock Input : During the             |

|           |           |         | EEPROM auto load sequence, MA0 pin acts as the EECK pin             |

|           |           |         | that provides clock to the EEPROM. After the EEPROM autoload        |

|           |           |         | sequence is done, this pin becomes MA0. Together with MA[19:1],     |

|           |           |         | they form the packet buffer address lines. MA0 is don't care        |

|           |           |         | when packet memory is in word mode.                                 |

| 11-8,     | MD[15:0]  | I/O,4ma | Packet Memory Data Bits 15-0: (Internal pull-down)                  |

| 6-3,      |           |         |                                                                     |

| 1,        |           |         |                                                                     |

| 160, 159, |           |         |                                                                     |

| 157-155,  |           |         |                                                                     |

| 152,151   |           |         |                                                                     |

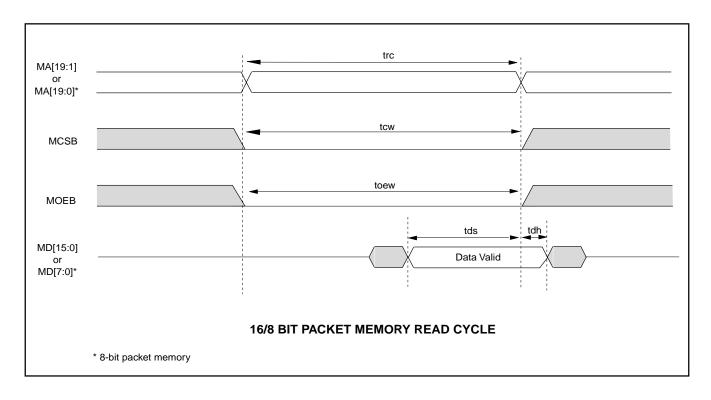

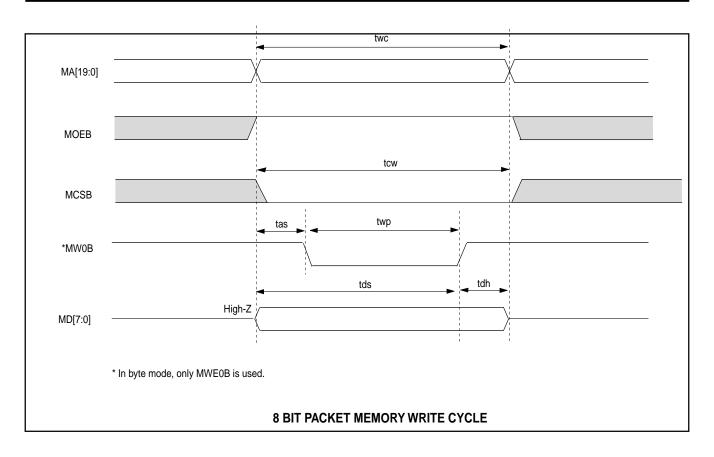

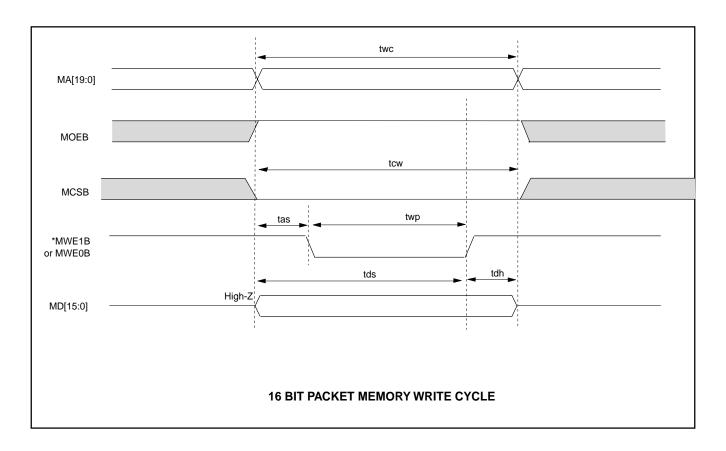

| 148       | MOEB      | O,4ma   | Memory Output Enable: Active low during packet buffer read          |

|           |           |         | accesses.                                                           |

| 147       | MCSB      | O,4ma   | Memory Chip Select: Active low during packet buffer accesses.       |

| 150,149   | MWEB[1:0] | O,4ma   | Byte Write Enable: Active low during the packet buffer write cycle. |

|           |           |         | MWEB1 for the high byte and MWEB0 for the low byte.                 |

#### 10/100 Transceiver interface

| PAD# | Pin Name  | Туре  | Description                                                          |

|------|-----------|-------|----------------------------------------------------------------------|

| 53   | RDA       | 0     | RDA external resistor to ground: 10K ohm, 5%                         |

| 56   | CKREF(X1) | I,TTL | 25Mhz , 30 PPM external osc./crystal input :                         |

| 55   | X2        | 0     | 25Mhz , 30 PPM external crystal output :                             |

| 64   | RXIN      | I     | Twisted pair receive differential input: supports both 10/100 Mbps   |

|      |           |       | speeds.                                                              |

| 65   | RXIP      | I     | Twisted pair receive differential input: supports both 10/100 Mbps   |

|      |           |       | speeds.                                                              |

| 71   | TXON      | 0     | Twisted pair transmit differential output: supports both 10/100 Mbps |

|      |           |       | speeds, 802.3 AOI spec.                                              |

| 72   | TXOP      | 0     | Twisted pair transmit differential output: supports both 10/100 Mbps |

|      |           |       | speeds, 802.3 AOI spec.                                              |

| 75   | CPK       | 0     | NC pin : used in the test mode only.                                 |

| 76   | RTX2EQ    | 0     | RTX2EQ external resistor to ground: 1.4K ohm, 5%                     |

| 77   | RTX       | 0     | RTX external resistor to ground: 560 ohm, 5%                         |

|      |           |       |                                                                      |

#### Miscellaneous

| PIN#  | Pin Name   | Туре     | Description                                                                 |

|-------|------------|----------|-----------------------------------------------------------------------------|

| 20    | EECS       | O,2ma    | EEPROM Chip Select Signal                                                   |

| 87    | C46/C66    | I,TTL    | EEPROM Size Select: 1 for C46, 0 for C66. Default is 1.(Internal pull-      |

|       |            |          | up)                                                                         |

| 145   | LED0(TXC)  | I/O,16ma | LED0 (TXC in MII mode): When on-chip tranceiver is used, it is defined      |

|       |            |          | as SPEED LED. When the light is on, it indicates the 100 Mbps speed.        |

|       |            |          | When off, it indicates the 10 Mbps speed. When both LED0 and LED1           |

|       |            |          | are flashing identically, it means the bus integrity error. (Internal pull- |

|       |            |          | up). When in MII mode, this pin is defined as transmit clock TXC (25        |

|       |            |          | MHz or 2.5 MHz) input.                                                      |

| 144   | LED1(TXEN) | O,16ma   | LED1 (TXEN in MII mode) :When on-chip tranceiver is used, it is de-         |

|       |            |          | fined as Link/Activity LED. When the light is stable and on, it indicates   |

|       |            |          | a good link. When flashing, it indicates TX and RX activities. When off,    |

|       |            |          | it means a bad link. (Internal pull-up). When in MII mode, this pin is      |

|       |            |          | defined as transmit enable TXEN pin.                                        |

| 47-50 | TXD[3:0]   | O, 4ma   | MII Test port TXD[3:0]: Used only in the test mode as part of the MII       |

|       |            |          | interface. (Internal pull-down)                                             |

#### **VDD/GND Pins**

| PIN#                  | Pin Name  | Туре     | Description                                              |

|-----------------------|-----------|----------|----------------------------------------------------------|

| 51,54,59,70,78,81,83  | VDDA      |          | Analog Vdd Pins : Must be carefully isolated in the      |

|                       |           |          | separated Vdd plane.                                     |

| 52,57,58,73,74,79,80, | GNDA      |          | Analog Ground Pins: Must be carefully isolated in the    |

| 82,84                 |           |          | seperated GND plane.                                     |

| 62,63,66,67           | VDDR      |          | RX Vdd Pins: Must be carefully isolated in the separated |

|                       |           |          | Vdd plane.                                               |

| 60,61,68,69           | GNDR      |          | RX Ground Pins : Must be carefully isolated in the       |

|                       |           |          | separated ground plane.                                  |

| 42,30,2,153,115,107   | VDD       |          | Digital Vdd Pins : Must be carefully isolated in the     |

| 158                   |           |          | separated Vdd plane.                                     |

| 41,39,34,22,7,154,    | GND       |          | Digital Ground Pins : Must be carefully isolated in the  |

| 146,121,116,104,98,   |           |          | separated ground plane.                                  |

| 85                    | GND(MDIO) | I/O, 4ma | Normally grounded when on-chip tranceiver is used, while |

|                       |           |          | in MII mode, it is defined as MDIO pin.                  |

| 86                    | GND(MDC)  | I/O, 4ma | Normally grounded when on-chip tranceiver is used, while |

|                       |           |          | in MII mode, it is defined as MDC clock pin.             |

|                       |           |          |                                                          |

## 3.0 Register (Default value is defined after the hardware/power-up reset)

Reset logic: All register bits are cleared by the hardware reset, while the register bit with an "\*" in its symbol name is also cleared by the software reset.

#### Network Control Register A: NCRA (Reg0h), R/W, default=00h

| Bit       |                  | Description                                                                                                                                                                         |                                           |               |                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0.0       | Symbol<br>RESET  |                                                                                                                                                                                     | cot Δf                                    | fter h        | ardware reset this bit is 0 meaning normal operation. To                                                                                                                                                                                                                                                   |  |  |  |

| 0.0 KLOLI | KLOLI            | Reset: Software reset. After hardware reset, this bit is 0 meaning normal operation. To reset GMAC by software, software must write a 1 to this bit first, then followed by writing |                                           |               |                                                                                                                                                                                                                                                                                                            |  |  |  |

|           |                  | •                                                                                                                                                                                   |                                           |               | •                                                                                                                                                                                                                                                                                                          |  |  |  |

| 0.4       | CT0*             |                                                                                                                                                                                     |                                           |               | to this bit, GMAC starts normal operation.                                                                                                                                                                                                                                                                 |  |  |  |

| 0.1       | ST0*             |                                                                                                                                                                                     |                                           | /Stati        | us: Write to issue commands. When done, both bits are                                                                                                                                                                                                                                                      |  |  |  |

| 0.2       | ST1*             | cleared automatical                                                                                                                                                                 | ly.                                       |               |                                                                                                                                                                                                                                                                                                            |  |  |  |

|           |                  | Transmit command : ST1 ST0                                                                                                                                                          |                                           |               |                                                                                                                                                                                                                                                                                                            |  |  |  |

|           |                  | IDLE state                                                                                                                                                                          | 0                                         | 0             | Read to indicate TX DMA idle state, write has no effect.                                                                                                                                                                                                                                                   |  |  |  |

|           |                  | TX DMA Poll                                                                                                                                                                         | 0                                         | 1             | Start TX DMA, send packets stored in packet memory.                                                                                                                                                                                                                                                        |  |  |  |

|           |                  | TX FIFO Send                                                                                                                                                                        | 1                                         | 0             | Immediately send the packet stored in the TX FIFO.                                                                                                                                                                                                                                                         |  |  |  |

|           |                  | TX DMA Poll                                                                                                                                                                         | 1                                         | 1             | Start TX DMA, send packets stored in packet memory.                                                                                                                                                                                                                                                        |  |  |  |

|           |                  |                                                                                                                                                                                     |                                           | •             | and the TX FIFO Send can not be used at the same time.<br>he FIFO directly only when ST1, ST0=IDLE and                                                                                                                                                                                                     |  |  |  |

|           |                  |                                                                                                                                                                                     |                                           |               | poll and the TX FIFO Send commands can be issued only<br>DMA[3:0]=1h, regardless of any error status in previous                                                                                                                                                                                           |  |  |  |

| 0.3       | SR*              | when ST1, ST0=IDI transmission.                                                                                                                                                     | LE and                                    | d TXI         | •                                                                                                                                                                                                                                                                                                          |  |  |  |

|           | SR*<br>LB0*,LB1* | when ST1, ST0=IDI transmission.                                                                                                                                                     | LE and                                    | d TXI<br>e MA | DMA[3:0]=1h, regardless of any error status in previous                                                                                                                                                                                                                                                    |  |  |  |

|           |                  | when ST1, ST0=IDI transmission. Start Receive : Ena                                                                                                                                 | LE and                                    | d TXI         | DMA[3:0]=1h, regardless of any error status in previous  C to receive packets. Default is disabled.                                                                                                                                                                                                        |  |  |  |

|           |                  | when ST1, ST0=IDI<br>transmission.<br>Start Receive : Ena<br>Loop Back Mode:                                                                                                        | LE and<br>ble the<br>LB1                  | e MA          | DMA[3:0]=1h, regardless of any error status in previous  C to receive packets. Default is disabled.  LB0                                                                                                                                                                                                   |  |  |  |

|           |                  | when ST1, ST0=IDI<br>transmission.  Start Receive: Ena<br>Loop Back Mode:<br>Mode0                                                                                                  | ble the                                   | e MA          | DMA[3:0]=1h, regardless of any error status in previous  C to receive packets. Default is disabled.  LB0  Normal mode                                                                                                                                                                                      |  |  |  |

| 0.3       |                  | when ST1, ST0=IDI<br>transmission.  Start Receive : Ena Loop Back Mode: Mode0 Mode1                                                                                                 | ble the                                   | e MA          | DMA[3:0]=1h, regardless of any error status in previous  C to receive packets. Default is disabled.  LB0  Normal mode  Internal FIFO Loopback                                                                                                                                                              |  |  |  |

|           |                  | when ST1, ST0=IDI<br>transmission.  Start Receive: Ena<br>Loop Back Mode:<br>Mode0<br>Mode1<br>Mode2<br>Mode3                                                                       | ble the LB1 0 0 1 1                       | e MA          | DMA[3:0]=1h, regardless of any error status in previous  C to receive packets. Default is disabled.  LB0  Normal mode  Internal FIFO Loopback  Internal NWAY Loopback                                                                                                                                      |  |  |  |

|           |                  | when ST1, ST0=IDI transmission. Start Receive : Ena Loop Back Mode: Mode0 Mode1 Mode2 Mode3  Mode 2 and 3 are re                                                                    | ble the                                   | e MA          | DMA[3:0]=1h, regardless of any error status in previous  C to receive packets. Default is disabled.  LB0  Normal mode  Internal FIFO Loopback  Internal NWAY Loopback  Internal PMD Loopback  the IC test purpose. Only mode 1 can be used on the                                                          |  |  |  |

|           |                  | when ST1, ST0=IDI transmission.  Start Receive: Ena Loop Back Mode: Mode0 Mode1 Mode2 Mode3  Mode 2 and 3 are re bench. External loop                                               | ble the LB1 0 0 1 1 1 esserve oback       | e MA          | DMA[3:0]=1h, regardless of any error status in previous  C to receive packets. Default is disabled.  LB0  Normal mode  Internal FIFO Loopback  Internal NWAY Loopback  Internal PMD Loopback                                                                                                               |  |  |  |

|           |                  | when ST1, ST0=IDI transmission.  Start Receive: Ena Loop Back Mode: Mode0 Mode1 Mode2 Mode3  Mode 2 and 3 are rebench. External loop the real cable hooke                           | ble the LB1 0 0 1 1 1 esserve oback ed up | e MA          | DMA[3:0]=1h, regardless of any error status in previous  C to receive packets. Default is disabled.  LB0  Normal mode  Internal FIFO Loopback  Internal NWAY Loopback  Internal PMD Loopback  the IC test purpose. Only mode 1 can be used on the ne bench can be done by the full duplex normal mode with |  |  |  |

# Network Control Register B: NCRB (Reg1h),R/W, default=01h

| Bit   | Symbol       | Description                                                                          | า                 |                                                                |  |  |

|-------|--------------|--------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------|--|--|

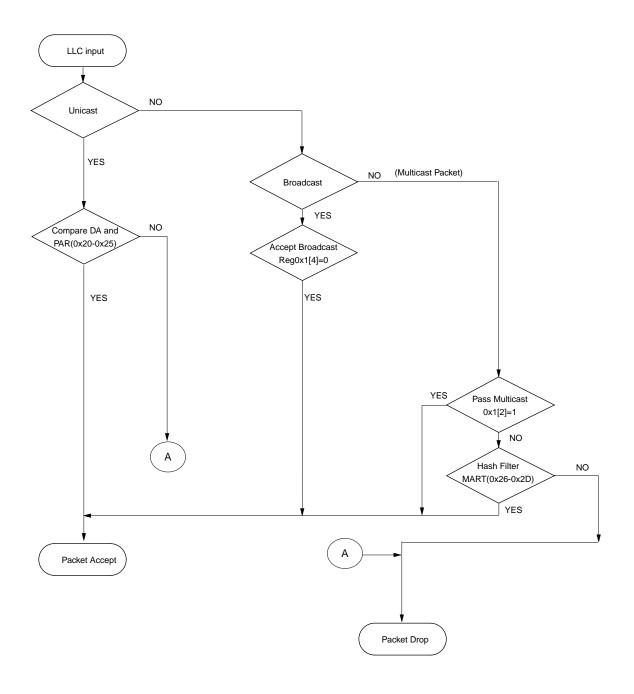

| 1.0   | PR*          | Promiscuous mode: Set to receive any incoming valid frames received, regardless of   |                   |                                                                |  |  |

|       |              | its destina                                                                          | tion address. D   | efault is set.                                                 |  |  |

| 1.1   | CA*          | CApture E                                                                            | ffect Mode: Set   | to enable an enhanced pick-off algorithm to avoid the net-     |  |  |

|       |              | work captu                                                                           | ure effect.       |                                                                |  |  |

| 1.2   | PM*          | Pass Mult                                                                            | cast: Set to ac   | cept all multicast packets (not including the broadcast ad-    |  |  |

|       |              | dress). De                                                                           | efault is reset w | hich directs all multicast address to hash table for further   |  |  |

|       |              | filtering .                                                                          |                   |                                                                |  |  |

| 1.3   | PB*          | Pass Bad                                                                             | Frame: Set to er  | able GMAC to accept Runt frames defined by register 50.2       |  |  |

|       |              | ( RUNTSI                                                                             | ZE). Default is   | reset. When PB=1, runt frame is accepted reguardless of        |  |  |

|       |              | Reg32.3 (A                                                                           | ARXERRB).         |                                                                |  |  |

| 1.4   | AB*          | Accept Bro                                                                           | padcast: Defaul   | is reset which yields control of all the broadcast addresses   |  |  |

|       |              | to the che                                                                           | ck logic defined  | by register 32h bit 7, register 38h and 39h. Set to accept all |  |  |

|       |              | broadcast                                                                            | packets withou    | t any further address filtering.                               |  |  |

| 1.5   | HBD*         | Reserved                                                                             | for test purpose  | e. Default is 0.                                               |  |  |

| 1.7-6 | RXINTC[1:0]* | Receive Interrupt Counter: Receive interrupt RI or REI assertion depends on the num- |                   |                                                                |  |  |

|       |              | ber of pacl                                                                          | kets received de  | fined by these two bits or the RXINTT timer ( $Reg.15/14h$ )   |  |  |

|       |              | timeout, w                                                                           | hichever comes    | s first.                                                       |  |  |

|       |              | Default is                                                                           | 00h after reset.  | meaning the normal receive interrupt operation which as-       |  |  |

|       |              |                                                                                      |                   | gle packet is received and no RXINTT timer is used. Non-       |  |  |

|       |              |                                                                                      |                   | s will enable this special receive interrupt operation.        |  |  |

|       |              |                                                                                      | RXINTC0           | Interrupt received packet count                                |  |  |

|       |              | 0                                                                                    | 0                 | 1 (default)                                                    |  |  |

|       |              | 0                                                                                    | 1                 | 2                                                              |  |  |

|       |              | 1                                                                                    | 0                 | 4                                                              |  |  |

|       |              | 1                                                                                    | 1                 | 8                                                              |  |  |

# GMACTest Register A:TRA (Reg02h),R/W, default=00h

| Bit     | Symbol     | Description                                                                                |

|---------|------------|--------------------------------------------------------------------------------------------|

| 2.0     | TEST       | Test mode enable: Set to enable test modes defined by TMODE[2:0]. Default is reset         |

|         |            | for the normal operation,                                                                  |

| 2.1-2.3 | TMODE[2:0] | Test Mode Select bits[2:0]: Reserved for GMAC's internal tests, only meaningful when       |

|         |            | the TEST bit is set, except when TMODE [2:0] = "110" which is also used as normal          |

|         |            | mode with EEPROM interface disabled. When TMODE [2:0] = "110" & Test =0, then              |

|         |            | MA19~MA16 are still SRAM address bit19~16, while Test = 1, MA19~MA16 are de-               |

|         |            | fined as test pins reserved for debug purpose.                                             |

| 2.4     | RWR        | Receive Watchdog Release: When set, the receive watchdog is released 40 to 48 bit          |

|         |            | times from the last carrier deassertion. When reset, the receive watchdog is released      |

|         |            | 16 to 24 bits times from the last carrier deassertion.                                     |

| 2.5     | RWD        | Receive Watchdog Disable: When set, the receive watchdog is disabled. When reset,          |

|         |            | receive carriers longer than 2560 bytes are guaranteed to cause the watchdog time-         |

|         |            | out. Packets shorted than 2048 bytes are guaranteed to pass.                               |

| 2.6     | FC         | Forced Collision : Set to force collision at every transmit packet. This bit works only    |

|         |            | in the internal FIFO loopback mode, i.e. LB0=1, LB1=0, to test the excessive colli-        |

|         |            | sion. Default is reset.                                                                    |

| 2.7     | SB         | Start/Stop Back-off counter: When set, indicates the internal back-off counter stops       |

|         |            | counting when any carrier is detected. The counter resumes when the carrier drops.         |

|         |            | When reset, the internal back-off counter is not affected by the carrier activity. Default |

|         |            | is reset.                                                                                  |

# GMACTest Register B:TRB (Reg03h),R/W, default=00h

| Bit | Symbol           | Description                                                             |

|-----|------------------|-------------------------------------------------------------------------|

| 3.0 | FKD*             | Flaky Oscillator Disable: When set, indicates that the internal flaky   |

|     |                  | oscillator is disabled. Pseudo random numbers are chosen instead of     |

|     |                  | fully random numbers, used for the internal diagnostic purpose. Set to  |

|     |                  | disable the normal clocking scheme in the timer's test. Reset to enable |

|     |                  | the timer test. Default is reset.                                       |

| 3.1 | RDNCNTCB*        | Reserved for test                                                       |

| 3.2 | RDNCNTSB*        | Reserved for test                                                       |

| 3.3 | COLCNTCB*        | Reserved for test                                                       |

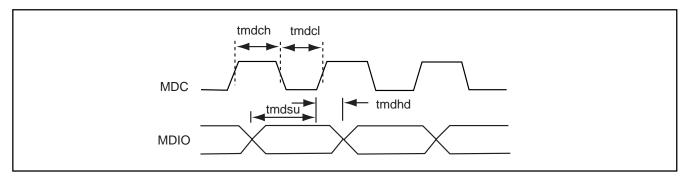

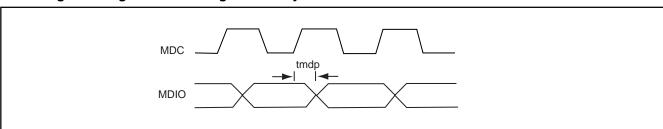

| 3.4 | BFS0*(MDC)       | Normally used as BFS0 pin for test purpose, while in MII mode, it is    |

|     |                  | defined as MII management clock signal (MDC) to be used as a timing     |

|     |                  | reference of MDIO pin.                                                  |

| 3.5 | BKCNTLB*(MDIOEN) | Normally used as BKCNTLB pin for test purpose, while in MII mode, it is |

|     |                  | used to control the direction of MDIO pin. Set MDIOEN = 1 will make     |

|     |                  | MDIO pin as input pin, the value can be read from MDI bit.              |

|     |                  | Set MDIOEN = 0 will make MDIO pin as output pin, the value of MDO bit   |

|     |                  | is driven out to MDIO pin.                                              |

| 3.6 | BFS1*(MDO)     | Normally used as BFS1 pin for test purpose, while in MII mode, it is     |

|-----|----------------|--------------------------------------------------------------------------|

|     |                | used as MII management write data (MDO) for MDIO pin's output data.      |

| 3.7 | BFSTATUS*(MDI) | Normally used as BFSTATUS pin for test purpose, while in MII mode, it is |

|     |                | used as MII management read data (MDI) for MDIO pin's input data.        |

#### Last Transmitted Packet Status: LTPS (Reg4h), RO, default=00h

| Bit | Symbol   | Description                                                                              |

|-----|----------|------------------------------------------------------------------------------------------|

| 4.0 | CC0*     | Collision Count Bit 0:                                                                   |

| 4.1 | CC1*     | Collision Count Bit 1:                                                                   |

| 4.2 | CC2*     | Collision Count Bit 2:                                                                   |

| 4.3 | CC3*     | Collision Count Bit 3: When CC[3:0] = 1111 and a new collision is detected, it is        |

|     |          | called the excessive collision error which will abort the current packet. The TEI inter- |

|     |          | rupt bit will be set.                                                                    |

| 4.4 | CRSLOST* | Carrier Sense Lost: Set to indicate CRS was lost during the transmission. Default is     |

|     |          | reset for the normal packet transmission.                                                |

| 4.5 | UF*      | TX FIFO Underflow: Set to indicate a underflow problem in the TX FIFO. An FIFOEI         |

|     |          | interrupt is generated for the driver to resolve this problem.                           |

| 4.6 | OWC*     | Out of Window Collision: Set to indicate a collision occurred after 64 bytes of data     |

|     |          | has been transmitted. No retransmission will be issued.                                  |

| 4.7 | TERR*    | Transmit Error: Set to indicate the packet transmitted with error. Reset for the normal  |

|     |          | packet transmission.                                                                     |

|     |          |                                                                                          |

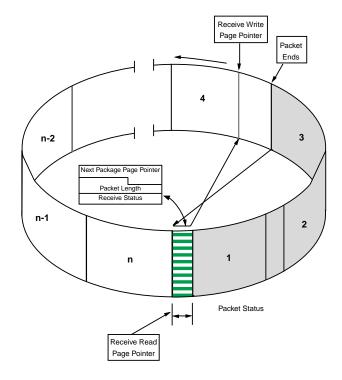

## Last Received Packet Status: LRPS (Reg5h), RO

| Bit | Symbol | Description                                                                               |

|-----|--------|-------------------------------------------------------------------------------------------|

| 5.0 | BF*    | RX Packet Buffer Full Error : 1 indicates the RX packet buffer is full.                   |

| 5.1 | CRC*   | CRC error: The calculation is based on the integer multiple of bytes. Set to indicate the |

|     |        | CRC error for the received packet.                                                        |

| 5.2 | FAE*   | Frame Alignment Error : Set to indicate an extra nibble is received which is not at the   |

|     |        | octet boundary. This error is independent of the CRC detection.                           |

| 5.3 | FO*    | FIFO Overrun: When set, an interrupt is generated. The driver must resolve this error.    |

| 5.4 | RW*    | Receive Watchdog: Set to indicate the frame length exceeds 2048 bytes. An interrupt       |

|     |        | will be generated to the driver.                                                          |

| 5.5 | MF*    | Multicast Frame address: Set to indicate the current frame has the multicast address.     |

| 5.6 | RF*    | Runt Frame : Set to indicate a frame length less than 64 or 60 bytes depending on         |

|     |        | register 50.2 ( RUNTSIZE ), only meaningful when the Reg01h.3 PB bit is set. When         |

|     |        | PB=1, a runt frame will be accepted & RI is set for receive interrupt. When PB=0, a runt  |

|     |        | frame is rejected.                                                                        |

| 5.7 | RERR*  | Receive Error: Set to indicate a packet received with errors including CRC, FAE, FO,      |

|     |        | RW error.                                                                                 |

Notes: This LRPS register contains the same status byte as in the description field of the last received packet in the packet memory.

## Missed Packet Counter: MPCL (Reg07/06h), R/W, default=0000h

| Bit   | Symbol         | Description                                                             |

|-------|----------------|-------------------------------------------------------------------------|

| 6.7-0 | MISSCNT[7:0]*  | Miss Packet Counter Bits [7:0]: Lower byte of the Miss packet counter.  |

| 7.7-0 | MISSCNT[15:8]* | Miss Packet Counter Bits [15:8]: Upper byte of the Miss packet counter. |

## Interrupt Mask Register: IMR (Reg.08h), R/W, default=00h

| Bit | Symbol  | Description                                                                                 |

|-----|---------|---------------------------------------------------------------------------------------------|

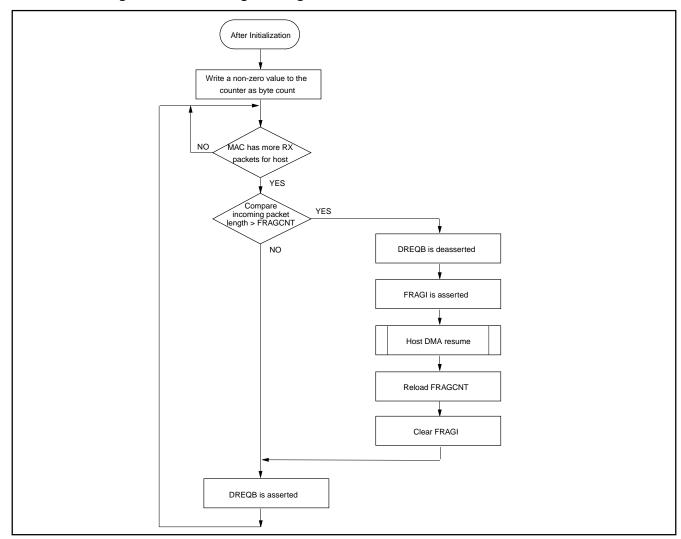

| 8.0 | FRAGIM  | Fragment Counter Interrupt Mask: Set to enable the host DMA Fragment counter (FRAGI)        |

|     |         | interrupt. Default is reset which disable the FRAGI interrupt. When AUTORCVR is set,        |

|     |         | this bit should be reset.                                                                   |

| 8.1 | RIM     | Received Interrupt Mask: Set to enable the Packet Received Interrupt. Default is reset      |

|     |         | which disables the RI interrupt.                                                            |

| 8.2 | TIM     | Transmit Interrupt Mask: Set to enable the Packet transmit OK interrupt. Default is reset   |

|     |         | which disables the TI interrupt.                                                            |

| 8.3 | REIM    | Receive Error Interrupt Mask: Set to enable the Receive Error interrupt. Default is reset   |

|     |         | which disables the REI interrupt.                                                           |

| 8.4 | TEIM    | Transmit Error Interrupt Mask: Set to enable transmit error interrupt. Default is reset     |

|     |         | which disables the TEI interrupt.                                                           |

| 8.5 | FIFOEIM | FIFO Error Interrupt Mask: Set to enable the FIFO Error interrupt. Default is reset which   |

|     |         | disables the FIFOEI interrupt. When AUTORCVR is set, this bit should be reset.              |

| 8.6 | BUSEIM  | Bus Error Interrupt Mask: Set to enable the Bus Error interrupt. Default is reset which     |

|     |         | disables the BUSEI interrupt.                                                               |

| 8.7 | RBFIM   | RX Buffer Full Interrupt Mask: Set to enable the RX Buffer full interrupt. Default is reset |

|     |         | which disables the BFI interrupt.                                                           |

|     |         |                                                                                             |

## Interrupt Register: IR (Reg09h), R/W, default=00h

| Bit | Symbol  | Description                                                                                      |

|-----|---------|--------------------------------------------------------------------------------------------------|

| 9.0 | FRAGI*  | Fragment Counter Interrupt : Set to assert the interrupt when the host DMA Fragment              |

|     |         | Counter is less than current received packet length. Writing 1 to this bit will clear the bit    |

|     |         | and the interrupt. Writing 0 has no effect.                                                      |

| 9.1 | RI*     | Receive OK Interrupt: Set to assert the interrupt. Writing 1 to this bit will clear the bit and  |

|     |         | the interrupt. Writing 0 has no effect. The assertion timing of RI can be programmed             |

|     |         | through the Reg50.4 bit (RINTSEL) for either the completion of the host receive DMA              |

|     |         | activity or the completion of the receive local DMA activity.                                    |

| 9.2 | TI*     | Transmit OK Interrupt: Set to assert the interrupt. Writing 1 to this bit will clear the bit and |

|     |         | the interrupt. Writing 0 has no effect.                                                          |

| 9.3 | REI*    | Receive Error Interrupt: Set to assert the interrupt when the packet is received with error      |

|     |         | . Writing 1 to this bit will clear the bit and the interrupt. Writing 0 has no effect. The       |

|     |         | assertion timing of RI can be programmed through the Reg50.4 bit (RINTSEL) for either            |

|     |         | the completion of the host receive DMA activity or the completion of the receive local           |

|     |         | DMA activity.                                                                                    |

| 9.4 | TEI*    | Transmit Error Interrupt: Set to assert the interrupt when the packet is transmitted with        |

|     |         | error. Writing 1 to this bit will clear the bit and the interrupt. Writing 0 has no effect.      |

| 9.5 | FIFOEI* | FIFO Error Interrupt: Set to assert the interrupt when either the TX FIFO is overrun or the      |

|     |         | RX FIFO is overrun. Writing 1 to this bit will clear the bit and the interrupt. Writing 0 has    |

|     |         | no effect.                                                                                       |

| 9.6 | BUSEI*  | Bus Error Interrupt: Set to assert the interrupt when the Bus integrity check is enabled         |

|     |         | and failed. Writing 1 to this bit will clear the bit and the interrupt. Writing 0 has no effect. |

| 9.7 | RBFI*   | RX Buffer Full Interrupt: Set to assert the interrupt when the RX buffer area is being           |

|     |         | overwritten by new received packets. Writing 1 to this bit will clear the bit and the inter-     |

|     |         | rupt. Writing 0 has no effect.                                                                   |

|     |         |                                                                                                  |

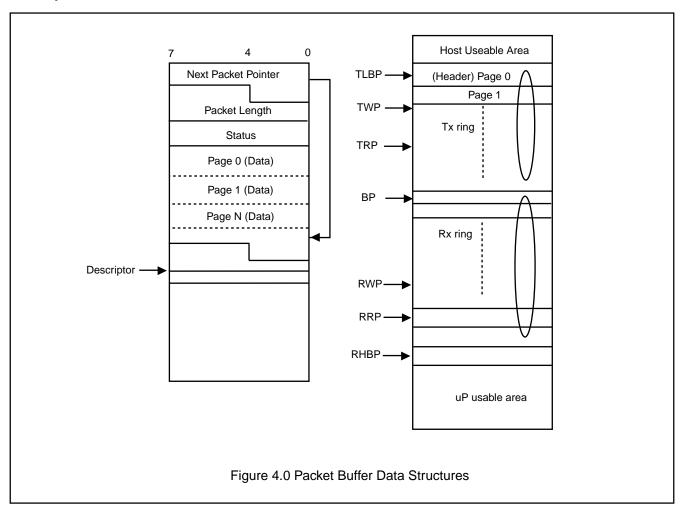

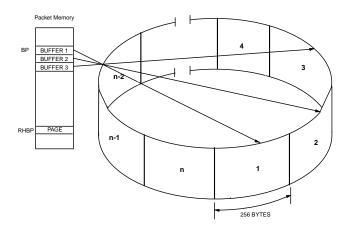

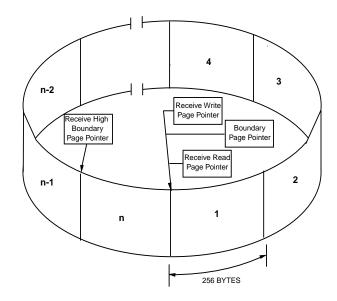

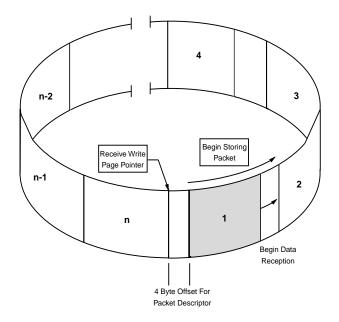

Note: All page pointer bits [11:0] are mapped to MA[19:8] with the same bit ordering.

#### Boundary Page Pointer Register: BP (Reg.0Bh/0Ah), R/W, default=x000h

| Bit     | Symbol   | Description                                                                   |

|---------|----------|-------------------------------------------------------------------------------|

| 0A.7-0, | BP[11:0] | Boundary Page Pointer between the tx/rx buffers: page TLBP[11:0] to page      |

| 0B.3-0  |          | BP[11:0] is the tx buffer. Page BP[11:0] to page RHBP[11:0] is the rx buffer. |

|         |          | BP[11:0] is mapped to MA[19:8]. The MSB is the Reg0BH.3 bit. The LSB is the   |

|         |          | Reg0AH.0 bit.                                                                 |

#### TX Low Boundary Page Pointer Register: TLBP (Reg.0Dh/0Ch), R/W, default=x000h

|      | Symbol Description                                                              |

|------|---------------------------------------------------------------------------------|

| bit. | TLBP [11:0] and BP [11:0]. The MSB is the Reg0Dh.3 bit. The LSB is the Reg0Ch.0 |

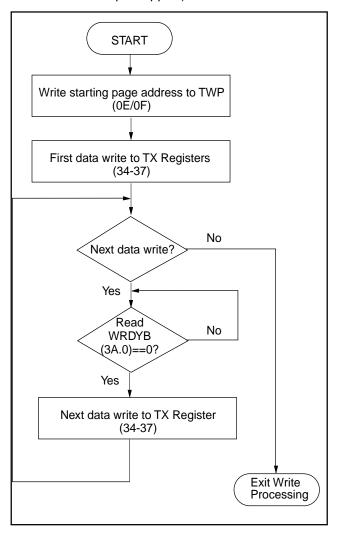

#### Transmit Buffer Write Page Pointer Register: TWP (Reg.0Fh/0Eh), R/W, default=x000h

| Bit     | Symbol    | Description                                                                   |

|---------|-----------|-------------------------------------------------------------------------------|

| 0E.7-0, | TWP[11:0] | Transmit Buffer Write Page Pointer: TWP[11:0] are mapped to MA[19:8] with the |

| 0F.3-0  |           | same bit ordering. The MSB is the Reg0Fh.3 bit. The LSB is the Reg0Eh.0 bit.  |

|         |           | TWP is normally controlled by the device driver. An internal Byte Counter     |

|         |           | (TWPBC) is associated with this page register.                                |

#### Reserved Register: (Reg11h/10h), default=x000h

| Bit      | Symbol | Description |  |

|----------|--------|-------------|--|

| reserved |        | not used    |  |

#### Transmit Buffer Read Page Pointer Register: TRP (Reg.13h/12h), R/W, default=x000h

| Bit     | Symbol    | Description                                                                    |

|---------|-----------|--------------------------------------------------------------------------------|

| 12.7-0, | TRP[11:0] | The Page Index of the Transmit Buffer Read Pointer: Current transmit read page |

| 13.3-0  |           | pointer. The MSB is the Reg13h.3 bit. The LSB is the Reg12h.0 bit. TRP is      |

|         |           | controlled by GMAC only. An internal Byte Counter (TRPBC) is associated with   |

|         |           | this page register.                                                            |

#### Receive Interrupt Timer: RXINTT (Reg15h/14h), R/W, default=0000h

| Bit     | Symbol       | Description                                                                       |

|---------|--------------|-----------------------------------------------------------------------------------|

| 14.7-0, | RXINTT[7:0], | Receive Interrupt Timer: Default is 0000h, meaning no time-out is used on the RI  |

| 15.7-0  | RXINTT[15:8] | or the REI interrupt assertion. Reg15h.7 is the RXINTT.15 bit. Reg14h.0 is        |

|         |              | the RXINTT.0 bit. Any non-zero value enables the time out function if RXINTC[1:0] |

|         |              | (Reg01h.[7:6]) > 0. The time unit of this counter is 40ns per count. The possible |

|         |              | timeout period ranges from 40ns to 2622 us. When the RXINTT times out, if the     |

|         |              | received packet count has not reached the RXINTC [1:0], an interrupt will be      |

|         |              | generated (which is caused by the RXINTT timeout alone). Depending on the         |

|         |              | Reg50.4 bit, RXINTT will start counting after the end of the last receive         |

|         |              | packet of either the host DMA or the RX local DMA. See waveform diagram about     |

|         |              | "RXINTT start time definifion."                                                   |

## Receive Buffer Write Page Pointer Register: RWP (Reg17h/16h), R/W, default=x000h

| Bit     | Symbol    | Description                                                                      |

|---------|-----------|----------------------------------------------------------------------------------|

| 16.7-0, | RWP[11:0] | Receive Buffer Write Page Pointer: Current receive write page pointer. The MSB   |

| 17.3-0  |           | is the Reg17h.3 bit. The LSB is the Reg16h.0 bit. This register is controlled by |

|         |           | GMAC only. An internal Byte Counter (RWPBC) is associated with this page         |

|         |           | register.                                                                        |

## Receive Buffer Read Page Pointer Register: RRP (Reg19h/18h), R/W, default=0000h

| Bit     | Symbol    | Description                                                                      |  |

|---------|-----------|----------------------------------------------------------------------------------|--|

| 18.7-0, | RRP[11:0] | Receive buffer Read Page Pointer: Current receive read page pointer. RRP[11:0]   |  |

| 19.3-0  |           | is mapped to MA[19:8]. The MSB is the Reg19h.3 bit. The LSB is the Reg18h.0      |  |

|         |           | bit. This register is normally controlled by the device driver. An internal Byte |  |

|         |           | Counter (RRPBC) is associated with this page register.                           |  |

#### RX High Boundary Page Pointer Register: RHBP Reg.1Bh/1Ah, R/W, default=x000h

| Bit                                                  | Symbol | Description                                                               |

|------------------------------------------------------|--------|---------------------------------------------------------------------------|

| 1A.7-0. RHBP[11:0] Receive High Boundary Page Pointe |        | Receive High Boundary Page Pointer: The RX packet buffer is defined as    |

| 1B.3-0                                               |        | between RHBP [11:0] and BP[11:0]. The MSB is the Reg1Bh.3 bit. The LSB is |

|                                                      |        | Reg1Ah.0 bit.                                                             |

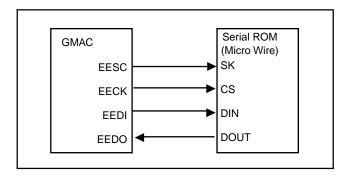

## EEPROM Interface Register: Reg1Ch, R/W, default=00h

| Bit  | Symbol  | Description                                                                      |  |  |  |  |

|------|---------|----------------------------------------------------------------------------------|--|--|--|--|

| 1C.0 | EECS*   | Chip Select output to the external EEPROM clock device                           |  |  |  |  |

| 1C.1 | EECK*   | Serial Clock output to the external EEPROM clock device, <1MHz.                  |  |  |  |  |

| 1C.2 | EEDI*   | Serial Data Input to the external EEPROM clock device                            |  |  |  |  |

| 1C.3 | EEDO*   | Serial Data Output from the external EEPROM clock device                         |  |  |  |  |

| 1C.4 | EESEL*  | Set to enable the external EEPROM write operation(write Select). Default 0 is    |  |  |  |  |

|      |         | read.                                                                            |  |  |  |  |

| 1C.5 | EELD*   | Set to enable reloading the entire contents of the EEPROM just like the power-on |  |  |  |  |

|      |         | reset or the hardware reset. When the loading is done, this bit will be set by   |  |  |  |  |

|      |         | GMAC automatically.                                                              |  |  |  |  |

| 1C.6 | HOLDREQ | Reserved, default = 0.                                                           |  |  |  |  |

|      |         |                                                                                  |  |  |  |  |

| 1C.7 | HLDAACK | Reserved, Read only.                                                             |  |  |  |  |

## Bus Integrity CheckTimer: BICT (Reg1Dh), R/W, default=00h

| Bit    | Symbol     | Description                                                                           |  |  |

|--------|------------|---------------------------------------------------------------------------------------|--|--|

| 1D.7-0 | BICT[7:0]* | Bus Integrity Check Timer: Default is 00h, meaning no bus integrity check             |  |  |

|        |            | enabled. The time unit of this counter is 40ns. Value in this counter other than zero |  |  |

|        |            | will enable the bus integrity check. Any bus cycle longer than the timeout period     |  |  |

|        |            | will cause the "termination of the current bus cycle", which can avoid the abnor-     |  |  |

|        |            | mal bus hang and the bus dead lock. The BUSEI interrupt will be issued. LED0          |  |  |

|        |            | and LED1 will both be flashing identically in 12.5Hz. The possible timeout period     |  |  |

|        |            | ranges from 40ns to a maximum of 10.24us. This counter can be used to warn            |  |  |

|        |            | long cycles so that the driver can tune the local DMA performance.                    |  |  |

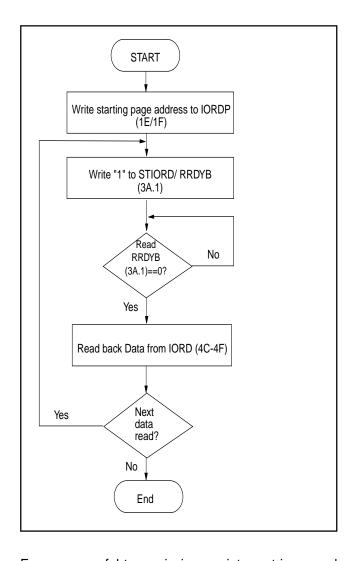

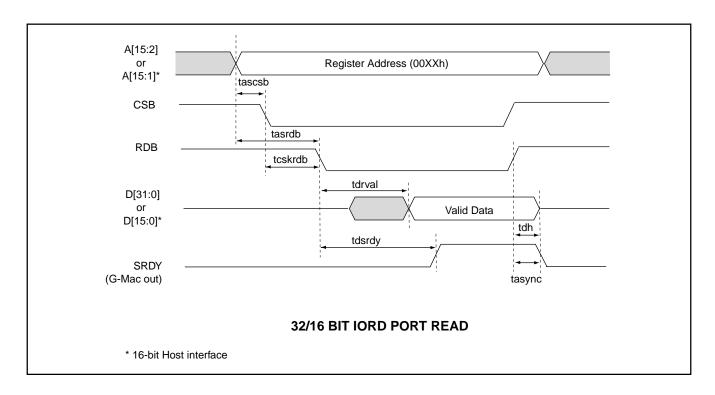

#### IO Data Port Page Pointer Register: IORDP (Reg.1Fh/1Eh), R/E, default=x000h

| Bit     | Symbol      | Description                                                                     |  |

|---------|-------------|---------------------------------------------------------------------------------|--|

| 1E.7-0, | IORDP[11:0] | IO Read Data Port Page Pointer [11:0]: Any read to IORD (Reg4C-4F) will be      |  |

| 1F.3-0  |             | mapped to the packet buffer address which consists of IORDP and the current     |  |

|         |             | content of the internal byte counter (IORDPBC). IORDP can be pointed to any     |  |

|         |             | page within the packet buffer space. IORDP[11:0] are mapped to MA[19:8]         |  |

|         |             | during the data port access. IORDP can be increment automatically when          |  |

|         |             | the current page is exhausted and if AUTOPUB is 0. This page pointer is usually |  |

|         |             | used by the driver to read multiple TX packets status in the packet memory. Bit |  |

|         |             | 3A.1 (STIORD/RRDYB) is with IORDP and IORD if the SRDY pin is not               |  |

|         |             | available on the system application.                                            |  |

## Network Address Filtering Registers: Reg20h~25h (R/W), 26h~2Dh (R/W), default=00h

| Bit      | Symbol | Description                                    |

|----------|--------|------------------------------------------------|

| 20.[7:0] | PAR0   | Physical Address Register Byte 0: PAR [7:0]    |

| 21.[7:0] | PAR1   | Physical Address Register Byte 1: PAR [15:8]   |

| 22.[7:0] | PAR2   | Physical Address Register Byte 2 : PAR [23:16] |

| 23.[7:0] | PAR3   | Physical Address Register Byte 3 : PAR [31:24] |

| 24.[7:0] | PAR4   | Physical Address Register Byte 4: PAR [39:32]  |

| 25.[7:0] | PAR5   | Physical Address Register Byte 5 : PAR [47:40] |

| 26.[7:0] | MAR0   | Hash Table Register Byte 0 : MAR [7:0]         |

| 27.[7:0] | MAR1   | Hash Table Register Byte 1 : MAR [15:8]        |

| 28.[7:0] | MAR2   | Hash Table Register Byte 2: MAR [23:16]        |

| 29.[7:0] | MAR3   | Hash Table Register Byte 3: MAR [31:24]        |

| 2A.[7:0] | MAR4   | Hash Table Register Byte 4: MAR [39:32]        |

| 2B.[7:0] | MAR5   | Hash Table Register Byte 5: MAR [47:40]        |

| 2C.[7:0] | MAR6   | Hash Table Register Byte 6: MAR [56:48]        |

| 2D.[7:0] | MAR7   | Hash Table Register Byte 7 : MAR [63:57]       |

#### Transceiver Control Register: ANALOG (Reg 2Eh), R/W, default=07h

| Bit    | Symbol                                                                        | Description                                                                      |  |  |

|--------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| 2E.0   | DS120                                                                         | Must be 1 for NORMAL mode with auto-compensation.                                |  |  |

| 2E.1   | DS130                                                                         | Must be 1 for NORMAL mode with auto-compensation                                 |  |  |

| 2E.2   | PWD10B                                                                        | Set for NORMAL mode, write 0 followed by write 1 will power down 10 Base-T       |  |  |

|        |                                                                               | analog circuit.                                                                  |  |  |

| 2E.3   | PWD100                                                                        | Reset for NORMAL mode, write 1 followed by write 0 will power down 100 Base-     |  |  |

|        |                                                                               | T analog circuit.                                                                |  |  |

| 2E.4   | RSQ                                                                           | Reduced SQuelch Enable: Set to enable the reduced squelch circuit in the 10      |  |  |

|        |                                                                               | Base-T mode for the receive channel. This can help the reception in a long cable |  |  |

|        |                                                                               | application. Default is reset, meaning the normal CAT-5 cable is used.           |  |  |

| 2E.5   | 2E.5 RST100 Reset for NORMAL mode, write 1 followed by write 0 will reset 100 |                                                                                  |  |  |

|        |                                                                               | circuit.                                                                         |  |  |

| 2E.6-7 | Reserved                                                                      | d must be zero.                                                                  |  |  |

|        |                                                                               |                                                                                  |  |  |

#### DMA Interval Timer: DINTVAL (Reg 2Fh), R/W, default=00h

| Bit    | Symbol  | Description                                                                        |  |

|--------|---------|------------------------------------------------------------------------------------|--|

| 2F.7-0 | DINTVAL | DMA Interval Timer: Used to control the latency between the two consecutive        |  |

|        |         | DMA read burst cycles. Default is all zero, meaning this function is disabled. A   |  |

|        |         | non-zero value tells GMAC to prepare the next host DMA read close to the timer's   |  |

|        |         | expiration. This timer will improve the Host DMA read access priority. The timer's |  |

|        |         | time base is 0.5Mhz, which gives a maximum of 512us.                               |  |

# NWAY Configuration Register: NWAYC (Reg 30h), R/W, default=84h

| Bit      | Symbol   | Description                                                                       |  |  |  |

|----------|----------|-----------------------------------------------------------------------------------|--|--|--|

| 30.0     | FD       | Full Duplex Mode: Set 1 to force the full duplex mode. The default is 0, meaning  |  |  |  |

|          |          | the half duplex mode. This bit is meaningful only if ANE = 0                      |  |  |  |

| 30.1     | PS100/10 | Port Select 100/10 bit: Default is 0, meaning the 10 Base-T mode.                 |  |  |  |

| 30.2     | ANE      | Autonegotiation Enable: Set to enable the NWAY function. Default is set. ANS[2:0] |  |  |  |

|          |          | should be written 001 to restart the autonegotiation sequence after ANE is set.   |  |  |  |

| 30.[5:3] | ANS[2:0] | Autonegotiation status bits: Read only for the NWAY status, except when write     |  |  |  |

|          |          | 001 will restart the autonegotiation sequence. The MSB is the Reg30h.5 bit when   |  |  |  |

|          |          | Nway settles down in one network mode, one bit of Reg31.4~Reg 31.7 will be set    |  |  |  |

|          |          | to indicate the chosen network mode.                                              |  |  |  |

|          |          | Autonegotiation Arbitration State, arbitration states are defined                 |  |  |  |

|          |          | 000 = Autonegotiation disable                                                     |  |  |  |

|          |          | 001 = Transmit disable                                                            |  |  |  |

|          |          | 010 = ability detect                                                              |  |  |  |

|          |          | 011 = Acknowledge detect                                                          |  |  |  |

|          |          | 100 = Complete acknowledge detect                                                 |  |  |  |

|          |          | 101 = FLP link good; autonegotiation complete                                     |  |  |  |

|          |          | 110 = Link check                                                                  |  |  |  |

| 30.6     | NTTEST   | Reserved                                                                          |  |  |  |

| 30.7     | LTE      | Link Test Enable: Default is high, meaning the link check is always enabled.      |  |  |  |

|          |          | Reset forces a good link in the 10 Base-T mode for the testing purpose.           |  |  |  |