### **FLASH MEMORY**

### MT28F321P20 MT28F321P18

Low Voltage, Extended Temperature 0.18µm Process Technology

### **FEATURES**

· Flexible dual-bank architecture

Support for true concurrent operation with zero latency

Read bank a during program bank b and vice versa

Read bank a during erase bank b and vice versa

• Basic configuration:

Seventy-one erasable blocks

Bank *a* (4Mb for data storage)

Bank b (28Mb for program storage)

• Vcc, VccQ, Vpp voltages\*

1.70V (MIN), 1.90V (MAX) Vcc, VccQ (MT28F321P18)

1.80V (MIN), 2.20V (MAX) Vcc, VccQ (MT28F321P20)

0.9V (MIN) VPP (in-system PROGRAM/ERASE)

12V ±5% (HV) VPP tolerant (factory

programming compatibility)

- Random access time: 70ns and 80ns @ 1.80V Vcc\*

- Page Mode read access\*

Eight-word page

Interpage read access: 70ns/80ns @ 1.80V Intrapage read access: 30ns @ 1.80V

• Low power consumption (Vcc = 2.20V) Asynchronous READ < 15mA Standby < 50µA

Automatic power save (APS) feature

- Enhanced write and erase suspend options

ERASE-SUSPEND-to-READ within same bank

PROGRAM-SUSPEND-to-READ within same bank

ERASE-SUSPEND-to-PROGRAM within same bank

- Dual 64-bit chip protection registers for security purposes

- Cross-compatible command support Extended command set Common flash interface

- PROGRAM/ERASE cycle 100,000 WRITE/ERASE cycles per block

- \* Data based on MT28F321P20 device.

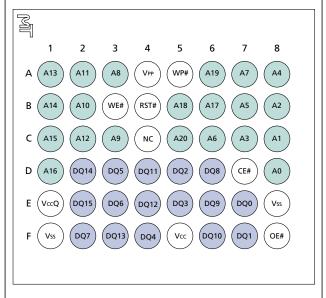

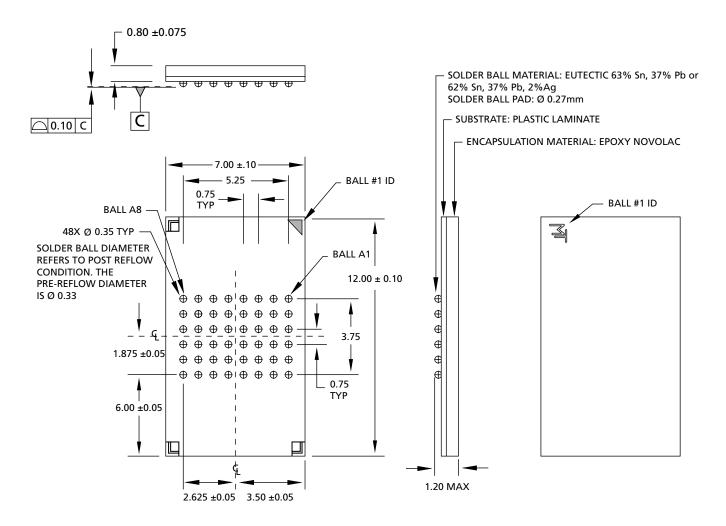

### BALL ASSIGNMENT 48-Ball FBGA

Top View (Ball Down)

**NOTE:** See page 7 for Ball Description Table. See page 33 for mechanical drawing.

### OPTIONS MARKING

| • | Timing                         |     |

|---|--------------------------------|-----|

|   | 70ns access                    | -70 |

|   | 80ns access                    | -80 |

|   | 90ns access                    | -90 |

| • | Boot Block Configuration       |     |

|   | Тор                            | T   |

|   | Bottom                         | В   |

| • | Package                        |     |

|   | 48-ball FBGA (6 x 8 ball grid) | FG  |

| • | Operating Temperature Range    |     |

|   | Extended (-40°C to +85°C)      | ET  |

Part Number Example:

MT28F321P20FG-70 TET

### **GENERAL DESCRIPTION**

The MT28F321P20 and MT28F321P18 are high-performance, high-density, nonvolatile memory solutions that can significantly improve system performance. This new architecture features a two-memory-bank configuration that supports background operation with no latency.

A high-performance bus interface allows a fast page mode, data transfer; a conventional asynchronous bus interface is provided as well.

The devices allow soft protection for blocks, as read only, by configuring soft protection registers with dedicated command sequences. For security purposes, two 64-bit chip protection registers are provided.

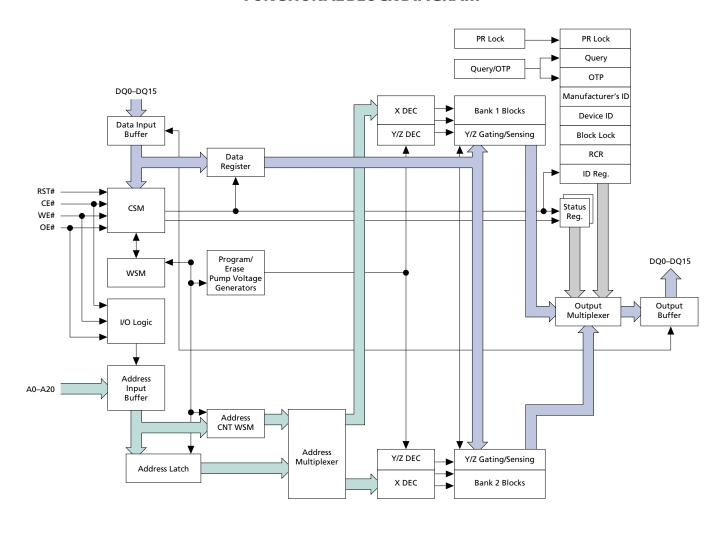

The embedded WORD WRITE and BLOCK ERASE functions are fully automated by an on-chip write state machine (WSM). Two on-chip status registers, one for each of the two memory partitions, can be used to monitor the WSM status and to determine the progress of the program/erase task.

The erase/program suspend functionality allows compatibility with existing EEPROM emulation software packages.

The device is manufactured using 0.18µm process technology.

Please refer to Micron's Web site (<u>www.micron.com/flash</u>) for the latest data sheet.

# ARCHITECTURE AND MEMORY ORGANIZATION

The Flash devices contain two separate banks of memory (bank a and bank b) for simultaneous READ and WRITE operations.

The Flash memory devices are available in the following bank segmentation configuration:

- Bank a comprises one-eighth of the memory and contains 8 x 4K-word parameter blocks; the remainder of bank a is split into 7 x 32Kword blocks.

- Bank b represents seven-eighths of the memory, is equally sectored, and contains 48 x 32K-word blocks.

Figures 2 and 3 show the bottom and top memory organizations.

### **DEVICE MARKING**

Due to the size of the package, Micron's standard part number is not printed on the top of each device. Instead, an abbreviated device mark comprised of a five-digit alphanumeric code is used. The abbreviated device marks are cross referenced to Micron part numbers in Table 1.

Table 1

Cross Reference for Abbreviated Device Marks

| PART NUMBER          | PRODUCT<br>MARKING | SAMPLE<br>MARKING | MECHANICAL<br>SAMPLE MARKING |

|----------------------|--------------------|-------------------|------------------------------|

| MT28F321P20FG-70 BET | FW818              | FX818             | FY818                        |

| MT28F321P20FG-70 TET | FW819              | FX819             | FY819                        |

| MT28F321P20FG-80 BET | FW810              | FX810             | FY810                        |

| MT28F321P20FG-80 TET | FW811              | FX811             | FY811                        |

| MT28F321P18FG-90 BET | FW820              | FX820             | FY820                        |

| MT28F321P18FG-90 TET | FW821              | FX821             | FY821                        |

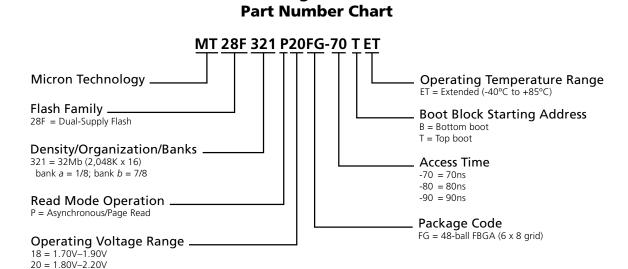

### **PART NUMBERING INFORMATION**

Micron's low-power devices are available with several different combinations of features (see Figure 1).

Valid combinations of features and their corresponding part numbers are listed in Table 2.

Figure 1

Table 2

Valid Part Number Combinations

| PART NUMBER          | ACCESS<br>TIME (ns) | BOOT BLOCK<br>STARTING<br>ADDRESS | OPERATING<br>TEMPERATURE<br>RANGE |

|----------------------|---------------------|-----------------------------------|-----------------------------------|

| MT28F321P20FG-70 BET | 70                  | Bottom                            | -40°C to +85°C                    |

| MT28F321P20FG-70 TET | 70                  | Тор                               | -40°C to +85°C                    |

| MT28F321P20FG-80 BET | 80                  | Bottom                            | -40°C to +85°C                    |

| MT28F321P20FG-80 TET | 80                  | Тор                               | -40°C to +85°C                    |

| MT28F321P18FG-90 BET | 90                  | Bottom                            | -40°C to +85°C                    |

| MT28F321P18FG-90 TET | 90                  | Тор                               | -40°C to +85°C                    |

### **FUNCTIONAL BLOCK DIAGRAM**

### Figure 2 Bottom Boot Block Device

|       | Bank <i>b</i> = 28Mb |                 |  |  |  |

|-------|----------------------|-----------------|--|--|--|

| Block | Block Size           | Address Range   |  |  |  |

|       | (K-bytes/K-words)    | (x16)           |  |  |  |

| 70    | 64/32                | 1F8000h-1FFFFFh |  |  |  |

| 69    | 64/32                | 1F0000h-1F7FFFh |  |  |  |

| 68    | 64/32                | 1E8000h-1EFFFFh |  |  |  |

| 67    | 64/32                | 1E0000h-1E7FFFh |  |  |  |

| 66    | 64/32                | 1D8000h-1DFFFFh |  |  |  |

| 65    | 64/32                | 1D0000h-1D7FFFh |  |  |  |

| 64    | 64/32                | 1C8000h-1CFFFFh |  |  |  |

| 63    | 64/32                | 1C0000h-1C7FFFh |  |  |  |

| 62    | 64/32                | 1B8000h-1BFFFFh |  |  |  |

| 61    | 64/32                | 1B0000h-1B7FFFh |  |  |  |

| 60    | 64/32                | 1A8000h-1AFFFFh |  |  |  |

| 59    | 64/32                | 1A0000h-1A7FFFh |  |  |  |

| 58    | 64/32                | 198000h-19FFFFh |  |  |  |

| 57    | 64/32                | 190000h-197FFFh |  |  |  |

| 56    | 64/32                | 188000h-18FFFFh |  |  |  |

| 55    | 64/32                | 180000h-187FFFh |  |  |  |

| 54    | 64/32                | 178000h-17FFFFh |  |  |  |

| 53    | 64/32                | 170000h-177FFFh |  |  |  |

| 52    | 64/32                | 168000h-16FFFFh |  |  |  |

| 51    | 64/32                | 160000h-167FFFh |  |  |  |

| 50    | 64/32                | 158000h-15FFFFh |  |  |  |

| 49    | 64/32                | 150000h-157FFFh |  |  |  |

| 48    | 64/32                | 148000h-14FFFFh |  |  |  |

| 47    | 64/32                | 140000h-147FFFh |  |  |  |

| 46    | 64/32                | 138000h-13FFFFh |  |  |  |

| 45    | 64/32                | 130000h-137FFFh |  |  |  |

| 44    | 64/32                | 128000h-12FFFFh |  |  |  |

| 43    | 64/32                | 120000h-127FFFh |  |  |  |

| 42    | 64/32                | 118000h-11FFFFh |  |  |  |

| 41    | 64/32                | 110000h-117FFFh |  |  |  |

| 40    | 64/32                | 108000h-10FFFFh |  |  |  |

| 39    | 64/32                | 100000h-107FFFh |  |  |  |

| 38    | 64/32                | 0F8000h-0FFFFFh |  |  |  |

| 37    | 64/32                | 0F0000h-0F7FFFh |  |  |  |

| 36    | 64/32                | 0E8000h-0EFFFFh |  |  |  |

| 35    | 64/32                | 0E0000h-0E7FFFh |  |  |  |

| 34    | 64/32                | 0D8000h-0DFFFFh |  |  |  |

| 33    | 64/32                | 0D0000h-0D7FFh  |  |  |  |

| 32    | 64/32                | 0C8000h-0CFFFFh |  |  |  |

| 31    | 64/32                | 0C0000h-0C7FFFh |  |  |  |

| 30    | 64/32                | 0B8000h-0E7FFFh |  |  |  |

| 29    | 64/32                | +               |  |  |  |

| 29    |                      | 0B0000h-0B7FFFh |  |  |  |

|       | 64/32                | 0A8000h-0AFFFFh |  |  |  |

| 27    | 64/32                | 0A0000h-0A7FFFh |  |  |  |

| 26    | 64/32                | 098000h-097FFFh |  |  |  |

| 25    | 64/32                | 090000h-097FFFh |  |  |  |

| 24    | 64/32                | 088000h-087FFFh |  |  |  |

| 23    | 64/32                | 080000h-087FFFh |  |  |  |

| 22    | 64/32                | 078000h-07FFFh  |  |  |  |

| 21    | 64/32                | 070000h-077FFFh |  |  |  |

| 20    | 64/32                | 068000h-067FFFh |  |  |  |

| 19    | 64/32                | 060000h-067FFFh |  |  |  |

| 18    | 64/32                | 058000h-05FFFh  |  |  |  |

| 17    | 64/32                | 050000h-057FFh  |  |  |  |

| 16    | 64/32                | 048000h-04FFFh  |  |  |  |

| 15    | 64/32                | 040000h-047FFFh |  |  |  |

| Bank <i>a</i> = 4Mb |                                 |                        |  |  |  |

|---------------------|---------------------------------|------------------------|--|--|--|

| Block               | Block Size<br>(K-bytes/K-words) | Address Range<br>(x16) |  |  |  |

| 14                  | 64/32                           | 038000h-03FFFFh        |  |  |  |

| 13                  | 64/32                           | 030000h-037FFFh        |  |  |  |

| 12                  | 64/32                           | 028000h-02FFFFh        |  |  |  |

| 11                  | 64/32                           | 020000h-027FFFh        |  |  |  |

| 10                  | 64/32                           | 018000h-01FFFFh        |  |  |  |

| 9                   | 64/32                           | 010000h-017FFFh        |  |  |  |

| 8                   | 64/32                           | 008000h-00FFFFh        |  |  |  |

| 7                   | 8/4                             | 007000h-007FFFh        |  |  |  |

| 6                   | 8/4                             | 006000h-006FFFh        |  |  |  |

| 5                   | 8/4                             | 005000h-005FFFh        |  |  |  |

| 4                   | 8/4                             | 004000h-004FFFh        |  |  |  |

| 3                   | 8/4                             | 003000h-003FFFh        |  |  |  |

| 2                   | 8/4                             | 002000h-002FFFh        |  |  |  |

| 1                   | 8/4                             | 001000h-001FFFh        |  |  |  |

| 0                   | 8/4                             | 000000h-000FFFh        |  |  |  |

# Figure 3 Top Boot Block Device

|       | Bank <i>a</i> = 4Mb             |                        |  |  |  |  |

|-------|---------------------------------|------------------------|--|--|--|--|

| Block | Block Size<br>(K-bytes/K-words) | Address Range<br>(x16) |  |  |  |  |

| 70    | 8/4                             | 1FF000h-1FFFFFh        |  |  |  |  |

| 69    | 8/4                             | 1FE000h-1FEFFFh        |  |  |  |  |

| 68    | 8/4                             | 1FD000h-1FDFFFh        |  |  |  |  |

| 67    | 8/4                             | 1FC000h-1FCFFFh        |  |  |  |  |

| 66    | 8/4                             | 1FB000h-1FBFFFh        |  |  |  |  |

| 65    | 8/4                             | 1FA000h-1FAFFFh        |  |  |  |  |

| 64    | 8/4                             | 1F9000h-1F9FFFh        |  |  |  |  |

| 63    | 8/4                             | 1F8000h-1F8FFFh        |  |  |  |  |

| 62    | 64/32                           | 1F0000h-1F7FFFh        |  |  |  |  |

| 61    | 64/32                           | 1E8000h-1EFFFFh        |  |  |  |  |

| 60    | 64/32                           | 1E0000h-1E7FFh         |  |  |  |  |

| 59    | 64/32                           | 1D8000h-1DFFFFh        |  |  |  |  |

| 58    | 64/32                           | 1D0000h-1D7FFFh        |  |  |  |  |

| 57    | 64/32                           | 1C8000h-1CFFFFh        |  |  |  |  |

| 56    | 64/32                           | 1C0000h-1C7FFFh        |  |  |  |  |

|         | Bank <i>b</i> = 28Mb |                                    |  |  |

|---------|----------------------|------------------------------------|--|--|

| Block   | Block Size           | Address Range                      |  |  |

|         | (K-bytes/K-words)    | (x16)                              |  |  |

| 55      | 64/32                | 1B8000h-1BFFFFh                    |  |  |

| 54      | 64/32                | 1B0000h-1B7FFFh                    |  |  |

| 53      | 64/32                | 1A8000h-1AFFFFh                    |  |  |

| 52      | 64/32                | 1A0000h-1A7FFFh                    |  |  |

| 51      | 64/32                | 198000h-19FFFFh                    |  |  |

| 50      | 64/32                | 190000h-197FFFh                    |  |  |

| 49      | 64/32                | 188000h-18FFFFh                    |  |  |

| 48      | 64/32                | 180000h-187FFFh                    |  |  |

| 47      | 64/32                | 178000h-17FFFFh                    |  |  |

| 46      | 64/32                | 170000h-177FFFh                    |  |  |

| 45      | 64/32                | 168000h-16FFFFh                    |  |  |

| 44      | 64/32                | 160000h-167FFFh                    |  |  |

| 43      | 64/32                | 158000h-15FFFFh                    |  |  |

| 42      | 64/32                | 150000h-157FFFh                    |  |  |

| 41      | 64/32                | 148000h-14FFFFh                    |  |  |

| 40      | 64/32                | 140000h-147FFFh                    |  |  |

| 39      | 64/32                | 138000h-13FFFFh                    |  |  |

| 38      | 64/32                | 130000h-137FFFh                    |  |  |

| 37      | 64/32                | 128000h-12FFFFh                    |  |  |

| 36      | 64/32                | 120000h-127FFFh                    |  |  |

| 35      | 64/32                | 118000h-11FFFFh                    |  |  |

| 34      | 64/32                | 110000h-117FFFh                    |  |  |

| 33      | 64/32                | 108000h-10FFFFh                    |  |  |

| 32      | 64/32                | 100000h-107FFFh                    |  |  |

| 31      | 64/32                | 0F8000h-0FFFFFh                    |  |  |

| 30      | 64/32                | 0F0000h-0F7FFFh                    |  |  |

| 29      | 64/32                | 0E8000h-0EFFFFh                    |  |  |

| 28      | 64/32                | 0E0000h-0E7FFFh                    |  |  |

| 27      | 64/32                | 0D8000h-0DFFFFh                    |  |  |

| 26      | 64/32                | 0D0000h-0D7FFFh                    |  |  |

| 25      | 64/32                | 0C8000h-0CFFFFh                    |  |  |

| 24      | 64/32                | 0C0000h-0C7FFFh                    |  |  |

| 23      | 64/32                | 0B8000h-0BFFFFh                    |  |  |

| 22      | 64/32                | 0B0000h-0B7FFh                     |  |  |

| 21      | 64/32                | 0A8000h-0AFFFFh                    |  |  |

| 20      | 64/32                | 0A0000h-0A7FFh                     |  |  |

| 19      | 64/32                | 098000h-09FFFFh                    |  |  |

| 18      | 64/32                | 090000h-097FFh                     |  |  |

| 17      | 64/32                | 088000h-08FFFFh                    |  |  |

| 16      | 64/32                | 080000h-087FFFh                    |  |  |

| 15      | 64/32                | 078000h-07FFFFh                    |  |  |

| 14      | 64/32                | 070000h-077FFFh                    |  |  |

| 13      | 64/32                | 068000h-06FFFFh                    |  |  |

| 12      | 64/32                | 060000h-067FFFh                    |  |  |

|         | 64/00                | 0500001 0555551                    |  |  |

| 11      | 64/32                | 058000h-05FFFFh                    |  |  |

| 10<br>9 | 64/32<br>64/32       | 050000h-057FFFh<br>048000h-04FFFFh |  |  |

|         | 64/32                | 040000h-047FFFh                    |  |  |

| 8       |                      |                                    |  |  |

| 7       | 64/32                | 038000h-03FFFFh                    |  |  |

| 6       | 64/32                | 030000h-037FFFh                    |  |  |

| 5       | 64/32                | 028000h-02FFFFh                    |  |  |

| 4       | 64/32                | 020000h-027FFFh                    |  |  |

| 3       | 64/32                | 018000h-01FFFFh                    |  |  |

| 2       | 64/32                | 010000h-017FFh                     |  |  |

| 1       | 64/32                | 008000h-00FFFFh                    |  |  |

| 0       | 64/32                | 000000h-007FFFh                    |  |  |

### **BALL DESCRIPTIONS**

| 48-BALL FBGA<br>NUMBERS                                                                           | SYMBOL   | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D8, C8, B8, C7,<br>A8, B7, C6, A7,<br>A3, C3, B2, A2,<br>C2, A1, B1, C1,<br>D1, B6, B5, A6,<br>C5 | A0-A20   | Input            | Address Inputs: Inputs for the address during READ and WRITE operations. Addresses are internally latched during READ and WRITE cycles.                                                                                                                                                                                                     |

| D7                                                                                                | CE#      | Input            | Chip Enable: Activates the device when LOW. When CE# is HIGH, the device is disabled and goes into standby power mode.                                                                                                                                                                                                                      |

| F8                                                                                                | OE#      | Input            | Output Enable: Enables the output buffer when LOW. When OE# is HIGH, the output buffers are disabled.                                                                                                                                                                                                                                       |

| В3                                                                                                | WE#      | Input            | Write Enable: Determines if a given cycle is a WRITE cycle. If WE# is LOW, the cycle is either a WRITE to the command state machine (CSM) or to the memory array.                                                                                                                                                                           |

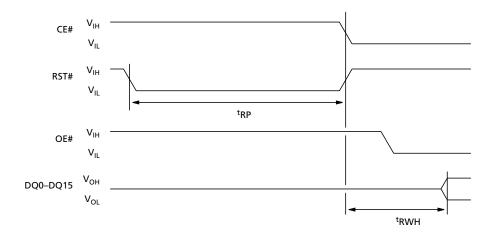

| В4                                                                                                | RST#     | Input            | Reset: When RST# is a logic LOW, the device is in reset mode, which drives the outputs to High-Z and resets the write state machine (WSM). When RST# is at logic HIGH, the device is in standard operation. When RST# transitions from logic LOW to logic HIGH, the device resets all blocks to locked and defaults to the read array mode. |

| A5                                                                                                | WP#      | Input            | Write Protect: Controls the lock down function of the flexible locking feature.                                                                                                                                                                                                                                                             |

| A4                                                                                                | VPP      | Input            | Program/Erase Enable: [0.9V–2.2V or 11.4V–12.6V] Operates as input at logic levels to control complete device protection. Provides factory programming compatibility when driven to 11.4V–12.6V.                                                                                                                                            |

| E7, F7, D5, B5,<br>F4, D3, E3, F2,<br>D6, 36, F6, D4,<br>E4, F3, D2, E2                           | DQ0-DQ15 | Input/<br>Output | Data Inputs/Outputs: Input array data on the second CE# and WE# cycle during PROGRAM command. Input commands to the command user interface when CE# and WE# are active. DQ0–DQ15 output data when CE# and OE# are active.                                                                                                                   |

| E8, F1                                                                                            | Vss      | Supply           | Do not float any ground ball.                                                                                                                                                                                                                                                                                                               |

| F5                                                                                                | Vcc      | Supply           | Device Power Supply: [1.70V–1.90V (MT28F321P18) or 1.80V–2.20V (MT28F321P20)] Supplies power for device operation.                                                                                                                                                                                                                          |

| E1                                                                                                | VccQ     | Supply           | I/O Power Supply: [1.70V–1.90V (MT28F321P18) or 1.80V–2.20V (MT28F321P20)] Supplies power for input/output buffers.                                                                                                                                                                                                                         |

| C4                                                                                                | NC       | _                | Internally not connected.                                                                                                                                                                                                                                                                                                                   |

### **COMMAND STATE MACHINE (CSM)**

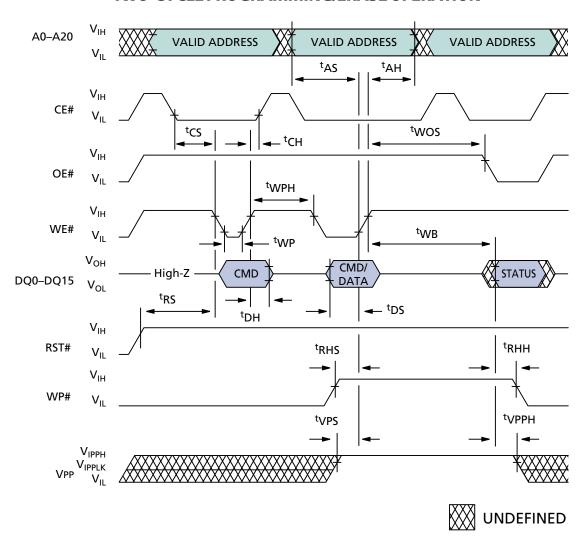

Commands are issued to the command state machine (CSM) using standard microprocessor write timings. The CSM acts as an interface between external microprocessors and the internal WSM. The available commands are listed in Table 3, their definitions are given in Table 4, and their descriptions in Table 5. Program and erase algorithms are automated by an on-chip WSM. For more specific information about the CSM transition states, see Micron technical note TN-28-33, "Command State Machine Description and Command Definition."

Once a valid PROGRAM/ERASE command is entered, the WSM executes the appropriate algorithm, which generates the necessary timing signals to control the device internally and accomplish the requested operation. A command is valid only if the exact sequence of WRITEs is completed. After the WSM completes its task, the WSM status bit (SR7) (see Table 7) is set to a logic HIGH level (1), allowing the CSM to respond to the full command set again.

### **OPERATIONS**

Device operations are selected by entering a standard JEDEC 8-bit command code with conventional microprocessor timings into an on-chip CSM through I/Os DQ0–DQ7. The number of bus cycles required to activate a command is typically one or two. The first operation is always a WRITE. Control signals CE# and WE# must be at a logic LOW level (VIL), and OE# and RST# must be at logic HIGH (VIH). The second operation, when needed, can be a WRITE or a READ depending upon the command. During a READ operation, control signals CE# and OE# must be at a logic LOW

level (V1L), and WE# and RST# must be at logic HIGH (V1H).

Table 6 shows the bus operations for all the modes: write, read, reset, standby, and output disable.

When the device is powered up, internal reset circuitry initializes the chip to a read array mode of operation. Changing the mode of operation requires that a command code be entered into the CSM. For each one of the two memory partitions, an on-chip status register is available. These two registers allow the progress of the various operations that can take place on a memory bank to be monitored. One of the two status registers is interrogated by entering a READ STATUS REGISTER command onto the CSM (cycle 1), specifying an address within the memory partition boundary, and reading the register data on I/Os DQ0–DQ7 (cycle 2). Status register bits SR0-SR7 correspond to DQ0–DQ7 (see Table 7).

### **COMMAND DEFINITION**

Once a specific command code has been entered, the WSM executes an internal algorithm, generating the necessary timing signals to program, erase, and verify data. See Table 4 for the CSM command definitions and data for each of the bus cycles.

### **STATUS REGISTER**

The status register allows the user to determine whether the state of a PROGRAM/ERASE operation is pending or complete. The status register is monitored by toggling OE# and CE#, and reading the resulting status code on I/Os DQ0–DQ7. The high-order I/Os (DQ8–DQ15) are set to 00h internally, so only the low-

Table 3

Command State Machine Codes For Device Mode Selection

| COMMAND DQ0-DQ7 | CODE ON DEVICE MODE                    |

|-----------------|----------------------------------------|

| 40h/10h         | Program setup/alternate program setup  |

| 20h             | Block erase setup                      |

| 50h             | Clear status register                  |

| 60h             | Protection configuration setup         |

| 70h             | Read status register                   |

| 90h             | Read protection configuration register |

| 98h             | Read query                             |

| B0h             | Program/erase suspend                  |

| C0h             | Protection register program/lock       |

| D0h             | Program/erase resume – erase confirm   |

| FFh             | Read array                             |

### 2 MEG x 16 PAGE FLASH MEMORY

order I/Os (DQ0–DQ7) need to be interpreted. Address lines select the status register pertinent to the selected memory partition.

Register data is updated and latched on the falling edge of OE# or CE#, whichever occurs last. Latching the data prevents errors from occurring if the register input changes during a status register read.

The status register provides the internal state of the WSM to the external microprocessor. During periods when the WSM is active, the status register can be polled to determine the WSM status. Table 7 defines the status register bits.

After monitoring the status register during a PROGRAM/ERASE operation, the data appearing on DQ0–DQ7 remains as status register data until a new command is issued to the CSM. To return the device to other modes of operation, a new command must be issued to the CSM.

### **CSM OPERATIONS**

The CSM decodes instructions for read array, read protection configuration register, read query, read status register, clear status register, program, erase, erase suspend, erase resume, program suspend, program resume, lock block, unlock block, and lock down block, chip protection program, and set read configuration register. The 8-bit command code is input to the device on DQ0–DQ7 (see Table 3 for CSM codes and Table 4 for command definitions). During a PROGRAM or ERASE cycle, the CSM informs the WSM that a PROGRAM or ERASE cycle has been requested.

During a PROGRAM cycle, the WSM controls the program sequences and the CSM responds to a PRO-GRAM SUSPEND command only.

During an ERASE cycle, the CSM responds to an ERASE SUSPEND command only. When the WSM has completed its task, the WSM status bit (SR7) is set to a logic HIGH level and the CSM responds to the full com-

## Table 4 Command Definitions

|                                        | FIF       | RST BUS CYC          | LE      | SEC       | OND BUS CY           | CLE               |

|----------------------------------------|-----------|----------------------|---------|-----------|----------------------|-------------------|

| COMMAND                                | OPERATION | ADDRESS <sup>1</sup> | DATA    | OPERATION | ADDRESS <sup>1</sup> | DATA <sup>1</sup> |

| READ ARRAY                             | WRITE     | WA                   | FFh     |           |                      |                   |

| READ PROTECTION CONFIGURATION REGISTER | WRITE     | IA                   | 90h     | READ      | IA                   | ID                |

| READ STATUS REGISTER                   | WRITE     | BA                   | 70h     | READ      | Х                    | SRD               |

| CLEAR STATUS REGISTER                  | WRITE     | ВА                   | 50h     |           |                      |                   |

| READ QUERY                             | WRITE     | QA                   | 98h     | READ      | QA                   | QD                |

| BLOCK ERASE SETUP                      | WRITE     | ВА                   | 20h     | WRITE     | BA                   | D0h               |

| PROGRAM SETUP/ALTERNATE PROGRAM SETUP  | WRITE     | WA                   | 40h/10h | WRITE     | WA                   | WD                |

| PROGRAM/ERASE SUSPEND                  | WRITE     | ВА                   | B0h     |           |                      |                   |

| PROGRAM/ERASE RESUME - ERASE CONFIRM   | WRITE     | BA                   | D0h     |           |                      |                   |

| LOCK BLOCK                             | WRITE     | ВА                   | 60h     | WRITE     | ВА                   | 01h               |

| UNLOCK BLOCK                           | WRITE     | ВА                   | 60h     | WRITE     | ВА                   | D0h               |

| LOCK DOWN BLOCK                        | WRITE     | BA                   | 60h     | WRITE     | ВА                   | 2Fh               |

| PROTECTION REGISTER PROGRAM            | WRITE     | PA                   | C0h     | WRITE     | PA                   | PD                |

| PROTECTION REGISTER LOCK               | WRITE     | LPA                  | C0h     | WRITE     | LPA                  | FFFDh             |

NOTE: 1. BA: Address within the block

IA: Identification code address

ID: Identification code data

LPA: Lock protection register address

PA: Protection register address

PD: Data to be written at the location PA

QA: Query code address

QD: Query code data

SRD: Data read from the status register

WA: Word address of memory location to be written, or read

WD: Data to be written at the location WA

X: "Don't Care"

# Table 5 Command Descriptions

| CODE | DEVICE MODE                           | <b>BUS CYCLE</b> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|---------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10h  | Alt. Program Setup                    | First            | Operates the same as a PROGRAM SETUP command.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 20h  | Erase Setup                           | First            | Prepares the CSM for an ERASE CONFIRM command. If the next command is not an ERASE CONFIRM command, the command will be ignored, and the bank will go to read status mode and wait for another command.                                                                                                                                                                                                                                                                                  |

| 40h  | Program Setup                         | First            | A two-cycle command: The first cycle prepares for a PROGRAM operation, and the second cycle latches addresses and data and initiates the WSM to execute the program algorithm. The Flash device outputs status register data on the falling edge of OE# or CE#, whichever occurs first.                                                                                                                                                                                                  |

| 50h  | Clear Status<br>Register              | First            | The WSM can set the block lock status (SR3), program status (SR4), and erase status (SR5) bits in the status register to "1," but it cannot clear them to "0." Issuing this command clears those bits to "0."                                                                                                                                                                                                                                                                            |

| 60h  | Protection<br>Configuration<br>Setup  | First            | Prepares the CSM for changes to the block locking status. If the next command is not BLOCK UNLOCK, BLOCK LOCK or BLOCK LOCK DOWN, the command will be ignored, and the device will go to read status mode.                                                                                                                                                                                                                                                                               |

| 70h  | Read Status<br>Register               | First            | Places the device into read status register mode. Reading the device will output the contents of the status register for the addressed bank. The device will automatically enter this mode for the addressed bank after a PROGRAM or ERASE operation has been initiated.                                                                                                                                                                                                                 |

| 90h  | Read Protection<br>Configuration      | First            | Puts the device into the read protection configuration mode so that reading the device will output the manufacturer/device codes or block lock status.                                                                                                                                                                                                                                                                                                                                   |

| 98h  | Read Query                            | First            | Puts the device into the read query mode so that reading the device will output common flash interface information.                                                                                                                                                                                                                                                                                                                                                                      |

| B0h  | Program/Erase<br>Suspend              | First            | Suspends the currently executing PROGRAM/ERASE operation. The status register will indicate when the operation has been successfully suspended by setting either the program suspend (SR2) or erase suspend (SR6), and the WSM status bit (SR7) to a "1" (ready). The WSM will continue to idle in the suspend state, regardless of the state of all input control signals except RST#, which will immediately shut down the WSM and the remainder of the chip if RST# is driven to VIL. |

| C0h  | Program Device<br>Protection Register | First            | Writes a specific code into the device protection register.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | Lock Device<br>Protection Register    | First            | Locks the device protection register; data can no longer be changed.                                                                                                                                                                                                                                                                                                                                                                                                                     |

(continued on the next page)

# Table 5 Command Descriptions (continued)

| CODE | DEVICE MODE             | <b>BUS CYCLE</b> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0h  | Erase Confirm           | Second           | If the previous command was an ERASE SETUP command, then the CSM will close the address and data latches, and it will begin erasing the block indicated on the address balls. During programming/erase, the device will respond only to the READ STATUS REGISTER, PROGRAM SUSPEND, or ERASE SUSPEND commands and will output status register data on the falling edge of OE# or CE#, whichever occurs last. |

|      | Program/Erase<br>Resume | First            | If a PROGRAM or ERASE operation was previously suspended, this command will resume the operation.                                                                                                                                                                                                                                                                                                           |

| FFh  | Read Array              | First            | During the array mode, array data will be output on the data bus.                                                                                                                                                                                                                                                                                                                                           |

| 01h  | Lock Block              | Second           | If the previous command was PROTECTION CONFIGURATION SETUP, the CSM will latch the address and lock the block indicated on the address bus.                                                                                                                                                                                                                                                                 |

| 2Fh  | Lock Down               | Second           | If the previous command was PROTECTION CONFIGURATION SETUP, the CSM will latch the address and lock down the block indicated on the address bus.                                                                                                                                                                                                                                                            |

| D0h  | Unlock Block            | Second           | If the previous command was PROTECTION CONFIGURATION SETUP, the CSM will latch the address and unlock the block indicated on the address bus. If the block had been previously set to lock down, this operation will have no effect.                                                                                                                                                                        |

| 00h  | Invalid /Reserved       |                  | Unassigned command that should not be used.                                                                                                                                                                                                                                                                                                                                                                 |

mand set. The CSM stays in the current command state until the microprocessor issues another command.

The WSM successfully initiates an ERASE or PRO-GRAM operation only when VPP is within its correct voltage range.

### **CLEAR STATUS REGISTER**

The internal circuitry can set, but not clear, the block lock status bit (SR1), the VPP status bit (SR3), the program status bit (SR4), and the erase status bit (SR5) of the status register. The CLEAR STATUS REGISTER command (50h) allows the external microprocessor to clear these status bits and synchronize to the internal operations. When the status bits are cleared, the device returns to the read array mode.

### **READ OPERATIONS**

The following READ operations are available: READ ARRAY, READ PROTECTION CONFIGURATION REGISTER, READ QUERY and READ STATUS REGISTER.

### **READ ARRAY**

The array is read by entering the command code FFh on DQ0–DQ7. Control signals CE# and OE# must

be at a logic LOW level (V<sub>IL</sub>), and WE# and RST# must be at logic HIGH level (V<sub>IH</sub>) to read data from the array. Data is available on DQ0–DQ15. Any valid address within any of the blocks selects that address and allows data to be read from that address. Upon initial power-up or device reset, the device defaults to the read array mode.

### **READ PROTECTION CONFIGURATION DATA**

The chip identification mode outputs three types of information: the manufacturer/device identifier, the block locking status, and the protection register. Two bus cycles are required for this operation: the chip identification data is read by entering the command code 90h on DQ0–DQ7 to the bank containing address 00h and the identification code address on the address lines. Control signals CE# and OE# must be at a logic LOW level (VIL), and WE# and RST# must be at a logic HIGH level (VIH) to read data from the protection configuration register. Data is available on DQ0–DQ15. After data is read from the protection configuration register, the READ ARRAY command, FFh, must be issued to the bank containing address 00h prior to issuing other commands. See Table 9 for further details.

#### **READ QUERY**

The read query mode outputs common flash interface (CFI) data when the device is read (see Table 11). Two bus cycles are required for this operation. It is possible to access the query by writing the read query command code 98h on DQ0–DQ7 to the bank containing address 0h. Control signals CE# and OE# must be at a logic LOW level (VIL), and WE# and RST# must be at a logic HIGH level (VIH) to read data from the query. The CFI data structure contains information such as block size, density, command set, and electrical specifications. To return to read array mode, write the read array command code FFh on DQ0–DQ7.

#### **READ STATUS REGISTER**

The status register is read by entering the command code 70h on DQ0–DQ7. Two bus cycles are required for this operation: one to enter the command code and the block address and a second to read the status register. In a READ cycle, the address is latched and register data is updated on the falling edge of OE# or CE#, whichever occurs last. Register data is updated and latched on the falling edge of OE# or CE#, whichever occurs last.

### **PROGRAMMING OPERATIONS**

There are two CSM commands for programming: PROGRAM SETUP and ALTERNATE PROGRAM SETUP (see Table 3).

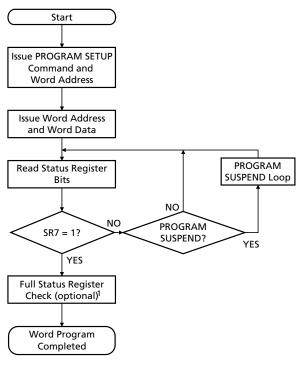

After the desired command code is entered (10h or 40h command code on DO0–DO7), the WSM takes over and correctly sequences the device to complete the PROGRAM operation. The WRITE operation may be monitored through the status register (see the Status Register section). During this time, the CSM will only respond to a PROGRAM SUSPEND command until the PROGRAM operation has been completed, after which time all commands to the CSM become valid again. The PROGRAM operation can be suspended by issuing a PROGRAM SUSPEND command (B0h). Once the WSM reaches the suspend state, it allows the CSM to respond only to READ ARRAY, READ STATUS REGISTER, READ PROTECTION CONFIGURATION, READ QUERY, PROGRAM SETUP, or PROGRAM RESUME. During the PROGRAM SUSPEND operation, array data should be read from an address other than the one being programmed. To resume the PROGRAM operation, a PRO-GRAM RESUME command (D0h) must be issued to cause the CSM to clear the suspend state previously set (see Figure 4 for programming operation and Figure 5 for program suspend and program resume).

Taking RST# to VIL during programming aborts the PROGRAM operation. During programming, VPP must remain in the appropriate VPP voltage range as shown in the recommended operating conditions table.

### **ERASE OPERATIONS**

An ERASE operation must be used to initialize all bits in an array block to "1s." After BLOCK ERASE confirm is issued, the CSM responds only to an ERASE SUSPEND command until the WSM completes its task.

Block erasure inside the memory array sets all bits within the address block to logic 1s. Erase is accomplished only by blocks; data at single address locations within the array cannot be erased individually. The block to be erased is selected by using any valid address within that block. Block erasure is initiated by a command sequence to the CSM: BLOCK ERASE setup (20h) followed by BLOCK ERASE CONFIRM (D0h) (see Figure 6). A two-command erase sequence protects against accidental erasure of memory contents.

When the BLOCK ERASE CONFIRM command is complete, the WSM automatically executes a sequence of events to complete the block erasure. During this sequence, the block is programmed with logic 0s, data is verified, all bits in the block are erased, and finally verification is performed to ensure that all bits are correctly erased. The ERASE operation may be monitored through the status register (see the Status Register section).

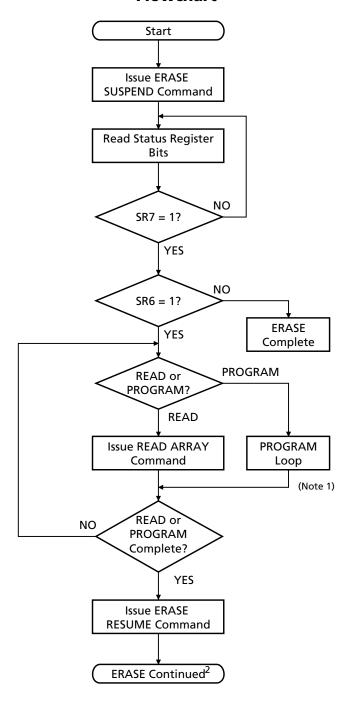

During the execution of an ERASE operation the ERASE SUSPEND command (B0h) can be entered to direct the WSM to suspend the ERASE operation. Once the WSM has reached the suspend state, it allows the CSM to respond only to the READ ARRAY, READ STATUS REGISTER, READ OUERY, READ CHIP PRO-TECTION CONFIGURATION, PROGRAM SETUP, PRO-GRAM RESUME, ERASE RESUME and LOCK SETUP (see the Block Locking section). During the ERASE SUS-PEND operation, array data must be read from a block other than the one being erased. To resume the ERASE operation, an ERASE RESUME command (D0h) must be issued to cause the CSM to clear the suspend state previously set (see Figure 7). It is also possible to suspend an ERASE in any bank and initiate a WRITE to another block in the same bank. After the completion of a WRITE, an ERASE can be resumed by writing an ERASE RESUME command.

# Table 6 Bus Operations

| MODE                                                                     | RST# | CE# | OE# | WE# | ADDRESS | DQ0-DQ15 |

|--------------------------------------------------------------------------|------|-----|-----|-----|---------|----------|

| Read (array, status registers, device identification register, or query) | Vін  | VIL | VIL | ViH | Х       | Dout     |

| Standby                                                                  | ViH  | ViH | Х   | Х   | Х       | High-Z   |

| Output Disable                                                           | ViH  | ViH | Х   | Х   | Х       | High-Z   |

| Reset                                                                    | VIL  | Х   | Х   | Х   | Х       | High-Z   |

| Write                                                                    | Vih  | VIL | ViH | VIL | Х       | Din      |

# Table 7 Status Register Bit Definition

| WSMS | ESS | ES | PS | VPPS | PSS | BLS | R |

|------|-----|----|----|------|-----|-----|---|

| 7    | 6   | 5  | 4  | 3    | 2   | 1   | 0 |

| STATUS<br>BIT # | STATUS REGISTER BIT                                                                                                          | DESCRIPTION                                                                                                                                                                                                                                                                                                       |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR7             | WRITE STATE MACHINE STATUS (WSMS)  1 = Ready  0 = Busy                                                                       | Check write state machine bit first to determine word program or block erase completion, before checking program or erase status bits.                                                                                                                                                                            |

| SR6             | ERASE SUSPEND STATUS (ESS)  1 = BLOCK ERASE Suspended  0 = BLOCK ERASE in  Progress/Completed                                | When ERASE SUSPEND is issued, WSM halts execution and sets both WSMS and ESS bits to "1." ESS bit remains set to "1" until an ERASE RESUME command is issued.                                                                                                                                                     |

| SR5             | ERASE STATUS (ES)  1 = Error in Block Erasure  0 = Successful BLOCK ERASE                                                    | When this bit is set to "1," WSM has applied the maximum number of erase pulses to the block and is still unable to verify successful block erasure.                                                                                                                                                              |

| SR4             | PROGRAM STATUS (PS)  1 = Error in PROGRAM  0 = Successful PROGRAM                                                            | When this bit is set to "1," WSM has attempted but failed to program a word.                                                                                                                                                                                                                                      |

| SR3             | VPP STATUS (VPPS)  1 = VPP Low Detect, Operation Abort  0 = VPP = OK                                                         | The VPP status bit does not provide continuous indication of the VPP level. The WSM interrogates the VPP level only after the program or erase command sequences have been entered and informs the system if VPP < 0.9V. The VPP level is also checked before the PROGRAM/ERASE operation is verified by the WSM. |

| SR2             | PROGRAM SUSPEND STATUS (PSS)  1 = PROGRAM Suspended  0 = PROGRAM in Progress/Completed                                       | When PROGRAM SUSPEND is issued, WSM halts execution and sets both WSMS and PSS bits to "1." PSS bit remains set to "1" until a PROGRAM RESUME command is issued.                                                                                                                                                  |

| SR1             | BLOCK LOCK STATUS (BLS)  1 = PROGRAM/ERASE Attempted on a Locked Block; Operation Aborted  0 = No Operation to Locked Blocks | If a PROGRAM or ERASE operation is attempted to one of<br>the locked blocks, this is set by the WSM. The operation<br>specified is aborted and the device is returned to read<br>status mode.                                                                                                                     |

| SR0             | RESERVED FOR FUTURE ENHANCEMENT                                                                                              | This bit is reserved for future use.                                                                                                                                                                                                                                                                              |

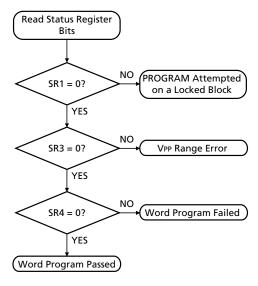

### Figure 4 **Automated Word Programming Flowchart**

| BUS<br>OPERATION | COMMAND                   | соммі                                                                   | ENTS                                                            |  |  |

|------------------|---------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| WRITE            | WRITE<br>PROGRAM<br>SETUP |                                                                         | 40h or 10h<br>Address of word to be<br>programmed               |  |  |

| WRITE            | WRITE<br>DATA             |                                                                         | Word to be<br>programmed<br>Address of word to be<br>programmed |  |  |

| READ             |                           | Status register data<br>Toggle OE# or CE# to<br>update status register. |                                                                 |  |  |

| Standby          |                           |                                                                         | Check SR7<br>1 = Ready, 0 = Busy                                |  |  |

Repeat for subsequent words.

Write FFh after the last word programming operation to reset the device to read array mode.

### **FULL STATUS REGISTER CHECK FLOW**

| BUS<br>OPERATION | COMMAND | COMMENTS                                         |

|------------------|---------|--------------------------------------------------|

| Standby          |         | Check SR1<br>1 = Detect locked block             |

| Standby          |         | Check SR3 <sup>2</sup><br>1 = Detect VPP LOW     |

| Standby          |         | Check SR4 <sup>3</sup><br>1 = Word program error |

- NOTE: 1. Full status register check can be done after each word or after a sequence of words.

- 2. SR3 must be cleared before attempting additional PROGRAM/ERASE operations.

- 3. SR4 is cleared only by the CLEAR STATUS REGISTER command, but it does not prevent additional program operation attempts.

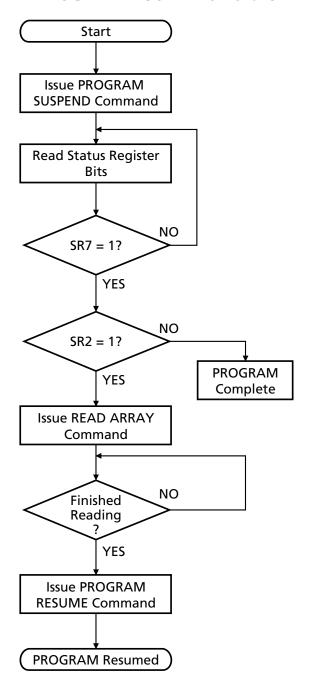

### Figure 5 **PROGRAM SUSPEND/ PROGRAM RESUME Flowchart**

| BUS<br>OPERATION | COMMAND            | COMMENTS                                                                |

|------------------|--------------------|-------------------------------------------------------------------------|

| WRITE            | PROGRAM<br>SUSPEND | Data = B0h                                                              |

| READ             |                    | Status register data<br>Toggle OE# or CE# to update<br>status register. |

| Standby          |                    | Check SR7<br>1 = Ready                                                  |

| Standby          |                    | Check SR2<br>1 = Suspended                                              |

| WRITE            | read<br>Array      | Data = FFh                                                              |

| READ             |                    | Read data from block other than that being programmed.                  |

| WRITE            | PROGRAM<br>RESUME  | Data = D0h                                                              |

- **NOTE:** 1. Full status register check can be done after each word or after a sequence of words.

- 2. SR3 must be cleared before attempting additional PROGRAM/ERASE operations.

- 3. SR5 is cleared only by the CLEAR STATUS REGISTER command in cases where multiple blocks are erased before full status is checked.

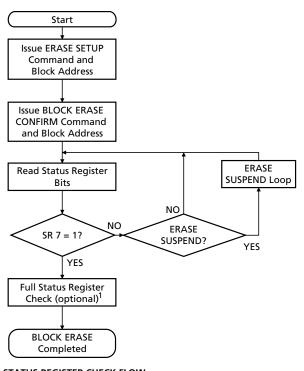

### Figure 6 **BLOCK ERASE Flowchart**

#### BUS OPERATION COMMAND **COMMENTS** WRITE WRITE Data = 20h**ERASE** Block Addr = Address **SETUP** within block to be erased WRITE **ERASE** Data = D0hBlock Addr = Address within block to be erased **READ** Status register data Toggle OE# or CE# to update status register. Standby Check SR7 1 = Ready, 0 = Busy

Repeat for subsequent blocks. Write FFh after the last BLOCK ERASE operation to reset the device to read array mode.

### **FULL STATUS REGISTER CHECK FLOW**

| BUS<br>OPERATION | COMMAND | COMMENTS                                                   |

|------------------|---------|------------------------------------------------------------|

| Standby          |         | Check SR1<br>1 = Detect locked block                       |

| Standby          |         | Check SR3 <sup>2</sup><br>1 = Detect V <sub>PP</sub> block |

| Standby          |         | Check SR5 <sup>3</sup><br>1 = BLOCK ERASE error            |

- NOTE: 1. Full status register check can be done after each block or after a sequence of blocks.

- 2. SR3 must be cleared before attempting additional PROGRAM/ERASE operations.

- 3. SR5 is cleared only by the CLEAR STATUS REGISTER command in cases where multiple blocks are erased before full status is checked.

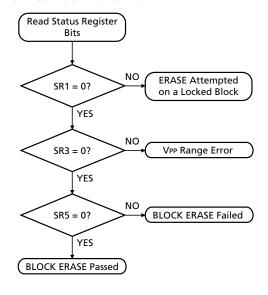

# Figure 7 ERASE SUSPEND/ERASE RESUME Flowchart

| BUS<br>OPERATION | COMMAND          | COMMENTS                                                                |

|------------------|------------------|-------------------------------------------------------------------------|

| WRITE            | ERASE<br>SUSPEND | Data = B0h                                                              |

| READ             |                  | Status register data<br>Toggle OE# or CE# to<br>update status register. |

| Standby          |                  | Check SR7<br>1 = Ready                                                  |

| Standby          |                  | Check SR6<br>1 = Suspended                                              |

| WRITE            | READ<br>ARRAY    | Data = FFh                                                              |

| READ             |                  | Read data from block other than that being erased.                      |

| WRITE            | ERASE<br>RESUME  | Data = D0h                                                              |

**NOTE:** 1. See BLOCK ERASE Flowchart for complete erasure procedure.

2. See Word Programming Flowchart for complete programming procedure.

# READ-WHILE-WRITE/ERASE CONCURRENCY

It is possible for the device to read from one bank while erasing/writing to another bank. Once a bank enters the WRITE/ERASE operation, the other bank automatically enters read array mode. For example, during a READ CONCURRENCY operation, if a PRO-GRAM/ERASE command is issued in bank *a*, then bank a changes to the read status mode and bank b defaults to the read array mode. The device will read from bank b if the latched address resides in bank b (see Figure 8). Similarly, if a PROGRAM/ERASE command is issued in bank b, then bank b changes to read status mode and bank a defaults to read array mode. When returning to bank a, the device will read PROGRAM/ERASE status if the latched address resides in bank a. A correct bank address must be specified to read status register after returning from concurrent read in the other bank.

When reading the CFI or the chip protection register, concurrent operation is not allowed on the top boot device. Concurrent READ of the CFI or the chip protection register is only allowed when a PROGRAM or ERASE operation is performed on bank b on the bottom boot device. For a bottom boot device, reading of the CFI table or the chip protection register is only allowed if bank b is in read array mode. For a top boot device, reading of the CFI table or the chip protection register is only allowed if bank a is in read array mode.

# Figure 8 READ-While-WRITE Concurrency

|                                                                                                                                                                                                                                                                     | T                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bank a                                                                                                                                                                                                                                                              | Bank <i>b</i>                                                                                                                                                                                                                                                                   |

| <ol> <li>Erasing/writing to bank a</li> <li>Erasing in bank a can be suspended, and a WRITE to another block in bank a can be initiated.</li> <li>After the WRITE in that block is complete, an ERASE can be resumed by writing an ERASE RESUME command.</li> </ol> | 1 - Reading from bank <i>b</i>                                                                                                                                                                                                                                                  |

| 1 - Reading bank <i>a</i>                                                                                                                                                                                                                                           | <ol> <li>1 - Erasing/writing to bank b</li> <li>2 - Erasing in bank b can be suspended, and a WRITE to another block in bank b can be initiated.</li> <li>3 - After the WRITE in that block is complete, an ERASE can be resumed by writing an ERASE RESUME command.</li> </ol> |

### **BLOCK LOCKING**

The Flash memory devices provide a flexible locking scheme which allows each block to be individually locked or unlocked with no latency.

The devices offer two-level protection for the blocks. The first level allows software-only control of block locking (for data which needs to be changed frequently), while the second level requires hardware interaction before locking can be changed (code which does not require frequent updates).

Control signals WP#, DQ0, and DQ1 define the state of a block; for example, state [001] means WP# = 0, DQ0 = 1 and DQ1 = 0.

Table 8 defines all of the possible locking states.

NOTE: All blocks are software-locked upon powerup sequence completion.

#### **LOCKED STATE**

After a power-up sequence completion, or after a reset sequence, all blocks are locked (states [001] or [101]). This means full protection from alteration. Any PROGRAM or ERASE operations attempted on a locked block will return an error on bit SR1 of the status register. The status of a locked block can be changed to unlocked or lock down using the appropriate software commands. Writing the lock command sequence, 60h followed by 01h, can lock an unlocked block.

### UNLOCKED STATE

Unlocked blocks (states [000], [100], [110]) can be programmed or erased. All unlocked blocks return to the locked state when the device is reset or powered down. An unlocked block can be locked or locked down using the appropriate software command sequence, 60h followed by D0h (see Table 4).

#### LOCKED DOWN STATE

Blocks that are locked down (state [011]) are protected from PROGRAM and ERASE operations, but their protection status cannot be changed using software commands alone. A locked or unlocked block can be locked down by writing the lock down command sequence, 60h followed by 2Fh. Locked down blocks revert to the locked state when the device is reset or powered down.

The LOCK DOWN function is dependent on the WP# input. When WP# = 0, blocks in lock down [011] are protected from program, erase, and lock status changes. When WP# = 1, the lock down function is disabled ([111]), and locked down blocks can be individually unlocked by a software command to the [110] state, where they can be erased and programmed. These blocks can then be relocked [111] and unlocked [110] as desired while WP# remains HIGH. When WP# goes LOW, blocks that were previously locked down return to the locked down state [011] regardless of any changes made while WP# was HIGH. Device reset or powerdown resets all locks, including those in lock down, to locked state (see Table 9).

### **READING A BLOCK'S LOCK STATUS**

The lock status of every block can be read in the read device identification mode. To enter this mode, write 90h to the the bank containing address 00h. Subsequent READs at block address +00002 will output the lock status of that block. The lowest two outputs, DQ0 and DQ1, represent the lock status. DQ0 indicates the block lock/unlock status and is set by the LOCK command and cleared by the UNLOCK command. It is also automatically set when entering lock down. DQ1 indicates lock down status and is set by the LOCK DOWN

Table 8

Block Locking State Transition

| WP# | DQ1 | DQ0 | NAME                  | ERASE/PROGRAM<br>ALLOWED | LOCK      | UNLOCK    | LOCK<br>DOWN |

|-----|-----|-----|-----------------------|--------------------------|-----------|-----------|--------------|

| 0   | 0   | 0   | Unlocked              | Yes                      | To [001]  | No Change | To [011]     |

| 0   | 0   | 1   | Locked (Default)      | No                       | No Change | To [000]  | To [011]     |

| 0   | 1   | 1   | Lock Down             | No                       | No Change | No Change | No Change    |

| 1   | 0   | 0   | Unlocked              | Yes                      | To [101]  | No Change | To [111]     |

| 1   | 0   | 1   | Locked                | No                       | No Change | To [100]  | To [111]     |

| 1   | 1   | 0   | Lock Down<br>Disabled | Yes                      | To [111]  | No Change | To [111]     |

| 1   | 1   | 1   | Lock Down<br>Disabled | No                       | No Change | To [110]  | No Change    |

command. It can only be cleared by reset or power-down, not by software. Table 8 shows the locking state transition scheme. The READ ARRAY command, FFh, must be issued to the bank containing address 00h prior to issuing other commands.

### LOCKING OPERATIONS DURING ERASE SUSPEND

Changes to block lock status can be performed during an ERASE SUSPEND by using the standard locking command sequences to unlock, lock, or lock down. This is useful in the case when another block needs to be updated while an ERASE operation is in progress.

To change block locking during an ERASE operation, first write the ERASE SUSPEND command (B0h), then check the status register until it indicates that the ERASE operation has been suspended. Next, write the desired lock command sequence to block lock, and the lock status will be changed. After completing any desired LOCK, READ, or PROGRAM operations, resume the ERASE operation with the ERASE RESUME command (D0h).

If a block is locked or locked down during an ERASE SUSPEND on the same block, the locking status bits will be changed immediately. When the ERASE is resumed, the ERASE operation will complete.

A locking operation cannot be performed during a PROGRAM SUSPEND.

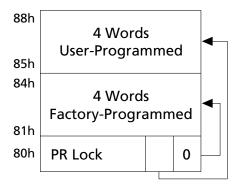

### **CHIP PROTECTION REGISTER**

A 128-bit chip protection register can be used to fulfill the security considerations in the system (preventing the device substitution).

The 128-bit security area is divided into two 64-bit segments. The first 64 bits are programmed at the manufacturing site with a unique 64-bit unchangeable number. The other segment is left blank for customers to program as desired. (See Figure 9).

Figure 9

Protection Register Memory Map

Table 9

Chip Configuration Addressing<sup>1</sup>

| ITEM                                                                               | ADDRESS <sup>2</sup> | DATA                                  |

|------------------------------------------------------------------------------------|----------------------|---------------------------------------|

| Manufacturer Code (x16)                                                            | 00000h               | 002Ch                                 |

| Device Code Top boot configuration Bottom boot configuration                       | 00001h               | 44B2h<br>44B3h                        |

| Block Lock Configuration  Block is unlocked  Block is locked  Block is locked down | XX002h               | Lock<br>DQ0 = 0<br>DQ0 = 1<br>DQ1 = 1 |

| Chip Protection Register Lock                                                      | 80h                  | PR Lock                               |

| Chip Protection Register 1                                                         | 81h–84h              | Factory Data                          |

| Chip Protection Register 2                                                         | 85h–88h              | User Data                             |

**NOTE:** 1. Other locations within the configuration address space are reserved by Micron for future use.

2. "XX" specifies the block address of lock configuration.

### **READING THE CHIP PROTECTION REGISTER**

The chip protection register is read in the device identification mode. To enter this mode, load the 90h command to the bank containing address 00h. Once in this mode, READ cycles from addresses shown in Table 9 retrieve the specified information. To return to the read array mode, write the READ ARRAY command (FFh). The READ ARRAY command, FFh, must be issued to the bank containing address 00h prior to issuing other commands.

### PROGRAMMING THE CHIP PROTECTION REGISTER

The first 64 bits (PR1) of the protection register (addresses 81h-84h) are programmed with a unique identifier at the factory. DQ0 of the PR lock register (address 80h) is programmed to a "0" state, locking the first 64 bits and preventing any further programming. The second 64 bits (PR2) is a user area (addresses 85h-88h), where the user can program any information into this area as long as DQ1 of the PR lock register remains unprogrammed. After DQ1 of the PR lock register is programmed, no further programming is allowed on PR2. The programming sequence is similar to array programming except that the PROTECTION REGIS-TER PROGRAMMING SETUP command (C0h) is issued instead of an ARRAY PROGRAMMING SETUP command (40h), followed by the data to be programmed at addresses 85h-88h.

To program the PR lock bit for PR2 (to prevent further programming), use the above sequence on address 80h, with data of FFFDh (DQ1 = 0).

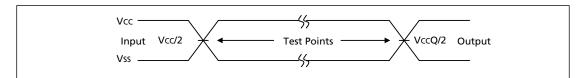

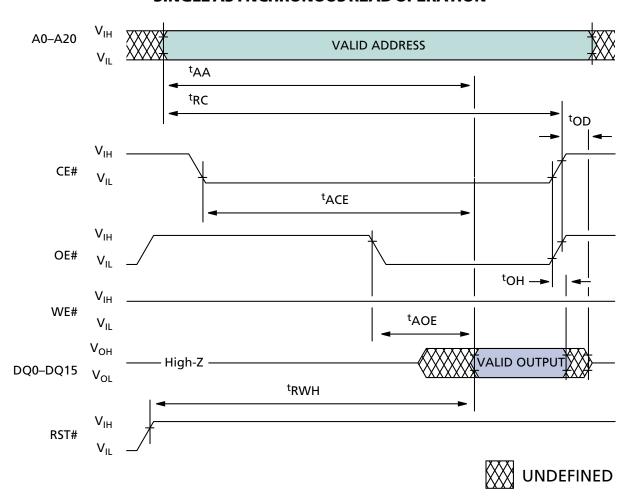

### **ASYNCHRONOUS READ CYCLE**

When accessing addresses in a random order or when switching between pages, the access time is given by <sup>t</sup>AA.

When CE# and OE# are LOW, the data is placed on the data bus and the processor can read the data.

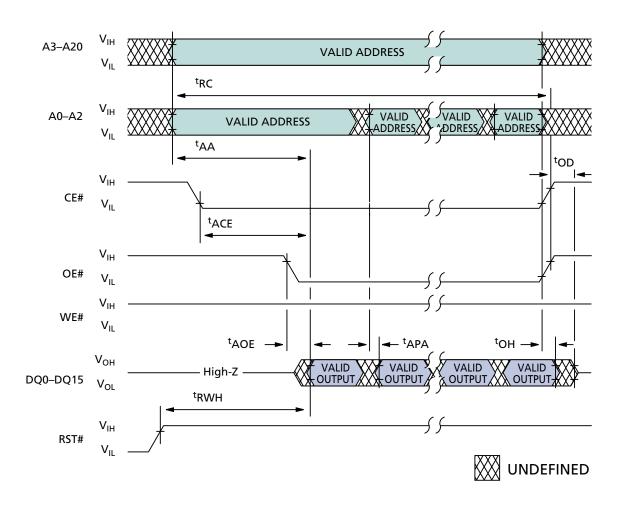

### **PAGE READ MODE**

The initial portion of the page mode cycle is the same as the asynchronous access cycle. Holding CE# LOW and toggling addresses A0–A2 allows random access of other words in the page. The page word size is eight words.

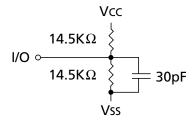

# VPP / Vcc PROGRAM AND ERASE VOLTAGES

The MT28F321P20 Flash memory provides insystem programming and erase with VPP in the 0.9V–2.2V range. The 12V VPP mode programming is offered for compatibility with existing programming equipment and does not enhance program/erase performance.

The device can withstand 100,000 WRITE/ERASE operations when  $V_{PP} = V_{PP1}$  or 100 WRITE/ERASE operations and 10 cumulative hours when  $V_{PP} = V_{PP2}$ .

In addition to the flexible block locking, the VPP programming voltage can be held low for absolute hardware write protection of all blocks in the Flash device. When VPP is below VPPLK, any PROGRAM or ERASE operation will result in an error, prompting the corresponding status register bit (SR3) to be set.

During WRITE and ERASE operations, the WSM monitors the VPP voltage level. WRITE/ERASE operations are allowed only when VPP is within the ranges specified in Table 10.

When Vcc is below Vlko, any WRITE/ERASE operation will be disabled.

Table 10 Vpp Range (V)

|            | MIN  | MAX  |

|------------|------|------|

| In-System  | 0.9  | 2.2  |