# 8/16-bit Data Bus Static RAM Card

**Connector Type**

Two-piece 68-pin

MF365A-LZCATXX

MF3129-LZCATXX

MF3257-LZCATXX

MF3513-LZCATXX

MF31M1-LZCATXX

MF32M1-LZCATXX

MF34M1-LZCATXX

## 1. DESCRIPTION

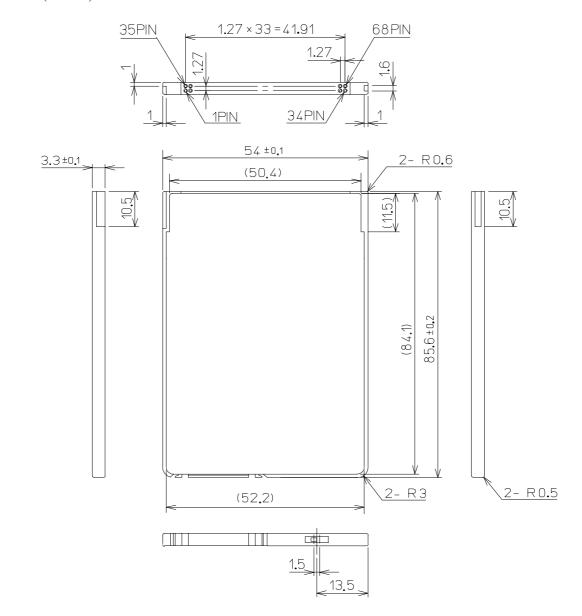

Mitsubishi's Static RAM cards provide large memory capacities on a device approximately the size of a credit card (85.6mm×54mm×3.3mm).

The cards use a 8/16 bit data-bus. The devices use a replaceable lithium battery to maintain data. Available in 64K byte-4M byte capacities, Mitsubishi's Static RAM cards are available with a 68-pin, two-piece connector.

#### 2. FEATURES

- ■Uses TSOP (Thin Small Outline Package) to achieve very high memory density coupled with high reliability, without enlarging card size

- ■Electrostatic discharge protection to 15kV

- ■Buffered interface

- ■Write protect switch

- ■Attribute memory

- ■68pin

### 3. APPLICATIONS

■Office automation

■Data Communication

**■**Computers

**■**Industrial

■Telecommunications

**■**Consumer

## 4. PRODUCT LIST

|                | Item | Memory   | Data Bus    | Attribute | Auxiliary |

|----------------|------|----------|-------------|-----------|-----------|

| Type name      |      | capacity | width(bits) | memory    | battery   |

| MF365A-LZCATXX |      | 64KB     |             |           |           |

| MF3129-LZCATXX |      | 128KB    |             |           |           |

| MF3257-LZCATXX |      | 256KB    |             |           |           |

| MF3513-LZCATXX |      | 512KB    | 8/16        | 8KB       | NO        |

| MF31M1-LZCATXX |      | 1MB      |             | $E^2PROM$ |           |

| MF32M1-LZCATXX |      | 2MB      |             |           |           |

| MF34M1-LZCATXX |      | 4MB      |             |           |           |

#### 5. SUMMARY

MF3XXX-LZCATXX series is the Static RAM cards which has 8/16 bit changeable data-bus width. The card has a replaceable lithium battery to maintain data in memory. When the card is not use or the supply voltage drops, the battery will automatically maintain data in memory.

# 6. FUNCTIONAL DESCRIPTION

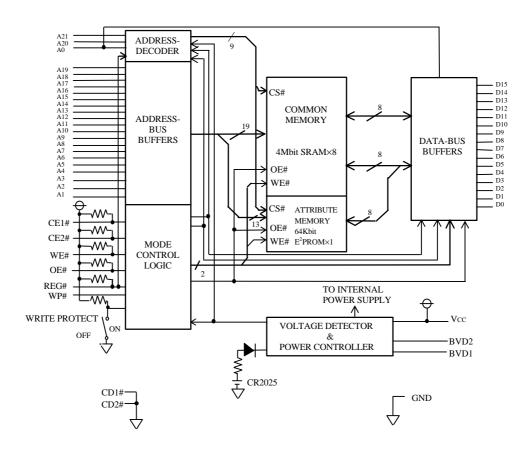

The function of the card is determined by the combination of the following five control signals, REG#, CE1#, CE2#, OE#, WE#; active low signals. (Please refer to section 10 FUNCTION TABLE on page 5) (1)COMMON MEMORY FUNCTION

When REG# signal is high level, the common memory area is selected.

## (a)READ MODE

To read, WE# is set high level and CE1# or CE2# is set low level and the memory address is applied at inputs A0-A21(4MB). Setting OE# low level executes the reading with output at data-bus. It is available to make the following functions according to the combination of CE1# and CE2#.

When CE1# is set low level and CE2# is set high level, the card operates as an 8 bit data-bus width card. The data can be dealt with lower data-bus(D0-D7).

When both CE1# and CE2# are set low level, the card operates as a 16 bit data-bus width card.

At this mode LSB of address-bus (A0) is ignored.

In addition odd byte can be accessed through upper data-bus(D8-D15) when CE1# is set high level and CE2# is set low level. This mode is useful when handling only odd bytes in the 16 bit data-bus interface system (A0 is ignored).

When both CE1# and CE2# are set high level, the card becomes a standby mode where the card consumes low power and the data-bus is placed in high impedance state (above functions of CE1# and CE2# are the same as in the following modes).

When both OE# and WE# are set high level, the card becomes a output disable mode and the data-bus is placed in high impedance state.

#### (b)WRITE MODE

To write, the memory address is first applied at inputs A0-A21(4MB) and the data is applied at output pins. Setting CE1# or CE2# low level, WE# low level and OE# high level executes the writing.

## (2) ATTRIBUTE MEMORY FUNCTION

When REG# is set low level, the attribute memory area is selected. MF3XXX-LZCATXX series accommodates an attribute memory of 8KB E<sup>2</sup>PROM on even addresses.

#### (a)READ MODE

First set CE1# and CE2# low level or high level and select residing address (even address). Data can be read by setting OE# low level and WE# high level.

#### (b)WRITE MODE

Writing can be done either by byte-mode or page-mode. The page-mode write is the function to be able to write data of 32 bytes in a single write cycle. The page address is set by A6 to A13 (Please note that attribute memory exists in even bytes only). To write, set OE# high level and WE# low level. Data will be latched at the rising edge of WE#. After the first load unless WE# changes from high level to low level within 30µs, the automatic erase/program starts and completes in 10ms or before. Page data can be latched if WE# transits from high level to low level before the 30µs. Page-mode write also executes erase/program operation within 10ms. The page address must be maintained during the page data loading.

## 7. WRITE PROTECT MODE

When the write protect switch is switched on, this card goes into a write protect mode that can read but not write data. In this mode, WP pin becomes "H" level.

At the shipment the write protect switch is switched off (Normal mode : The card can be written ; WP pin indicates "L" level).

# 8. PIN ASSIGNMENTS

| Pin            |          | GWEVIS                   | Pin      |           |                                         |

|----------------|----------|--------------------------|----------|-----------|-----------------------------------------|

| No.            | Symbol   | Function                 | No.      | Symbol    | Function                                |

| 1              | GND      | Ground                   | 35       | GND       | Ground                                  |

| 2              | D3       | \                        | 36       | CD1#      | Card detect 1                           |

| 3              | D4       |                          | 37       | D11       | \                                       |

| 4              | D5       | Data I/O                 | 38       | D12       |                                         |

| 5              | D6       |                          | 39       | D13       | Data I/O                                |

| 6              | D7       | )                        | 40       | D14       |                                         |

| 7              | CE1#     | Card enable 1            | 41       | D15       | Ų                                       |

| 8              | A10      | Address input            | 42       | CE2#      | Card enable 2                           |

| 9              | OE#      | Output enable            | 43       | NC        | h                                       |

| 10             | A11      | )                        | 44       | NC        | No connection                           |

| 11             | A9       |                          | 45       | NC        | Ų                                       |

| 12             | A8       | Address input            | 46       | A17       | A17 (NC for $\leq$ 128KB types)         |

| 13             | A13      | _                        | 47       | A18       | A18 (NC for $\leq$ 256KB types)         |

| 14             | A14      | )                        | 48       | A19       | A19 (NC for $\leq$ 512KB types) Address |

| 15             | WE#      | Write enable             | 49       | A20       | A20 (NC for $\leq$ 1MB type) input      |

| 16             | NC       | No connection            | 50       | A21       | A21 (NC for $\leq$ 2MB type)            |

| 17             | VCC      | Power supply voltage     | 51       | VCC       | Power supply voltage                    |

| 18             | NC       | No connection            | 52       | NC        |                                         |

| 19             | A16      | \ A16 (NC for 64KB type) | 53       | NC        |                                         |

| 20             | A15      |                          | 54       | NC        |                                         |

| 21             | A12      |                          | 55       | NC        |                                         |

| 22             | A7       |                          | 56       | NC        | > No connection                         |

| 23             | A6       |                          | 57       | NC        |                                         |

| 24             | A5       | Address input            | 58       | NC        |                                         |

| 25             | A4       |                          | 59       | NC        | ])                                      |

| 26             | A3       |                          | 60       | NC        | Y                                       |

| 27             | A2       |                          | 61       | REG#      | Attribute memory select                 |

| 28             | A1       |                          | 62       | BVD2      | Battery voltage detect 2                |

| 29             | A0       | )                        | 63       | BVD1      | Battery voltage detect 1                |

| 30<br>31       | D0<br>D1 | Data I/O                 | 64<br>65 | D8<br>D9  | Data I/O                                |

| 32             | D1<br>D2 | Data I/O                 | 66       | D9<br>D10 | Data I/O                                |

| 33             | WP       | Write protect            | 67       | CD2#      | Card detect 2                           |

| 34             | GND      | Ground                   | 68       | GND       | Ground                                  |

| J <del>4</del> | עויט     | Orvaila                  | UO       | מאט       | Oround                                  |

## 9. BLOCK DIAGRAM (4MB) (MF34M1-LZCATXX)

# 10. FUNCTION TABLE

| Mode                      | REG# | CE1# | CE2# | OE# | WE# | A0 | I/O (D15~D8)          | I/O (D7~D0)           | Icc     |

|---------------------------|------|------|------|-----|-----|----|-----------------------|-----------------------|---------|

| Standby                   | X    | Н    | Н    | X   | X   | X  | High-impedance        | High-impedance        | standby |

| Read A (16bit)<br>common  | Н    | L    | L    | L   | Н   | X  | Odd Byte<br>Data out  | Even Byte<br>Data out | Active  |

| Write A (16bit) common    | Н    | L    | L    | Н   | L   | X  | Odd Byte<br>Data in   | Even Byte<br>Data in  | Active  |

| Read B (8bit) common      | Н    | L    | Н    | L   | Н   | L  | High-impedance        | Even Byte<br>Data out | Active  |

|                           | Н    | L    | Н    | L   | Н   | Н  | High-impedance        | Odd Byte<br>Data out  | Active  |

| Write B (8bit)            | Н    | L    | Н    | Н   | L   | L  | High-impedance        | Even Byte Data in     | Active  |

| common                    | Н    | L    | Н    | Н   | L   | Н  | High-impedance        | Odd Byte Data in      | Active  |

| Read C (8bit)<br>common   | Н    | Н    | L    | L   | Н   | X  | Odd Byte<br>Data out  | High-impedance        | Active  |

| Write C (8bit) common     | Н    | Н    | L    | Н   | L   | X  | Odd Byte<br>Data in   | High-impedance        | Active  |

| Output disable            | X    | X    | X    | Н   | Н   | X  | High-impedance        | High-impedance        | Active  |

| Read A (16bit) attribute  | L    | L    | L    | L   | Н   | X  | Data out<br>(unknown) | Even Byte<br>Data out | Active  |

| Read B (8bit) attribute   | L    | L    | Н    | L   | Н   | L  | High-impedance        | Even Byte<br>Data out | Active  |

|                           | L    | L    | Н    | L   | Н   | Н  | High-impedance        | Data out (unknown)    | Active  |

| Read C (8bit) attribute   | L    | Н    | L    | L   | Н   | X  | Data out (unknown)    | High-impedance        | Active  |

| Write A (16bit) attribute | L    | L    | L    | Н   | L   | X  | don't care            | Even Byte Data in     | Active  |

| Write B (8bit)            | L    | L    | Н    | Н   | L   | L  | don't care            | Even Byte Data in     | Active  |

| attribute                 | L    | L    | Н    | Н   | L   | Н  | don't care            | don't care            | Active  |

| Write C (8bit) attribute  | L    | Н    | L    | Н   | L   | X  | don't care            | don't care            | Active  |

Note 1 : H=Vih, L=Vil, X=Vih or Vil

# 11. ABSOLUTE MAXIMUM RATINGS

| Symbol | Parameter               | Conditions              | Ratings      | Unit |

|--------|-------------------------|-------------------------|--------------|------|

| Vcc    | Supply voltage          |                         | -0.3~6.0     | V    |

| VI     | Input voltage           | With respect to GND     | -0.3~VCC+0.3 | V    |

| Vo     | Output voltage          |                         | 0~VCC        | V    |

| Topr1  | Operating temperature 1 | Read, Write Operation   | 0~60         | °C   |

| Topr2  | Operating temperature 2 | Data retention          | 0~60         | °C   |

| Tstg   | Storage temperature     | Excludes data retention | -20~70       | °C   |

# 12. RECOMMENDED OPERATING CONDITIONS (Ta=0~55°C, unless otherwise noted)

| Sumbol | December           |      | T I :4 |      |      |

|--------|--------------------|------|--------|------|------|

| Symbol | Parameter          | Min. | Тур.   | Max. | Unit |

| Vcc    | Vcc Supply voltage | 4.75 | 5.0    | 5.25 | V    |

| GND    | System ground      |      | 0      |      | V    |

| VIH    | High input voltage | 2.4  |        | VCC  | V    |

| VIL    | Low input voltage  | 0    |        | 0.8  | V    |

# **13. ELECTRICAL CHARACTERISTICS** (Ta=0~55°C, Vcc=5V±5%, unless otherwise noted)

| Symbol    | Parameter           |                                   | Test conditions     |               |      | Limits |      | Unit |

|-----------|---------------------|-----------------------------------|---------------------|---------------|------|--------|------|------|

|           |                     |                                   |                     |               | Min. | Тур.   | Max. |      |

| Vон       | High output voltage | Iон= -1.0mA                       |                     |               | 2.4  |        |      | V    |

| Vol       | Low output voltage  | IoL=2mA                           |                     |               |      |        | 0.4  | V    |

| Іін       | High input current  | V <sub>I</sub> =V <sub>cc</sub> V |                     |               |      |        | 10   | μΑ   |

| IIL       | Low input current   | VI=0V                             | CE1#, CE2#, WI      | E#, OE#, REG# | -10  |        | -70  | μΑ   |

|           |                     |                                   | Other inputs        |               |      |        | -10  |      |

| Iozh      | High output current | CE1#=CE2#=                        | VIH or OE#=VIH V    | VE#=Vih,      |      |        | 10   | μΑ   |

|           | in off state        | Vo=Vcc                            |                     |               |      |        |      |      |

| Iozl      | Low output current  | CE1#=CE2#=                        | VIH or OE#=VIH V    | VE#=Vih,      |      |        | -10  | μΑ   |

|           | in off state        | Vo=0V                             |                     |               |      |        |      |      |

| Icc 1 • 1 | Active supply       | CE1#=CE2#=                        | VIL, Other inputs   | 64KB~512KB    |      |        | 170  | mA   |

|           | current 1           | =VIH or VIL,C                     | Outputs=open        | 1MB~4MB       |      |        | 230  |      |

| Icc 1 • 2 | Active supply       | CE1#=CE2# ≤                       | $\leq 0.2$ V, Other | 64KB~512KB    |      |        | 160  | mA   |

|           | current 2           | inputs $\leq 0.2V$                | or $\geq$ Vcc-0.2V, |               |      |        |      |      |

|           |                     | Outputs=open                      |                     | 1MB~4MB       |      |        | 220  |      |

| Icc 2 • 1 | Standby supply      | CE1#=CE2#=                        | VIH                 | 64KB~4MB      |      |        | 10   | mA   |

|           | current 1           | Other inputs=                     | VIH or VIL          |               |      |        |      |      |

| Icc 2 • 2 | Standby supply      | CE1#=CE2# ≥                       | ≥ Vcc-0.2V          | 64KB~512KB    |      |        | 0.45 | mA   |

|           | current 2           | Other inputs ≤                    | ≤ 0.2V or           | 1MB~4MB       |      |        | 0.65 |      |

|           |                     | ≥ Vcc-0.2V                        | =                   |               |      |        |      |      |

| VBDET1    | Battery detect      | Vcc=5V, Ta=25°C                   |                     |               | 2.27 | 2.37   | 2.47 | V    |

|           | reference voltage 1 |                                   | , <del></del> -     |               |      |        |      |      |

| VBDET2    | Battery detect      | Vcc=5V, Ta=2                      | 25°C                |               | 2.55 | 2.65   | 2.75 | V    |

|           | reference voltage 2 |                                   |                     |               |      |        |      |      |

Note 2: Currents flowing into the card are taken as positive (unsigned).

# 14. CAPACITANCE

| Symbol Parameter |                    | Test conditions                       |  | Limits |      |      |  |

|------------------|--------------------|---------------------------------------|--|--------|------|------|--|

| Symbol           | Farameter          | Test conditions                       |  | Тур.   | Max. | Unit |  |

| CI               | Input capacitance  | VI=GND, vi=25mVrms<br>f=1MHz, Ta=25°C |  |        | 30   | pF   |  |

| Со               | Output Capacitance | Vo=GND, vo=25mVrms<br>f=1MHz, Ta=25°C |  |        | 20   | pF   |  |

Note 4: These parameters are not 100% tested.

<sup>3 :</sup> Typical values are measured at Vcc=5V, Ta=25°C.

# 15. SWITCHING CHARACTERISTICS

**Read Cycle** (Ta=0~55°C, VCC=5V±5%, unless otherwise noted)

| Symbol   | Parameter                              | Lin  | nits | Unit |

|----------|----------------------------------------|------|------|------|

|          |                                        | Min. | Max. |      |

| tcR      | Read cycle time                        | 150  |      | ns   |

| ta(A)    | Address access time                    |      | 150  | ns   |

| ta(CE)   | Card enable access time                |      | 150  | ns   |

| ta(OE)   | Output enable access time              |      | 75   | ns   |

| tdis(CE) | Output disable time (from CE#)         |      | 75   | ns   |

| tdis(OE) | Output disable time (from OE#)         |      | 75   | ns   |

| ten(CE)  | Output enable time (from CE#)          | 5    |      | ns   |

| ten(OE)  | Output enable time (from OE#)          | 5    |      | ns   |

| tv(A)    | Data valid time (after address change) | 0    |      | ns   |

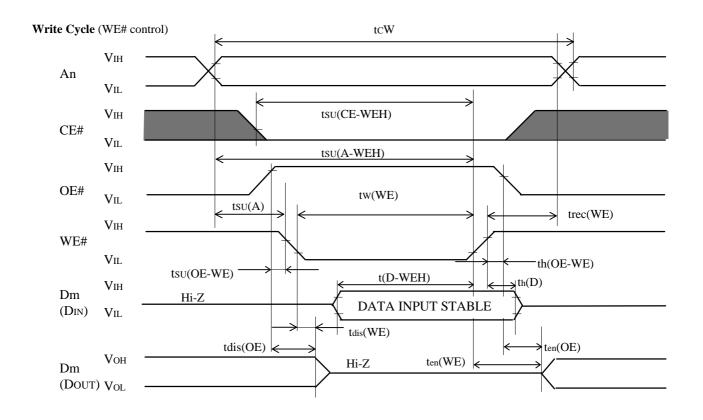

# **16. TIMING REQUIREMENTS**

Write Cycle (Ta=0~55°C, Vcc=5V±5%, unless otherwise noted)

| Symbol      | Parameter                                        | Lin  | nits | Unit |

|-------------|--------------------------------------------------|------|------|------|

|             |                                                  | Min. | Max. |      |

| tcW         | Write cycle time                                 | 150  |      | ns   |

| tw(WE)      | Write pulse width                                | 80   |      | ns   |

| tsu(A)      | Address set up time                              | 20   |      | ns   |

| tsu(A-WEH)  | Address set up time with respect to WE# high     | 100  |      | ns   |

| tsu(CE-WEH) | Card enable set up time with respect to WE# high | 100  |      | ns   |

| t(D-WEH)    | Data set up time with respect to WE# high        | 50   |      | ns   |

| th(D)       | Data hold time                                   | 20   |      | ns   |

| trec(WE)    | Write recovery time                              | 20   |      | ns   |

| tdis(WE)    | Output disable time (from WE#)                   |      | 75   | ns   |

| tdis(OE)    | Output disable time (from OE#)                   |      | 75   | ns   |

| ten(WE)     | Output enable time (from WE#)                    | 5    |      | ns   |

| ten(OE)     | Output enable time (from OE#)                    | 5    |      | ns   |

| tsu(OE-WE)  | OE# set up time with respect to WE# low          | 10   |      | ns   |

| th(OE-WE)   | OE# hold time with respect to WE# high           | 10   |      | ns   |

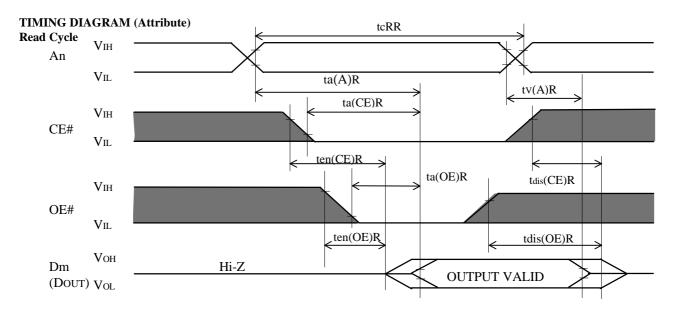

#### TIMING DIAGRAM Read Cycle tcR $V_{IH}$ An $V_{IL}$ ta(A) tv(A) ta(CE) $V_{IH}$ CE# $V_{IL} \\$ ten(CE) tdis(CE) $V_{IH}$ > ta(OE) OE# $V_{IL} \\$ ten(OE) tdis(OE) Von Hi-Z Dm **OUTPUT VALID** (DOUT) VOL

WE#="H" level REG#="H" level

REG#="H" level

# Write Cycle (CE# control)

OE#="H" level REG#="H" level

# 17. SWITCHING CHARACTERISTICS (Attribute)

**Read Cycle** (Ta=0~55°C, Vcc=5V±5%, unless otherwise noted)

| Symbol    | Parameter                            | Lin  | nits | Unit |

|-----------|--------------------------------------|------|------|------|

|           |                                      | Min. | Max. |      |

| tcRR      | Read cycle time                      | 300  |      | ns   |

| ta(A)R    | Address access time                  |      | 300  | ns   |

| ta(CE)R   | Card enable access time              |      | 300  | ns   |

| ta(OE)R   | Output enable access time            |      | 150  | ns   |

| tdis(CE)R | Output disable time (from CE#)       |      | 100  | ns   |

| tdis(OE)R | Output disable time (from OE#)       |      | 100  | ns   |

| ten(CE)R  | Output enable time (from CE#)        | 5    |      | ns   |

| ten(OE)R  | Output enable time (from OE#)        | 5    |      | ns   |

| tV(A)R    | Data valid time after address change | 0    |      | ns   |

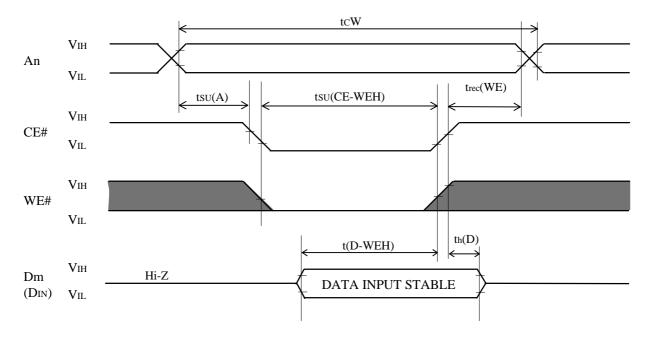

# 18. TIMING REQUIREMENTS (Attribute)

Write Cycle (Ta=0~55°C, Vcc=5V±5%, unless otherwise noted)

| Symbol      | Parameter                   | Lin  | nits | Unit |

|-------------|-----------------------------|------|------|------|

|             |                             | Min. | Max. |      |

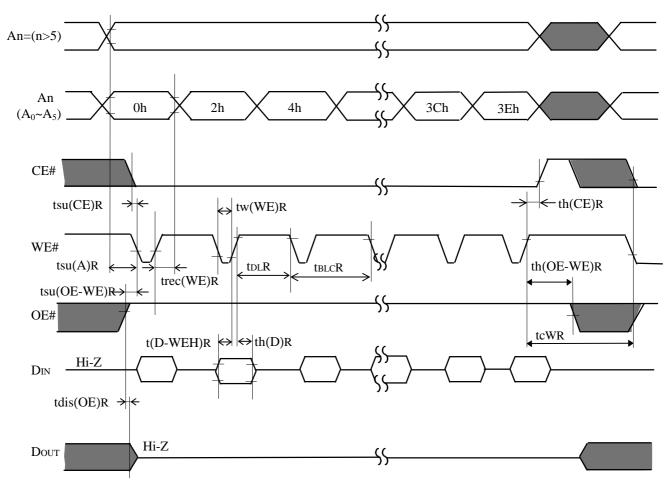

| tsu(A)R     | Address setup time          | 30   |      | ns   |

| tsu(CE)R    | CE# setup time              | 40   |      | ns   |

| th(CE)R     | CE# hold time               | 30   |      | ns   |

| t(D-WEH)R   | Data setup time             | 120  |      | ns   |

| th(D)R      | Data hold time              | 40   |      | ns   |

| tsu(OE-WE)R | OE# setup time              | 30   |      | ns   |

| th(OE-WE)R  | OE# hold time               | 40   |      | ns   |

| tw(WE)R     | Write pulse width           | 170  |      | ns   |

| tdlR        | Data latch time             | 120  |      | ns   |

| tBLCR       | Byte load cycle time        | 0.3  | 30   | μs   |

| tcWR        | Write cycle time            | 10   |      | ms   |

| ten(OE)R    | Output enable time from OE# | 5    |      | ns   |

| trec(WE)R   | Write recovery time         | 30   |      | ns   |

WE#="H" level REG#="L" level

## BYTE WRITE TIMING CHART

REG#="L" level

## PAGE MODE WRITE TIMING CHART

REG#="L" level

Note 5: Test Conditions

Input pulse levels : VIL=0.4V, VIH=2.8V

Input pulse rise, fall time : tr=tf=10ns

Reference voltage

$\begin{array}{ll} \text{Input} & : \text{Vil} = 0.8 \text{V}, \text{Vih} = 2.4 \text{V} \\ \text{Output} & : \text{Vol} = 0.8 \text{V}, \text{Voh} = 2.0 \text{V} \\ \end{array}$

(ten and tdis are measured when output voltage is  $\pm$  500mV from steady state.)

Load : 100pF + 1 TTL gate

5pF + 1 TTL gate (at ten and tdis measuring)

6: Indicates the don't care input

7: Writing is executed in overlap of CE# and WE# are "L" level. (only for Common Memory)

8 : Don't apply inverted phase signal externally when Dm pin is in output mode.

9 : CE# is indicated as follows:

Read A/Write A: CE#=CE1#=CE2#

Read B/Write B : CE#=CE1#, CE2#="H" level Read C/Write C : CE#=CE2#, CE1#="H" level

# 19. ELECTRICAL CHARACTERISTICS

# **BATTERY BACKUP** (Ta=0~55°C, unless otherwise noted)

| Symbol | Parameter                      | Test condi     | ions  |         | Limits |         | Unit |

|--------|--------------------------------|----------------|-------|---------|--------|---------|------|

|        |                                |                |       | Min.    | Тур.   | Max.    |      |

| VBATT  | Back-up enable battery voltage | All pins open  |       | 2.6     |        |         | V    |

| Vi(CE) | Card enable voltage            | 2.4V≤VCC≤5.25° | V     | 2.4     |        |         | V    |

|        |                                | 0V≤VCC<2.4V    |       | Vcc-0.1 | Vcc    | Vcc+0.1 |      |

|        |                                |                | 64KB  |         |        | 3       |      |

|        |                                |                | 128KB |         |        | 3       |      |

|        |                                | All pins open, | 256KB |         |        | 3       |      |

|        | Battery back-up supply current | VBATT=3V,      | 512KB |         |        | 5       | μΑ   |

|        |                                | Ta=25°C        | 1MB   |         |        | 3       |      |

|        |                                |                | 2MB   |         |        | 5       |      |

| Icc    |                                |                | 4MB   |         |        | 9       |      |

| (Bup)  |                                |                | 64KB  |         |        | 30      |      |

|        |                                |                | 128KB |         |        | 30      |      |

|        |                                | All pins open, | 256KB |         |        | 30      |      |

|        | Battery back-up supply current | VBATT=3V       | 512KB |         |        | 50      | μΑ   |

|        |                                |                | 1MB   |         | •      | 30      |      |

|        |                                |                | 2MB   |         | •      | 50      |      |

|        |                                |                | 4MB   |         | •      | 90      |      |

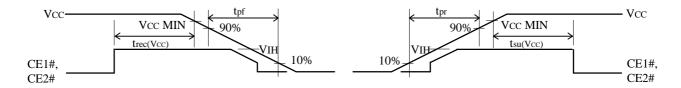

# **20. TIMING REQUIREMENTS** (Ta=0~55°C, unless otherwise noted)

| Symbol    | Parameter                  | Limits |      |      | Unit |

|-----------|----------------------------|--------|------|------|------|

|           |                            | Min.   | Тур. | Max. |      |

| tpr       | Power supply rise time     | 0.1    |      | 300  | ms   |

| tpf       | Power supply fall time     | 3      |      | 300  | ms   |

| tsu(Vcc)  | Setup time at power on     | 20     |      |      | ms   |

| trec(Vcc) | Recovery time at power off | 1000   |      |      | ns   |

## CARD INSERTION/REMOVAL TIMING DIAGRAM

## 21. BATTERY SPECIFICATIONS

Please use the following coin type lithium battery.

Type of main battery; CR2025 or equivalents

## 21.1 BATTERY LIFE EXPECTANCY

The calculated main battery's life expectancies are as follows.

| Card Type      | main battery's life<br>(when the card is<br>left continuously) |

|----------------|----------------------------------------------------------------|

| MF365A-LZCATXX | 5.9years                                                       |

| MF3129-LZCATXX | 5.9years                                                       |

| MF3257-LZCATXX | 5.9years                                                       |

| MF3513-LZCATXX | 3.6years                                                       |

| MF31M1-LZCATXX | 5.9years                                                       |

| MF32M1-LZCATXX | 3.6years                                                       |

| MF34M1-LZCATXX | 2.0years                                                       |

Conditions; Temperature : 25°C Humidity : 60%RH

#### 22. CONNECTOR

The number of card insertion and removal are as follows.

Office environment 10000 times min. at speed of 10 cycles/min. Harsh environment 5000 times min. at speed of 10 cycles/min.

# **23. CARD WEIGHT** about 30g

#### 24. UL CLASS OF MAIN CARD PARTS

(1)MAIN FRAME UL94V-0 (2)PCB UL94V-0 (3)PLASTIC PART OF CONNECTOR UL94V-0

## 25. THE BATTERY VOLTAGE DETECT SIGNALS (BVD1,2)

| BVD1 | BVD2 | Comment                                             |  |

|------|------|-----------------------------------------------------|--|

| Н    | Н    | Battery operational                                 |  |

| Н    | L    | Battery operational, but battery should be replaced |  |

| L    | L    | Battery and data integrity is not kept              |  |

Note10. The battery voltage detect signals indicate the present state of the battery. They do not guarantee the data retention.

## 26.CONCERNING THE SECURITY OF DATA

There is always the possibility that a soft-error (this malfunction is not permanent hence it is called soft and the data can be restored by rewriting) may occur with semiconductor products.

When keeping the important data within an IC card, remember to give due consideration to safety when making your circuit designs, with appropriate measures such as

- (1) Keeping multiple copies of the data.

- (2) Addition of ECC or CRC by software or hardware.

# – $\triangle$ Warning ( if card with battery / card with auxiliary battery ) –

- (1)Do not charge, short, disassemble, deform, heat, or throw the batteries into fire, as they may ignite, overheat, rupture or explode.

- (2)Place the batteries out of the reach of children. If somebody swallows them, they should see a doctor immediately.

- (3)When discarding or storing the batteries, wrap them individually with cellophane tape or other nonconductive material. If they are positioned in contact with any other metals or batteries, they may explode, rupture or leak electrolyte solution.

# - /!\ Caution

This product is not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for a special applications, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

## Keep safety first in your circuit designs!

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (1)placement of substitutive, auxiliary circuits,(2)use of non-flammable material or (3)prevention against any malfunction or mishap.

#### Notes regarding these materials

- •These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams and charts, represent

information on products at the time of publication of these materials, and are subject to change by Mitsubishi

Electric Corporation without notice due to product improvements or other reasons. It is therefore

recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi

Semiconductor product distributor for the latest product information before purchasing a product listed

herein.

- For instruction on proper use of the IC card, thoroughly read the manual attached to the product before use. After reading please store the manual in s safe place for future reference.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than approved destination. Any diversion or re-export contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

# OUTLINE(68P-012)