Preliminary

## Single-Chip 8-BIT CMOS Microcontroller M37640E8-XXXFP Specification

Ver 1.04

This publication, or any parts thereof, may not be reproduced in any form without the prior written permission of Mitsubishi Semiconductor America, Inc. (MSAI).

The product(s) described in this publication are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the product could create a situation where personal injury or death may occur. Should Buyer purchase or use this product for any such unintended or unauthorized application, Buyer shall indemnify and hold MSAI and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that MSAI was negligent regarding the design and manufacture of the part.

Rev. 1.0Internal ReleaseApril 2, 1997Rev. 1.01Design Spec UpdatesJuly 1, 1997Rev. 1.02Design Spec UpdatesAugust 28, 1997Rev. 1.03Internal Spec UpdatesJan. 22, 1998Rev. 1.04Design Spec UpdatesJune 2, 1998

Information supplied by MSAI is believed to be accurate and reliable. MSAI assumes no responsibility for any errors that may appear in this publication. MSAI reserves the right, without notice, to make changes in device design or specifications. Product is subject to availability. ©1997 Mitsubishi Semiconductor America, Inc.

#### **1** Overview

| 1.1 MCU Features               | 1-5 |

|--------------------------------|-----|

| 1.2 Pin Description and Layout | 1-6 |

### **2** Functional Description

| 2.1 Central Processing Unit                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

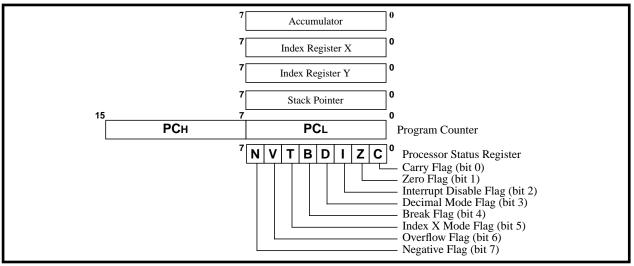

| 2.1.1 Register Structure                                                                                              | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1.2 Accumulator (A)                                                                                                 | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1.3 Index Registers X and Y                                                                                         | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1.4 Stack Pointer                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.1.5 Program Counter                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.1.6 Processor Status Register                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

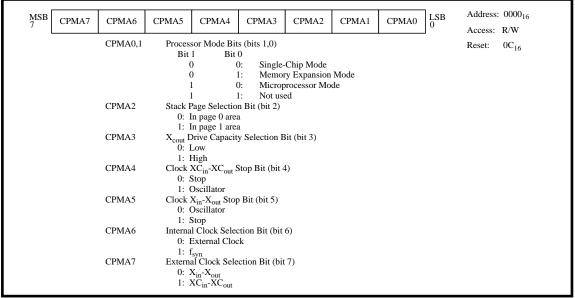

| 2.2 CPU Mode Registers                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.3 Oscillator Circuit                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.3.1 Description                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

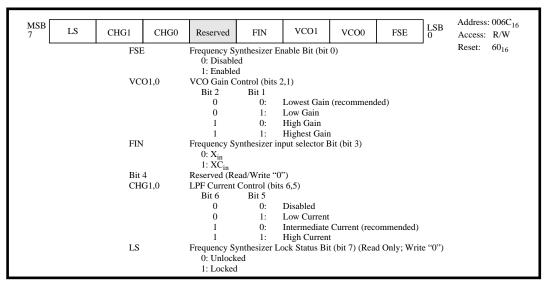

| 2.3.2 Frequency Synthesizer Circuit                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

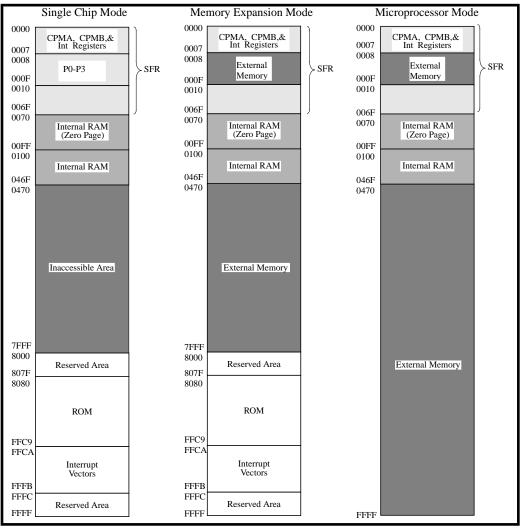

| 2.4 Memory Map                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.4.1 Zero page                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.4.2 Special Page                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.4.3 Special Function Registers                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.5 Processor Modes                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.5.1 Single Chip                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.5.2 Memory Expansion                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.5.3 Microprocessor                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.5.4 EPROM                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

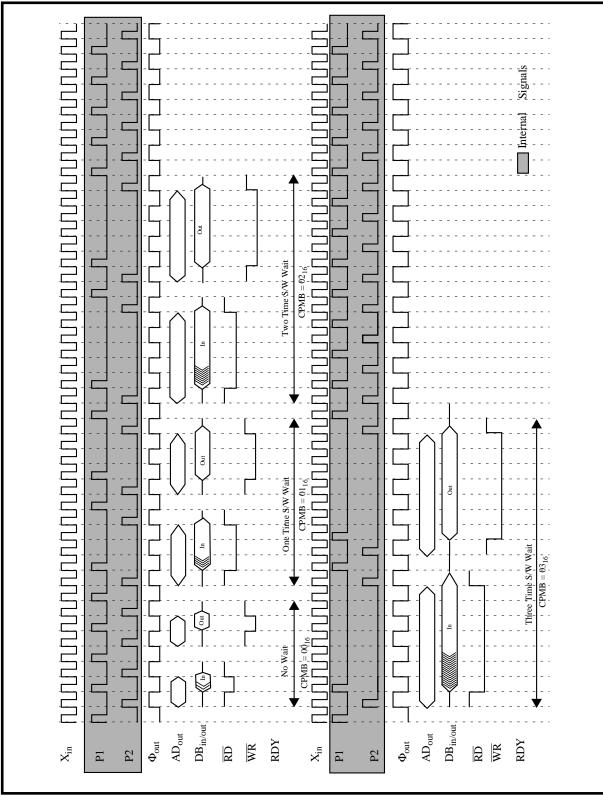

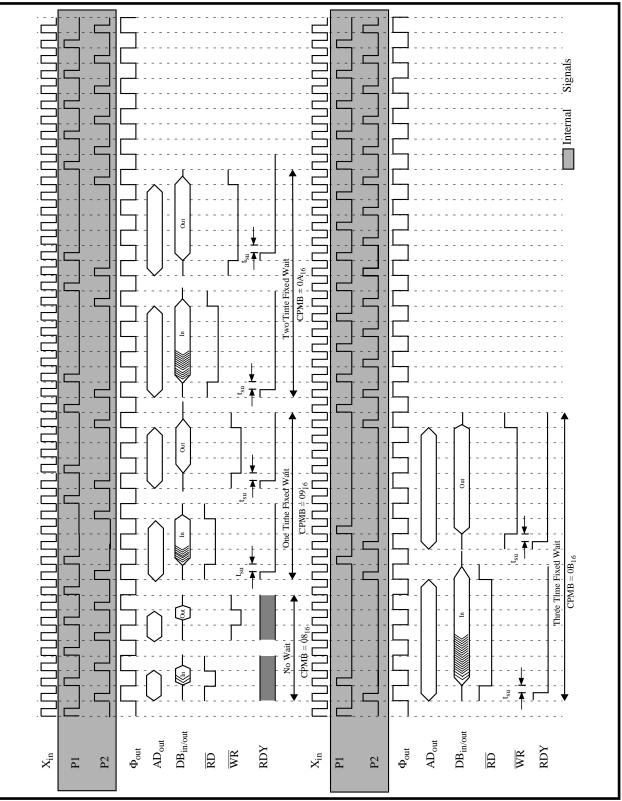

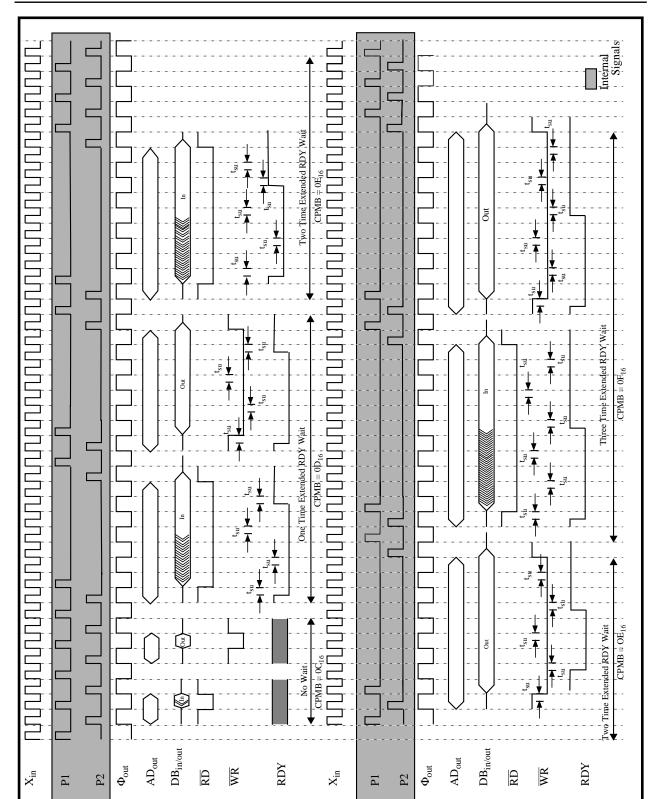

| 2.5.5 Slow Memory Wait                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

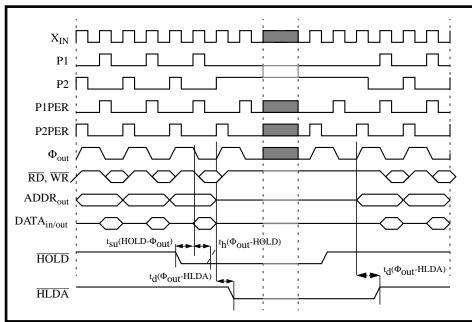

| 2.5.6 Hold Function                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.5.7 Expanded Data Memory Access                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.6 Peripheral Interface                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2 C 1 Chin Deer Timin a                                                                                               | 2 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

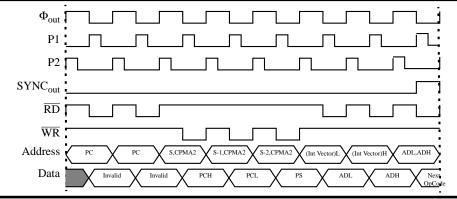

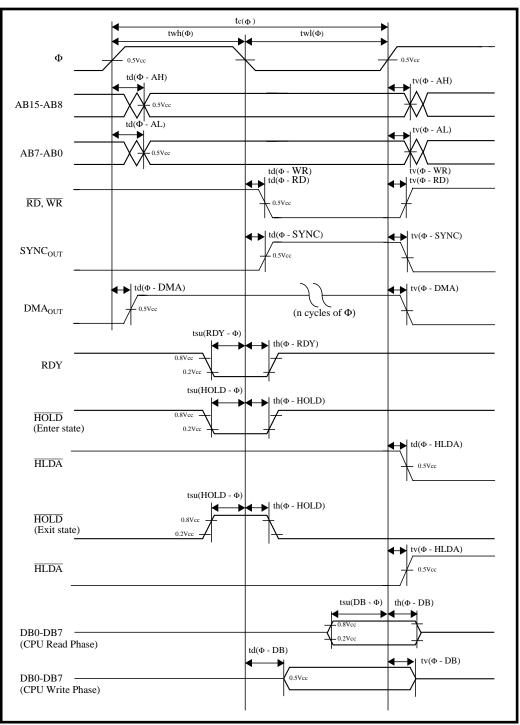

| 2.6.1 Chip Bus Timing                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

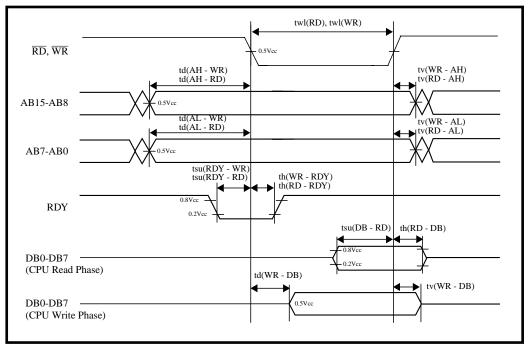

| 2.6.2 Peripheral Interface and Access Timing                                                                          | 2-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul><li>2.6.2 Peripheral Interface and Access Timing</li><li>2.7 Input and Output Ports</li></ul>                     | 2-26<br>2-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul><li>2.6.2 Peripheral Interface and Access Timing</li><li>2.7 Input and Output Ports</li><li>2.7.1 Ports</li></ul> | 2-26<br>2-28<br>2-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul><li>2.6.2 Peripheral Interface and Access Timing</li><li>2.7 Input and Output Ports</li><li>2.7.1 Ports</li></ul> | 2-26<br>2-28<br>2-28<br>2-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>2.6.2 Peripheral Interface and Access Timing</li> <li>2.7 Input and Output Ports</li></ul>                   | 2-26<br>2-28<br>2-28<br>2-29<br>2-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>2.6.2 Peripheral Interface and Access Timing</li> <li>2.7 Input and Output Ports</li></ul>                   | 2-26<br>2-28<br>2-28<br>2-29<br>2-40<br>2-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>2.6.2 Peripheral Interface and Access Timing</li> <li>2.7 Input and Output Ports</li></ul>                   | 2-26<br>2-28<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>2.6.2 Peripheral Interface and Access Timing</li> <li>2.7 Input and Output Ports</li></ul>                   | 2-26<br>2-28<br>2-28<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <ul> <li>2.6.2 Peripheral Interface and Access Timing</li> <li>2.7 Input and Output Ports</li></ul>                   | 2-26<br>2-28<br>2-28<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.6.2 Peripheral Interface and Access Timing<br>2.7 Input and Output Ports                                            | 2-26<br>2-28<br>2-28<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>2.6.2 Peripheral Interface and Access Timing</li> <li>2.7 Input and Output Ports</li></ul>                   | 2-26<br>2-28<br>2-28<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>2.6.2 Peripheral Interface and Access Timing</li> <li>2.7 Input and Output Ports</li></ul>                   | 2-26<br>2-28<br>2-28<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>2.6.2 Peripheral Interface and Access Timing</li> <li>2.7 Input and Output Ports</li></ul>                   | 2-26<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                  | 2-26<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                  | 2-26<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.6.2 Peripheral Interface and Access Timing<br>2.7 Input and Output Ports                                            | 2-26<br>2-28<br>2-28<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.6.2 Peripheral Interface and Access Timing<br>2.7 Input and Output Ports                                            | 2-26<br>2-28<br>2-28<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.6.2 Peripheral Interface and Access Timing<br>2.7 Input and Output Ports                                            | 2-26<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.6.2 Peripheral Interface and Access Timing<br>2.7 Input and Output Ports                                            | 2-26<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-42<br>2-42<br>2-42<br>2-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.6.2 Peripheral Interface and Access Timing<br>2.7 Input and Output Ports                                            | 2-26<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41 |

| 2.6.2 Peripheral Interface and Access Timing<br>2.7 Input and Output Ports                                            | 2-26<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-42<br>2-42<br>2-43<br>2-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.6.2 Peripheral Interface and Access Timing<br>2.7 Input and Output Ports                                            | 2-26<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-42<br>2-42<br>2-43<br>2-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.6.2 Peripheral Interface and Access Timing<br>2.7 Input and Output Ports                                            | 2-26<br>2-28<br>2-29<br>2-29<br>2-40<br>2-40<br>2-40<br>2-40<br>2-40<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-41<br>2-42<br>2-42<br>2-43<br>2-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Mitsubishi<br>Semiconductor Corporation      |        |

|----------------------------------------------|--------|

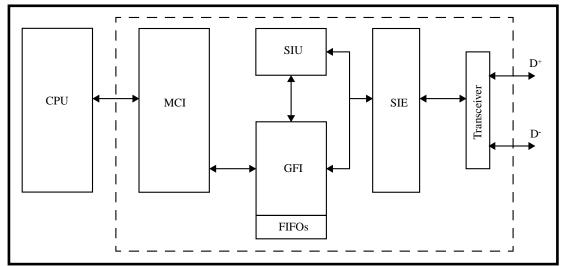

| 2.9.1 USB Function Control Unit (USB FCU)    | ) 2-50 |

| 2.9.1.1 Serial Interface Engine              |        |

| 2.9.1.2 Generic Function Interface           |        |

| 2.9.1.3 Serial Engine Interface Unit         | 2-50   |

| 2.9.1.4 Microcontroller Interface Unit       |        |

| 2.9.1.5 USB Transceiver                      |        |

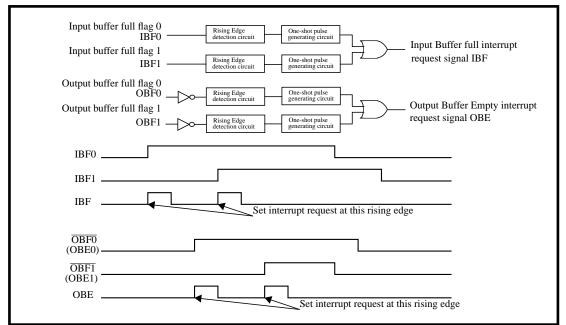

| 2.9.2 USB Interrupts                         |        |

| 2.9.2.1 USB Function Interrupt               |        |

| 2.9.2.2 USB SOF Interrupt                    |        |

| 2.9.3 USB Endpoint FIFOs                     | 2-52   |

| 2.9.3.1 IN (Transmit) FIFOs                  |        |

| 2.9.3.2 Out (Receive) FIFOs                  |        |

| 2.9.4 USB Special Function Registers         |        |

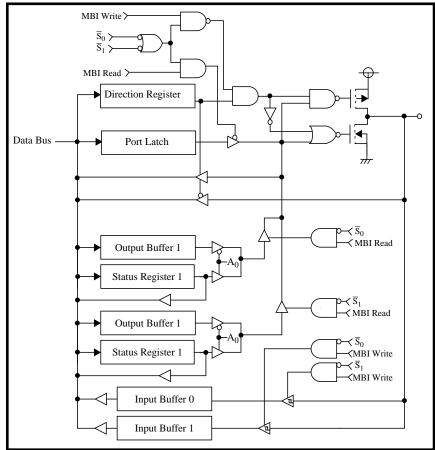

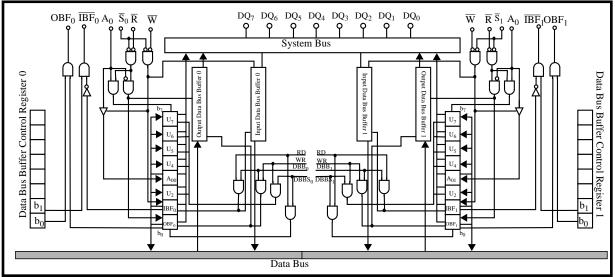

| 2.10 Master CPU Bus Interface                |        |

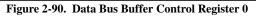

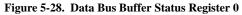

| 2.10.1 Data Bus Buffer Status Registers      |        |

| (DBBS0, DBBS1)                               | 2-68   |

| 2.10.2 Input Data Bus Buffer Registers       |        |

| (DBBIN0, DBBIN1)                             | 2-68   |

| 2.10.3 Output Data Bus Buffer Registers      |        |

| (DBBOUT0, DBBOUT1)                           | 2-68   |

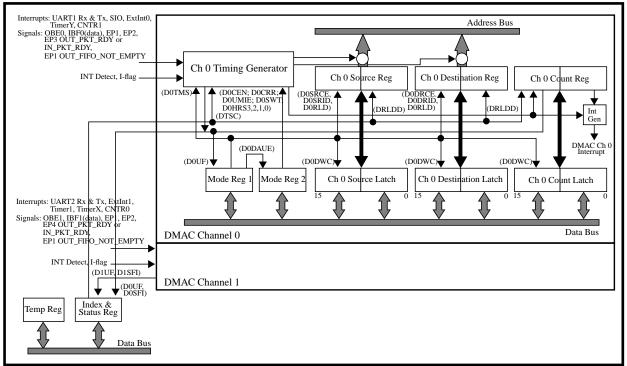

| 2.11 Direct Memory Access Controller         |        |

| 2.11.1 Operation                             |        |

| 2.11.1.1 Source, Destination, and Transfer ( |        |

| Register Operation                           |        |

| 2.11.1.2 DMAC Transfer Request Sources .     |        |

| 2.11.1.3 Transfer Features for USB and MB    | I2-72  |

| 2.11.1.4 DMAC Transfer Mode                  | 2-74   |

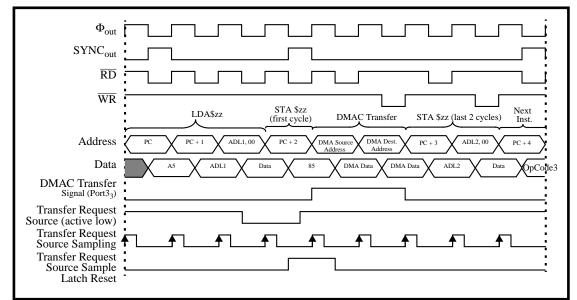

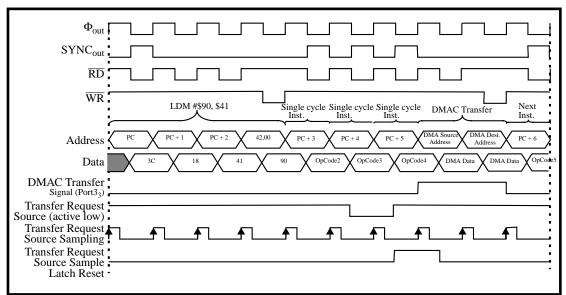

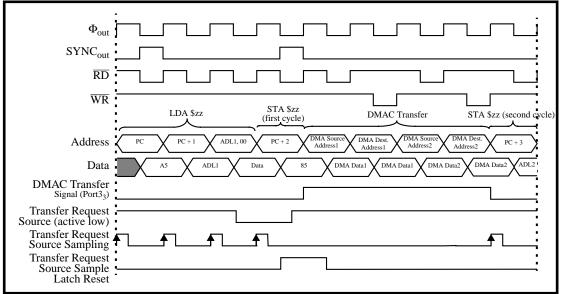

| 2.11.1.5 DMAC Transfer Timing                | 2-74   |

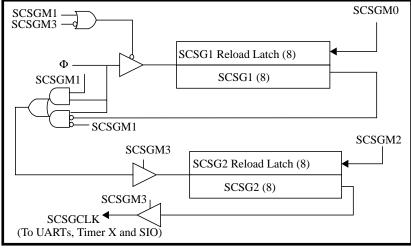

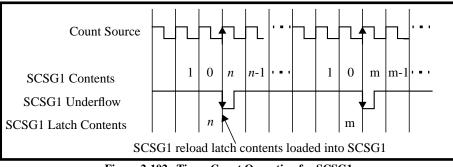

| 2.12 Special Count Source Generator          | 2-79   |

| 2.12.1 SCSG Operation                        | 2-79   |

| 2.12.2 SCSG Description                      | 2-80   |

| 2.12.2.1 SCSG1                               |        |

| 2.12.2.2 SCSG2                               | 2-80   |

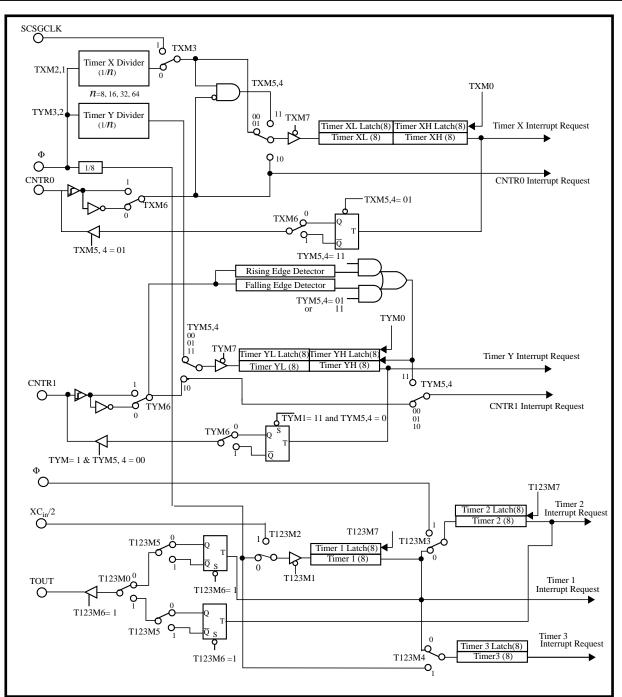

| 2.13 Timers                                  | 2-82   |

| 2.13.1 Timer X                               | 2-82   |

| 2.13.1.1 Read and Write Method               | 2-82   |

| 2.13.1.2 Count Stop Control                  | 2-83   |

| 2.13.1.3 Timer Mode                          | 2-83   |

| 2.13.1.4 Pulse Output Mode                   | 2-83   |

| 2.13.1.5 Event Counter Mode                  | 2-84   |

| 2.13.1.6 Pulse Width Measurement Mode        | 2-84   |

| 2.13.2 Timer Y                               |        |

| 2.13.2.1 Read and Write Method               | 2-85   |

| 2.13.2.2 Count Stop Control                  | 2-85   |

2.13.2.4 Pulse Period Measurement Mode ...... 2-86 2.13.2.6 HL Pulse-width Measurement Mode.. 2-86 2.13.3 Timer 1 ...... 2-87 2.13.3.2 Pulse Output Mode ...... 2-87 2.13.4.2 Pulse Output Mode ...... 2-88

| 2.13.5 Timer 3                  |  |

|---------------------------------|--|

| 2.13.5.1 Timer Mode             |  |

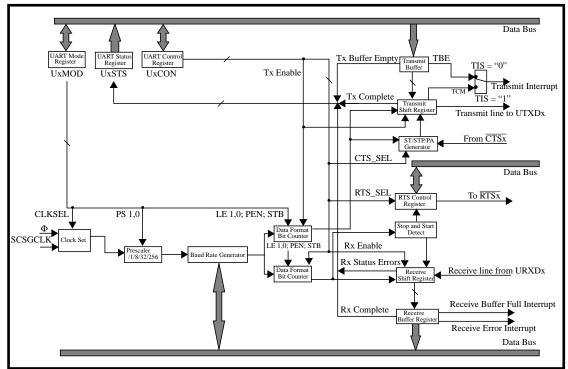

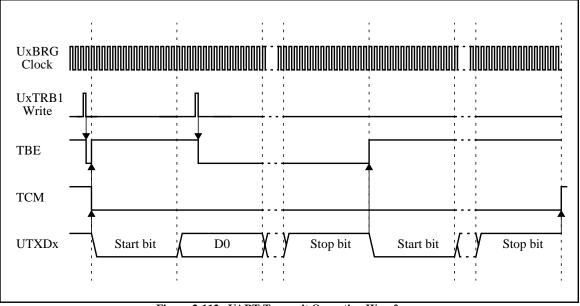

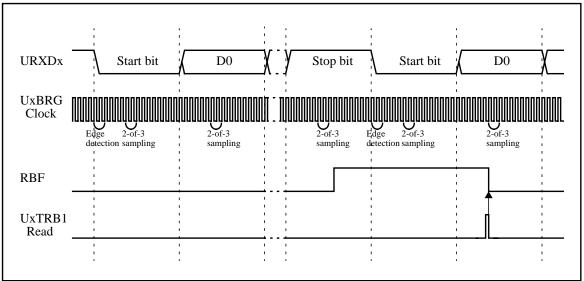

| 2.14 UART                       |  |

| 2.14.1 Baud Rate Selection      |  |

| 2.14.2 UART Mode Register       |  |

| 2.14.3 UART Control Register    |  |

| 2.14.4 UART Baud Rate Register  |  |

| 2.14.5 UART Status Register     |  |

| 2.14.6 Transmit/Receive Format  |  |

| 2.14.7 Interrupts               |  |

| 2.14.8 Clear-to Send (CTSx) and |  |

| Request-to-Send (RTSx) Signals  |  |

| 2.14.9 UART Address Mode        |  |

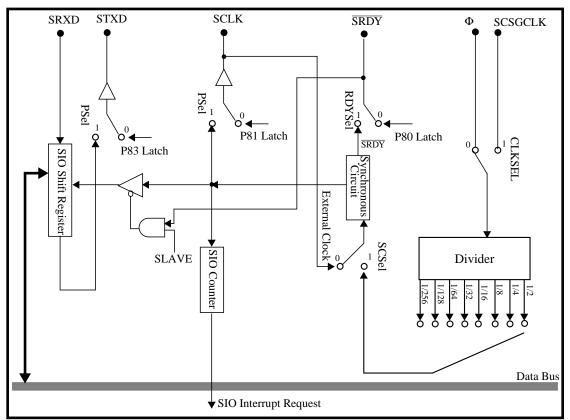

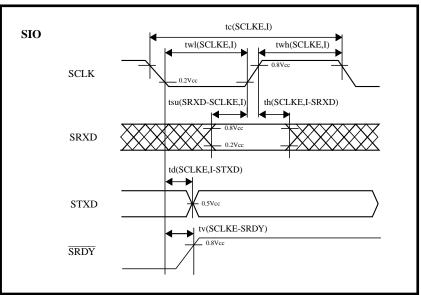

| 2.15 Serial I/O                 |  |

| 2.15.1 SIO Control Register     |  |

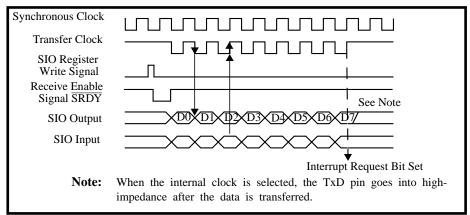

| 2.15.2 SIO Operation            |  |

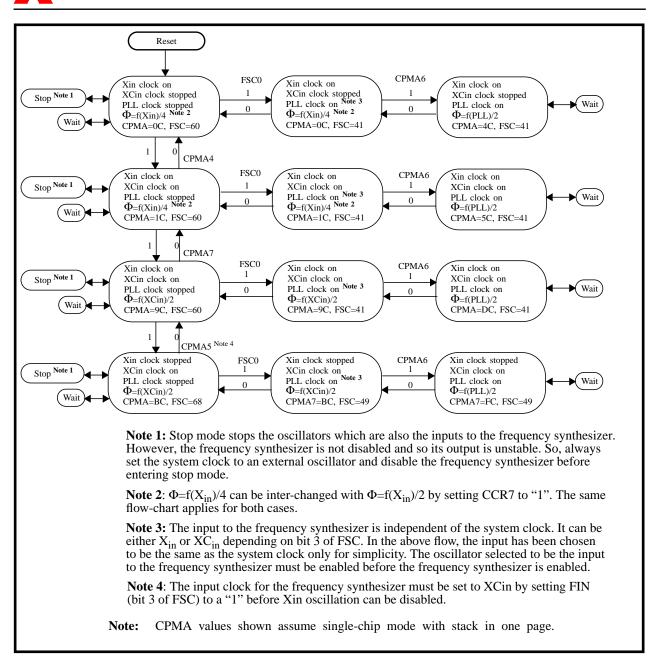

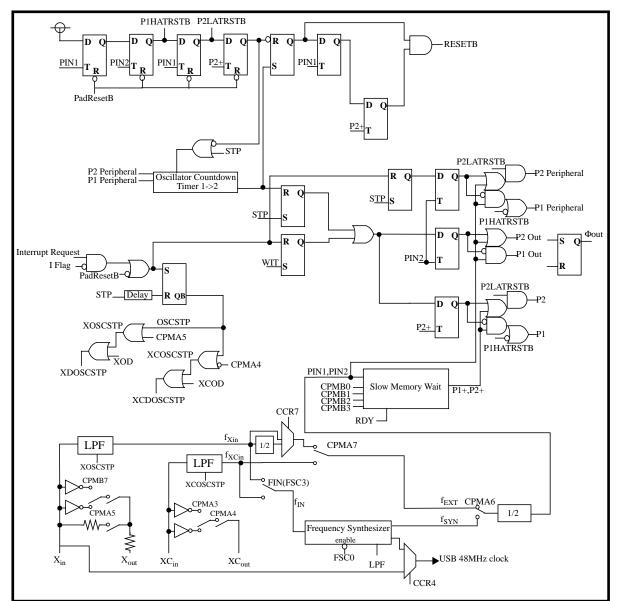

| 2.16 Low Power Modes            |  |

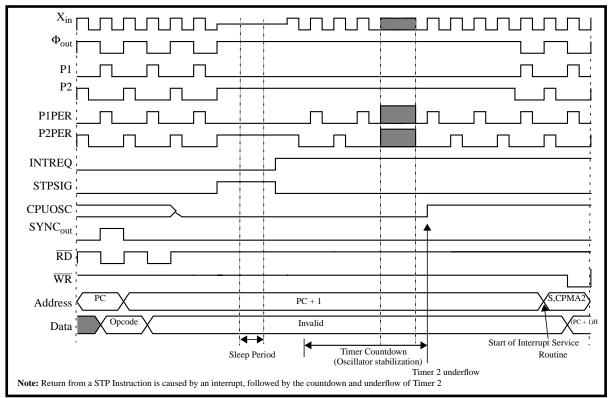

| 2.16.1 Stop Mode                |  |

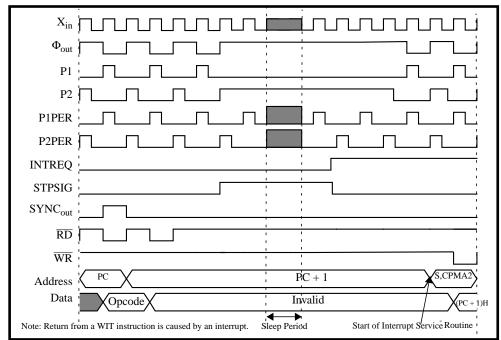

| 2.16.2 Wait Mode                |  |

| 2.17 Reset                      |  |

| 2.18 Key-On Wake-Up             |  |

|                                 |  |

### **3 Electrical Characteristics**

| 3.1 Absolute Maximum Ratings         | . 3-3 |

|--------------------------------------|-------|

| 3.2 Recommended Operating conditions | . 3-4 |

| 3.3 Electrical Characteristics       | . 3-6 |

| 3.4 Timing Requirements and          |       |

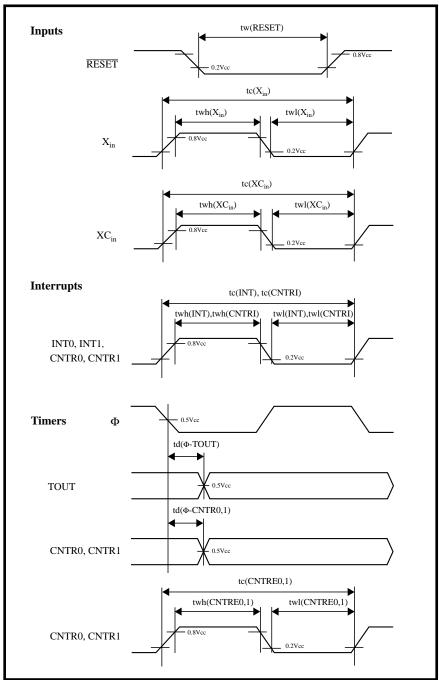

| Switching Characteristics            | . 3-8 |

### **4** Application Notes

| 4.1 DMAC                            |  |

|-------------------------------------|--|

| 4.1.1 Application                   |  |

| 4.2 UART                            |  |

| 4.2.1 Application                   |  |

| 4.3 Timer                           |  |

| 4.3.1 Usage                         |  |

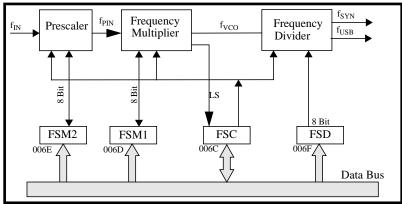

| 4.4 Frequency Synthesizer Interface |  |

| 4.5 USB Transceiver                 |  |

| 4.6 Ports                           |  |

| 4.7 Programming Notes               |  |

|                                     |  |

### 5 Register List

MITSUBISHI SEMICONDUCTOR AMERICA, INC.

## PRELIMINARY

## Chapter 1 PRODUCT DESCRIPTION

| 1 C | Overview                   | 1-3 |

|-----|----------------------------|-----|

| 1.1 | MCU Features               | 1-5 |

| 1.2 | Pin Description and Layout | 1-6 |

## 1 Overview

Mitsubishi Microcomputer

The 7600 series, an enhanced family of CMOS 8-bit microcontrollers, offers high-speed operation at low voltage, large internal-memory options, and a wide variety of standard peripherals. The series is code compatible with the M38000, M37200, M37400, and the M37500 series, and provides many performance enhancements to the instruction set.

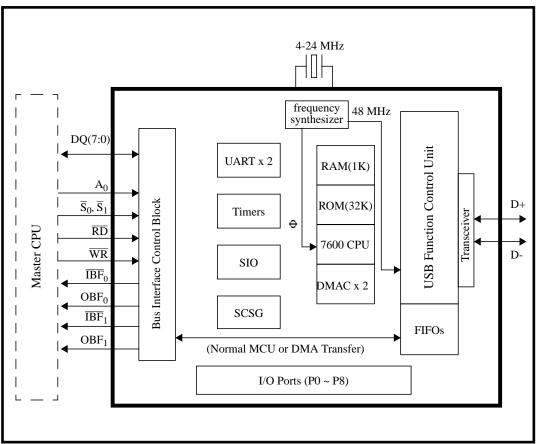

This device is a single chip PC peripheral microcontroller based on the Universal Serial Bus (USB) Version 1.0 specification. This device provides data exchange between a USB-equipped host computer and PC peripherals such as telephones, audio systems and digital cameras. See Figure 1-1 for an application system diagram.

The USB function control unit can support all four data transfer types listed in the USB specification: Control, Isochronous, Interrupt, and Bulk. Each transfer type is used for controlling a different set of PC peripherals. Isochronous transfers provide guaranteed bus access, a constant data rate, and error tolerance for devices such as computer-telephone integration (CTI) and audio systems. Interrupt transfers are designed to support human input devices (HID) that communicate small amounts of data infrequently. Bulk transfers are necessary for devices such as digital cameras and scanners that communicate large amounts of data to the PC as bus bandwidth becomes free. Finally, control transfers are supported and are useful for bursty, host-initiated type communication where bus management is the primary concern.

Figure 1-1. Application System Diagram

#### 7600 Series M37640E8-XXXF Preliminary Specification

| Parameter                             |                      |     | Function Description                                                                                                                                                                                                                  |  |

|---------------------------------------|----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number of basic instructions          |                      |     | 71                                                                                                                                                                                                                                    |  |

| Instruction execution time (minimum)  |                      |     | 83ns at $\Phi = 12$ MHz (setting $\Phi$ to less than 5MHz is NOT recommended)                                                                                                                                                         |  |

| Clock frequency (maximum)             |                      |     | Xin = 48 MHz, XC <sub>in</sub> = 5 MHz (square wave), $\Phi = 12$ MHz                                                                                                                                                                 |  |

| Clock multiplier option               |                      |     | External clock $X_{in}$ and $XC_{in}$ can be selectively divided and multiplied by X to create system internal clock $\Phi$                                                                                                           |  |

|                                       | ROM                  |     | 32K bytes                                                                                                                                                                                                                             |  |

| Memory size                           | RAM                  |     | 1K bytes                                                                                                                                                                                                                              |  |

| Input/Output ports                    | P0~P3, P5, P6,<br>P8 | I/O | 8-bit X 7 (Port 2 has a key-on wake-up feature)                                                                                                                                                                                       |  |

|                                       | P4, P7               | I/O | 5-bit X 2                                                                                                                                                                                                                             |  |

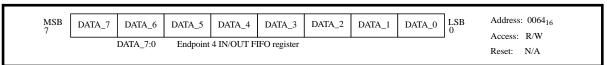

| USB Function Control                  |                      |     | FIFO:<br>Endpoint 0: IN 16-byte OUT 16-byte<br>Endpoint 1: IN 512-byteOUT 800-byte<br>Endpoint 2: IN 32-byte OUT 32-byte<br>Endpoint 3: IN 16-byte OUT 16-byte<br>Endpoint 4: IN 16-byte OUT 16-byte                                  |  |

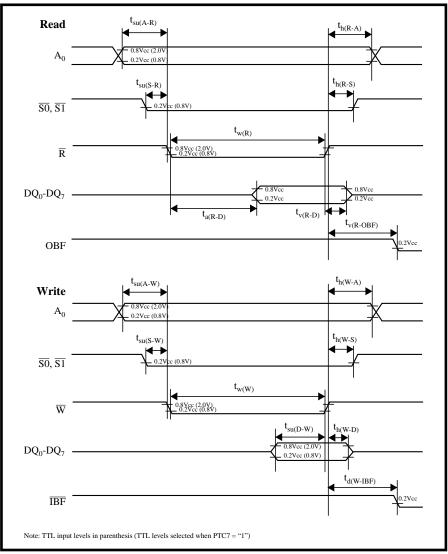

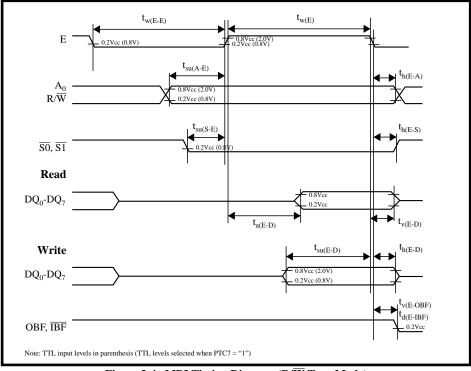

| Master CPU bus interface              |                      |     | $\overline{DQ}(7:0), \overline{R}(E), \overline{W}(R/\overline{W}), \overline{S}_0, \overline{S}_1, A_0, \overline{IBF}_0, OBF_0, \overline{IBF}_1, OBF_1;$ total of 17 signals interface with master CPU (Intel 8042-like interface) |  |

| Special Count Source                  | Generator(SCSG)      |     | Baud rate synthesizer                                                                                                                                                                                                                 |  |

| UART X 2                              |                      |     | 7/8/9-bit character length, with $\overline{\text{CTS}}$ , $\overline{\text{RTS}}$ available                                                                                                                                          |  |

| Serial I/O                            |                      |     | 8-bit clock synchronous serial I/O, supports both master and slave modes                                                                                                                                                              |  |

| Timers                                |                      |     | 8-bit X 3, 16-bit X 2                                                                                                                                                                                                                 |  |

| DMAC                                  |                      |     | 2 channels, 16 address lines, support single byte or burst transfer modes                                                                                                                                                             |  |

| Software selectable slew rate control |                      |     | Ports P0 ~ P8                                                                                                                                                                                                                         |  |

| Interrupts                            |                      |     | 4 external, 19 internal, 1 software, 1 system interrupts                                                                                                                                                                              |  |

| Supply voltage                        |                      |     | $V_{cc} = 4.15 \sim 5.25 V$                                                                                                                                                                                                           |  |

| External memory expansion             |                      |     | Memory Expansion and Microprocessor mode                                                                                                                                                                                              |  |

| External Data Memory Access (EDMA)    |                      |     | Allows > 64 Kbyte data access for instruction LDA (indY) and STA (indY)                                                                                                                                                               |  |

| Device structure                      |                      |     | CMOS                                                                                                                                                                                                                                  |  |

| Package                               |                      |     | 80P6N                                                                                                                                                                                                                                 |  |

| Operating temperature range           |                      |     | -20 to 85°C                                                                                                                                                                                                                           |  |

|                                       |                      |     |                                                                                                                                                                                                                                       |  |

Table 1-1. Device Feature List

1-4

### 1.1 MCU Features

- 7600 8-bit CPU core, CMOS process

- Minimum instruction execution time of 83ns (1-cycle instruction @  $\Phi$  = 12 MHz)

- Efficient software support (C and/or Assembly)

- ROM: 32 KB on-chip

- RAM: 1 KB on-chip

- Built-in Microprocessor or Memory-expansion modes

- Three slow memory wait modes: Software Wait, RDY Wait, and Extended RDY Wait

- Nine I/O Ports, total 66 programmable I/O pins available

- · Programmable direction control on every I/O pin

- Software selectable slew rate control on every I/O pin

- Master CPU Bus Interface:

- · MCU can be operated in slave mode by control signals from the host CPU

- 8 data lines (DQ7-DQ0) and  $\overline{R}(E)$ ,  $\overline{W}(R/\overline{W})$ ,  $A_0$ ,  $\overline{S}_0$ ,  $\overline{S}_1$ ,  $\overline{IBF}_0$ ,  $OBF_0$ ,  $\overline{IBF}_1$ ,  $OBF_1$  signals available

- Master CPU sends and receives data, command, and status by means of DQ7-DQ0

- USB Function Control Unit

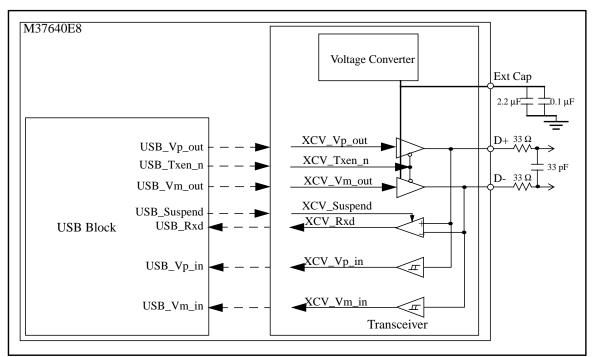

- USB Transceiver (conforms to USB V1.0 Specification)

- DMA Controller:

- Two DMA channels available

- 16 address lines for 64K byte address space

- Single byte or burst transfer modes

- Transfer request by external pins, software triggers or built-in peripherals

- Maximum 6M byte/sec transfer speed (in burst mode)

- Timers: three 8-bit timers and two 16-bit timers available

- Two full duplex UARTs available

- · One master/slave clock synchronous I/O (SIO), internal or external clock selectable

- Built-in Special Count Source Generator (SCSG): can be a clock source for Timer X, UARTs, and SIO

- · Power-saving wait (IDLE) and stop (powerdown) modes.

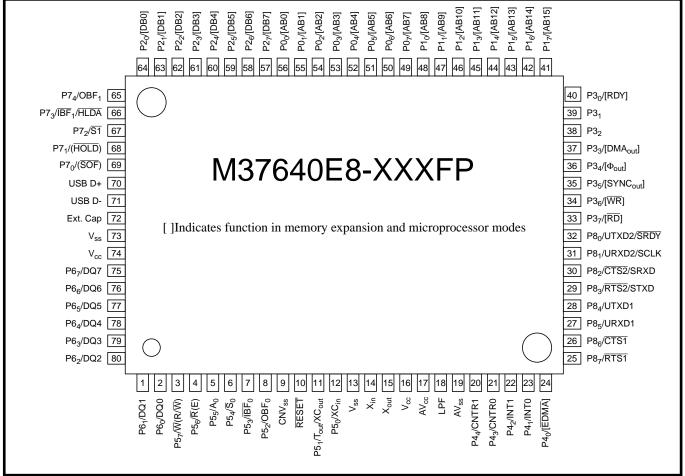

## 1.2 Pin Description and Layout

Figure 1-2. Pin Layout

| Name                                                     | I/O | Description                                                                                                                                                                                                                                                                                                                  | Pin #         |  |  |  |

|----------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|

| P0 <sub>0</sub> /AB0<br>~ P1 <sub>7</sub> /AB15          | I/O | CMOS I/O port (address bus). When the MCU is in memory expansion or microprocessor mode, these pins function as the address bus.                                                                                                                                                                                             | 56-41         |  |  |  |

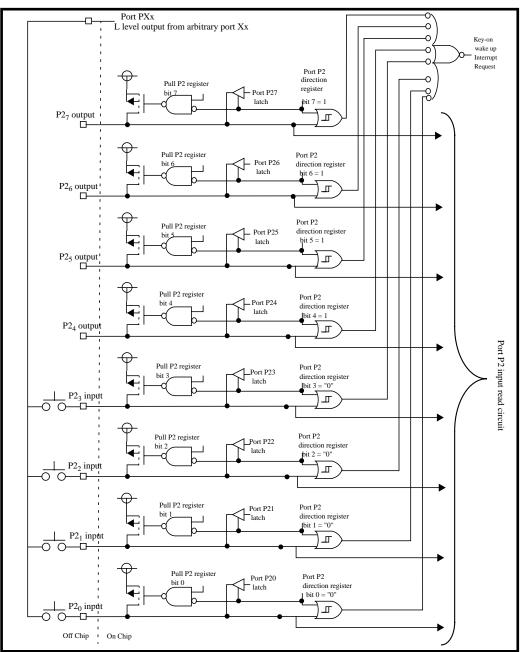

| P2 <sub>0</sub> /DB0<br>~ P2 <sub>7</sub> /DB7           | I/O | CMOS I/O port (data bus). When the MCU is in memory expansion or microprocessor mode, these pins<br>function as the data bus. These pins may also be used to implement the Key-on Wake up function.                                                                                                                          |               |  |  |  |

| P3 <sub>0</sub> /RDY                                     | I/O | CMOS I/O port (Ready). When the MCU is in memory expansion or microprocessor mode, this pin functions as RDY (hardware wait cycle control).                                                                                                                                                                                  | 40            |  |  |  |

| P3 <sub>1</sub>                                          | I/O | CMOS I/O port.                                                                                                                                                                                                                                                                                                               | 39            |  |  |  |

| P3 <sub>2</sub> /(VRFY)                                  | I/O | CMOS I/O port. When the MCU is in EPROM program mode, the pin is used as VRFY (EPROM memory verify).                                                                                                                                                                                                                         | 38            |  |  |  |

| P3 <sub>3</sub> /DMA <sub>out</sub><br>/PGM              | I/O | CMOS I/O port (DMA <sub>out</sub> ). When the MCU is in memory expansion or microprocessor mode, this pin is set to a "1" during a DMA transfer. When the MCU is in EPROM program mode, the pin is used as $\overline{PGM}$ (EPROM memory program).                                                                          | 37            |  |  |  |

| $P3_4/\Phi_{out}$                                        | I/O | CMOS I/O port ( $\Phi$ ). When the MCU is in memory expansion or microprocessor mode, this pin becomes $\Phi_{out}$ pin.                                                                                                                                                                                                     | 36            |  |  |  |

| P3 <sub>5</sub> /SYNC <sub>out</sub>                     | I/O | CMOS I/O port (SYNC output). When the MCU is in memory expansion or microprocessor mode, this pin becomes the SYNCout pin.                                                                                                                                                                                                   | 35            |  |  |  |

| $P3_{6}/\overline{WR}/(\overline{CE})$                   | I/O | CMOS I/O port. ( $\overline{WR}$ output). When the MCU is in memory expansion or microprocessor mode, this pin becomes $\overline{WR}$ . When the MCU is in EPROM program mode, the pin is used as $\overline{CE}$ (EPROM memory chip enable).                                                                               | 34            |  |  |  |

| $P3_7/\overline{RD}/(\overline{OE})$                     | I/O | CMOS I/O port. ( $\overline{RD}$ output). When the MCU is in memory expansion or microprocessor mode, this pin becomes $\overline{RD}$ . When the MCU is in EPROM program mode, the pin is used as $\overline{OE}$ (EPROM memory output enable).                                                                             | 33            |  |  |  |

| P4 <sub>0</sub> /EDMA                                    | I/O | CMOS I/O port (EDMA: Expanded Data Memory Access). When the MCU is in memory expansion or microprocessor mode, this pin can become the EDMA pin.                                                                                                                                                                             | 24            |  |  |  |

| P4 <sub>1</sub> /INT0<br>~ P4 <sub>2</sub> /INT1         | I/O | CMOS I/O port or external interrupt ports INT0 and INT1. These external interrupts can be configured to be active high or low.                                                                                                                                                                                               | 23-22         |  |  |  |

| P4 <sub>3</sub> /CNTR0                                   | I/O | CMOS I/O port or Timer X input pin for pulse width measurement mode and event counter mode or Timer X output pin for pulse output mode. This pin can also be used as an external interrupt when Timer X is not in output mode. The interrupt polarity is selected in the Timer X mode register.                              |               |  |  |  |

| P4 <sub>4</sub> /CNTR1                                   | I/O | CMOS I/O port or Timer Y input pin for pulse period measurement mode, pulse H-L measurement mode and event counter mode or Timer Y output pin for pulse output mode. This pin can also be used as an external interrupt when Timer Y is not in output mode. The interrupt polarity is selected in the Timer Y mode register. | 20            |  |  |  |

| P5 <sub>0</sub> /XC <sub>in</sub>                        | I/O | CMOS I/O port or XC <sub>in</sub> .                                                                                                                                                                                                                                                                                          | 12            |  |  |  |

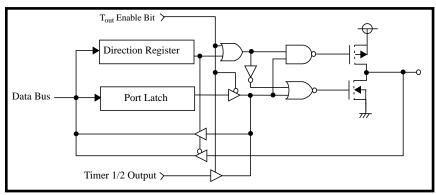

| P5 <sub>1</sub> /T <sub>out</sub> /<br>XC <sub>out</sub> | I/O | CMOS I/O port or Timer 1/2 pulse output pin (can be configured initially high or initially low), or XC <sub>out</sub> .                                                                                                                                                                                                      | 11            |  |  |  |

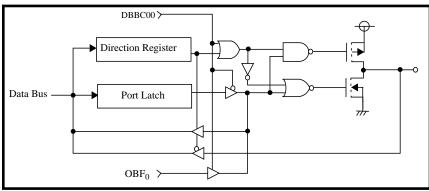

| P5 <sub>2</sub> /OBF <sub>0</sub>                        | I/O | CMOS I/O port or OBF <sub>0</sub> output to master CPU for data bus buffer 0.                                                                                                                                                                                                                                                | 8             |  |  |  |

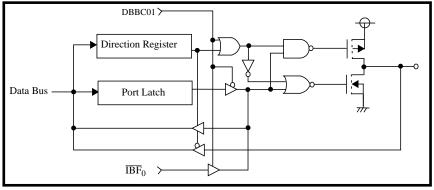

| P5 <sub>3</sub> /IBF <sub>0</sub>                        | I/O | CMOS I/O port or $\overline{\text{IBF}}_0$ output to master CPU for data bus buffer 0.                                                                                                                                                                                                                                       | 7             |  |  |  |

| $P5_4/\overline{S}_0$                                    | I/O | CMOS I/O port or $\overline{S}_0$ input from master CPU for data bus buffer 0.                                                                                                                                                                                                                                               | 6             |  |  |  |

| P5 <sub>5</sub> /A <sub>0</sub>                          | I/O | CMOS I/O port or A <sub>0</sub> input from master CPU.                                                                                                                                                                                                                                                                       | 5             |  |  |  |

| $P5_6/\overline{R}(E)$                                   |     | CMOS I/O port or $\overline{R}(E)$ input from master CPU.                                                                                                                                                                                                                                                                    | 4             |  |  |  |

| $P5_7/\overline{W}(R/\overline{W})$                      | I/O | CMOS I/O port or $\overline{W}(R/\overline{W})$ input from master CPU.                                                                                                                                                                                                                                                       | 3             |  |  |  |

| P6 <sub>0</sub> /DQ0<br>~ P6 <sub>7</sub> /DQ7           |     | CMOS I/O port or master CPU data bus.                                                                                                                                                                                                                                                                                        | 2-1,<br>80-75 |  |  |  |

| USB D <sup>-</sup>                                       | I/O | USB D- voltage line interface, a series resistor of 33 $\Omega$ should be connected to this pin. (see note)                                                                                                                                                                                                                  | 71            |  |  |  |

| USB D+                                                   | I/O | USB D+ voltage line interface, a series resistor of 33 $\Omega$ should be connected to this pin. (see note)                                                                                                                                                                                                                  | 70            |  |  |  |

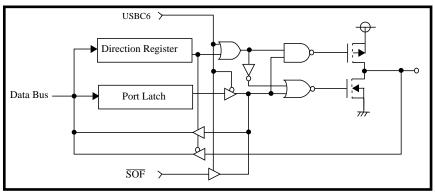

| P70/SOF                                                  |     | CMOS I/O port or USB start of frame pulse output, an 80 ns pulse outputs on this pin for every USB frame.                                                                                                                                                                                                                    | 69            |  |  |  |

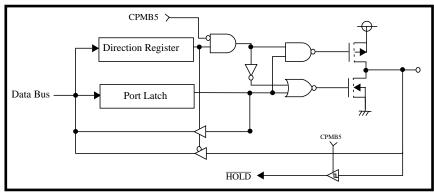

| P7 <sub>1</sub> /HOLD                                    |     | CMOS I/O port or HOLD pin.                                                                                                                                                                                                                                                                                                   | 68            |  |  |  |

| $\overline{P7_2/\overline{S}_1}$                         |     | CMOS I/O port or $\overline{S}_1$ input from master CPU for data bus buffer 1.                                                                                                                                                                                                                                               | 67            |  |  |  |

| 2 1                                                      |     | i i i i i i i i i i i i i i i i i i i                                                                                                                                                                                                                                                                                        | 1             |  |  |  |

#### Table 1-2. Pin Description

| Name                                        | I/O    | Description                                                                                                                                                                                                                                                                                                                            | Pin #           |  |  |

|---------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| P7 <sub>3</sub> /IBF <sub>1</sub> /<br>HLDA | I/O    | CMOS I/O port or $\overline{IBF}_1$ output to master CPU for data bus buffer 1, or $\overline{HLDA}$ pin. $\overline{IBF}_1$ and $\overline{HLDA}$ are nutually exclusive. $\overline{IBF}_1$ has priority over $\overline{HLDA}$ .                                                                                                    |                 |  |  |

| P7 <sub>4</sub> /OBF <sub>1</sub>           | I/O    | CMOS I/O port or OBF <sub>1</sub> output to master CPU for data bus buffer 1.                                                                                                                                                                                                                                                          | 65              |  |  |

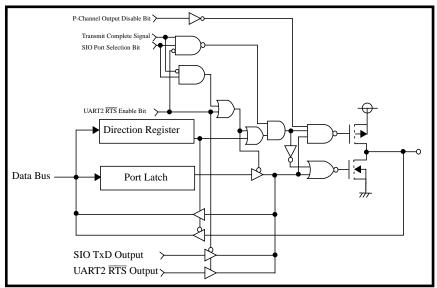

| P8 <sub>0</sub> /UTXD2/<br>SRDY             | I/O    | CMOS I/O port or UART2 pin UTXD2 or SIO pin SRDY. UART2 and SIO are mutually exclusive, UART2 has priority over SIO.                                                                                                                                                                                                                   | 32              |  |  |

| P8 <sub>1</sub> /URXD2/<br>SCLK             | I/O    | CMOS I/O port or UART2 pin URXD2 or SIO pin SCLK. UART2 and SIO are mutually exclusive, UART2 has priority over SIO.                                                                                                                                                                                                                   | 31              |  |  |

| P8 <sub>2</sub> /CTS2/<br>SRXD              | I/O    | CMOS I/O port or UART2 pin CTS2 or SIO pin SRXD. UART2 and SIO are mutually exclusive, UART2 has priority over SIO.                                                                                                                                                                                                                    | 30              |  |  |

| P8 <sub>3</sub> / <del>RTS2</del> /<br>STXD | I/O    | CMOS I/O port or UART2 pin RTS2 or SIO pin STXD. UART2 and SIO are mutually exclusive, UART2 has priority over SIO.                                                                                                                                                                                                                    | 29              |  |  |

| P8 <sub>4</sub> /UTXD1                      | I/O    | CMOS I/O port or UART1 pin UTXD1.                                                                                                                                                                                                                                                                                                      | 28              |  |  |

| P85/URXD1                                   | I/O    | CMOS I/O port or UART1 pin URXD1.                                                                                                                                                                                                                                                                                                      | 27              |  |  |

| P8 <sub>6</sub> /CTS1                       | I/O    | CMOS I/O port or UART1 pin CTS1.                                                                                                                                                                                                                                                                                                       | 26              |  |  |

| P87/RTS1                                    | I/O    | CMOS I/O port or UART1 pin RTS1.                                                                                                                                                                                                                                                                                                       | 25              |  |  |

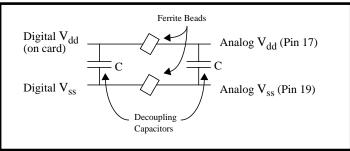

| AV <sub>cc</sub> ,AV <sub>ss</sub>          | Ι      | Power supply inputs for analog circuitry $AV_{cc} = 4.15 \sim 5.25V$ , $AV_{ss} = 0V$                                                                                                                                                                                                                                                  | 17,19           |  |  |

| CNV <sub>ss</sub>                           | Ι      | Controls the processor mode of the chip. Normally connected to $V_{ss}$ or $V_{cc}$ . When the MCU is in EPROM program mode, this pin supplies the programming voltage to the EPROM.                                                                                                                                                   |                 |  |  |

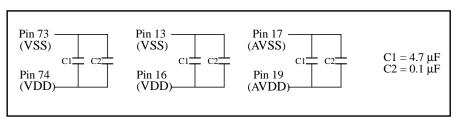

| V <sub>cc</sub> ,V <sub>ss</sub>            | Ι      | Power supply inputs: $V_{cc} = 4.15 \sim 5.25 V$ , $V_{ss} = 0 V$                                                                                                                                                                                                                                                                      | 16/74,<br>13/73 |  |  |

| RESET                                       | Ι      | To enter the reset state, this pin must be kept L for more that $2\mu s$ (20 $\Phi$ cycles under normal V <sub>cc</sub> conditions). If the crystal or ceramic resonator requires more time to stabilize, extend this L level time appropriately.                                                                                      | 10              |  |  |

| XC <sub>in</sub><br>XC <sub>out</sub>       | I<br>O | An external ceramic or quartz crystal oscillator can be connected between the $XC_{in}$ and $XC_{out}$ pins. If an external clock source is used, connect the clock source to the $XC_{in}$ pin and leave the $XC_{out}$ pin open.                                                                                                     | 12<br>11        |  |  |

| X <sub>in</sub><br>X <sub>out</sub>         | I<br>O | Input and output signals to and from the internal clock generation circuit. Connect a ceramic resonator or quartz crystal between $X_{in}$ and $X_{out}$ pins to set the oscillation frequency. If an external clock is used, connect the clock source to the $X_{in}$ pin and leave the $X_{out}$ pin open.                           |                 |  |  |

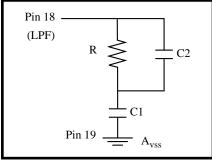

| LPF                                         | 0      | Loop filter for the frequency synthesizer.                                                                                                                                                                                                                                                                                             | 18              |  |  |

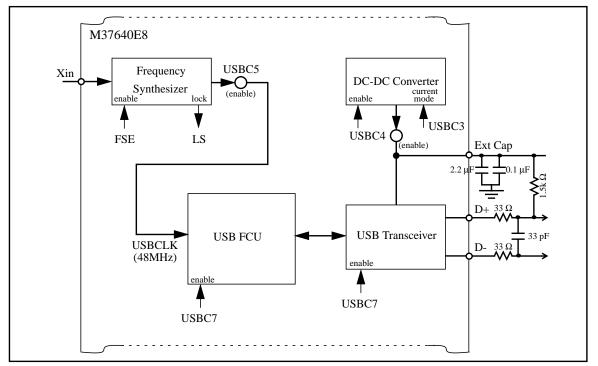

| Ext. Cap                                    | Ι      | An external capacitor (Ext. Cap) pin. When the USB transceiver voltage converter is used, a $2\mu$ f or larger capacitor should connect between this pin and $V_{ss}$ to ensure proper operation of the USB line driver. The voltage converter is enabled by setting bit 4 of the USB control register (0013 <sub>16</sub> ) to a "1". |                 |  |  |

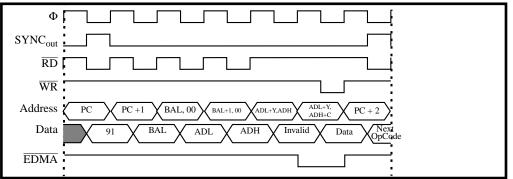

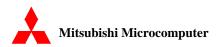

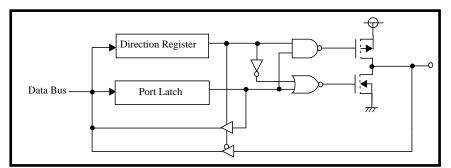

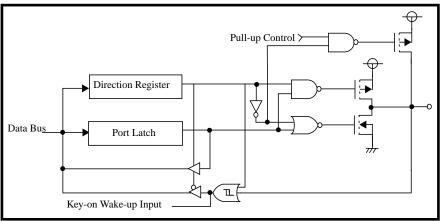

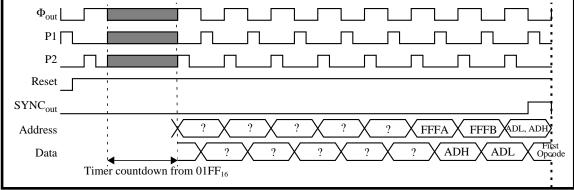

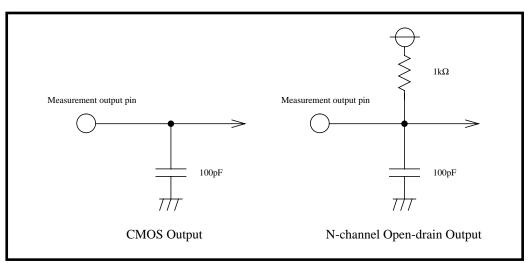

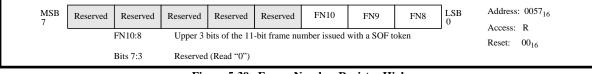

#### Table 1-2. Pin Description